# FCAL testbeam preparation

Szymon Kulis\* on behalf of FCAL Collaboration

\*) AGH-UST Kraków

#### Outline

- Development status

- Preparation of test setup of the whole readout chain

- □ Testbeam plans

- □ Summary & plans

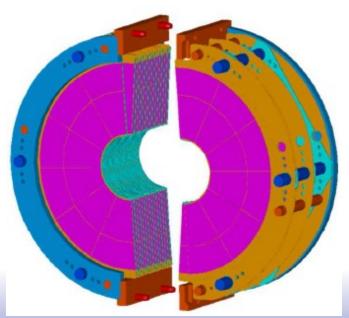

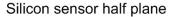

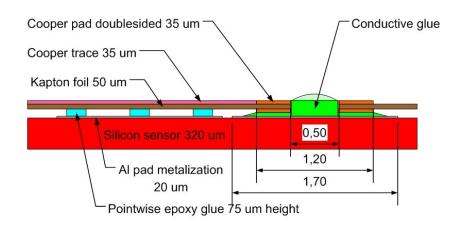

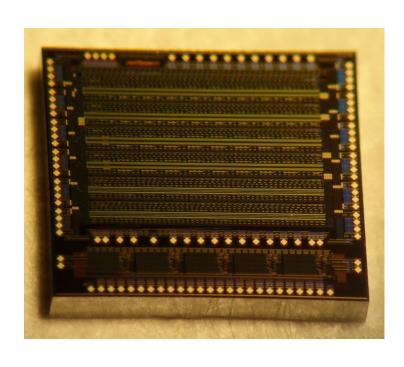

#### Silicon sensors

- 48 azimuthal sectors

- 64 radial pads in sector

- Prototypes (30°

4 sectors each) from Hamamatsu

- High resistivity n-type Si bulk 320um thick

- P+ pads with Al-metalization (DC coupled)

#### Prototypes produced

Electrical parameters checked

Tests with particles needed

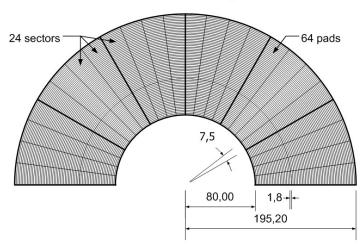

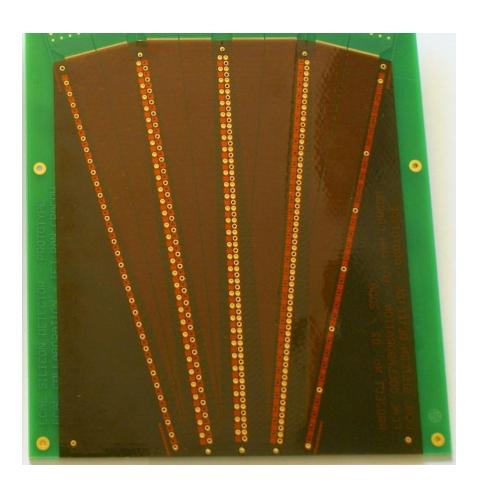

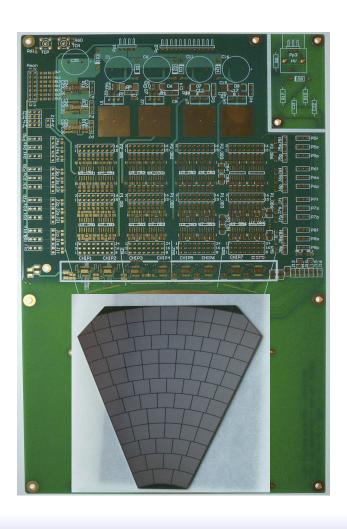

### Capton fanout

- 50um thick

- Two slightly different types of fanout produced

- Will be glued to sensors

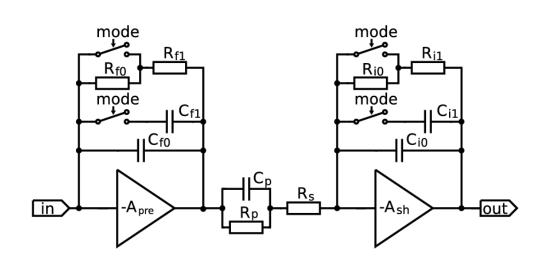

#### Front-end electronics

#### Specifications:

- $C_{det} = 10 100 pF$

- $T_{peak} \sim 60 \text{ ns}$

- Variable gain: physics and calibration mode

- $Q_{max} \sim 10 pC$

- Calibration mode: S/N > 10 for MIP

- Charge amplifier

- □ Pole zero cancellation

- □ 1<sup>st</sup> order shaping

- Fabricated in AMS 0.35μm

8 channels prototype produced

measurements agree with simulations

Tests with sensor needed

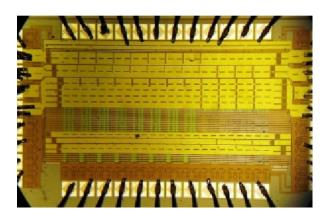

### 10 bit pipeline ADC

Prototype ADC channels with and without S/H fabricated in AMS 0.35  $\mu m$  technology

- → Pipeline architecture (fully differential) power efficient & small area

- □ 10 bits resolution (1.5 bit per stage)

- Input dynamic range 2 V

- □ Maximum sampling rate ~30 MHz

- $\supset$  DNL < 0.5 LSB, INL < 1 LSB

- Multi channel version should be ready in few months (beginning of 2010)

single channel prototypes produced

measurements agree with simulations

More measurements needed

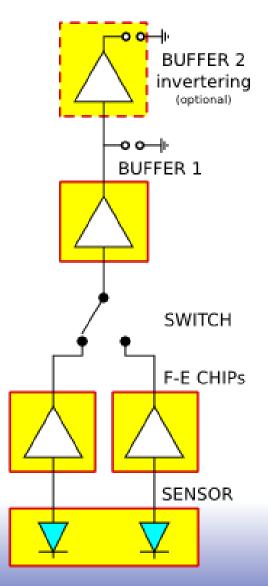

## Preparation of sensor-readout electronics test-setup chain

- □ Setup includes:

- Sensor

- Capton fanout

- Dedicated PCB

- Front-end ASICs

- Output buffers (to drive long wires)

- No ADC on board

(NO multichannel ADC yet)

#### Readout chain test setup

- □ Up to 8 front-end ASIC (64 channels)

- Two types of fanout can be tested

- All needed biasing and power supply included

- Buffered analogue outputs

PCB produced and partially assembled

Assembly needs to be completed... Readout chain needs to be tested...

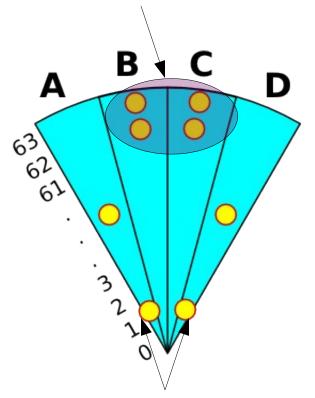

### Preparation of testbeam

testbeam area?

Each yellow dot means : 1 ASIC (8 channels)

- Same setup is going to be used for testbeam – PCB board designed to be used also in testbeam

- □ Up to 32 readout channels can be read at the same time

- External multichannel ADC has to be used

- VME V1740 will be used

- Work on software has started

- □ External trigger (Eudet telescope ?)

The whole readout chain needs to be checked first...

### Preparation of testbeam...

- We would like to use EUDET telescope for tracking

- We would like to check the chain also with BeamCal GaAs sensors

#### Status & Plans

- Sensors

- ☐ Capton fanout

- 8 channel front-end ASIC

- Single channel ADC ASIC

- Dedicated PCB

- Parametrization of setup

- Multichannel ADC ASIC

READY

READY

READY

READY

READY

N ROGRESS

~ Jan.2010

IN ROGRESS

~ Dec.2009(submission)

□ Test beam planed in the middle of 2010