#### Baseline ECal update

R. Frey (Oregon) for the ECal group

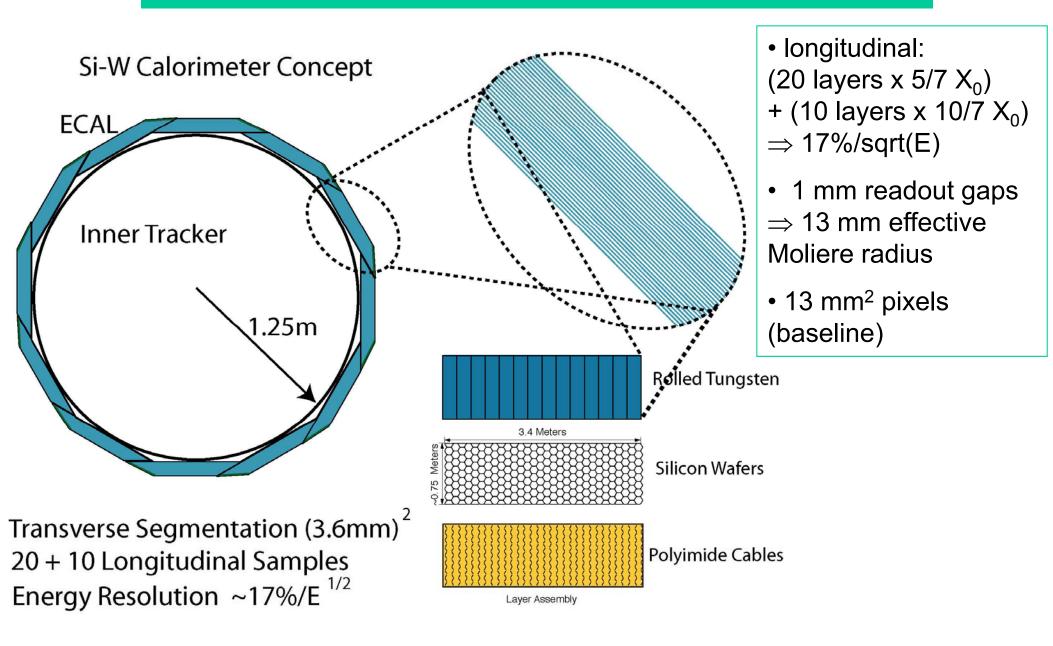

- Silicon/tungsten concept

- Baseline option: R&D progress

- Sensors

- KPiX readout (→ D. Freytag talk)

- Interconnects

- (Mechanical design for SiD)

- SiD/CLIC

Alternative technology choice: MAPS/Terapixel progress (see Marcel Stanitzki talk)

## Si/W (baseline) R&D Collaboration

M. Breidenbach, D. Freytag, N. Graf, R. Herbst, G. Haller, J. Jaros, T. Nelson, M. Oriunno Stanford Linear Accelerator Center

J. Brau, R. Frey, D. Strom, P. Radloff, C. Gallagher, W. McCann *U. Oregon*

> V. Radeka Brookhaven National Lab

B. Holbrook, R. Lander, M. Tripathi, M. Woods *UC Davis*

- KPiX readout chip

- downstream readout

- mechanical design and integration

- detector development

- readout electronics

- readout electronics

- Interconnects: bump bonding, flex cable development

#### **Baseline Silicon-Tungsten ECal**

#### Two intertwined goals

Complete the R&D, build a test stack, and evaluate performance in a test beam.

Fully integrate the design into SiD

|        | Year 1<br>(7/2009–7/2010)                                                                                                                                                                                                                                                                      | Year 2<br>(7/10-7/11)                                                                               | Year 3<br>(7/11-7/12)          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------|

| Goal   | Complete R&D on component technologies                                                                                                                                                                                                                                                         | Assemble test<br>module, start<br>beam test                                                         | Beam test,<br>data<br>analysis |

| Status | <ul> <li>Sensors – OK</li> <li>Tungsten – OK</li> <li>KPiX – 512 channel chip to be evaluated. If ok, order 1024 KPiX.</li> <li>KPiX-Si bumps: need to converge on technology – gold stud thermo-compress?</li> <li>Flex cable – ok</li> <li>Cable-Si connect: needs R&amp;D – ACF?</li> </ul> | Need the<br>integrated tests<br>first.<br>Flex cable can<br>be done<br>separately;<br>same for DAQ  | tbd                            |

| Plan   | <ul> <li>Have 1024 KPiX and bumping technology<br/>by summer for combined testing in lab. (512<br/>KPiX would be ok for initial combined tests.)</li> <li>indium/solder bb as fallback for gold studs</li> <li>Need to finalize cable-Si technology</li> </ul>                                 | If integrated<br>tests look OK,<br>begin planning<br>for beam test.<br>Assume SLAC<br>beam for now. | tbd                            |

|        | Year 1<br>(7/2009–7/2010)                                                                                                                                                                                                                                                                                      | Year 2<br>(7/10-7/11)                                                                               | Year 3<br>(7/11-7/12)          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------|

| Goal   | Complete R&D on component technologies                                                                                                                                                                                                                                                                         | Assemble test<br>module, start<br>beam test                                                         | Beam test,<br>data<br>analysis |

| Status | <ul> <li>Status</li> <li>Sensors – OK</li> <li>Tungsten – OK</li> <li>KPiX – 512 channel chip to be evaluated. If ok, order 1024 KPiX.</li> <li>KPiX-Si bumps: need to converge on technology – gold stud thermo-compress?</li> <li>Flex cable – ok</li> <li>Cable-Si connect: needs R&amp;D – ACF?</li> </ul> | Need the integrated tests                                                                           | tbd                            |

|        |                                                                                                                                                                                                                                                                                                                | first.<br>Flex cable can<br>be done<br>separately;<br>same for DAQ                                  | Not there yet                  |

|        |                                                                                                                                                                                                                                                                                                                |                                                                                                     |                                |

| Plan   | <ul> <li>Have 1024 KPiX and bumping technology<br/>by summer for combined testing in lab. (512<br/>KPiX would be ok for initial combined tests.)</li> <li>indium/solder bb as fallback for gold studs</li> <li>Need to finalize cable-Si technology</li> </ul>                                                 | If integrated<br>tests look OK,<br>begin planning<br>for beam test.<br>Assume SLAC<br>beam for now. | tbd                            |

|        | Year 1<br>(7/2009–7/2010)                                                                                                                                                                                                                                                                      | Year 2<br>(7/10-7/11)                                                                               | Year 3<br>(7/11-7/12)          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------|

| Goal   | Complete R&D on component technologies                                                                                                                                                                                                                                                         | Assemble test<br>module, start<br>beam test                                                         | Beam test,<br>data<br>analysis |

| Status | <ul> <li>Sensors – OK</li> <li>Tungsten – OK</li> <li>KPiX – 512 channel chip to be evaluated. If ok, order 1024 KPiX.</li> <li>KPiX-Si bumps: need to converge on technology – gold stud thermo-compress?</li> <li>Flex cable – ok</li> <li>Cable-Si connect: needs R&amp;D – ACF?</li> </ul> | Need the integrated tests first.                                                                    | tbd                            |

| Plan   | <ul> <li>Have 1024 KPiX and bumping technology<br/>by summer for combined testing in lab. (512<br/>KPiX would be ok for initial combined tests.)</li> <li>indium/solder bb as fallback for gold studs</li> <li>Need to finalize cable-Si technology</li> </ul>                                 | If integrated<br>tests look OK,<br>begin planning<br>for beam test.<br>Assume SLAC<br>beam for now. | tbd                            |

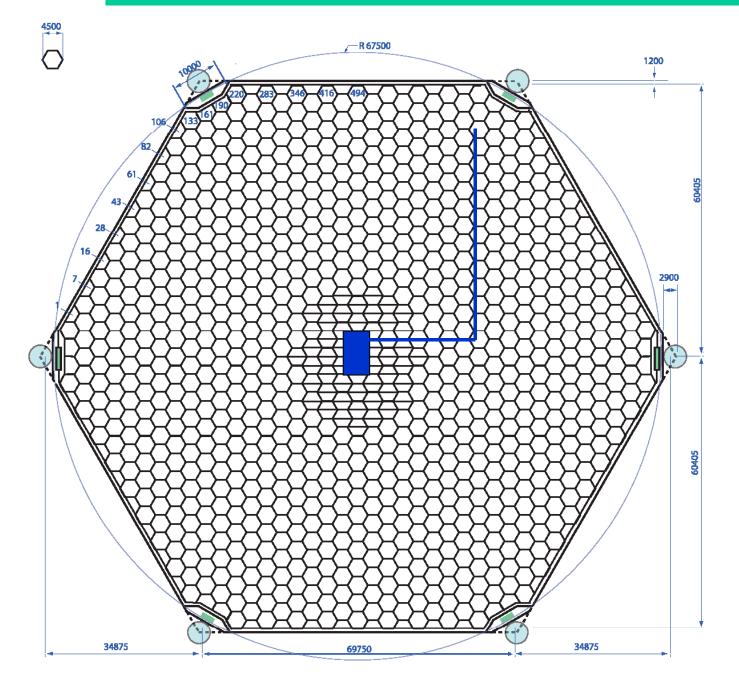

#### v2 Si sensors – mid 2008

- 6 inch wafer

- 1024 13 mm<sup>2</sup> pixels

- improved trace

layout and split pixels

near KPiX to reduce

capacitance

• 40 good + 20 NG sensors in hand, Hamamatsu

KPiX ASIC and sample trace

|        | Year 1<br>(7/2009–7/2010)                                                                                                                                                                                                                                      |                           | Year 2<br>(7/10-7/11)                                                                               | Year 3<br>(7/11-7/12)          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------|

| Goal   | Complete R&D on component technologies                                                                                                                                                                                                                         |                           | Assemble test<br>module, start<br>beam test                                                         | Beam test,<br>data<br>analysis |

| Status | <ul> <li>Sensors – OK</li> <li>Tungsten – OK</li> </ul>                                                                                                                                                                                                        | 1024 chip<br>ordered ~now | Need the integrated tests                                                                           | tbd                            |

|        | <ul> <li>KPiX – 512 channel chip to be evaluated. If ok, order 1024 KPiX.</li> <li>KPiX-Si bumps: need to converge on technology – gold stud thermo-compress?</li> <li>Flex cable – ok</li> <li>Cable-Si connect: needs R&amp;D – ACF?</li> </ul>              |                           | first.                                                                                              |                                |

|        |                                                                                                                                                                                                                                                                |                           | Flex cable can<br>be done<br>separately;<br>same for DAQ                                            |                                |

| Plan   | <ul> <li>Have 1024 KPiX and bumping technology<br/>by summer for combined testing in lab. (512<br/>KPiX would be ok for initial combined tests.)</li> <li>indium/solder bb as fallback for gold studs</li> <li>Need to finalize cable-Si technology</li> </ul> |                           | If integrated<br>tests look OK,<br>begin planning<br>for beam test.<br>Assume SLAC<br>beam for now. | tbd                            |

|        | Year 1<br>(7/2009–7/2010)                                                                                                                                                                                                                                      | Year 2<br>(7/10-7/11)                                                                               | Year 3<br>(7/11-7/12)          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------|

| Goal   | Complete R&D on component technologies                                                                                                                                                                                                                         | Assemble test<br>module, start<br>beam test                                                         | Beam test,<br>data<br>analysis |

| Status | <ul> <li>Sensors – OK</li> <li>Tungsten – OK</li> <li>KPiX – 512 channel chip to be evaluated. If ok, order 1024 KPiX</li> <li>KPiX-Si bumps: need to converge on technology – gold stud thermo-compress?</li> </ul>                                           | Need the<br>integrated tests<br>first.<br>Flex cable can<br>be done                                 | tbd                            |

|        | <ul> <li>Flex cable – ok</li> <li>Cable-Si connect: needs R&amp;D – ACF ?</li> </ul>                                                                                                                                                                           | separately;<br>same for DAQ                                                                         |                                |

| Plan   | <ul> <li>Have 1024 KPiX and bumping technology<br/>by summer for combined testing in lab. (512<br/>KPiX would be ok for initial combined tests.)</li> <li>indium/solder bb as fallback for gold studs</li> <li>Need to finalize cable-Si technology</li> </ul> | If integrated<br>tests look OK,<br>begin planning<br>for beam test.<br>Assume SLAC<br>beam for now. | tbd                            |

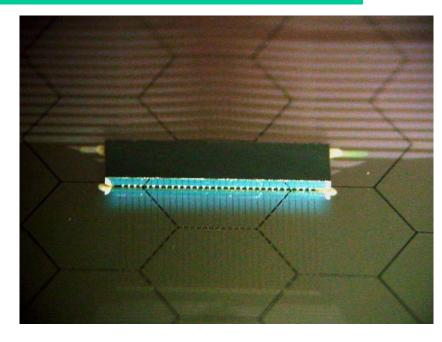

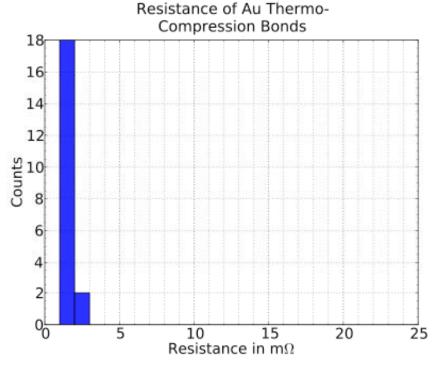

## **Gold-Stud Thermo-compression Bonding**

Appeared to be an ideal technique for bump-bonding with prototypes:

- Complete in-house capability.

- Good results obtained with dummy chips with bump resistances <5 m $\Omega$

However, the same technique did not work for Hamamatsu sensor wafers because the oxide under the bump could not withstand the ~160g/bump pressure. It was crushed resulting in shorts with buried traces.

#### Take n: Current plan for KPiX-sensor bb

- The new version of KPiX (1024) will have solder bumps placed on it by TSMC. (!!)

- These bumps are made using the C4 process -- the solder used is high temp Pb/Sn (95/5 %).

- We (Davis) are looking to acquire an oven capable of uniform and controlled re-flow of this solder at 320° C for bonding to sensors.

|        | Year 1<br>(7/2009–7/2010)                                                                                                                                                                                                                                                                            | Year 2<br>(7/10-7/11)                                                                               | Year 3<br>(7/11-7/12)          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------|

| Goal   | Complete R&D on component technologies                                                                                                                                                                                                                                                               | Assemble test<br>module, start<br>beam test                                                         | Beam test,<br>data<br>analysis |

| Status | <ul> <li>Sensors – OK</li> <li>Tungsten – OK</li> <li>KPiX – 512 channel chip to be evaluated. If ok, order 1024 KPiX.</li> <li>KPiX-Si bumps: need to converge on technology – gold stud thermo-compress?</li> <li>Flex cable – ok maybe</li> <li>Cable-Si connect: needs R&amp;D – ACF?</li> </ul> | Need the<br>integrated tests<br>first.<br>Flex cable can<br>be done<br>parately;<br>same for DAQ    | tbd                            |

| Plan   | <ul> <li>Have 1024 KPiX and bumping technology<br/>by summer for combined testing in lab. (512<br/>KPiX would be ok for initial combined tests.)</li> <li>indium/solder bb as fallback for gold studs</li> <li>Need to finalize cable-Si technology</li> </ul>                                       | If integrated<br>tests look OK,<br>begin planning<br>for beam test.<br>Assume SLAC<br>beam for now. | tbd                            |

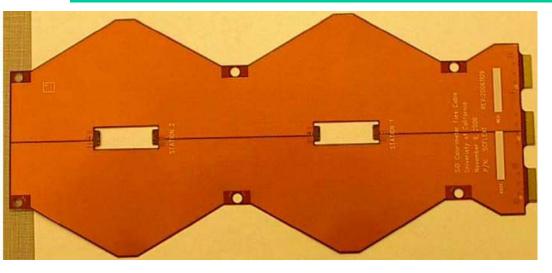

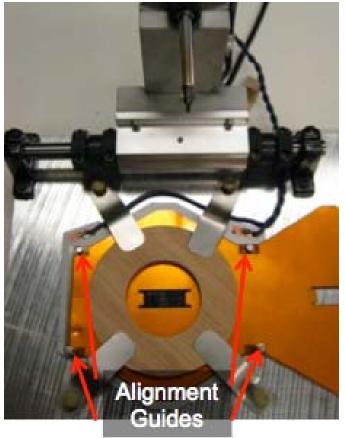

#### Flex cables (Davis)

#### **Flexcables**

- "OK" for test stack

- Need to check longer ~1 m cables for SiD.

Sensor connection technology:

- ACF looks promising for largescale production

- Solder bumps current default

- Placed using Davis setup

- <180 C solder</p>

- Trials with dummy sensors started

|        | Year 1<br>(7/2009–7/2010)                                                                                                                                                                                                                                                                      | Year 2<br>(7/10-7/11)                                                                              | Year 3<br>(7/11-7/12)                                       |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Goal   | Complete R&D on component technologies                                                                                                                                                                                                                                                         | Assemble test<br>module, start<br>beam test                                                        | Beam test,<br>data<br>analysis                              |

| Status | <ul> <li>Sensors – OK</li> <li>Tungsten – OK</li> <li>KPiX – 512 channel chip to be evaluated. If ok, order 1024 KPiX.</li> <li>KPiX-Si bumps: need to converge on technology – gold stud thermo-compress?</li> <li>Flex cable – ok</li> <li>Cable-Si connect: needs R&amp;D – ACF?</li> </ul> | Need the<br>integrated tests<br>first.<br>Flex cable can<br>be done<br>separately;<br>same for DAQ | tbd<br>S                                                    |

|        | Have 1024 KPiX and bumping technology                                                                                                                                                                                                                                                          | If integrated                                                                                      | tbd                                                         |

| Plan   | <ul> <li>by summer for combined testing in lab. (512</li> <li>KPiX would be ok for initial combined tests.)</li> <li>indium/solder bb as fallback for gold studs</li> <li>Need to finalize cable-Si technology</li> </ul>                                                                      | tests look OK<br>begin plannin<br>for beam test<br>Assume SLA<br>beam for now                      | Our schedule<br>is adjusting to<br>that of the<br>SLAC test |

|        | R Frey Eugene SiD                                                                                                                                                                                                                                                                              |                                                                                                    | beam !                                                      |

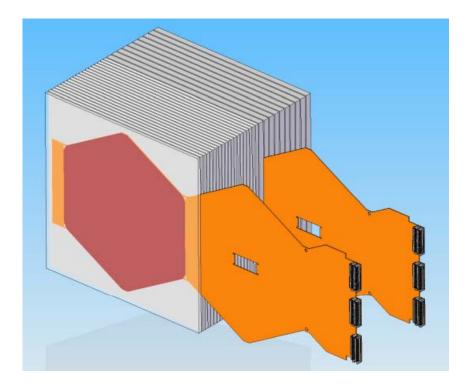

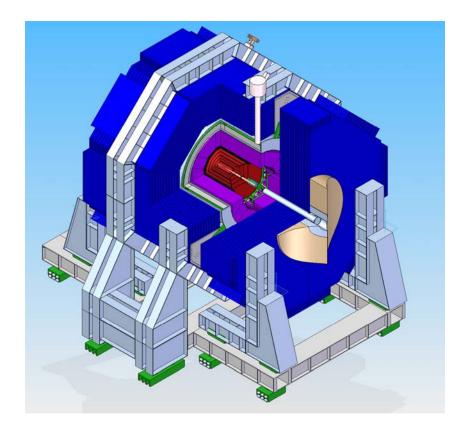

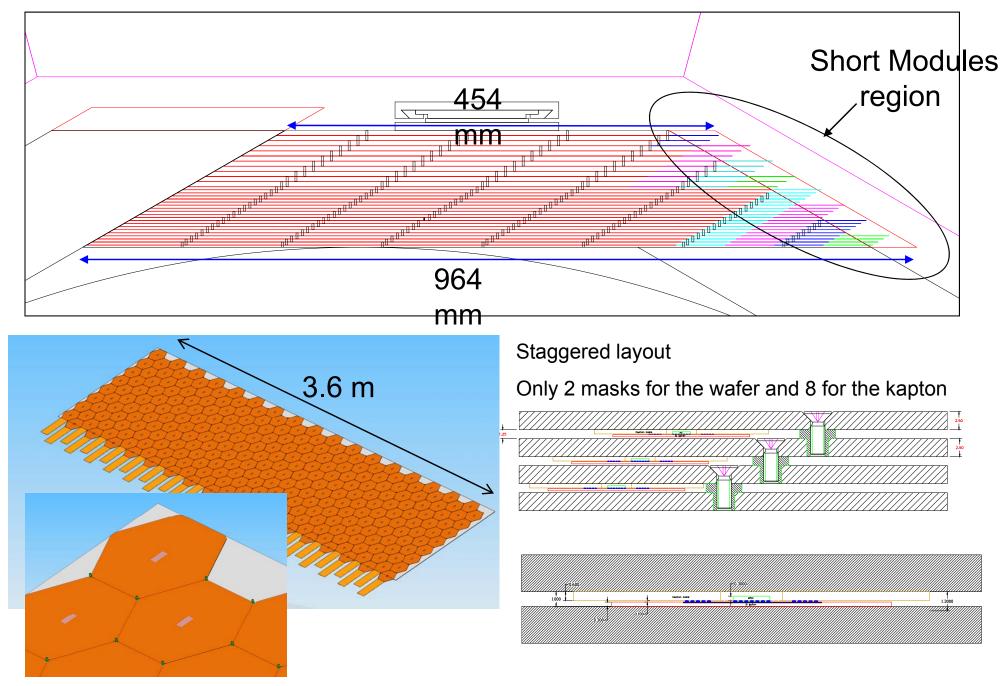

#### ECal barrel mech. design – Oriunno, 2008

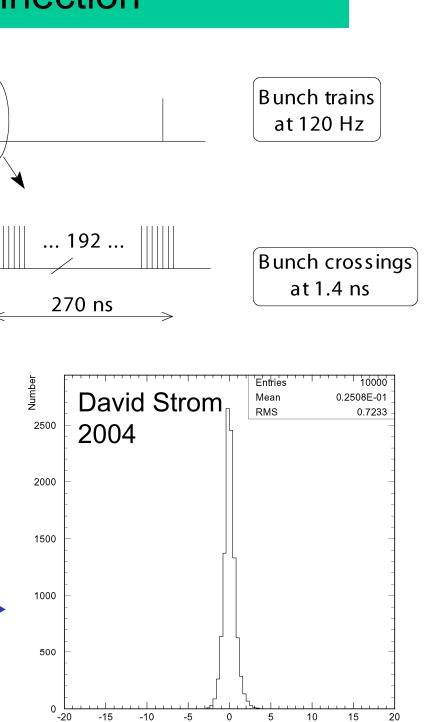

## (another) CLIC connection

8.33 ms

For warm technology, we considered the ability to do time stamping with the Si/W ECal (ca 2004)

- The ECal was ~ identical to the current baseline Si/W, but with electronics designed for warm.

- A MIP hit would give ~5 ns timing resolution per Si layer

- Result is for simulation of single MIPs (30 layers) with 50 ns time → constant in preamp.

Reconstructed Time (ns)

### Summary

- Steady technical progress with the R&D

- 1024-channel KPiX will be available in ~2 months

- If bump-bonding technology works (!), we will be able to do the first system tests of the sensor+KPiX (winter 2011).

- (Still) getting close to fabricating a test stack for a beam test.

- (Still) compatible with schedule of SLAC test beam

- For implementation in SiD, a number of issues to settle:

- Finalize the mechanical design for the barrel.

- System tests: cooling, power delivery, correlated noise, etc.

- Need a tiling scheme and mech. design for the endcaps

- Reconstruction effort welcome, e.g. photon id in jets

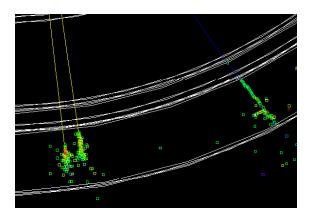

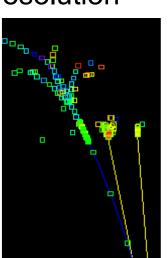

# Physics, ECal, LOI

Guiding principles: Measure all final states and measure with precision

- Multi-jet final states

- $\pi^{\circ}$  measurement should not limit jet resolution

- id and measure h° and h<sup>±</sup> showers

- track charged particles

- Tau id and analysis

- Photons

- Energy resolution, e.g.  $h \rightarrow \gamma \gamma$

- Vertexing of photons (  $\sigma_b \sim 1 \text{ cm}$  ), e.g. for GMSB

- Electron id

- Bhabhas and Bhabha acollinearity

- Hermiticity

#### $\Rightarrow$ Imaging Ecalorimetry can do all this