# A Consideration of Combined DAQ for hybrid ECAL

### Taikan Suehara (Kyushu University)

# **CALICE DAQ**

According to https://twiki.cern.ch/twiki/bin/view/CALICE/CALICEDAQ The CALICE DAQ is supposed to be generic and quite independent of the underlying detector technology. But currently we use independent DAQ systems in •Si ECAL •Sc ECAL / AHCAL •SDHCAL •DHCAL •Others?

# **Our motivation**

### Hybrid ECAL

- We are considering hybrid (Si+Sc) ECAL as an option of good balance for cost and robustness

- We are considering to perform a combined beam test for some time in this or next year

- We'd like to combine DAQ of SiECAL and ScECAL to run synchronously and to get an easy-to-combine output

- In addition, I think ILD should gain from combined DAQ to reduce overall efforts since ROC chips are very similar for all systems.

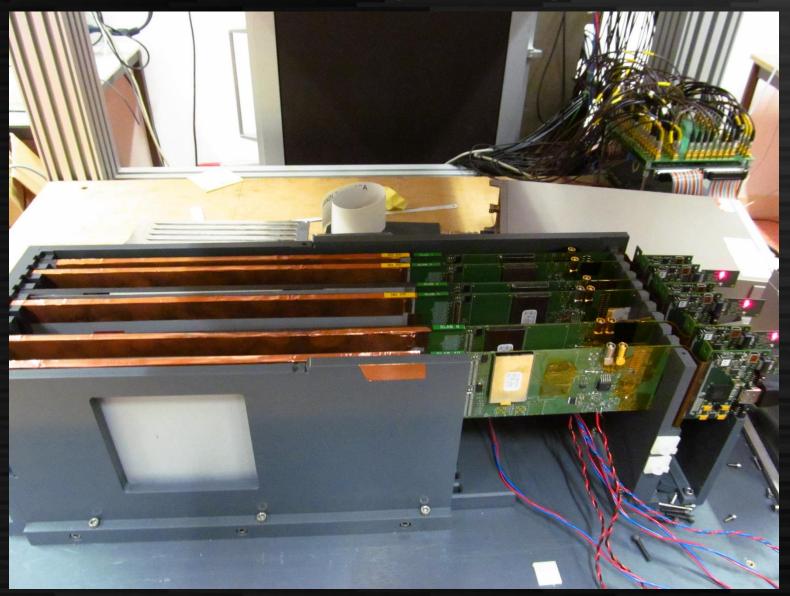

# SiECAL slabs (FEV8) in LLR

### Si-ECAL DAQ

SKIROC2

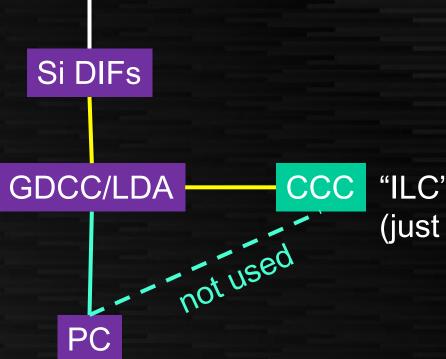

#### "ILC" mode (just a fanout of clock)

#### HDMI connetion Ethernet connection

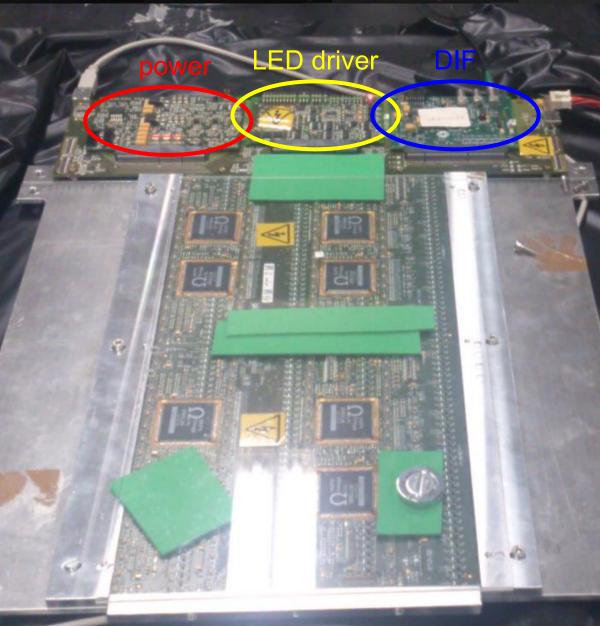

# Sc-ECAL slab (EBU) in Shinshu

Mar. 2014 page 7

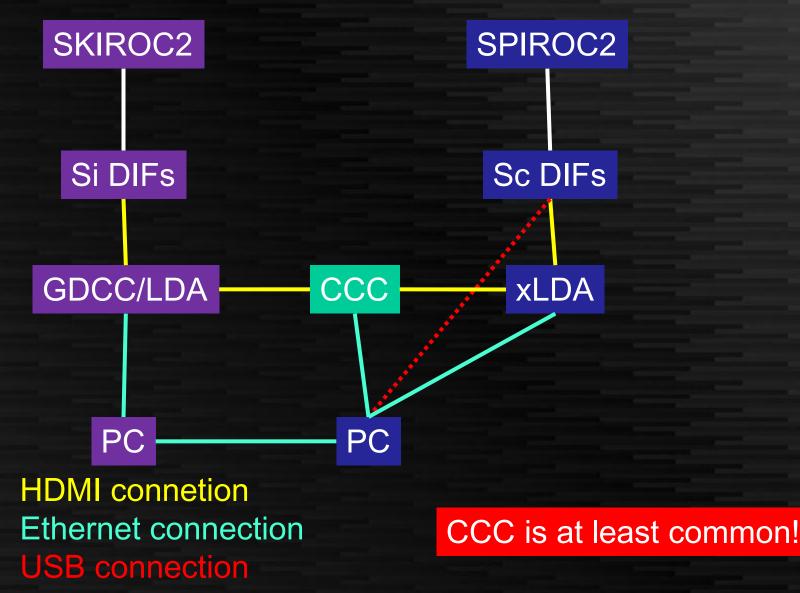

## **New CCC/xLDA in DESY**

#### still under development

### Sc-ECAL/AHCAL DAQ

CCC

#### SPIROC2

Sc DIFs

PC LabVIEW software HDMI connetion Ethernet connection USB connection

# Sc-ECAL/AHCAL DAQ (planned)

SPIROC2

Sc DIFs

**xLDA**

command only or removed ...

CCC

PC LabVIEW display + C++ DAQ

HDMI connetion Ethernet connection USB connection

### **Combined DAQ?**

## Some issues on CCC

- BUSY treatment

- BUSY = clock (or oscillating) in Si-ECAL

- BUSY = just a level in Sc

- Possible to treat by "two-mode" CCC

- Ramp-up time (in power-pulsing)

- May be different in Si and Sc

- "Pre-spill" preferred or fixed wait?

- BX tagging

- Common problem reliability of timing of FAST command

# **CCC: three modes**

1. "test beam" mode

start\_acq → wait busy → stop\_acq → wait busy

cleared → start\_acq

### 2. "ILC" mode

- start\_acq → wait fixed time → stop\_acq → wait

fixed time → start\_acq

- Start/stop of run is still controlled by CCC

- 3. "just a fanout" operation

- Same cycle as 2

- No run control: just passing through spills

# CCC I/O of HDMI

- Digital lines (3+2 pairs in HDMI)

- Clock, ExTrig, commands CCC→LDA

- Busy, (commands) LDA→CCC

- Commands

- Start\_acq (SPILL)

- Stop\_acq

New CCC from DESY/Mainz for all?

# LDA/GDCC/xLDA

- Claimed that "function is the same"

- Possibly exchangeable, maybe not

- Maybe not needed

- Easier if exchangeable

- Output connection to PC not compatible

- TCP/UDP/raw ethernet

- format of data

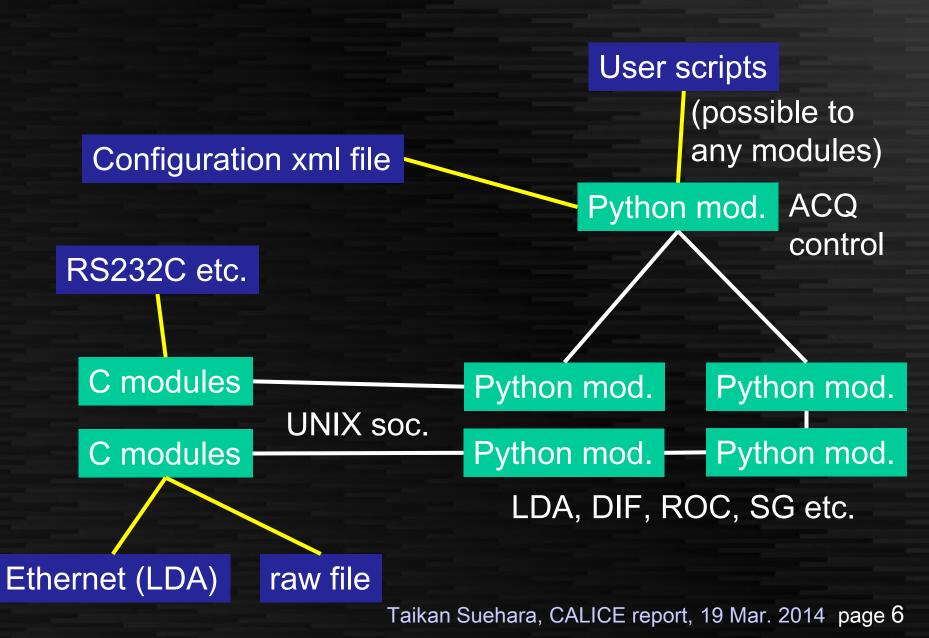

# Software: options

- 1. Independent software

- The way which I do not want to go

- just keep at a backup option

- At least run info should be communicated

- 2. Unified software

- Calicoes/LLR

- LabVIEW/DESY

- xDAQ (CMS/SDHCAL)

- AIDA EUDAQ (just heard from Vincent today)

- others/completely new

# **Comparison in my opinion**

| DAQ                                                                                                                         | Advantages                                                                                 | Disadvantages                                                |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Calicoes                                                                                                                    | SiECAL implemented<br>Simple & easy                                                        | Lower maintenance level<br>Not public<br>GUI not implemented |

| LabVIEW                                                                                                                     | Sc implemented<br>Easy to implement GUI                                                    | Slow<br>Difficult to read/maintain codes                     |

| xDAQ                                                                                                                        | Maintained by CERN/CMS<br>public framework<br>Many features<br>C++ based (for me: easiest) | A little complicated<br>Have to learn the framework          |

| AIDA<br>EUDAQ                                                                                                               | Simpler than xDAQ<br>C++ based<br>LCIO output?                                             | No implementation for CALICE now?                            |

| new                                                                                                                         | Completely free                                                                            | Maximum effort needed                                        |

| Will consider xDAQ and AIDA                                                                                                 |                                                                                            |                                                              |

| Support (I mean, just a code sharing) from SDHCAL possible<br>for xDAQ? Taikan Suehara, CALICE report, 19 Mar. 2014 page 17 |                                                                                            |                                                              |

## **Consideration on unified software**

- Connectivity to calicoes

- Connectivity to LabVIEW configuration and data display for Sc system

- Maybe have own GUI

- Focused on DAQ control and display, not for making detailed ASIC configuration files

- each already has a script for the configuration

# Summary

- With some consideration, hardware can be interoperated

- For software, I'll investigate xDAQ & AIDA

- Plan to be available later in this year

software will be public

- Any cooperation is highly welcome