# **AHCAL Status.**

## **Electronics and DAQ**

Mathias Reinecke

CALICE meeting Argonne ANL, Mar. 19th, 2014

## **Outline**

- Status Hardware

- HBU3 redesign.

- EBU

- New DAQ

- Replace USB => x-LDA

- Towards a combined CALICE testbeam

A flexlead disappears in an AHCAL steel cassette.

## **HBU3** redesign

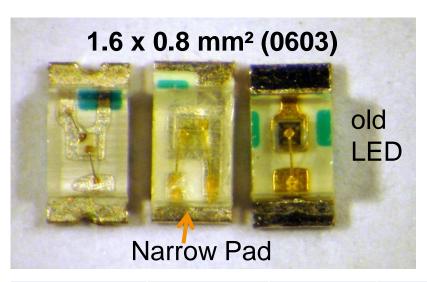

- UV LEDs of calibration system obsolete => redesign.

- Two new LED types have been investigated:

Uni Wuppertal, DESY

|                  | Wavelength [nm] | Pulse width FWHM [ns] | •   |

|------------------|-----------------|-----------------------|-----|

| Ledtronics (old) | 395             | ~7                    | 6.3 |

| WEMU             | 420             | ~7                    | 6.1 |

| Lighthouse       | 400             | ~9                    | 5.1 |

Lighthouse LED will be used!

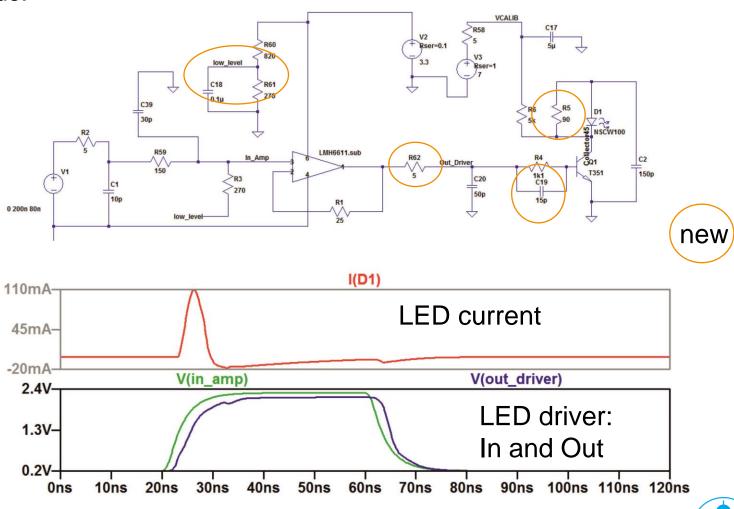

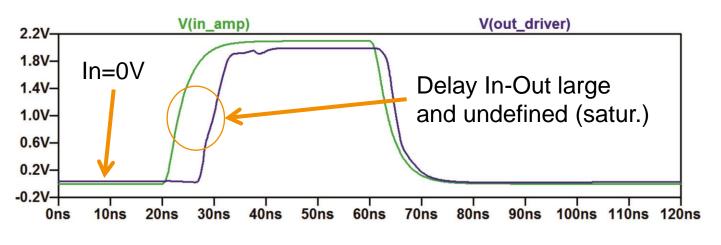

#### **LED driver circuit – SPICE simulation**

Goal: Improve Channel-to-channel uniformity: LED pulse delay and amplitude.

## **LED driver – input bias**

LED driver modified in HBU3 accordingly. Can we use LED system for TDC calibration now?

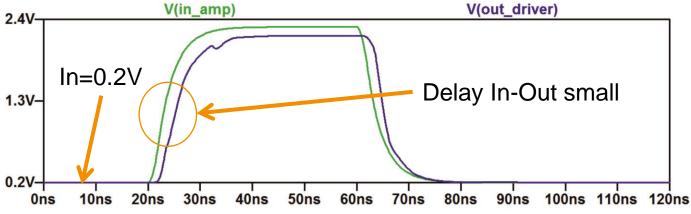

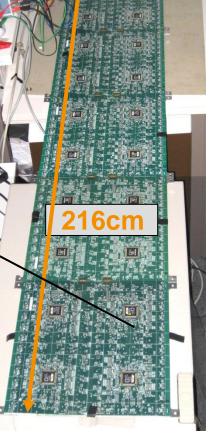

## Full extension: Test of 6 HBU2s in a Row

6 HBU2s with 864 detector channels in lab (Sept. 2013).

Questions: Transport of 40MHz LVDS clocks, power, LED trigger over 216cm possible without limitations of detector performance?

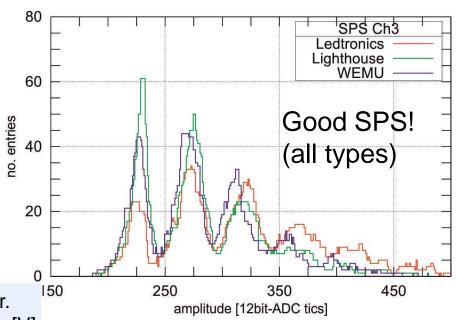

First results for smallest signals (single-pixel spectra of SiPMs) prove the suitability of the setup:

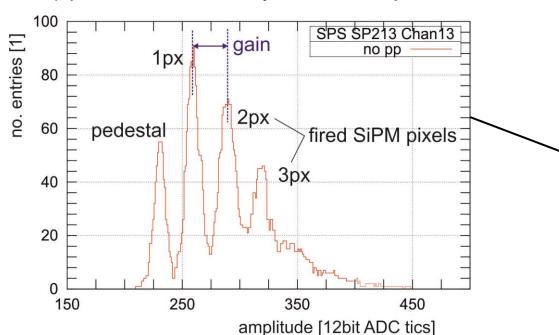

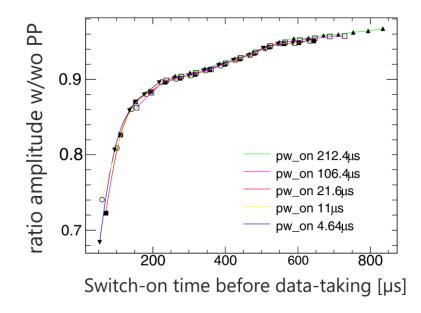

## **Full extension: Power Pulsing**

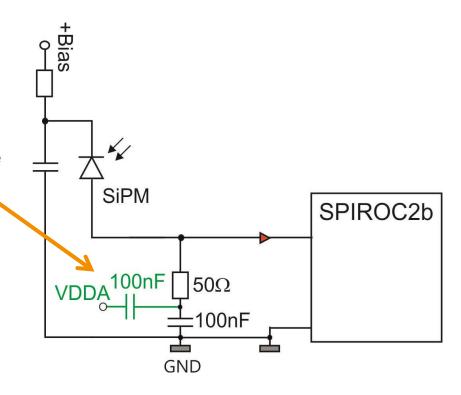

- Switched Current: 2.75A (analog supply voltage VDDA).

- Voltage drop across 216cm (dominated by flexleads):

- 0.18V on VDDA (19m $\Omega$  per HBU2+flexlead)

- 0.04V on GND (4m $\Omega$  per HBU2+flexlead)

- Quite 9000, however... Tradeoff needed: switch-on time – blocking caps:

Switch-on time T\_on too small: Low gain and high noise!

# HBU3 redesign – changes to HBU2

- New LEDs

- > 2mF additional block capacitors VDDA-GND (40 capacitors per HBU).

- > Termination of SiPMs to VDDA. Same for SPIROC bias references.

- VDDA/GND pads next to flexconnectors.

- LED trigger: line lengths equilization.

- LED driver circuit optimization.

- Remaining 960 SPIROC2b have been sent for packaging.

HBU3 redesign completed. Board can be ordered now.

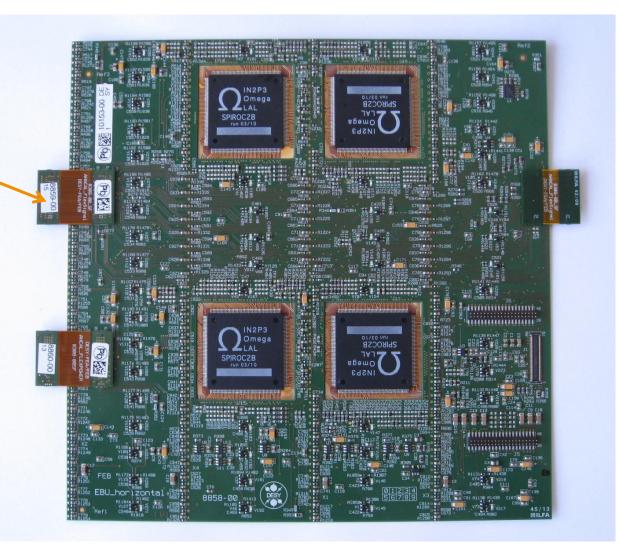

# EBU\_horizontal / Long Flexleads

- 4 EBUs realized.

- Horizontal strip orientation.

- Long flexleads realized for EBU interconnection.

- Survived smoke test (pedestal readout).

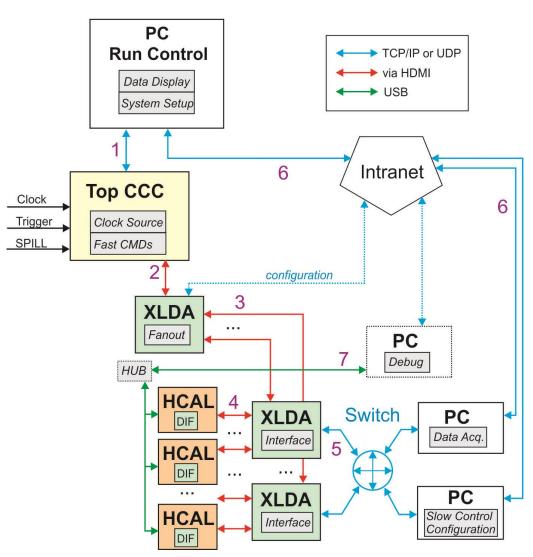

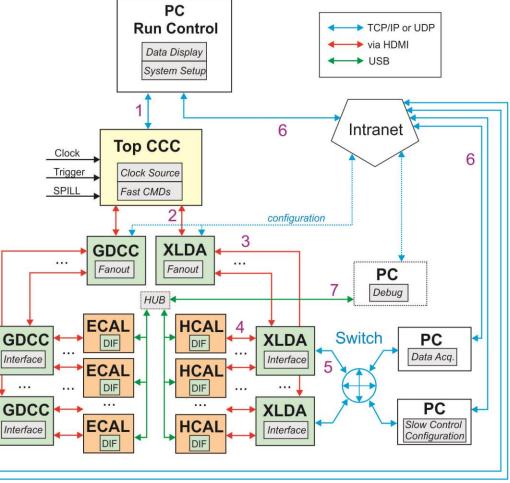

## **AHCAL DAQ proposal**

- Coorporation Uni Mainz and DESY.

- Can operate ScECAL directly.

- CCC and x-LDA based on Zedboards (Xilinx Zynq).

- includes Wing-LDA from Mainz (96 layers)

- Still in conceptional design phase. Currently implementing block-transfer commands via HDMI into DIF.

- First "operation": October CERN testbeam.

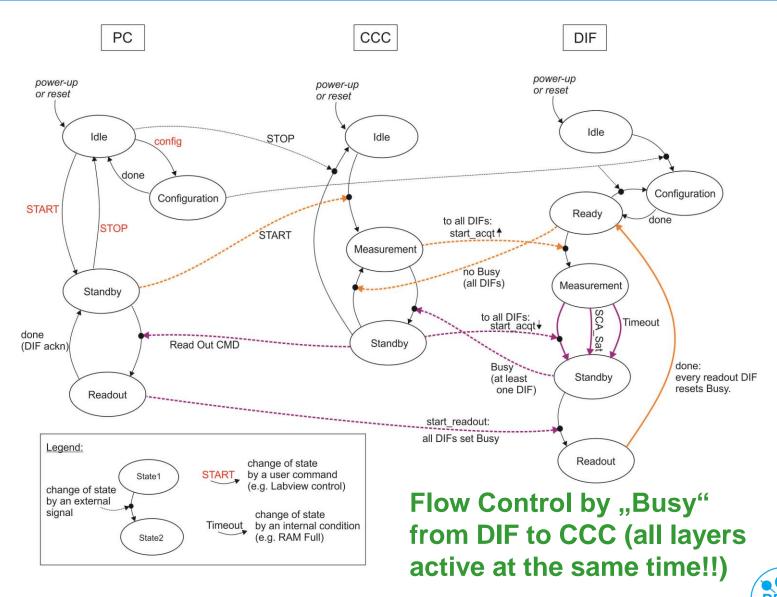

## Flow Control proposal

## Combined testbeam with other CALICE detectors

Switch

PC

Data Acq.

PC

Slow Control

Configuration

Independent operation of all detectors possible.

Easy switching: stand-alonecombined testbeam.

Various operation modes under discussion (see Taikan's talk).

Manual in preparation (to be sent around soon).

## **Outlook**

- > HBU3 and testbeam extenders ready for ordering.

- > DAQ under development in order to replace USB completely.

- New LEDs have been ordered and need to be turned over in reel.

- Temperature readout problem has been fixed (CALIB2 board).

# Backup Slides

#### **Towards the next SPIROC**

#### Topics to keep in mind ...

- Pedestal shift when too many channels have a high signal.

- Memory cell dependent amplitude decay. Solved by compensation caps.

- Slow-Control configuration is problematic for long slabs.

- > Feedback of channel-wise trigger thresholds on the global threshold.

- Random zero events and zero-results for the first trigger.

- Poor uniformity of the input DACs.

- Holdscan is different for HG/LG.

- Trigger threshold width increases with threshold height.

- Amplitude-to-threshold relation depends on preamp. setting and pulse shape.

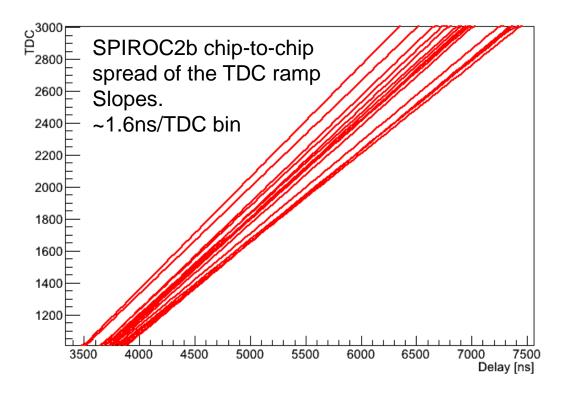

- > TDC: Amplitude dependent time-shifts and channel-to-channel spread.

- TDC: Result depends on which ramp is used and the memory cell.

- TDC: big chip-to-chip spread of ramp slopes.

## **Power and Power Pulsing (PP)**

- Aim: Switch on as short as possible before data taking starts (initial idea: 20µs).

- Results with charge injection show a decreased amplitude response with PP.

- Single-Pixel Spectra measurements show a reduced amplitude with PP.

- Aimed power dissipation of 20µW per channel not reached yet.

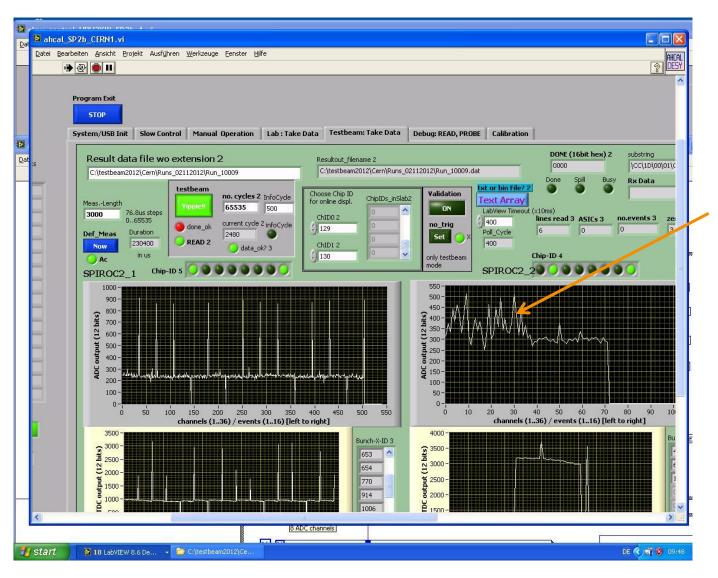

## **TDC Calibration – CERN Module**

- Calibration of all 16 SPIROC2b ASICs of the CERN Testbeam-module with charge injection.

- Chip-to\_chip spread of the TDC ramp slopes: Calibration necessary: TDC (time measurement!).

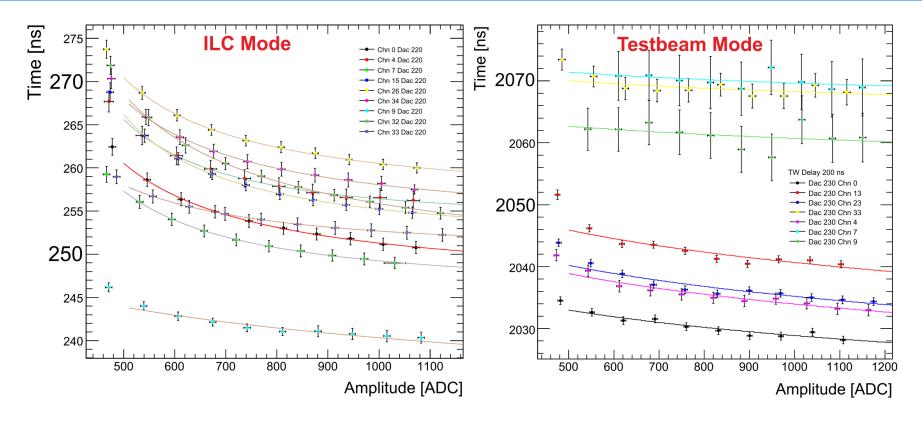

## **TDC: Time Walk and Channel-to-Channel Spread**

- > Amplitude-dependent time-shifts and channel-to-channel differences.

- Difficult to parameterize because of different behaviours. Channel-wise TDC calibration necessary as for ADC (MIP calibration)?

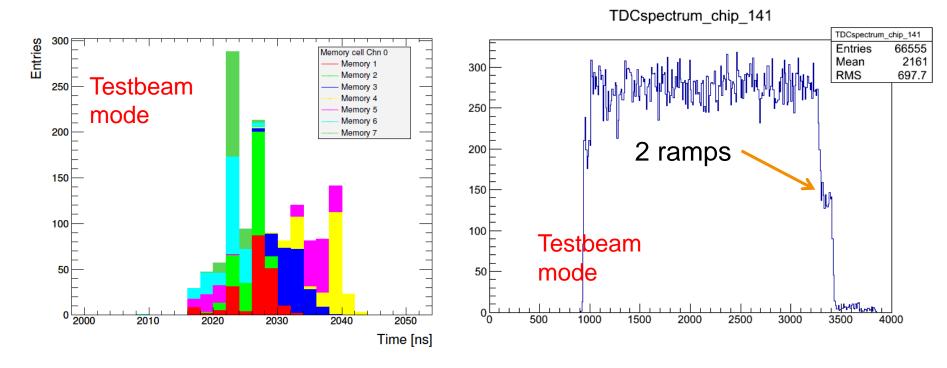

## TDC: Memory Cell Dependence and "2-Ramp" Problem

- TDC result depends on memory cell

- The SPIROC2b internal TDC ramps have different amplitudes and for a specific event it cannot be identified with which ramp the TDC result has been achieved (known problems).

#### **Start-Run Problem**

CERN testbeam

High noise on pedestal for first 1-2 readout cycles

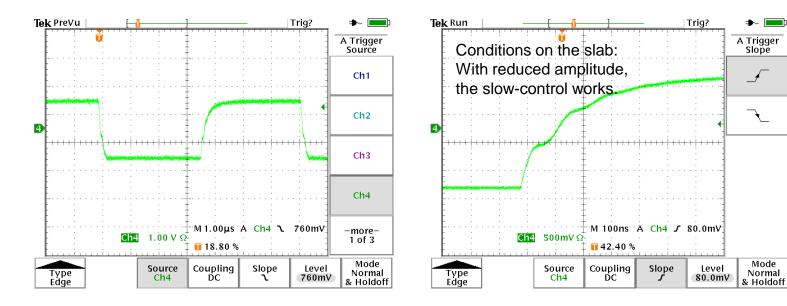

#### **Slow-Control Problem**

For longer AHCAL slabs, the slow-control programming is instable. Reason:

Slow-control clock, special pulse-shape needed (series R, termination R, block-C)

- Although the slow-clock looks fine, the configuration does not work.

- Analysis ongoing, I2C in SPIROC3.