# SDHCAL Overview

Mary-Cruz Fouz, Imad Laktineh, CIEMAT IPN-Lyon

For the GRPC SDHCAL group

# Outline

- √ Chambers

- √ Electronics

- √ Mechanics

- ✓ Conclusions

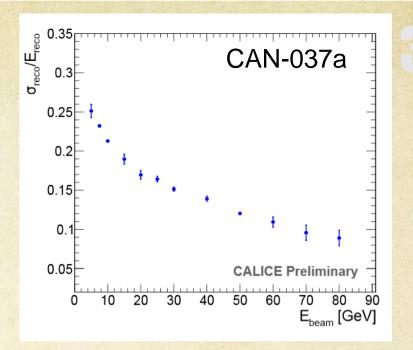

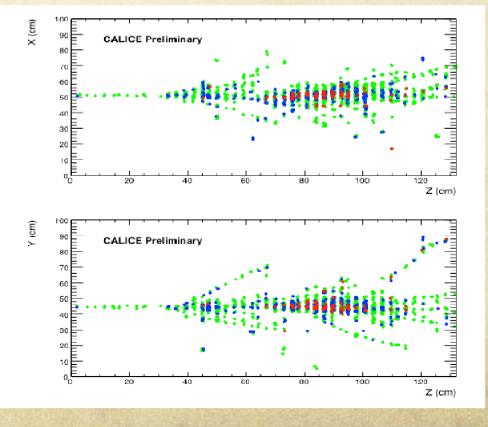

## 1m<sup>3</sup> prototype

#### SDHCAL RPC (50 units)

- → Large detectors: 100X100 cm<sup>2</sup> RPC

- → Electronics : HARDROC, embedded

- → Readout : one side of the 1m<sup>2</sup>

- → Cassette design : ok, part of the absorber

- → DAQ : ok, not the final

## Chambers

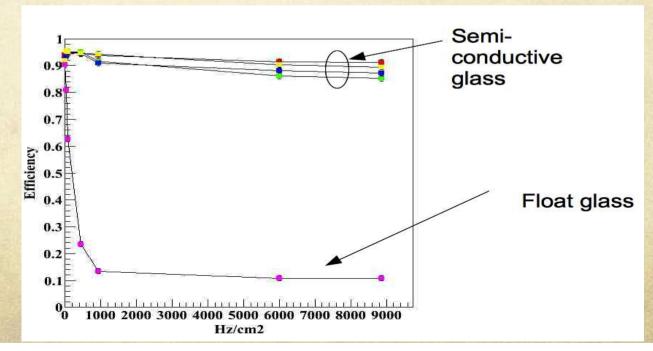

#### High-Rate GRPC

High-Rate GRPC may be needed in the very forward region

✓ Semi-conductive glass (10¹⁰ Ω.cm) produced by our collaborators from Tsinghua University was used to build few chambers.

✓ 4 chambers were tested at DESY as well as standard GRPC (float glass)

Performance is found to be excellent at high rate for GRPCs with the semiconductive glass and can be used in the very forward of ILD region if the rate exceeds 100 Hz/cm² in future ILD upgrades as well as for CLIC

CALICE meeting, Argonne March 2014

#### Large GRPC for ILD model:

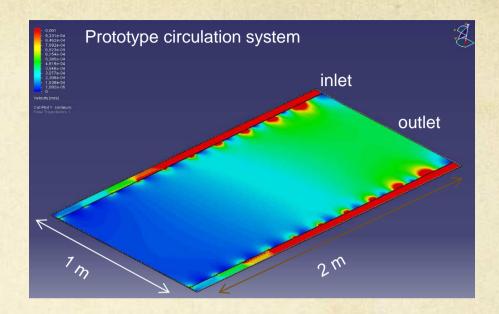

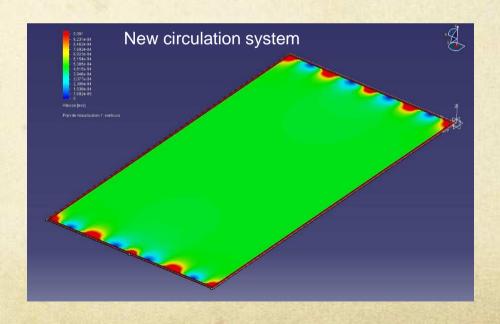

GRPC with a surface ≤ 3 m<sup>2</sup> are needed.

We intend to build a 2m<sup>2</sup> GRPC.

We are currently studying the gas distribution system to ensure a good gas renewal.

Once the first large detector is built the gas circulation of the new scheme will be controlled using radioactive 183mKr

# Electronics

#### HARDROC3

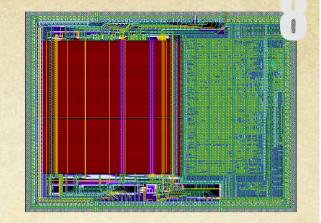

This new version of the HARDROC ASIC has:

- -64 independent channels, zero suppression

- -I2C link

- -PLL: Input frequency 2.5 MHz =>output frequency: 10, 20, 40, and 80 MHz

Bandgap: new one with a better temperature sensitivity

Triple voting

Roll mode

Temperature sensor: tested in a building block, slope – 6mV/°C

Die size ~30 mm2 (6.3 x 4.7 mm2)

Packaged in a TQFP208

The ASIC was produced and tested. All functionalities were successfully tested.

A minor problem was found with the I2C scheme (buffer stuck to zero)

This I2C was however successfully tested after a BIF.

See Hadroc3 talk by Frederic Dulucq

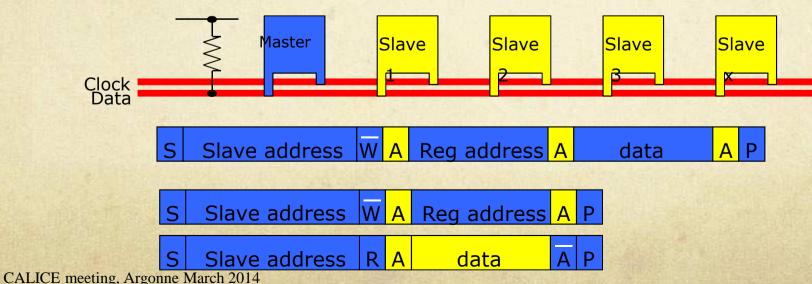

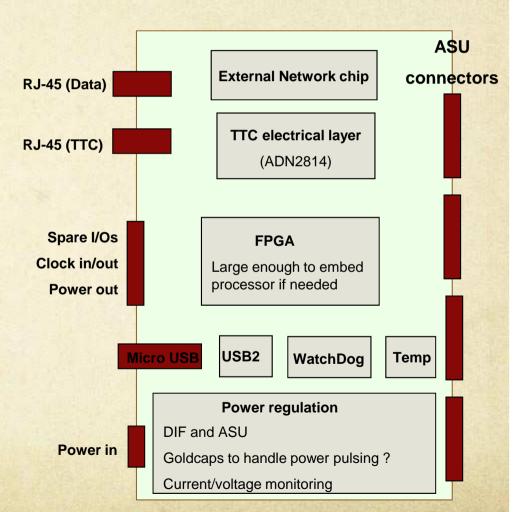

## New SDHCAL DIF main features

- Only one DIF per plane. For the maximum length plane (1x3m) the DIF will handle 432 HR3 chips

- Slow control through the new HR3 I2C bus

- Data transmission to DAQ by Ethernet using commercial switches for concentration

- Clock and synchronization by TTC

- USB 2.0 for debugging

Synergy with R&D on fast links R&D of LHC(GBT)

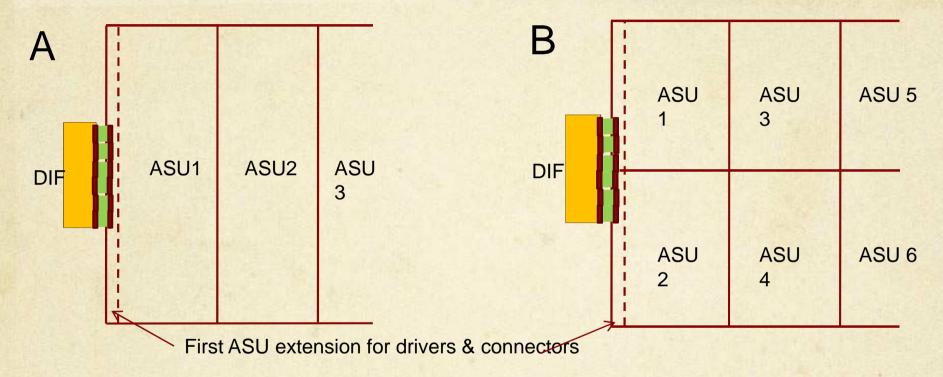

## New ASU layout options

As there will be only one DIF per plane, the distribution of the ASU boards in the plane will be rearranged to reduce the number of conections between the DIF and the plane

- In option B the common signals for the plane have to be sent twice (one per slab) while in option B they can be sent only once

- But, option A looks more risky from the point of view of the feasibility of the 1m long ASU boards.

- In both options the ASUs connected to the DIF will be a bit longer to host the connectors and the buffers for driving the long lines. This extension provides more freedom for the connectors selection and moves the drivers heat disipation to the ventilation area

## Mechanics

### From the 1m<sup>3</sup> mechanic structure to the final one

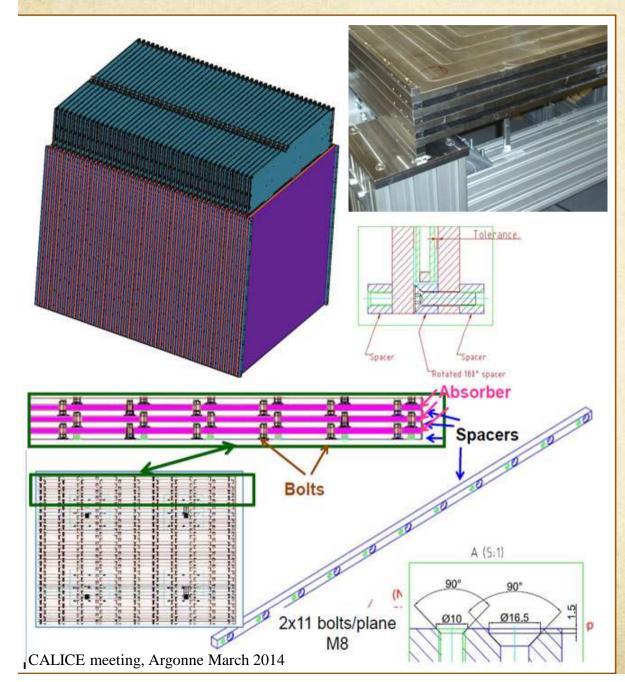

The 1m³ mechanical structure was made of 51 stainless steel plates assembled together using lateral spacers fixed to the absorbers through staggered bolts.

Thickness tolerance 0.05mm

Surface planarity < 0.5 mm

→ < 1mm for the big plates

For the final structure

→ Welding instead of bolts

Allows to decrease the lateral size of the spacer

→ Less dead zone

Could introduce deformations

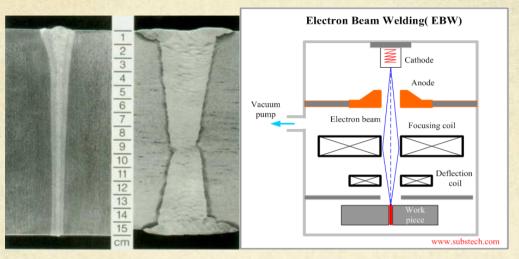

## Welding

#### Standard welding:

Could introduce deformations

#### **Electron beam welding:**

The best but need vacuum conditions and could be not affordable for big modules

#### Laser welding:

Could have reasonable deformations and is easier (and cheaper) than electron beam welding

### Planned tests

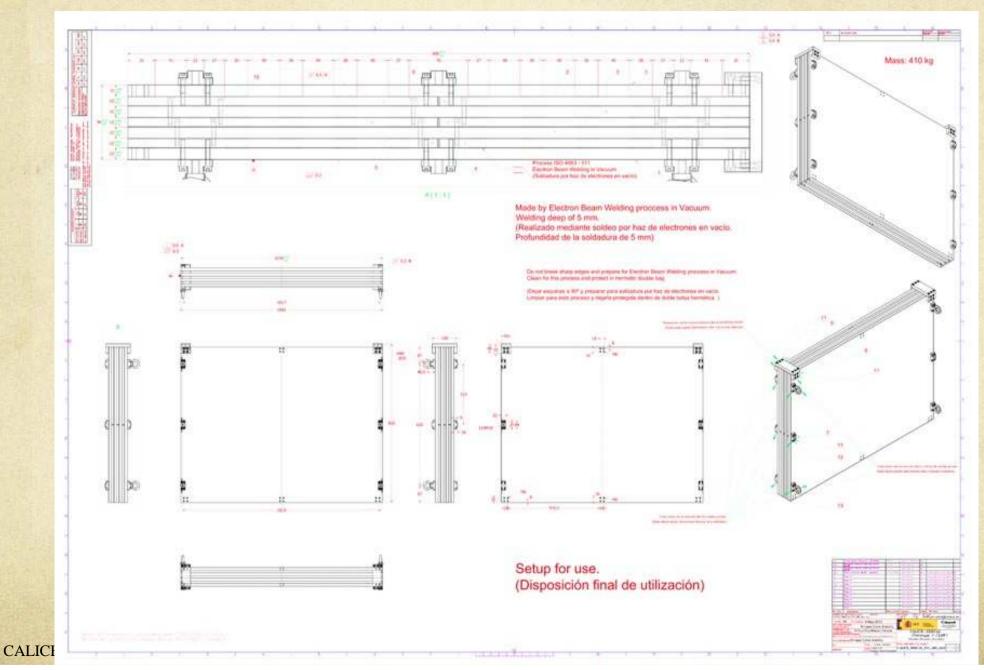

#### → Tests with small prototypes

Width of plates = 15mm

Few plates of 1x 0.80 m<sup>2</sup> welded by electron beam welding (EBW) process in vacuum at CERN.

Few plates of 1x 0.40m<sup>2</sup> with standard welding at CIEMAT trying to see if it's possible to find methods for optimizing the procedure and minimizing the eventual deformations

Depending on the results from those tests -> Laser welding test will be considered

#### → Test with a prototype with large plates

Assembly of a prototype with 4-5 plates with the largest dimensions (3 x 0.80 m<sup>2</sup>) of an ILD SHDCAL module

It will be equipped with some large GRPC chambers and its new electronics

## 15

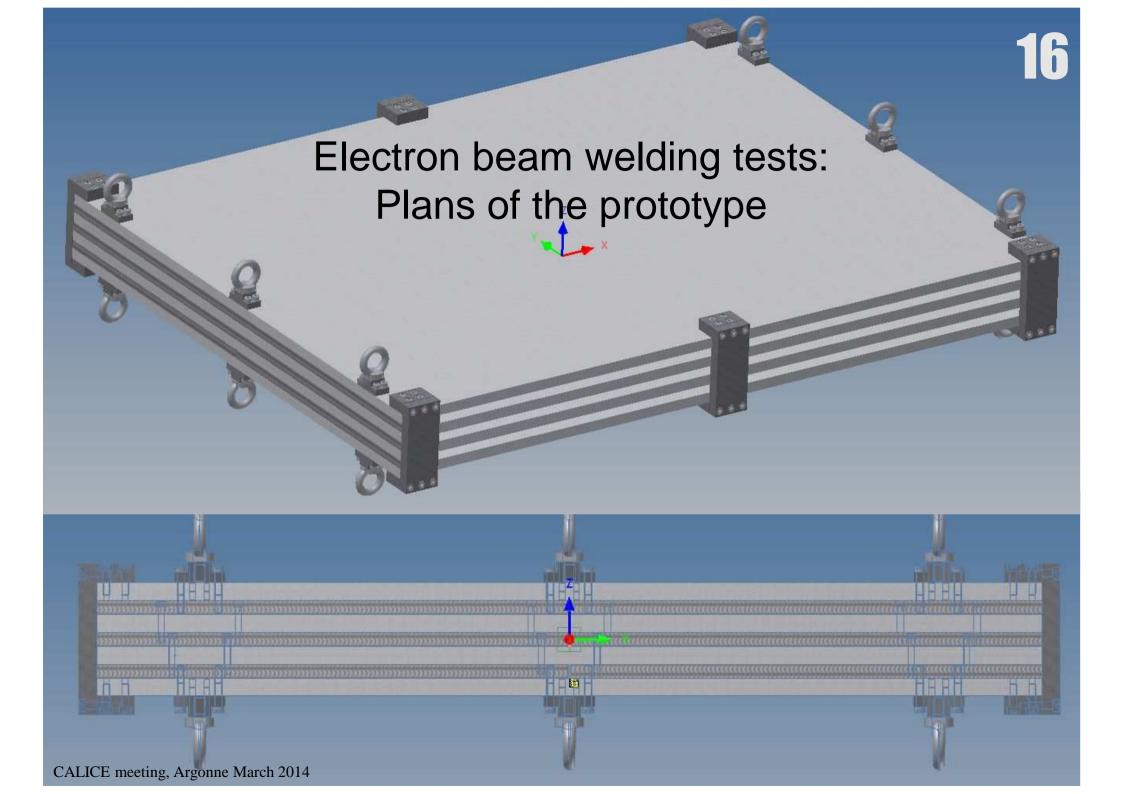

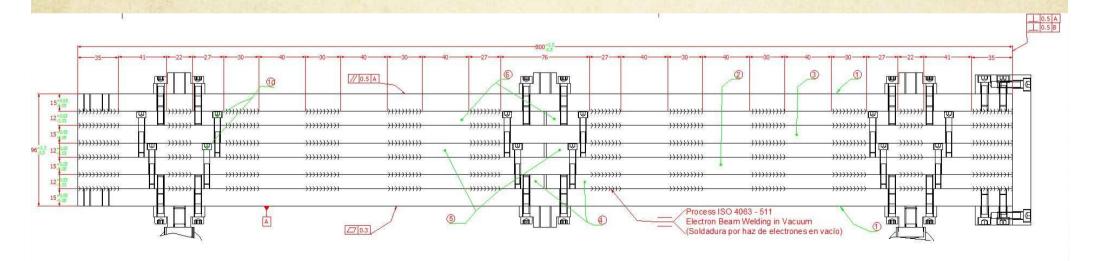

# Electron beam welding tests: Plans of the prototype

# Electron beam welding tests: Welding details

Welding techniques

Made by Electron Beam Welding process in Vacuum. Welding deep of 5 mm.

## 18

# Electron beam welding tests: Plate machining and verification

CALICE meeting, Argonne March 2014

## Large plates prototype

ongoing

## Conclusions

Very large detectors are being conceived and will be shortly build

New **electronics** being developed (**chip** and **readout**)

New mechanic design using welding

- → Preparation for tests is ongoing

- → A mechanical structure with 4-5 large plates is foreseen.