# Status and perspectives of Deep N-Well CMOS MAPS for the ILC Vertex Detector

Valerio Re Università di Bergamo and INFN - Pavia

International Linear Collider Workshop 2008

16-20 November 2008

Chicago, IL

#### **Outline**

- The first generation of Deep N-Well (DNW) MAPS with on-pixel data sparsification and time stamping, tested in a beam for the first time in September 2008

- ILC-class and SuperB-class 130nm DNW CMOS MAPS with different pixel pitch, analog signal processing and digital readout architecture

- The way forward to use DNW MAPS in actual experiments

- Impact of new technologies on the performance of DNW-MAPS

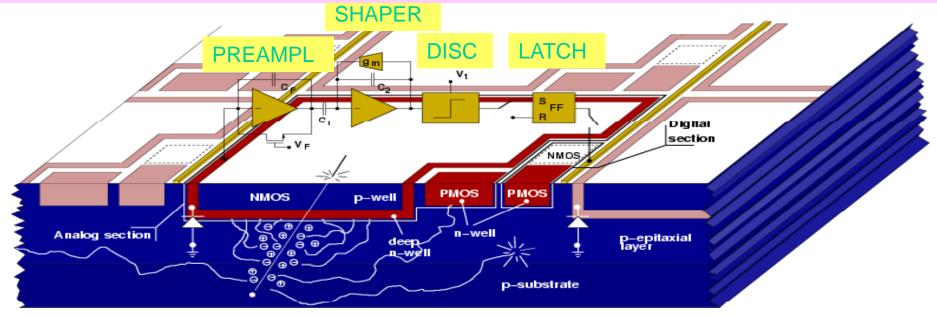

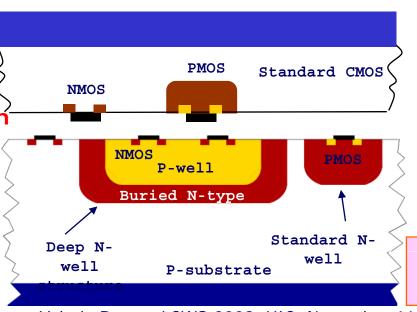

#### Deep N-Well (DNW) sensor concept

New approach in CMOS MAPS design compatible with data sparsification architecture to improve the readout speed potential

Classical optimum signal processing chain for capacitive detector can be implemented at pixel level:

- Charge-to-Voltage conversion done by the charge preamplifier

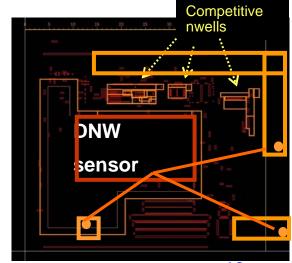

- The collecting electrode (Deep N-Well) can be extended to obtain higher single pixel collected charge (the gain does NOT depend on the sensor capacitance), reducing charge loss to competitive N-wells where PMOSFETs are located

- Fill factor = DNW/total n-well area ~90% in the prototype test structures

Valerio Re LCWS 2008, UIC, November 16-20, 2008

## After 5 years of R&D....

130 nm DNW MAPS: first generation of CMOS sensors with in-pixel sparsification and time stamping (130 nm STM CMOS process)

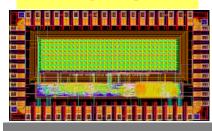

#### **APSEL3D**

8x32 matrix.

Shielded pixel

Data Driven

sparsified readout

#### **APSEL4D**

32x128 matrix.

Data Driven,

continuously operating

sparsified readout

Beam test Sep. 2008

#### **SDRO**

16x16 matrix + smaller test structures. Intertrain sparsified readout

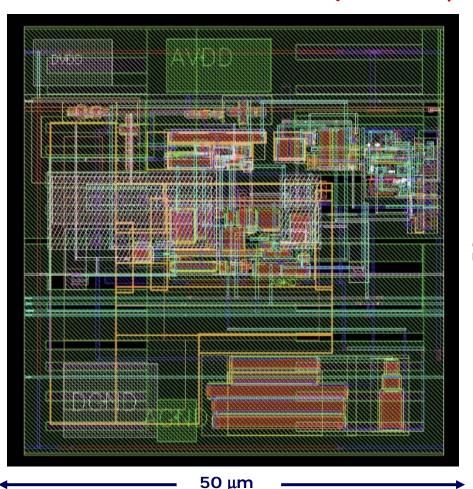

50x50 μm pitch

25x25 μm pitch

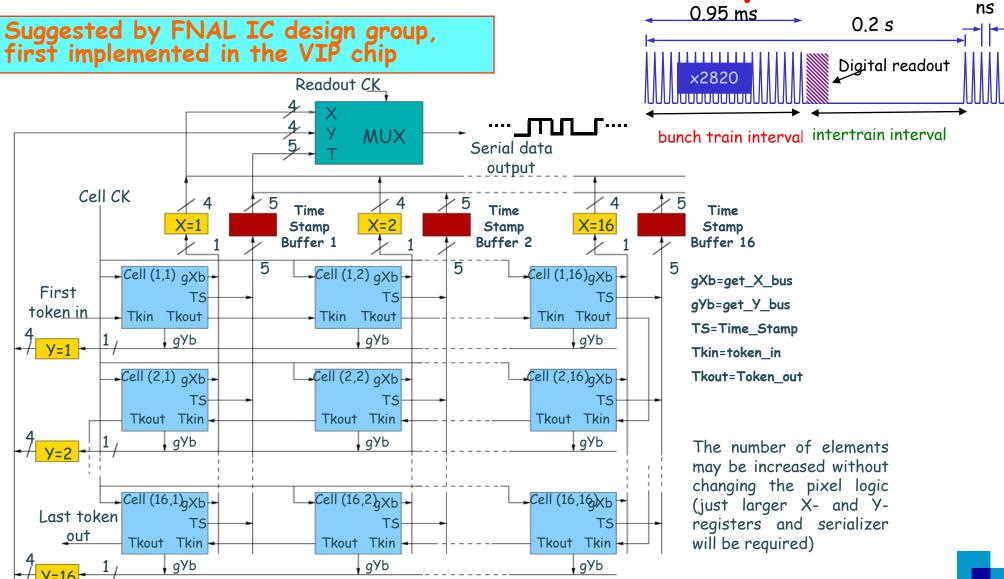

### Intertrain Readout Architecture for "ILC" MAPS (SDRO chip)

Valerio Re - LCWS 2008, UIC, November 16-20, 2008

5

337

## Two versions of the analog section for different pixel pitch

#### **APSEL (SuperB VTX Layer0)**

Preamplifier RC-CR Shaper

V F

Gm

C 2

C 2

C 2

C 2

C 2

C 2

C 3

C 4

C 4

C 5

C 1

High impedance node

VDD

Vth

- Pixel cell: 50x50 μm²

- Sensor capacitance: 400 fF

- Power dissipation: 30 μW

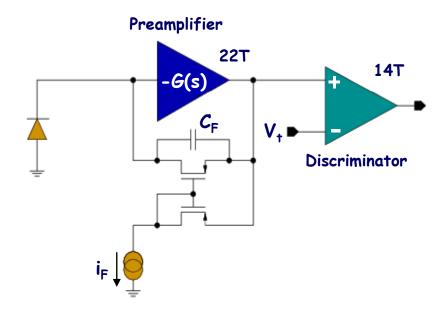

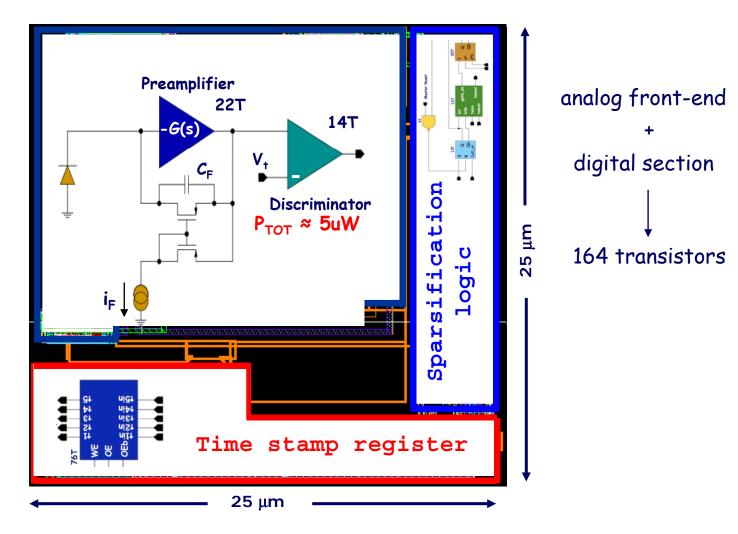

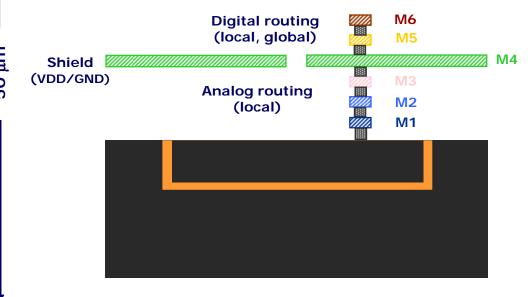

SDRO (ILC VTX)

- Pixel cell: 25x25 μm<sup>2</sup>

- Sensor capacitance: 150 fF

- Power dissipation:  $5 \mu W$

## The SDRO pixel

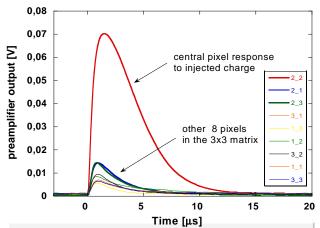

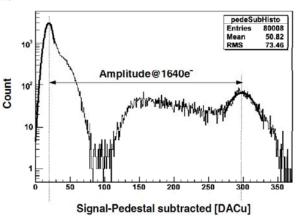

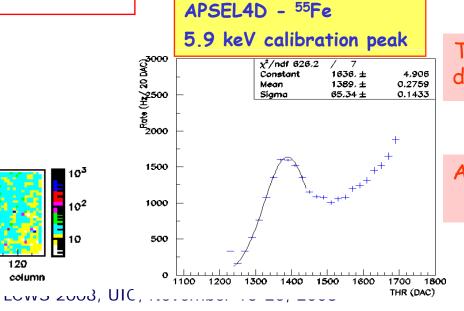

## SDRO performance

SDR0 - 16x16 pixels 25  $\mu$ m pixel pitch

- Average charge sensitivity ≈ 0.7 V/fC

- ENC = 40 e rms @  $C_D$ =120 fF (preamplifier input device:  $I_D$  = 1  $\mu$ A, W/L = 22/0.25)

- Threshold dispersion ≈ 60 e

##

#### Test with 55Fe

#### Digital readout is working fine

Valerio Re - LCWS 2008, UIC, November 16-20, 2008

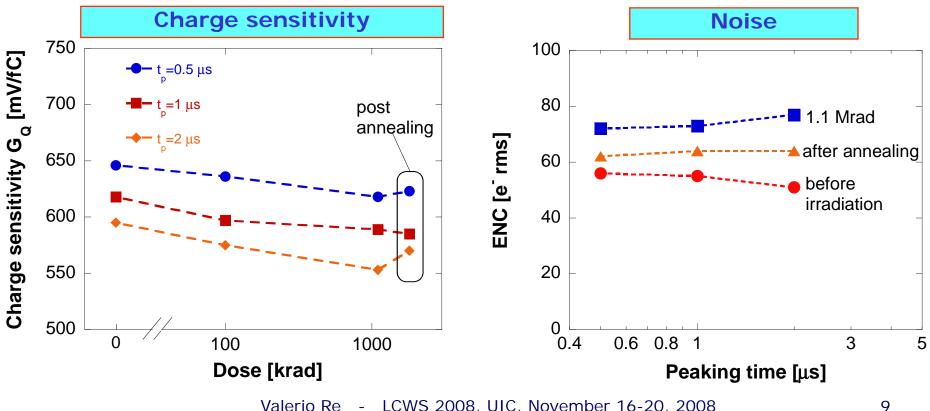

#### Radiation hardness

- Radiation tests on prototypes (APSEL chips) show that DNW MAPS sensors are rad-hard at ILC total dose levels (1 Mrad), even without any rad-tolerant design trick

- At these TID levels, sensor leakage current is still not a problem; radiation effects are associated to thick oxides (field oxide, STI)

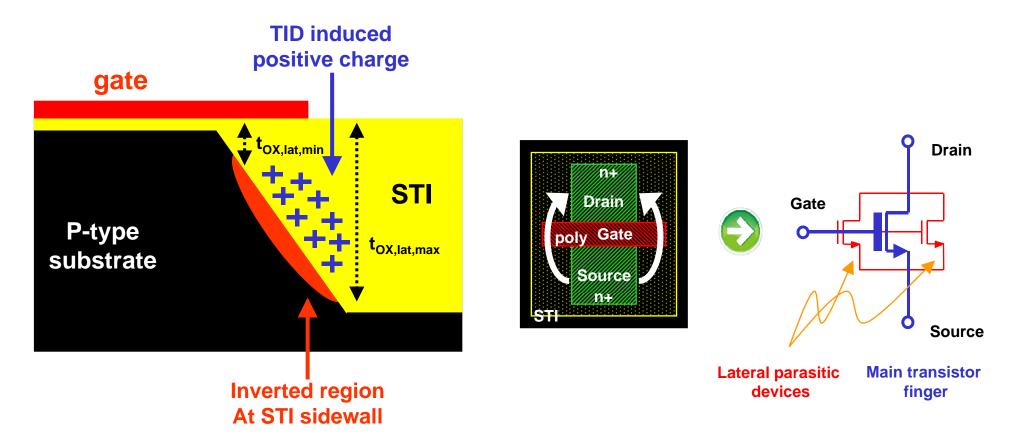

#### Ionizing radiation effects on lateral isolation oxides

> Besides affecting static characteristics and leakage currents and lateral transistors are noisy as the main MOSFET device

#### SLIM5 Beam test

Valerio Re - LCWS 2008, UIC, November 16-20, 2008

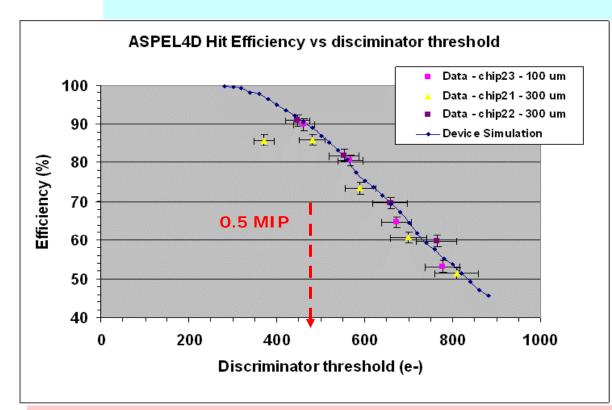

## DNW MAPS Hit Efficiency measured in a beam test (APSEL4D)

Measured with tracks reconstructed with the reference telescope extrapolated on MAPS matrix

MAPS hit efficiency up to 90 % with threshold @ 450 e- (~  $4\sigma$ \_noise+ $2\sigma$ \_thr\_disp) 300 and 100  $\mu$ m thick chips give similar results

- Competitive N-wells (PMOS) in pixel cell can steal charge reducing the hit efficiency

- Fill factor DNW/total N-well area ~ 90 % in present design

- Room for improvements with a different design of the sensor (multiple collecting electrodes around competitive N-wells)

## Detection efficiency and charge collection

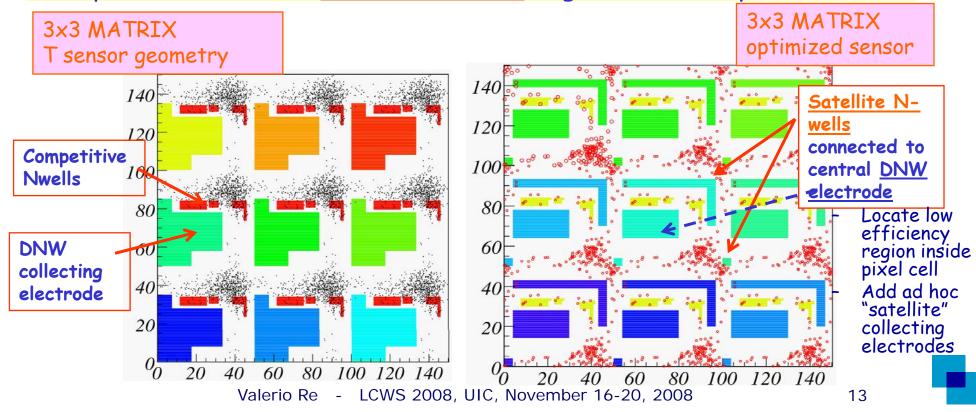

- Beam test results of APSEL4D show a ~90% efficiency, which agrees very well with TCAD simulations

- With APSEL4D sensor geometry (left), Efficiency ~ 93.5% from simulation (pixel threshold @ 250 e- = 5xNoise)

- Inefficient regions shown with dots (pixel signal < 250 e-)</li>

- Optimized cell with <u>satellite N-wells</u> (right) Efficiency ~ 99.5%

## The way forward

Next generation of DNW MAPS has to provide devices that approach actual experiment specifications more closely

Several issues have to be addressed to meet ILC Vertex Detector specifications (pixel pitch, detection efficiency):

- Binary readout: ILC VTX demands a pixel pitch < 20  $\mu$ m to achieve required single point resolution < 5  $\mu$ m.

- Detection efficiency does not meet requirements (> 99 %) because of competitive n-wells (PMOS) decreasing the fill factor

- Capability of handling multiple pixel hits has to be included without degrading efficiency and pitch

- Two different ways to approach this goal:

- 1) A gradual performance improvement

- ⇒ better sensor layout, optimize interconnections and pixel cell ⇒ SuperB LayerO test module

- 2) A technology leap

- ⇒ Vertical integration

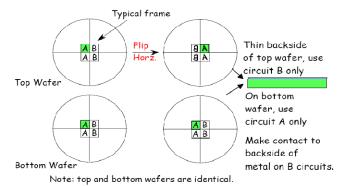

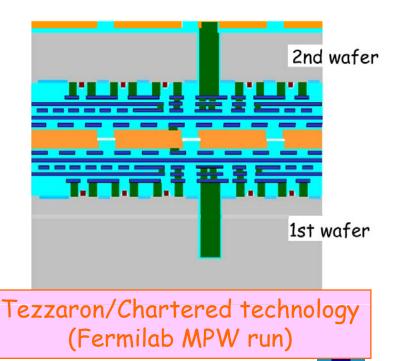

#### 3D vertical integration and DNW MAPS

Use vertical integration technology to interconnect two 130nm CMOS layers

Overcome limitations typically associated to "conventional" and DNW CMOS MAPS:

- Reduced pixel pitch

- 100 % fill factor (few or no PMOS in the sensor layer, no competitive N-wells)

- Better S/N vs power dissipation (smaller sensor capacitance)

- Increased pixel functionalities

Mostly digital CMOS tier

Tier interconnection

and vias

Analog and sensor CMOS (mostly NMOS) tier

Face to Face Bonding

#### The Italian VIPIX collaboration

- "Pixel systems for thin charged particle trackers based on vertical integration technologies" - VIPIX (INFN Pisa, Pavia, Bologna, Trieste, Trento, Perugia, Roma3, Torino)

- Members of the CMOS-3DIT Consortium (FNAL-IN2P3-INFN)

- 1. Interconnection between 2 (or more) CMOS layers, one layer with a MAPS (DNW) device and analog front-end, and the other layer(s) with the digital readout

- 2. Interconnection between a CMOS readout electronics chip (2D or 3D) and a fully-depleted high resistivity sensor

- a) with bump bonding (standard, but low pitch may be needed)

- b) with a vertical integration technique (low material budget, more advanced)

#### Conclusions

- After several years of R&D, Deep N-Well monolithic active pixel sensors are reaching a good maturity level, but there is room for substantial improvements

- The performance of DNW MAPS needs to be upgraded if they have to fulfill ILC specifications

- DNW MAPS can benefit from technological advances

## Acknowledgments

## SLIM5-Silicon detectors with Low Interactions with Material

- G. Batignani<sup>1,2</sup>, S. Bettarini<sup>1,2</sup>, F. Bosi<sup>1,2</sup>, G. Calderini<sup>1,2</sup>, R. Cenci<sup>1,2</sup>, M. Dell'Orso<sup>1,2</sup>, F. Forti<sup>1,2</sup>, P.Giannetti<sup>1,2</sup>, M. A. Giorgi<sup>1,2</sup>, A. Lusiani<sup>2,3</sup>, G. Marchiori<sup>1,2</sup>, F. Morsani<sup>2</sup>, N. Neri<sup>2</sup>, E. Paoloni<sup>1,2</sup>, G. Rizzo<sup>1,2</sup>, J. Walsh<sup>2</sup>

- C. Andreoli<sup>4,5</sup>, E. Pozzati<sup>4,5</sup>, L. Ratti<sup>4,5</sup>, V. Speziali<sup>4,5</sup>, M. Manghisoni<sup>5,6</sup>, V. Re<sup>5,6</sup>, G. Traversi<sup>5,6</sup>, L.Gaioni<sup>4,5</sup>

- L. Bosisio<sup>7</sup>, G. Giacomini<sup>7</sup>, L. Lanceri<sup>7</sup>, I. Rachevskaia<sup>7</sup>, L. Vitale<sup>7</sup>,

- M. Bruschi<sup>8</sup>, B. Giacobbe<sup>8</sup>, A. Gabrielli<sup>8</sup>, N. Semprini<sup>8</sup>, R. Spighi<sup>8</sup>, M. Villa<sup>8</sup>, A. Zoccoli<sup>8</sup>,

D. Gamba<sup>9</sup>, G. Giraudo<sup>9</sup>, P. Mereu<sup>9</sup>,

G.F. Dalla Betta<sup>10</sup>, G. Soncini<sup>10</sup>, G. Fontana<sup>10</sup>, L. Pancheri<sup>10</sup>, G. Verzellesi<sup>11</sup>

<sup>1</sup>Università degli Studi di Pisa, <sup>2</sup>INFN Pisa, <sup>3</sup>Scuola Normale Superiore di Pisa,

<sup>4</sup>Università degli Studi di Pavia, <sup>5</sup>INFN Pavia,

<sup>6</sup>Università degli Studi di Bergamo,

<sup>7</sup>INFN Trieste and Università degli Studi di Trieste

<sup>8</sup>INFN Bologna and Università degli Studi di Bologna

<sup>9</sup>INFN Torino and Università degli Studi di Torino

<sup>10</sup>Università degli Studi di Trento and INFN Padova

<sup>11</sup>Università degli Studi di Modena e Reggio Emilia and INFN Padova

#### ILC VTX - Italy

- G. Traversi<sup>a,b</sup>, A. Bulgheroni<sup>b,c</sup>, M. Caccia<sup>b,c</sup>, M. Jastrzab<sup>b,c</sup>,

- M. Manghisoni<sup>a,b</sup>, E. Pozzati<sup>b,d</sup>, L. Ratti<sup>b,d</sup>, V. Re<sup>a,b</sup>

<sup>a</sup>Università degli Studi di Bergamo

**bINFN**

<sup>c</sup>Università degli Studi dell'Insubria

<sup>d</sup>Università degli Studi di Pavia

## Backup slides

#### Design specifications for the ILC vertex detector

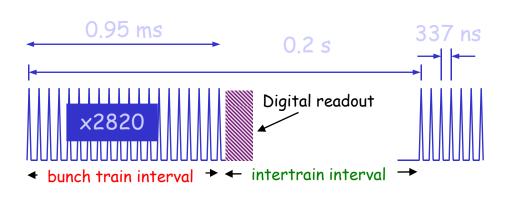

- The beam structure of ILC will feature 2820 crossings in a 1 ms bunch train, with a DC of 0.5%. Assuming:

- maximum hit occupancy 0.03 part./Xing/mm²

- > 3 pixels fire for every particle hitting  $\rightarrow$  hit rate  $\approx$  250 hits/train/mm<sup>2</sup>

- digital readout adopted: 5um resolution requires

17.3 um pixel pitch

- > 15 um pixel pitch  $\rightarrow$   $O_c \approx 0.056$  hits/train  $\rightarrow$  the probability of a pixel being hit at least twice in a bunch train period  $\approx 0.0016$   $\rightarrow$  there is no need to include a pipeline for storing more than one hit per pixel (more than 99% of events recorded without ambiguity)

- > MAPS sensor operation is tailored on the structure of ILC beam

- > Detection phase (corresponding to the bunch train interval)

- Readout phase (corresponding to the intertrain interval)

- $\succ$  Data readout in the intertrain interval  $\rightarrow$  system EMI insensitive

- > Sparsified readout based on the token passing scheme. This architecture was first implemented in the VIP1 chip (3-D MIT LL technology) by the ILC pixel design group at Fermilab

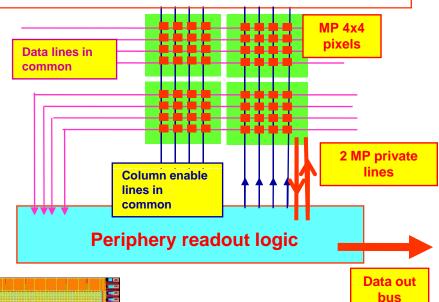

### Continuous Readout Architecture for "SuperB" MAPS (APSEL chips)

- Data-driven readout architecture with sparsification and timestamp information under development.

- In the active sensor area we need to minimize:

- the logical blocks with PMOS to minimize the competitive nwell area and preserve the collection efficiency of the DNW sensor.

- digital lines for point to point connections to allow scalability of the architecture with matrix dimensions and to reduce cross talk with the sensor underneath.

Matrix subdivided in MacroPixel (MP=4x4) with point to point connection to the periphery readout logic:

- Register hit MP & store timestamp

- Enable MP readout

- Receive, sparsify, format data to output bus

APSEL3D: 256 pixels

APSEL4D: 4k pixels

50x50 um pitch

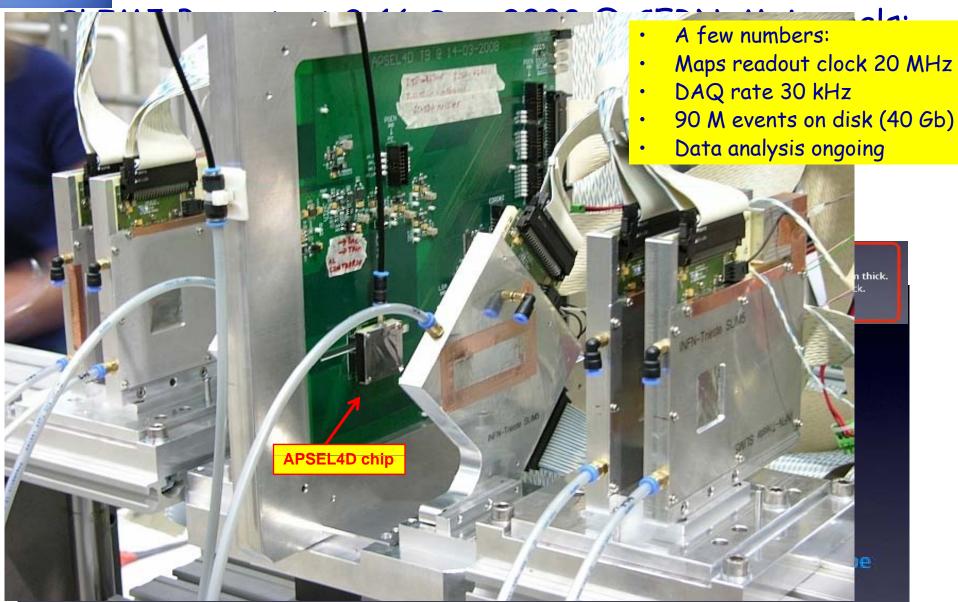

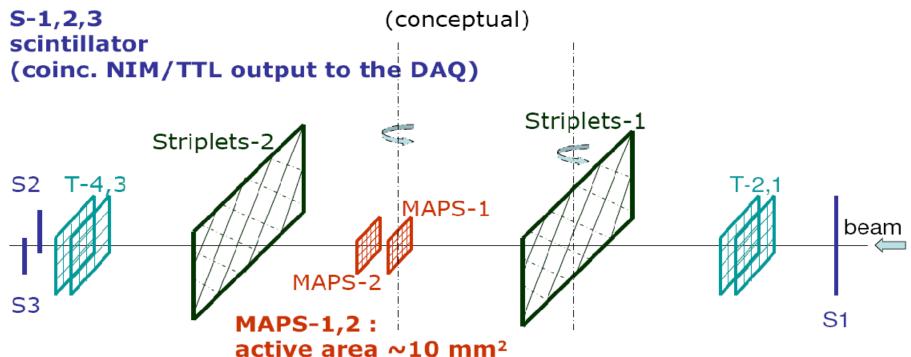

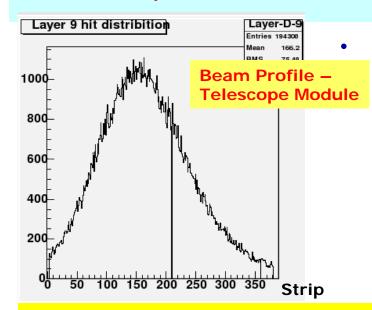

#### SLIM5 CERN beam test with APSEL4D

#### The "DEMONSTRATOR"

Cell:50x50 μm<sup>2</sup> (300→100 μm-thick)

Reference telescope T-1,2,3,4: area~2x2 cm<sup>2</sup>

DSSD 300μm thick

25 p-side, 50 n-side μm pitch

50 μm r.o. pitch

(3 chips FSSR2/side)

Striplets-1,2: area 1.29x6.0 cm<sup>2</sup> DSSD 200 $\mu$ m thick ( $\angle$ 45°) 25 p-side, 50 n-side  $\mu$ m pitch 50  $\mu$ m r.o. pitch (3 chips FSSR2/side)

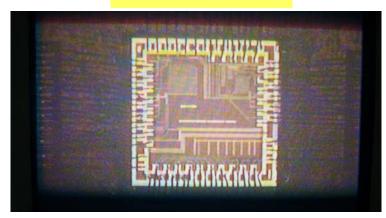

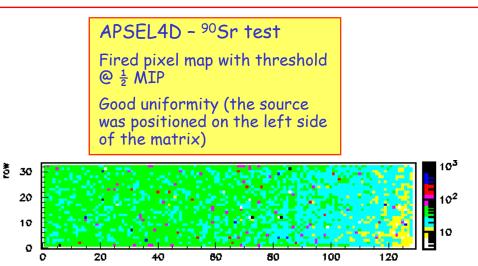

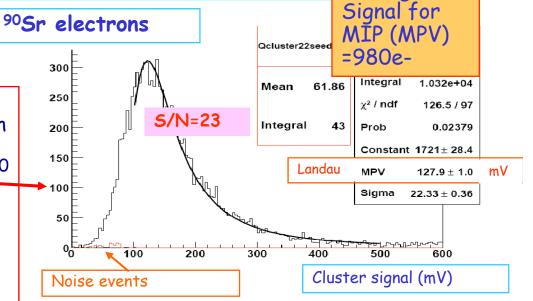

### APSEL4D performance

APSEL4D - 32x128 pixels 50  $\mu$ m pixel pitch

#### Tests of the APSEL4D chip:

- Optimization of the Deep NWell MAPS pixel with respect to previous versions

- 5/N up to 25 with reduced power consumption (~30  $\mu$ W/ch)

- Fast readout architecture (sparsification and timestamp) implemented in a 4k pixel matrix.

- Good sensitivity to e- from  $^{90}{\rm Sr}$  and to  $\gamma$  from  $^{55}{\rm Fe}$  source

- Must operate at DVDD = 1V to reduce interferences

hit-thrdac= 1900 (70 mV)

vaici io ive

Threshold dispersion = 60 e

Average

Average gain = 860 mV/fC

## The APSEL4D pixel

The sensing electrode has a T-shaped geometry, from the Deep N-Well and standard N-well extensions ( $A = 900 \mu m^2$ )

Sensor and analog lines had to be shielded from digital lines (continuous readout)

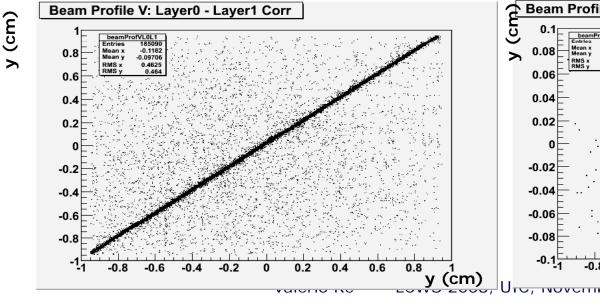

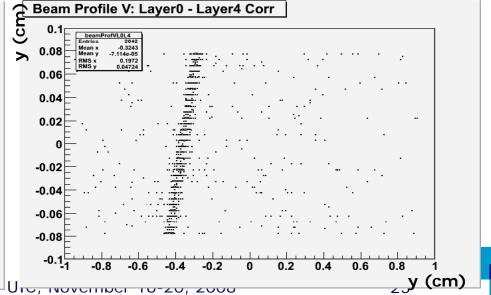

#### A first look to the CERN beam test data

Beam test started last week @ CERN (T9). Main goals:

- DNW MAPS matrix resolution & efficiency

- Thin (200 μm) striplets module with FSSR2 readout chips

- Demostrate LVL1 capability with tracker information sent to Associative Memories

- New DAQ system developed for data push architecture

Y hit correlation Telescope T2 vs T1

Y hit correlation MAPS vs Telescope T1