# New front end board for ILD Si-W ECAL

CALICE WEEK 24-26/03/2021

### Electrical long SLAB

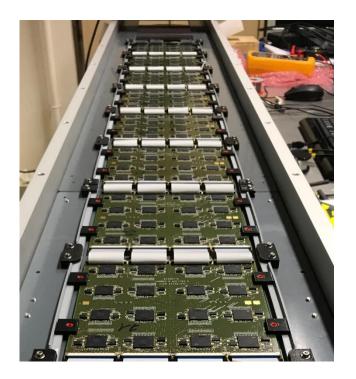

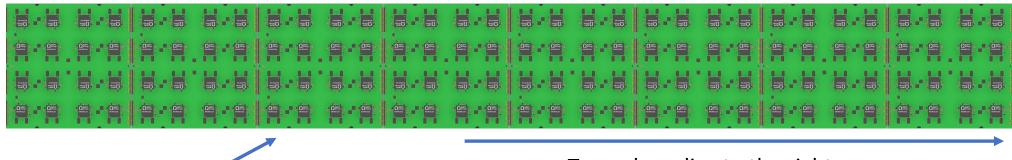

#### Success of assembly of 8 boards chained 2017-2018

- Test beam @DESY 2018

- Results (see presentation @ LCWS 2018)

Confirm measure after TB

Voltage drop cross with bandgap distribution

#### Feedback

- Important voltage drop (5%)

- Need extra electronics to configure more than 4 boards

- Need too many manipulations to move or replace board

- Mini wafers not adapted to observe cumulative effect

For final project, we need new board & new mechanics

→ Move to physics long SLAB (fully equipped of 6" Si wafers

#### **Compact Readout electronics**

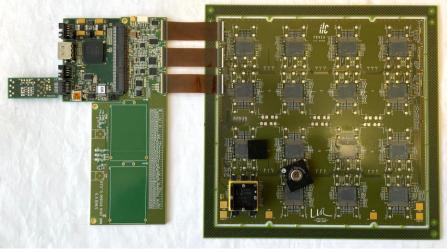

- In the last 3 years, a new compact readout electronics have been developed by IJCLab. These electronics are composed by:

- The **SL-Board** :

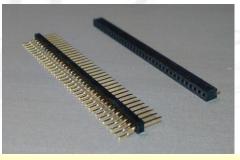

- It is interfaced to the Front-End board via flat connectors : GradConn (1,5 mm high)

- Its **size** is compatible with the final detector requirements.

- It limits the current delivered to the Slab to ~ 100 mA :

- Need capacitors on the Front-End board to store the charge during the power pulsing

- Configuration (slow control) and readout through 2 partitions ( < Fev12 like)</li>

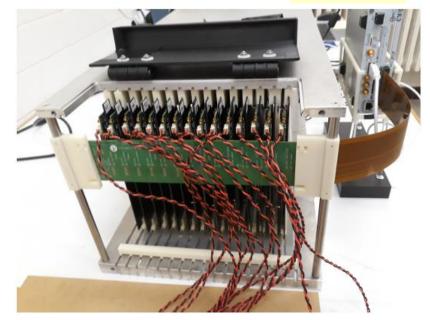

- The CORE-Kapton and CORE-Module :

- It permits to synchronise and readout up to 15 x 2 Layers (~30 k channels)

- Collaboration between IJCLab and LLR to develop a new Si-W Ecal Front End Board :

- Compatible with the new compact readout electronics

- Benefits from experience of the long Slabs developed by LLR.

22/02/2021

Gradconn connectors (1,5 mm high)

SL – Board V2

15-Layer prototype with SL-Board, CORE kapton and CORE module (~ 15 000 channels)

### Challenges of the new Front End Board

#### > Optimise Power Pulsing Mode:

- The new philosophy is to **limit the current** through the Slab (current limiter present on the SL Board). This will permit to :

- Avoid driving high currents through the connectors and makes the current peaks local around the SKIROCs chips.

- Avoid voltage drop along the slab.

- Temperature uniformity

- > Clean clock distribution all over the slab :

- For slow control and readout.

- > Parallel configuration and readout over 2 partitions. ( < Fev12 like)

- > Easy disassembly and full individual test for ASUs

- Use of flat connectors for connexion between boards.

- > Drive high voltage up to 350V for 750 $\mu$ m wafer (through the connectors)

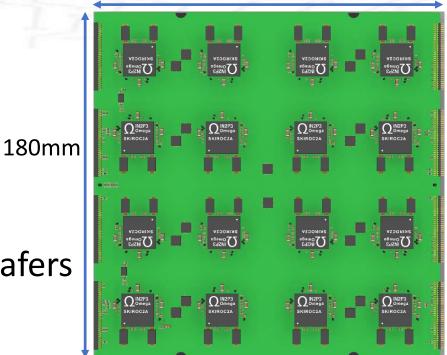

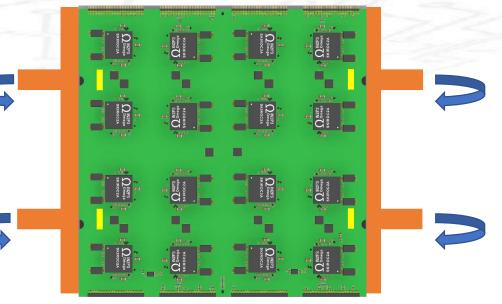

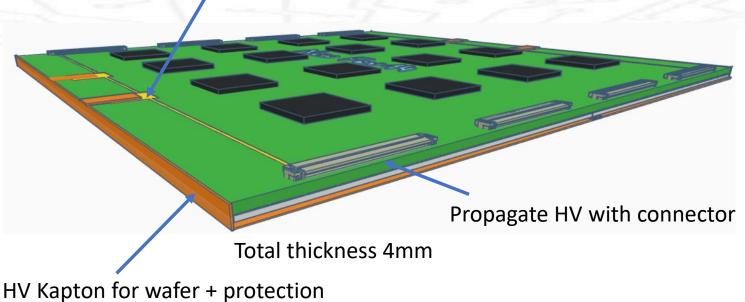

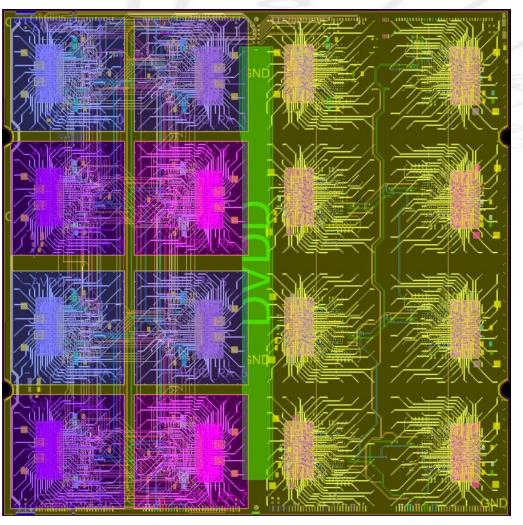

### Properties of the new front end board

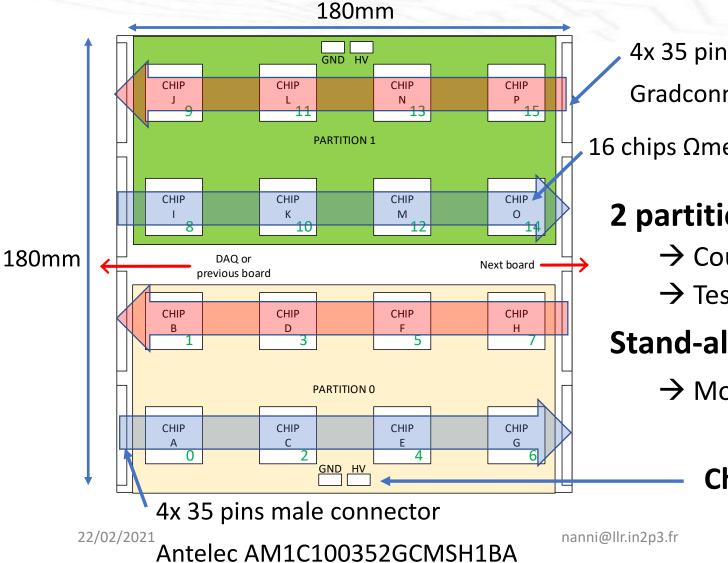

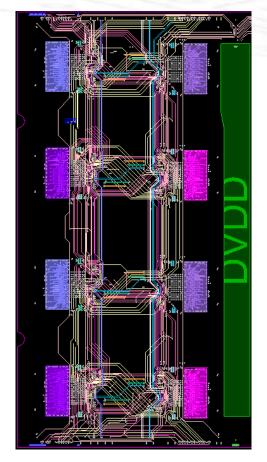

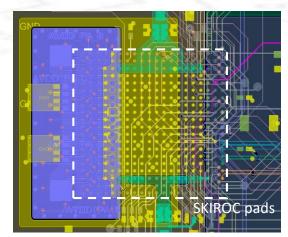

- 16 chips Ωmega SK2A to read pixels

- 2 power supply AVDD and DVDD

- Generate local analog power per chip

- Generate local digital power per partition

- 1024 pixels on bottom side to glue 4 x 6" Si wafers

- Up to 10 boards configured

- Keep or improve performances (ex: S/N of 20)

- Precision on flatness, dimensions, ... ±25µm

180mm

3D view from Cadence Allegro

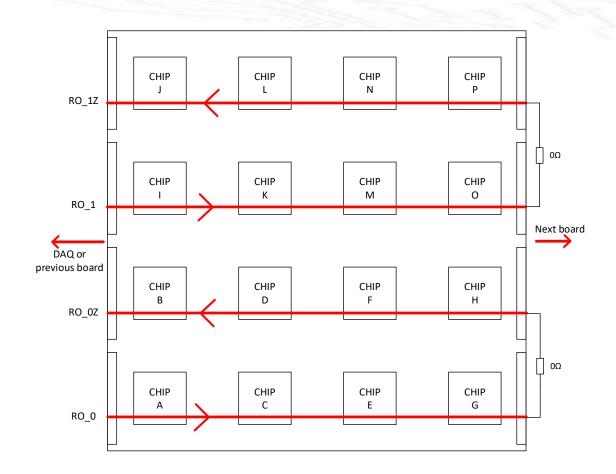

# **Board** synoptic

4x 35 pins female connector Gradconn BB02-WF352-K03-000000

16 chips Ωmega SK2A

**2 partitions** for slowcontrol and data flow.  $\rightarrow$  Could be link or bypass with 0 $\Omega$  resistor  $\rightarrow$  Test mode for 1 chip only per partition

#### **Stand-alone HV** distribution

$\rightarrow$  More flexibility: testing & set-ups

**Choose solution for HV connexion**

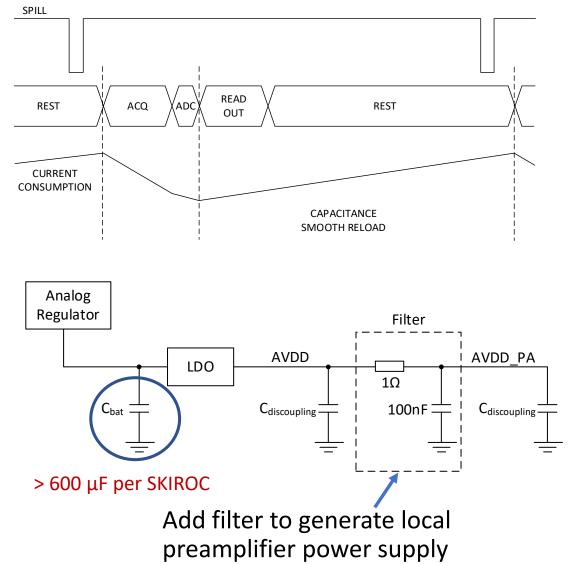

#### Power distribution and power pulsing

On the electrical long slab (8 boards chained), we measure important voltage drop (5%) due to:

- 50%: Resistivity of vdda layer

- Propagation of high current to the power supply (300mA / board in acquisition)

- 50%: Ωmega SKIROC 2 Bandgap distribution

#### We decide to :

- Limit the current through the slab.

- Add large capacitors with low ESR for local energy storage (around each SKIROC chip)

- Generate local power supply with LDO (Low Drop Out) to remove voltage variations

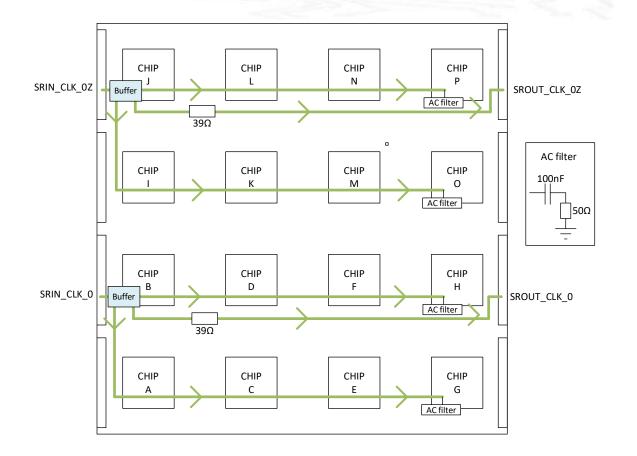

# Configuration lines (1/2)

In the electrical long SLAB, we have some difficulties to configure more than 4 boards. Configuration clock line is not design for variable number of boards chained.

→ Only 1 buffer upstream drive all readout chips, not adapted for variable wire length.

→ Need long studies to find solution with hardware

- Make simulations with Sigrity

- Place filter to shift the reflection effect on the configuration clock

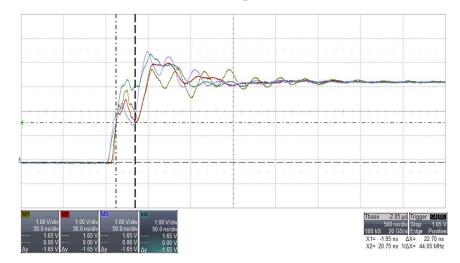

# Configuration lines (2/2)

Need system to reduce length of clock line and load capacitors.

- → Add buffer or logic gates, dedicated per local partition and for next board

- → Add AC filter to reduce reflection effect on each partition.

- → Configuration clock is drawing to limit stub and reflection

### Data lines

Each chip is chained in coil per partition.

Ωmega SK2A chips are not design to drive signal on 180 cm (10 boards).

Possibility to bypass chip if necessary with slowcontrol or shunt resistors.

- → The last chip of each partition must be the closest of DAQ.

- → Board is divided in 2 partitions to reduce readout time

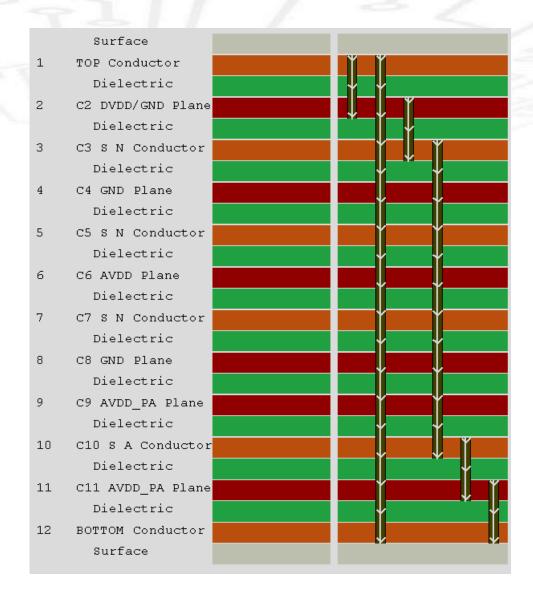

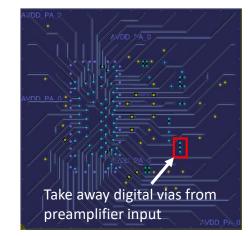

### Stack-up board

- Keep layer for power

- 2 x GND

- 2 x AVDD\_PA

- 1 x AVDD

- 1 x DVDD

- Minimize crosstalk

- Keep shielding mush as possible

- AVDD\_PA for preamplifier signals

- GND for analog and digital signals

- Move away digital from preamplifier line

- Adaptation lines

- $50\Omega$  for single ended

- $100\Omega$  for ddifferential lines

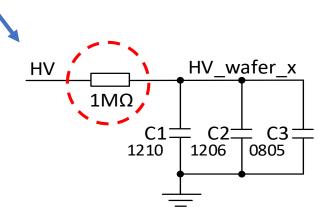

## High voltage proposition

We have no idea of cumulative effect on HV for 10 boards

- 40 wafers connected on the same HV

- Leakage current <1nA / wafer in average</p>

- Noise effect ?

- → Add a filter for each wafer and limit the current in case of wafer failure.

#### How to connect kapton to board ?

#### HIROSE TF443SW series

Request samples to test connectors solutions

### Mechanics propositions

- Kapton is enlarge to protect

2 sides of the system during insertion or slice in the support.

- High voltage is driven by the board instead of the kapton for assembly, maintenance and costs reductions.

High voltage power supply

Example of faulty board <

To unplug: slice to the right

#### Layout optimizations

Digital lines optimize for long SLAB

Insulate input signals with GND ring

Each pattern of input signal are identical

#### Board finished 45%

- 5% for LDO power

- 50% for partition duplication

# New packaging for SKIROC2A chips

- Previous company Novapack stop BGA activities

- Very difficult to find a company for BGÁ encapsulation.

- Test a new company Aptasic

- $\rightarrow$  No conclusive results

- Contact with a new Chinese company (recommend by  $\Omega$ mega) **NCAP**

- Package BGA size: 17mm x 17 mm

- Thickness: 1,2mm

#### I receive quotation today !

NCAP CHINA

Aptasic solution

Awaited solution

#### Upgrade bench of unique chip

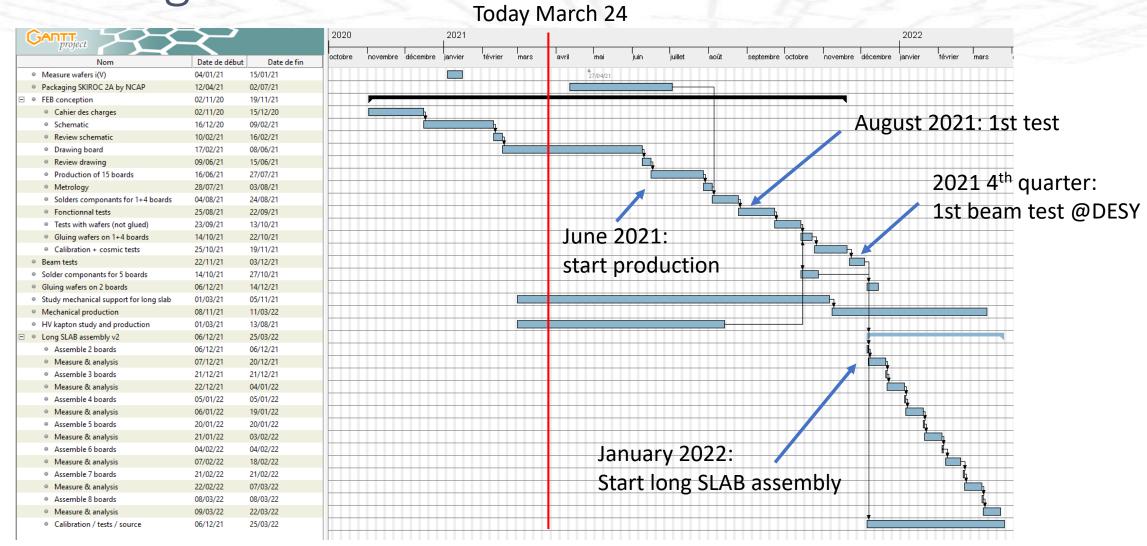

### Planning for 2021

### Conclusion/planning

Design of new front end board (Collaboration between LLR and IJCLab) :

- Optimisation of the power pulsing (compatible with the SL Board and the new philosophy of current limitation over the slab)

- Reduce voltage drop on power supply

- ➤Clean clock distribution over the slab.

- Change high voltage distribution through the board (HV distribution over connectors)

- Add solutions to simplify manipulation and protect wafers

- June: production of 15 new front end boards

- September: 1st electrical test

- End of 2021: beam test @ DESY (COVID ?)

- 2022: start long slab assembly

- ightarrow Be ready in 2023, with new long slab design for ILD schedule