# Tracking Vertexing and Timing Detectors Summary

Ziad El Bitar (CNRS) Nicola De Filippis (Politecnico and INFN Bari) Shinya Narita (Iwate University) <u>Ariel Schwartzman</u> (SLAC) Caterina Vernieri (SLAC)

LCWS2024 International Workshop on Future Linear Colliders

11-July-2024

# Outline

- Vertex detector (MAPS)

- Tracker

- Dual Timer Pixel (Belle)

- TPC

- Drift Chamber

- CLD silicon

- Timing layers

- Particle ID

- dE/dX / dN/dx

- impact of RICH in CLE silicon tracking performance

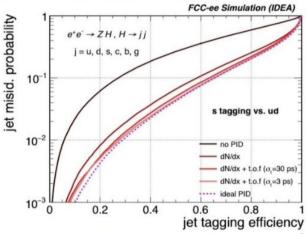

## flavor physics

## strange-tagging

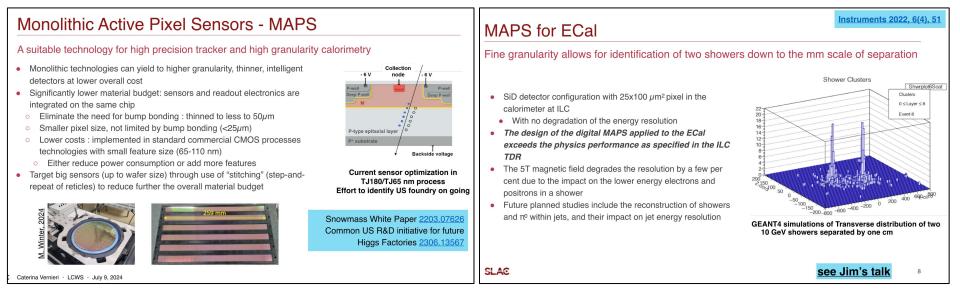

# MAPS for tracking and calorimetry

### Caterina Vernieri

- 65nm CMOS imaging process

- increased density for circuits: higher spatial resolution and improved timing at same power consumption

- supports stitching  $\rightarrow$  Wafer scale MAPS

## **MAPS** for tracking and calorimetry

- Focus on achieving nanosecond timing resolution at low power consumption:

- Suppression of beam backgrounds to keep Ο occupancy low and/or trigger decision before reading out the detector

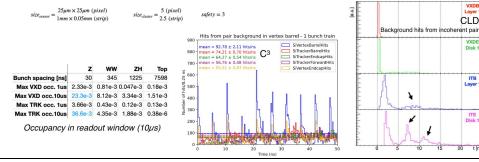

### Beam induced backgrounds at future HF

D. Ntounis (2023) G. Marchiori (2023) TDAQ@Annecy2024

Layer

CLD

VXDE

Disk 1

ITR Layer

Diek

#### Same tools and methodology between ILC & FCC within Key4HEP

- ILC physics studies are based on full simulation data and some have been recently repeated for C<sup>3</sup>

- Time distribution of hits per unit time and area on 1st layer ~ 4.4 · 10<sup>-3</sup> hits/(ns · mm<sup>2</sup>) = 0.03 hits/mm<sup>2</sup> /BX

- · CLD detailed studies @FCC show an overall occupancy of 2-3% in the vertex detector at the Z pole

- assuming 10µs integration time

$occupancy = hits/mm^2/BX \cdot size_{sensor} \cdot size_{cluster} \cdot safety$

### Summary of NAPA-p1 Performance

|                          | Specification           | Simulated NAPA-p                            |              |

|--------------------------|-------------------------|---------------------------------------------|--------------|

| Time resolution          | 1 ns-rms                | 0.4 ns-rms                                  | $\checkmark$ |

| Spatial<br>Resolution    | 7 µm                    | 7 µm                                        | $\checkmark$ |

| Noise                    | < 30 e-rms              | 13 e-rms                                    | $\checkmark$ |

| Minimum<br>Fhreshold     | 200 e-                  | ~ 80 e-                                     | $\checkmark$ |

| Average Power<br>density | < 20 mW/cm <sup>2</sup> | 0.1 mW/cm <sup>2</sup><br>for 1% duty cucle | $\checkmark$ |

|                          |                         | ,                                           |              |

Napa-p1

## DuTiP :

## Vertex Detector for Belle II Upgrade and Intermediate Silicon Tracker for ILC

Yasuo Arai, Tristan Fillinger, Junji Haba, <u>Akimasa Ishikawa</u>, Ikuo Kurachi<sup>B</sup>, Kenkichi Miyabayashi<sup>D</sup>, Miki Mitani<sup>C</sup>, Emi Ozaki<sup>D</sup>, Takehiro Takayanagi, Ayaki Takeda<sup>C</sup>, Hina Tagashira<sup>D</sup>, Toru Tsuboyama, Miho Yamada<sup>E</sup>

KEK, D&S<sup>B</sup>, Miyazaki University<sup>C</sup>, Nara Women's University<sup>B</sup>, TMCIT<sup>E</sup>

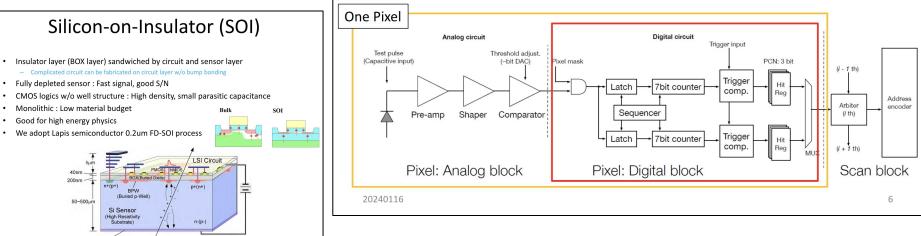

#### DuTiP and SOI

- We invented Dual Timer Pixel (DuTiP) concept for Belle II Vertex detector upgrade that can be also used for layer 7 and 8 of ILD SIT.

- Our requirements for Belle II Vertex detector

- Binary detector to reduce data size and power consumption.

- Relatively fast clock of > 10MHz to reduce the occupancy to  $O(10^{-4})$  or less

- Global shutter readout based on L1 Trigger to reduce data size.

- Hold signals at least trigger latency of 4.4us

- Low power consumption ~100W/cm<sup>2</sup>

- · For normal temperature air cooling

200nm

50~500ur

Back Plane

Radiation

•

٠

20240709

• We adopted Silicon on Insulator (SOI) technology to realize the DuTiP

## The Concept "DuTiP"

#### **Dual Timer Pixel** ۲

- Dual Timer (down time counters) in a Pixel to store signal and wait for trigger signal

- 7bit timer can wait trigger upto 127 x CLK.

- Two timers allow the second hit during trigger latency

- Hit registers for three time buckets, previous, current and next for timing scan

## DuTiP1 with SOI technology

- Dimension

- 6mm<sup>2</sup> chip

- Pixel Size 45um x 45um

- 45um/v12=13um

- charge sharing improves the resolution

- 64x64 pixel array

- 300um<sup>t</sup> (to be thinned to ~50um<sup>t</sup>)

- Analog circuit

- ALPIDE analog circuit fabricated on SOI by Strasbourg and modified by KEK.

- Low power consumption amplifier

- Digital Circuit

- 7bit timer x 2

- 15.9MHz(62.9ns) CLK (SuperKEKB 509MHz/32(1.97ns\*32))

- Trigger latency of at most 8us (4.4us requirement)

- Only current and previous time buckets (no next bucket)

- 20240116- No sophisticated readout circuit not fabricated

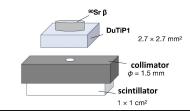

- Efficiency

- Using <sup>90</sup>Sr : ~98+-2%

- Cosmic or accidental noise hit are subtracted with dry run data.

- Large systematic uncertainty due to limited setup

- To be tested with test beam

- Production yield is checked without collimator

- More than 99% pixel is working

<sup>90</sup>Srβ

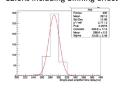

### Timing Resolution for single pixel

- DuTiP + Scintillation counter

- Tested with <sup>90</sup>Sr and 50MHz CLK (20ns)

- Timing resolution is 11.2ns

8

- With test pulse ~10ns

- Enough smaller than time bucket of 63ns

#### 12.6ns including binning effect

TIN test pu

from test pulse to chip outp

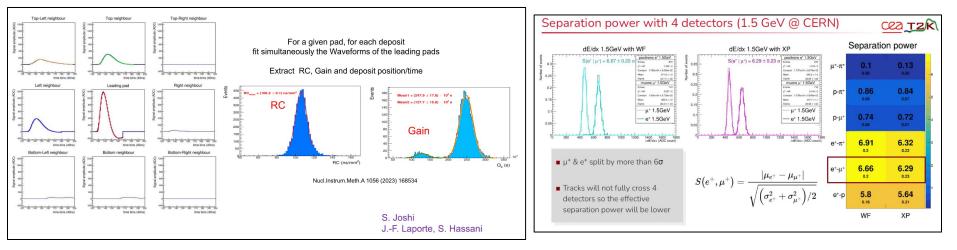

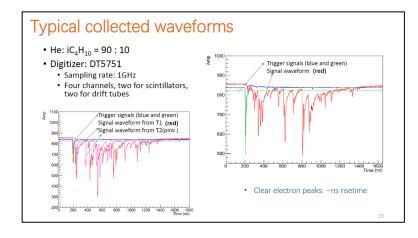

## New TPCs with charge spreading resistive Micromegas for T2K near detector Cesa I FNNIFFR<sup>2</sup>

Paul Colas, U. Paris Saclay

From ILC TPC R&D to a real neutrino experiment in Japan

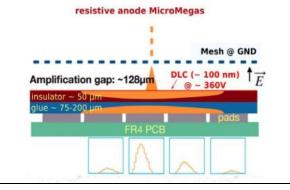

## Charge spreading

By adding a resistive layer and a dielectric layer on top of the anode, we obtain a **resistive-capacitive** continuous network that spreads evenly the charge between the hit pad and its neighbours.

This allows a barycentre to be determined, which greatly improves the resolution : resolutions as good as 1/50 times the pad size are obtained.

#### Many tests in recent years

Beam test at DESY in 2015 (LCTPC, 2 DLC modules) Cosmic-ray test at Saclay in 2017 (T2K) Beam test at CERN in August 2018 (T2K) Beam test at DESY in November 2018 (LCTPC) Cosmic-ray test in Saclay since January 2019 (LCTPC/FCC) Beam test at DESY in June 2019 and 2021 (T2K) Cosmic test at CERN since December 2019 (T2K) Cosmic tests in Saclay during the covid year (T2K) (4-6 modules)

5 TPC of 15, 58, 60, 100 and 150 cm length with 1000 to 2000 channels All with DLC charge spreading

Overal conclusion : extremely reliable and stable operation

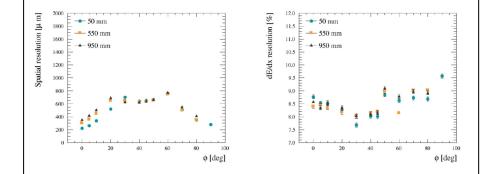

## Performance (beam test at DESY in 2021)

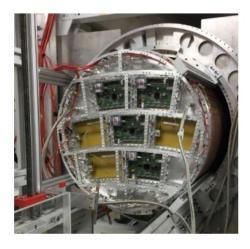

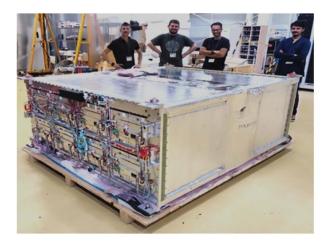

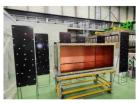

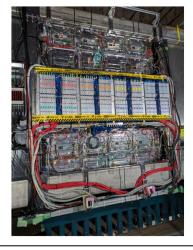

## Installation at JPARC

32 (+spares) ERAM modules built at CERN (Rui de Oliveira) and characterized/tested at CERN Field cages built in industry in Spain under supervision by T. Lux, G. Collazuol et al.).

TPCs assembled at CERN (gluing stripped kapton and soldering resistor chains) and transported by plane to JPARC. Then re-tested on surface and lowered in the T2K pit (T. Lux). 100% operationnal. Excellent gas (system by R. Guida built at CERN and commissioned by E. Radionici) : 2 ppm O<sub>2</sub> and 5 ppm H<sub>2</sub>O

### Summary

- In the last 8 years, a new type of TPCs has been designed, constructed and commissioned. It uses the ERAM technology (Encapsulated Resistive Anode Micromegas) to spread the charge and protect the electronics.

- A lot of progress has been obtained within T2K to understand the charge spreading, the homogeneity of the gain and RC maps.

- Two new such TPCs have been installed and commissionned at JPARC in the T2K Near Detector, contributing to a very significant upgrade of this experiment.

- All this will prove very useful as a preparation for an ILC TPC.

## **Building a Precise TPC Field Cage Oliver Schafer**

#### Kapton Copper shielding Large Prototype TPC Field Cage - V2 -GRP (0.3 mm) -Nomex Laver State of October 2019 Nomex honeycomb Challenge of a high-precision TPC field GRP (0.3 mm) Isolation layer (Kapton) cage: - Field strips Low material, high HV stability, high mechanical precision Why a new TPC prototype field cage? Current field cage built by external $610.4^{\pm 0.1}$ company: field cage barrel Skewed by about factor 10 too much $\rightarrow$ field homogeneity not within specs Want to gain more in-house experience nominal axis for building the big ILD TPC axis 0.04 F Verifiable material budget A New workshop at DESY with precision mandrel for construction including vacuum bag ready

DESY. The Quest of Building a Precise TPC Fieldcage | Oliver Schäfer | LCWS Tokyo July 9th 2024

٠

Page 5

#### Field Cage V2 in 2020 Field Strip Foil

- December: Investigating and fixing resistance mismatch

- Signal runtime measurements (reflectometry) lead to find a tiny hole to the mirror strip side

- Recorded the growth of that hole by interplay of electrical discharges and thermal decomposition (see separate video)

- · Carefully "cleaned" hole borders and removed copper

- · Closed by gluing in a polyimide patch

- · Re-painted conducting pattern on top

- · Resistance after repair roughly as expected

- December 16<sup>th</sup>: "We stay at home" rule

- HV test of the repaired place planned

- · Final gluing delayed, no activity in workshop since

#### Field Cage V2 in 2021

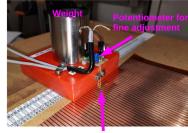

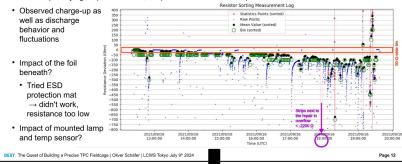

#### **Precision Measurement of the Resistor Chain**

- All resistors need to be in a bin of 50 Ω width to fulfill our requirement on the field homogeneity

- September:modified the measurement equipment we used to select/sort the resistors before soldering, so it can be used on the field strip foil (same Wheatstone bridge design); includes a temperature sensor

- · Measurement done with respect to a default resistor

2 spring loaded measurement pins

Field strip side

#### Field Cage V2 in 2021

#### Precision Measurement of the Resistor Chain

- · Measurement from 16.Sep.2021

- Field strip foil lying on protection foil, temperature sensor and lamp mounted on the table

- · Remeasured on 24th January 2022: all strips sufficiently within specs

- Assumption: epoxy resin took that long to fully cure and for moisture trapped in bubbles to diffuse out

→ Proceed with high voltage test

DESY. The Quest of Building a Precise TPC Fieldcage | Oliver Schäfer | LCWS Tokyo July 9th 2024

Page 11

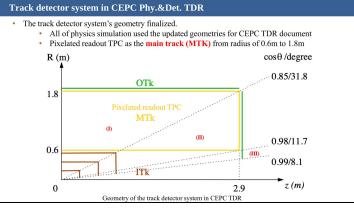

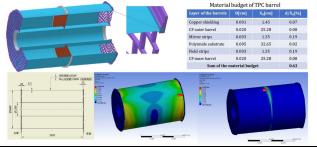

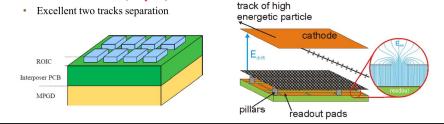

## High Granularity TPC for Tera-Z at CEPC

### Huirong Qi

#### #1. Material budget at endcape/barrel Carbon Fibber

- · Consideration of new Carbon Fiber barrel instead of the honeycomb barrel

- Ultra-light material of the TPC barrel :  $0.63\% X_0$  in total, including

- FEA preliminary calculation: 0.2mm carbon fibber barrel can tolerant of LGAD OTK (100Kg)

- · Optimization of the connection back frame of the endcap (on going)

#### Pixelated readout TPC technology for CEPC TDR

- A pixelated readout TPC is a good option to provide realistic physics requirements of Higgs Physical and Tera-Z Physics also (2E36) at CEPC.

- Pixelated readout  $\rightarrow$  better resolution  $\rightarrow$  low gain  $\rightarrow$  less distortion

- Highlights of Pixelated readout TPC technology for CEPC TDR

- Can deal with high rates (MHz/cm<sup>2</sup>)

- High spatial resolution  $\rightarrow$  better momentum resolution

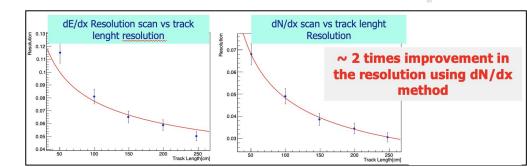

- PID: dE/dx + dN/dx (In space)

#### Low voxel occupancy : 1E-5 to 1E-6 (cite#2)

- At 2 E36 with Physics event only, even bunch distribution(cite#3).

- Pixelated readout much **LOWER** inner most occupancy (0.6m inner radius)

- Pixelated readout can easily handle a high hits rate at Z pole. (cite#4)

- The data at the inner radius @40M BX Z pole@1 Module ~0.05Gbps(Maximum).

Prototype setup to verify power, spatial resolution, and distortion tolerances

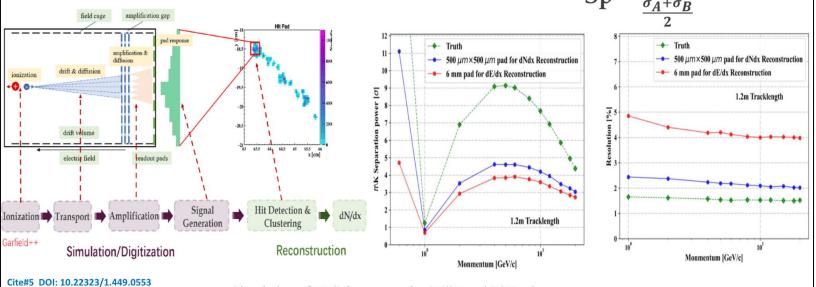

## High Granularity TPC for Tera-Z at CEPC

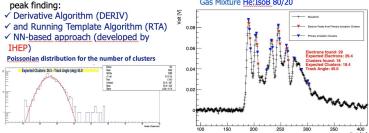

#### #3. Improved dE/dx+dN/dx √

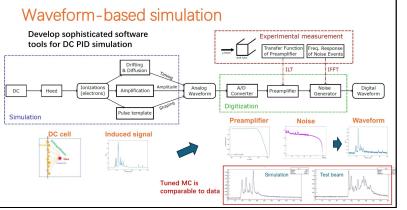

- Full simulation framework of pixelated TPC developed using Garfied++ and Geant4 at IHEP

- Investigating the  $\pi/\kappa$  separation power using reconstructed clusters, a  $3\sigma$  separation at 20GeV with 50cm drift length can be achieved

- dN/dx has significant potential for improving PID resolution

Cite#6 EPS-HEP 2023 talk by Yue Chang

Simulation of TPC detector under 3T/2T and T2K mixture gas

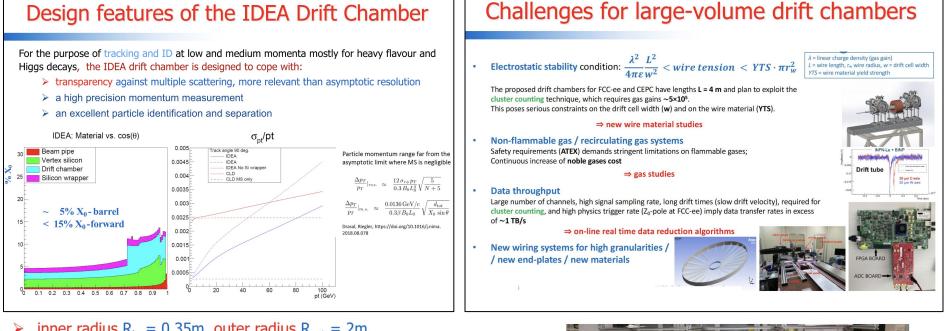

## **Drift Chamber for IDEA at FCC-ee**

### Nicola De Filippis

- > inner radius  $R_{in} = 0.35m$ , outer radius  $R_{out} = 2m$

- $\blacktriangleright$  length L = 4m

- drift length ~1 cm

- drift time ~150ns

- > 343968 wires in total:

sense vires:  $20 \ \mu m$  diameter W(Au) = > 56448 wires field wires:  $40 \ \mu m$  diameter Al(Ag) = > 229056 wires f. and g. wires:  $50 \ \mu m$  diameter Al(Ag) = > 58464 wires

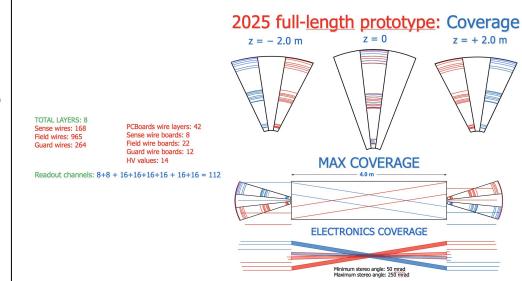

## **Drift Chamber for IDEA at FCC-ee**

### 2025 full-length prototype: Goals

- ► Check the limits of the wires' electrostatic stability at full length and at nominal stereo angles

- > Test different wires: uncoated Al, C monofilaments, Mo sense wires, ..., of different diameters

- Test different wire anchoring procedures (soldering, welding, gluing, crimping, ...) to the wire PCBs

- Test different materials and production procedures for spokes, stays, support structures and spacers

- Test compatibility of proposed materials with drift chamber operation (outgassing, aging, creeping, ...)

- Validate the concept of the wire tension recovery scheme with respect to the tolerances on the wire

positions

- Optimize the layout of the wires' PCBs (sense, field and guard), according to the wire anchoring

procedures, with aim at minimizing the end-plate total material budget

- Starting from the new concepts implemented in the MEG2 CDCH robot, optimize the wiring strategy, by taking into account the 4m long wires arranged in multi-wire layers

- ► Define and validate the assembly scheme (with respect to mechanical tolerances) of the multi-wire layers on the end plates

- Define the front-end cards channel multiplicity and their location (cooling system necessary?)

- Optimize the High Voltage and signal distribution (cables and connectors)

- ▶ Test performance of different versions of front-end, digitization and acquisition chain

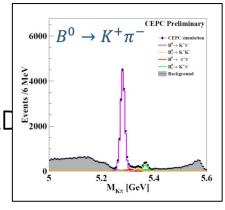

## • Several algorithms developed for electron pack finding:

### 2021/2022 beam test results: resolutions

## Drift Chamber Cluster Counting for CEPC Guang Zhao

arXiv: 2402.16493

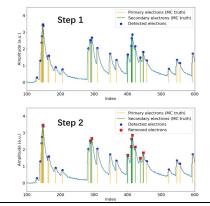

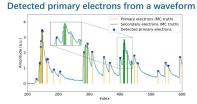

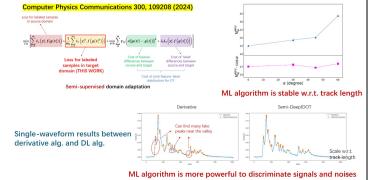

### dN/dx reconstruction with supervised learning

Reconstruction task: Determine the number of primary electrons in the waveform

#### 2-step machine learning algorithm:

- Peak finding by LSTM:

- Detect peaks from both primary and secondary electrons

- Clusterization by DGCNN:

- Remove secondary electrons from the detected peaks in step 1

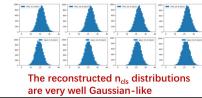

### PID performances with supervised models

#### Reconstructed # of clusters distributions

pions/kaons are < 3%, which are much better than typical dE/dx ~5%

## **Drift Chamber Cluster Counting for CEPC**

#### dN/dx reconstruction with domain adaptation

#### Summary

#### R & D progress of the CEPC drift chamber

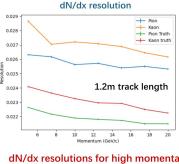

- PID performance: > $3\sigma$  K/ $\pi$  separation at 20 GeV/c for 1.2 m track length

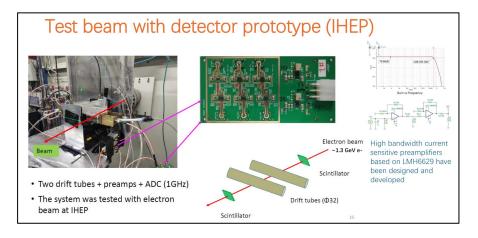

- dN/dx reconstruction with deep learning shows promising performance for simulation and testbeam data

- Fast electronics is under development. Preliminary analysis with the testbeam validates the electronics and the feasibility of dN/dx measurement

- Preliminary mechanical design and FEA show a stable structure

- Global electronics scheme is reasonable

#### Plans

- Fine detector optimization

- Optimize deep learning algorithm and FPGA implementation

- Prototyping and testing with full-length cells (mechanics, manufacturing, testing)

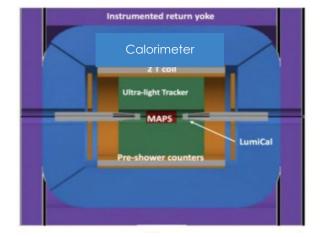

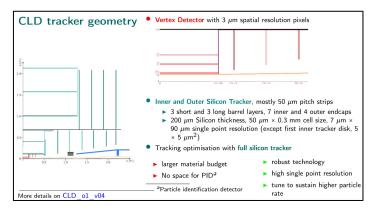

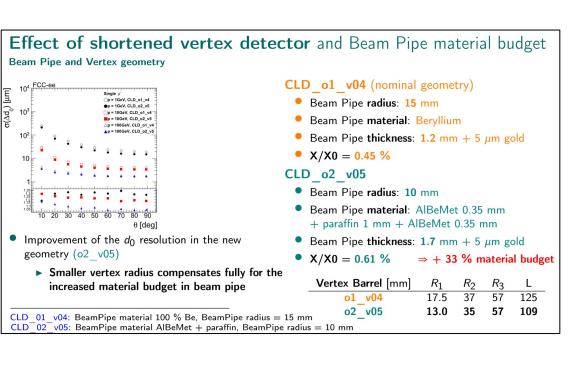

## CLD Tracking Performance Gaelle Sadowski

#### CLD\* detector concept at FCCee

- Consolidated option based on the detector design developed for CLIC detector

- ► All silicon vertex detector and tracker

- ▶ 3D-imaging highly-granular calorimeter system

- Coil outside calorimeter system

- Resistive plate chambers muons detector

# **CLD Tracking Performance**

CLD: magnetic field = 2 T

20

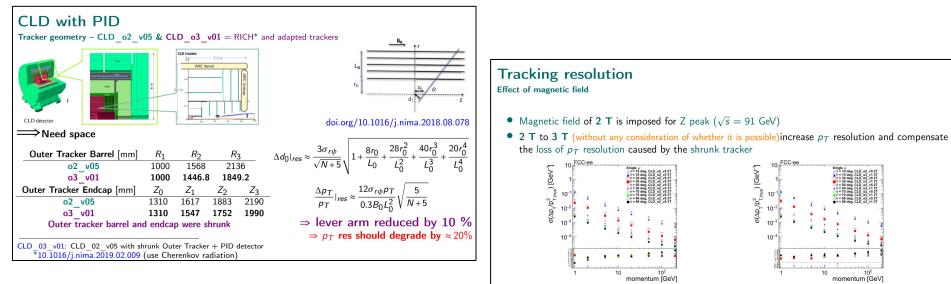

#### CLD with PID Tracker geometry – CLD\_o2\_v05 & CLD\_o3\_v01 • $p_T$ resolution depend mainly on lever arm • Differences observed are compatible with analytic formula $\approx 15$ %

• For  $\theta = 50$  °: transition Barrel / Endcap

# Summary

- Impressive progress in simulation, detector R&D, and building and testing prototypes to verify the functionality of various vertex and tracking technologies, as well as readout systems and ASICs

- Tracking, Vertex, and Timing Detector requirements continue to evolve as physics studies advance

- particle ID both at low and high momentum: Timing layers, cluster counting and dE/dx, impact of RICH on tracker design

- Long lived particles, kinks, ...