# <u>CMOS PIXEL SENSORS for TRACKING DEVICES at FUTURE HIGGS-TOP-EW FACTORIES:</u> WHERE DO WE STAND? WHAT CAN WE ANTICIPATE IN PERSPECTIVE of ILC?

Marc Winter, IJCLab-Orsay, IDT-WG3 meeting, 26th April 2024

#### **Reminder:**

- some characteristic features of CMOS Pixel Sensors (CPS)

- illustrative set-ups/concepts based on CPS

Most advanced CMOS process: TPSCo 65 nm imaging technology Generic development of the 65 nm sensors:

- R&D for fast and radiation tolerant sensors

(main drivers: HL-LHC → FCChh)

- R&D privileging spatial resolution & suppressed material budget

(main drivers: H.I. e.g. ALICE-ITS3, CBM-MVD, Belle-II → Higgs-Fact)

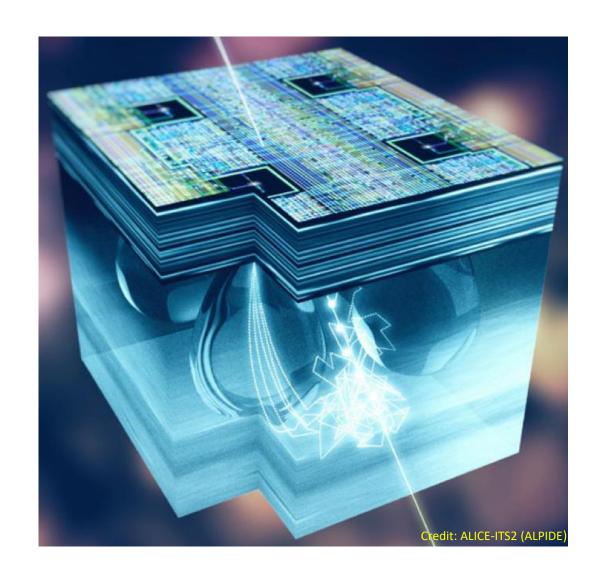

#### **ALICE-ITS3** project:

- Sensor developed for the ITS3 vertex detector

- Salient features coming out from R&D on:

CMOS-65 (vs CMOS-180), stitching, system integration

#### Other collaborative frameworks of R&D:

- DRD-TF*X* = 3, 7.6, 8 ; CERN-EP WP 1.2, 4 , ...

- CBM, Belle-II, Mu3e, eIC, ..., ALICE3

## Numerous CMOS sensors in use or development: some general features

- Main asset:  $\mu$ -circuits (steering, r.o., slow control) integrated on thin sensing substrate  $\rightarrow$  Monolithic & Thin (& Troom)

- Numerous developments of custom design CMOS Pixel Sensors (CPS) on-going for vertexing and tracking devices foreseen to equip experiments at existing infrastructures (LHC, KEK, PSI, ...) and future colliders (eIC, FAIR, FCCee, CEPC, C3, ILC, CLIC, ...)

- Some R&D for ECAL

- Optimisation imposes hierarchising conflicting requirements: Spatial resol. / Timing / Mat. budget (power) / Rad. Tol. / Hit rate

- Dependence on CMOS process (foundry) characteristics

- Frameworks: CERN-EP, DRD, ALICE-ITS3, ... (main driver for Higgs factories: 65 nm techno with stitched curved sensors)

- 3 predominent foundries: TJsc, TPSCo, L Foundry

- System Integration is crucial for realistic detector optimisation:

## Evolution of the Performances in Terms of Spatial & Time Resol. / Power / Hit Rate

| Sensor/time → (2007 -> 2024) | MIMOSA-26<br>-> EUDET, | MIMOSA-28<br>-> STAR-HFT, | ALPIDE<br>-> ALICE-ITS2,     | MIMOSIS<br>-> CBM-MVD     | MOSAIX<br>-> ALICE-ITS3   |

|------------------------------|------------------------|---------------------------|------------------------------|---------------------------|---------------------------|

| CMOS techno.                 | AMS/ <b>350</b> nm     | AMS/ <b>350</b> nm        | TJsc/ <b>180</b> nm          | TJsc/ <b>180</b> nm       | TPSco/ <b>65</b> nm       |

| Hit rate [MHz/cm²]           | ≤ 1 MHz/cm²            | ≤ 1 MHz/cm <sup>2</sup>   | > 1 MHz/cm <sup>2</sup>      | < 100 MHz/cm <sup>2</sup> | O(10) MHz/cm <sup>2</sup> |

| Pixel dim. [μm]              | 18.4 x 18.4            | 20.7 x 20.7               | ≈ 27 x 29                    | 26.9 x 30.2               | 20.8 x 22.8 (tbc)         |

| Discri. μcircuit             | End-of-col.            | End-of-col.               | In-pixel                     | In-pixel                  | In-pixel                  |

| $\sigma_{sp}$ [ $\mu m$ ]    | ≥ 3.1 µm               | ≥ 3.7 µm                  | ≥ 5 µm                       | ≥ 5.5 µm                  | ≈ 5 µm                    |

| $\Delta_t$ [ $\mu$ s]        | 115 μs                 | 185 μs                    | ≤ 10 µs                      | ≤ 5 µs                    | 2 – 10 μs                 |

| Power density                | 250 mW/cm <sup>2</sup> | 170 mW/cm <sup>2</sup>    | $\leq$ 50 mW/cm <sup>2</sup> | < 200 mW/cm2              | 50/900 mW/cm <sup>2</sup> |

#### From < 2008 to > 2024:

- CMOS technology feature size has decreased: 350 nm ≥ 65 nm

- Expts hit rate (& rad. tol.) requirements became more severe: < 1 MHz/cm² O(100) MHz/cm²

- → Global consequence: (binary) spatial resolution has degraded despite the steady feature size reduction

- Achieving  $\leq$  3 µm resol. for a vertex detector suited to Higgs fact. running conditions is a challenge (in part. for circular machines) but several potential sol. remain unexplored

## Numerous CMOS Sensors in Use or Development (illustrative sub-sample)

| Name      | Expt                 | Sub-syst      | Area                | Δ Pos., Time       | Power (fid.)                 | Technology      | Comment              |

|-----------|----------------------|---------------|---------------------|--------------------|------------------------------|-----------------|----------------------|

| ALPIDE    | ALICE-ITS2           | Vx & In. Trkr | 10 m²               | 5 μm, ≤ 10 μs      | ≤ 50 mW/cm <sup>2</sup>      | TJsc 180 nm EPI | In operation         |

| MOSAIX    | ALICE-ITS3           | Vx only       | 0.12m²              | 5 μm, 2-10 μs      | ≤ 50/900 mW/cm <sup>2</sup>  | TPSco 65 nm EPI | Wafer scale CPS      |

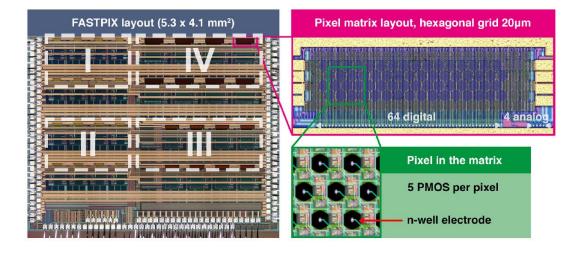

| FASTPIX   | $\rightarrow$ HL-LHC | Demonstr.     |                     | ≥ 1 µm, ≤ 100 ps   | +++                          | TJsc 180 nm EPI | Timing & Rad. Tol.   |

| MonoPix   | → ATLAS              | ITk           | few m²              | < 10 µm, ≤ 20 ns   | > 0.5 W/cm <sup>2</sup>      | TJsc 180 nm EPI | Not retained         |

| CACTUS    | FCC, eIC,            | Timing det.   |                     | < 100 ps           | 300 mW/cm <sup>2</sup>       | LF 150 nm       | R&D proto.           |

| MALTA     | HL-LHC,              | Fast det.     | few m <sup>2</sup>  | 36x40 μm², 25 ns   | > 100 mW/cm <sup>2</sup>     | TJsc 180 nm EPI | 512x512 pixels       |

| MIMOSIS   | CBM/FAIR             | Vx & In. Trkr | 0.16 m <sup>2</sup> | 5-6 μm, 5 μs       | < 100-200 mW/cm <sup>2</sup> | TJsc 180 nm EPI | Fixed target HI expt |

| TaichuPix | CEPC                 | Vx & In. Trkr |                     | ≤ 5 μm             | 90-160 mW/cm <sup>2</sup>    | TJsc 180 nm EPI | 8x8 μm² n-well       |

| NAPA      | SiD/C3               | Trkr, (calo.) |                     | 7μm pitch, O(ns)   | 20 mW/cm <sup>2</sup>        | TPSCo 65 nm EPI | Target values        |

| ARCADIA   | IDEA/FCCee           | Vx & In. Trkr |                     | 10-50 μm           |                              | LF 110 nm       | Working horse        |

| CLICpix   | CLICdp               | Vx & In. Trkr |                     | 25 μm pitch, 10 ns |                              | TPSCo 65 nm EPI | Follows TimePix      |

| OBELIX    | Belle-II             | Vx (7 layers) | O(1) m <sup>2</sup> | ≤ 10 µm, ≤ 100 ns  | ≈ 200 mW/cm <sup>2</sup>     | TJsc 180 nm EPI | Follows MonoPix      |

| MuPix     | Mu3e expt            | Vx & Trkr     |                     | ≤ 30 µm, ≤ 20 ns   | ≤ 350 mW/cm <sup>2</sup>     | HV TJsc 180 nm  | Muon decay expt      |

N.B.: list is not supposed to be complete but illustrative

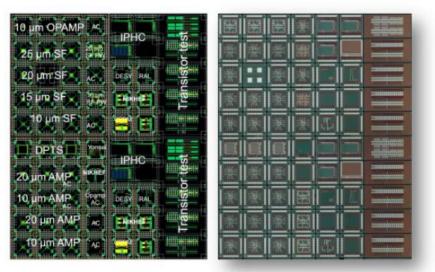

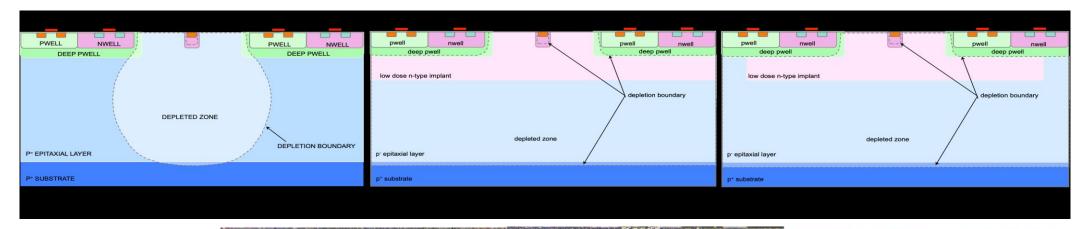

## TPSCo 65 nm Technology

#### TPSCo 65nm

- Currently in use for ALICE ITS3 and EP R&D WP1.2

- Joint runs already carried out MLR1, ER1

- CERN, IPHC, INFN, NIKHEF, STFC, SLAC, DESY, SLAC, Yonsei...

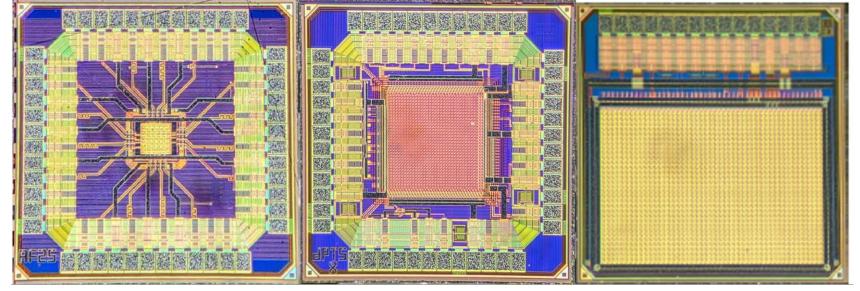

MLR1 (December 2020): 1.5 x 1.5 mm<sup>2</sup> test chips

ER1 (December 2022): stitching

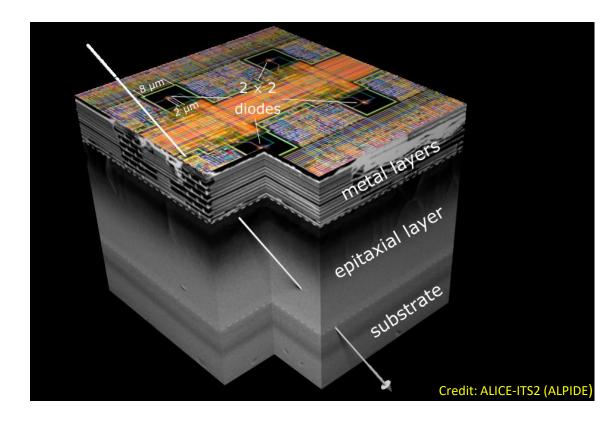

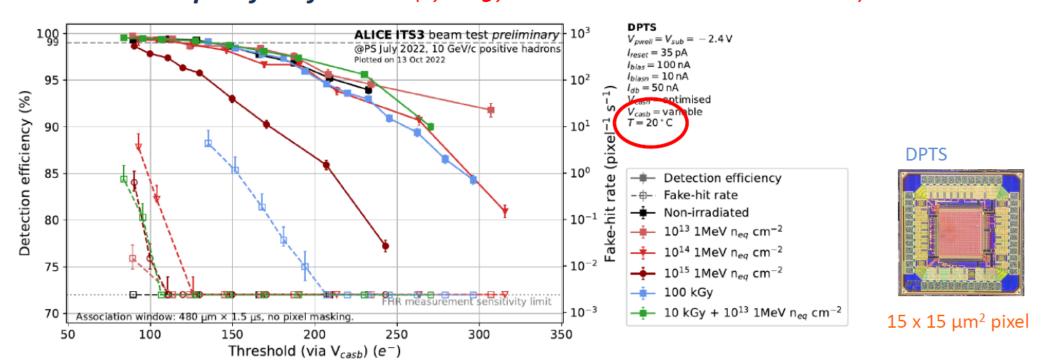

## TPSCo 65 nm Prototyping for the ALICE ITS-3 Vertex Detector

MLR-1 run (2021): Analog & Digital output prototypes with 10-25 µm pitch & 3 epitaxial layer doping profiles

Technology validation & Detection Performance assessment based on 3 different Mini-sensors & various Test structures

**APTS**: analog output

**DPTS**: digital output

CE-65: analog output

## MLR1 TEST RESULTS

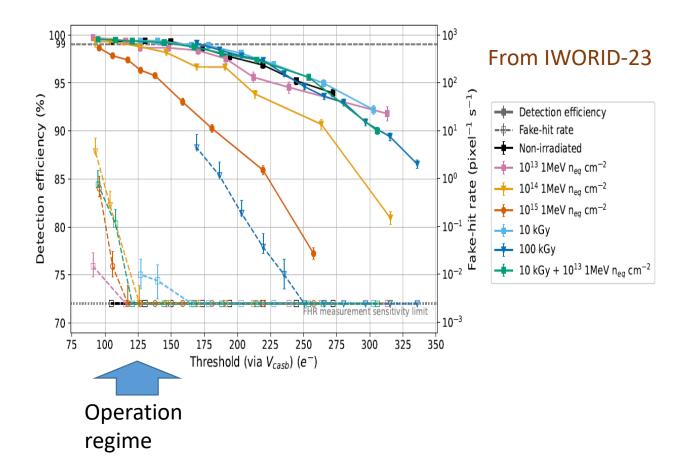

# **DPTS** (15 μm pitch) Detection Efficiency versus NIEL and TID

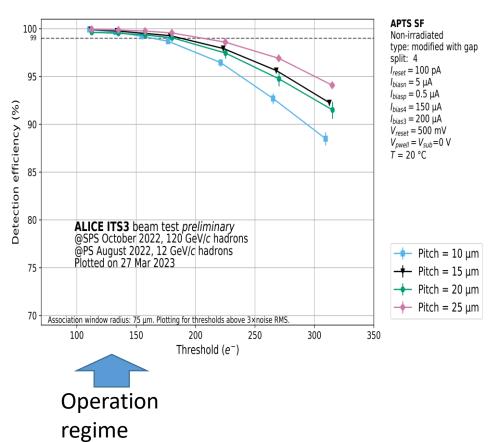

# APTS Detection Efficiency for a pitch of 10, 15, 20, 25 $\mu$ m

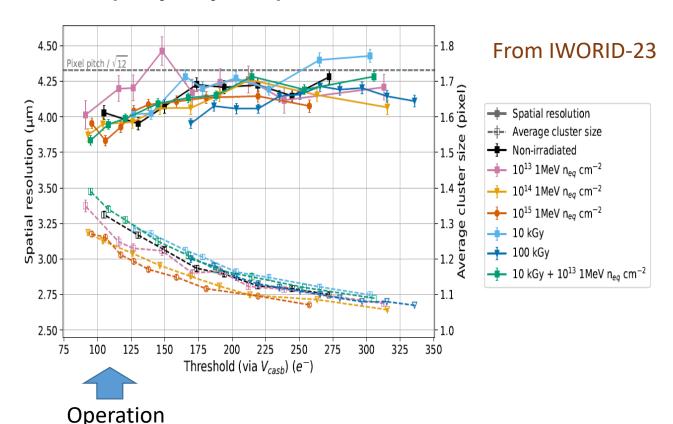

# MLR1 TEST RESULTS: Spatial Resolution & Cluster Size

#### **DPTS** (15 μm pitch) vs NIEL and TID

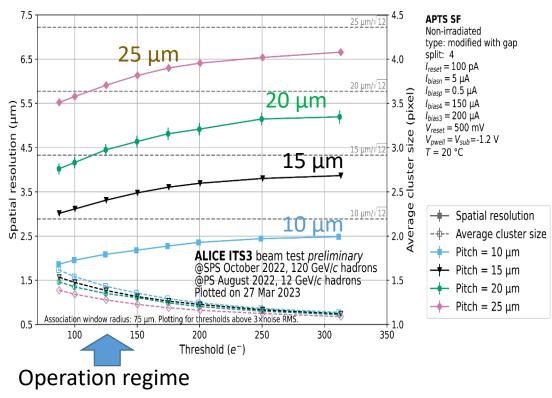

### **APTS** (10, 15, 20, 25 μm pitch)

regime

Binary resolution slightly better than pitch /  $\sqrt{12}$  (impact of thin EPI ?)

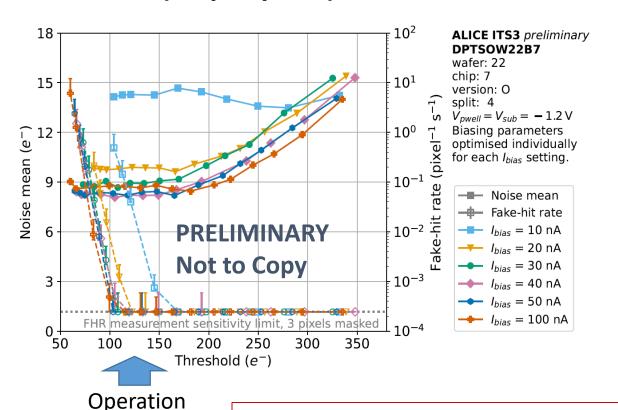

# MLR1 TEST RESULTS (soon to appear in ITS-3 TDR): Pixel Noise, Threshold Dispersion, Fake Hit Rate

#### **DPTS** (15 μm pitch): Pixel Noise

regime

#### **DPTS:** Discri. Threshold Dispersion

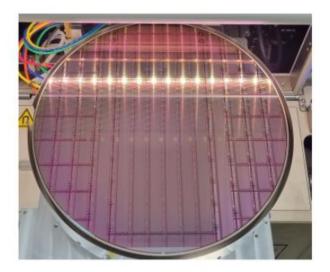

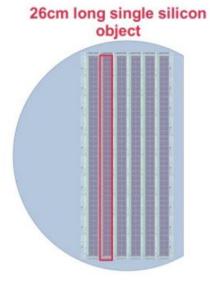

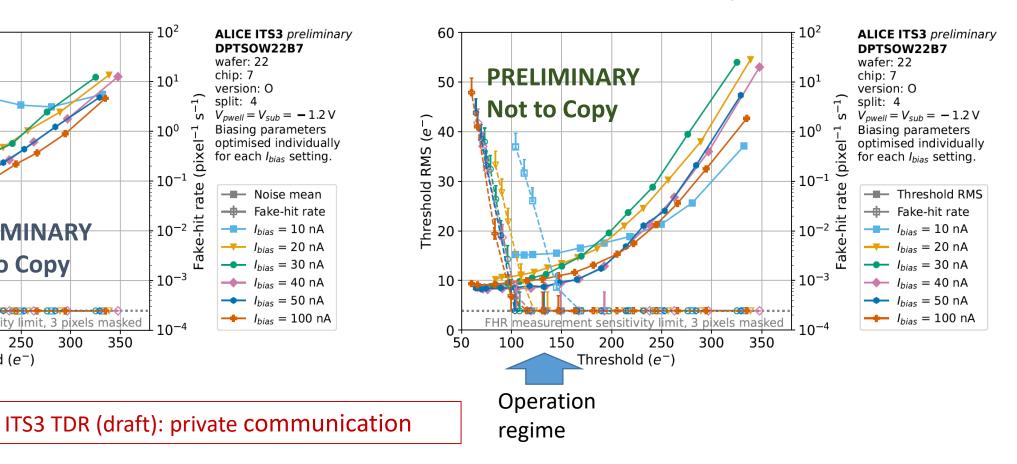

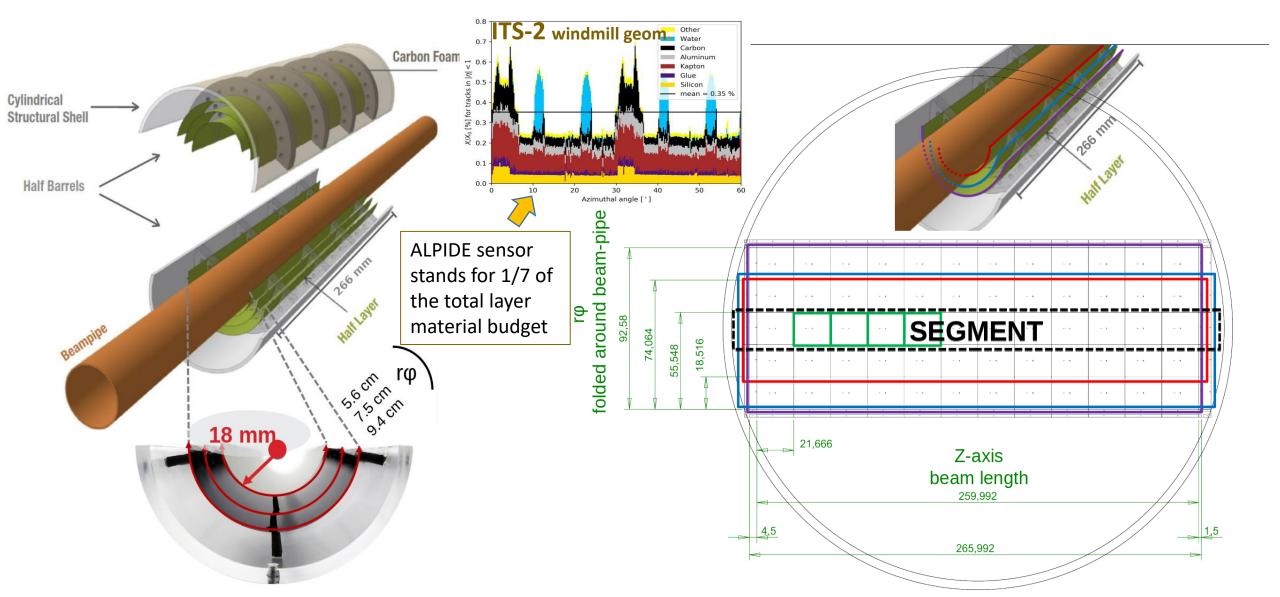

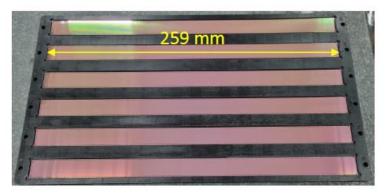

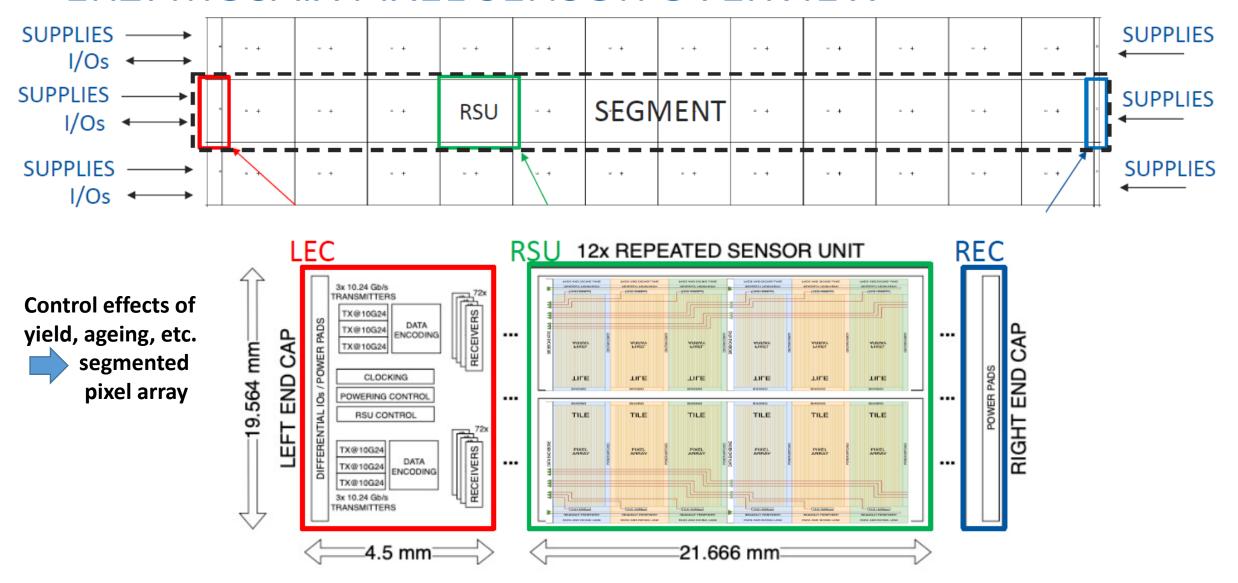

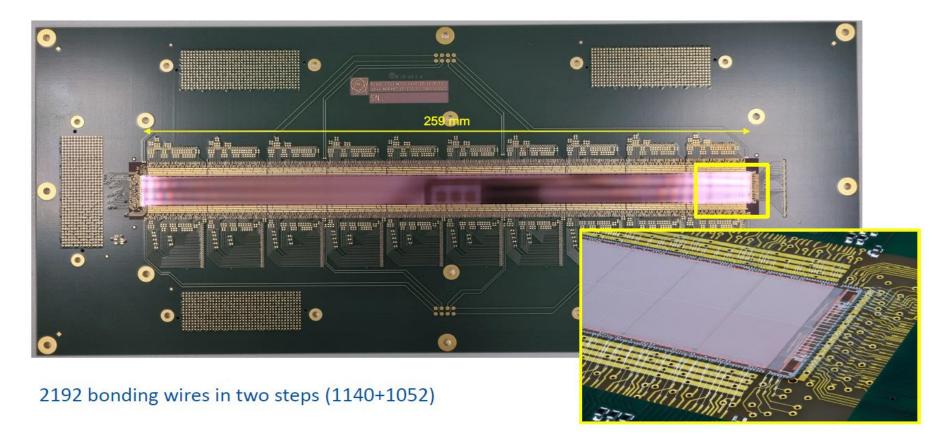

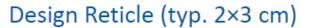

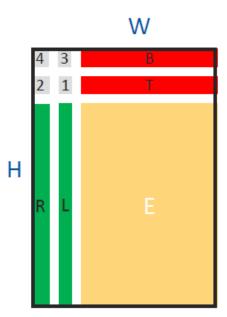

## LARGE STITCHED CMOS SENSORS DEVELOPED FOR THE ITS3

ITS3: multi-reticle (stepping), thin (≤ 50 μm), curved sensors to reach ≤ 0.1 % X0/ layer ⇒ stitching design rules

#### **ER1 Submission**

Aim at learning and proving **stitching**, submitted in December 2022

65 nm CMOS Imaging Technology

Design activities framed within CERN EP R&D WP1.2

Large effort of several teams and institutes

Two wafer scale stitched sensor chips (MOSS, MOST)

Different design approaches for resilience to

manufacturing faults

MOSS and MOST Tests on-going

16

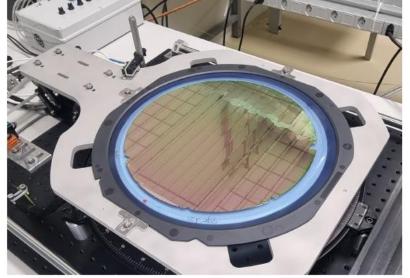

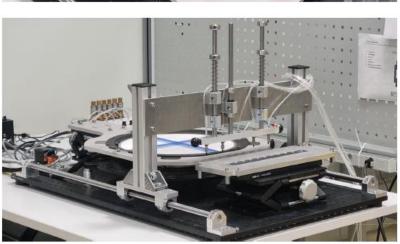

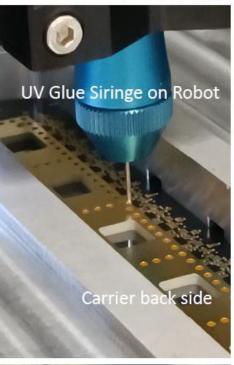

## MOSS PROTOTYPE HANDLING

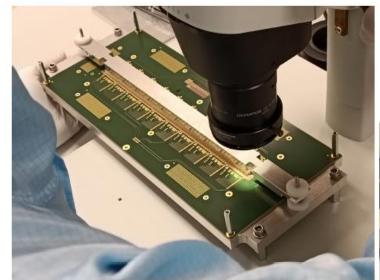

## Pick, Align, Glue MOSS on Carrier

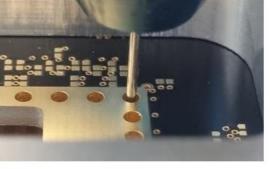

#### **ER1: MOSS SENSOR TEST RESULTS**

**MOSS beam tests**: 1st analyses indicate a spatial resolution  $\approx 5-6~\mu m$  (binary charge encoding), close to pitch/ $\sqrt{12}$

- → follows from pixel dimensions (22.5 μm x 20.8 μm) constrained by stitching rule induced system architecture design

- → shorter sensors (e.g. 12 cm long) may allow for (somewhat) smaller pixels, i.e. better spatial resolution (tbc)

Emblematic illustration of the necessity of a global approach when designing a sensor (experienced designers needed)

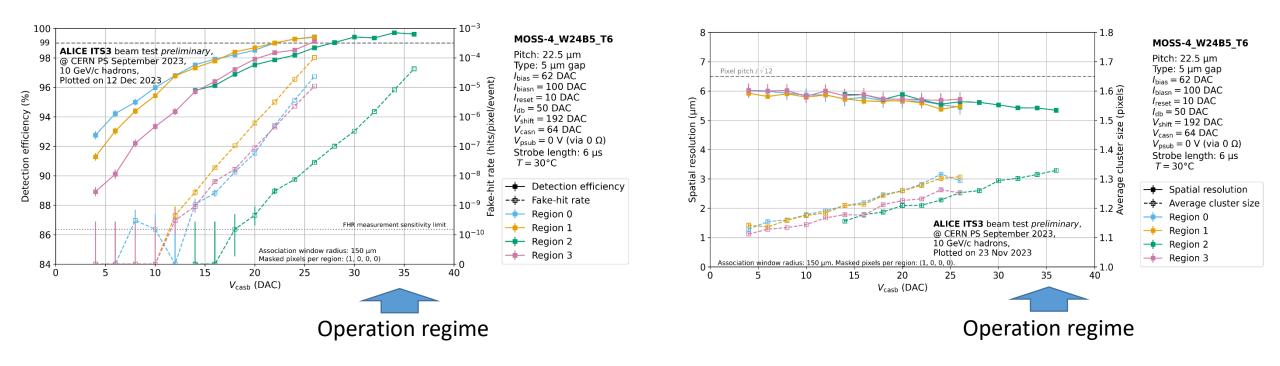

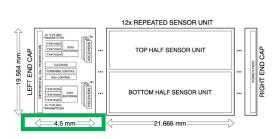

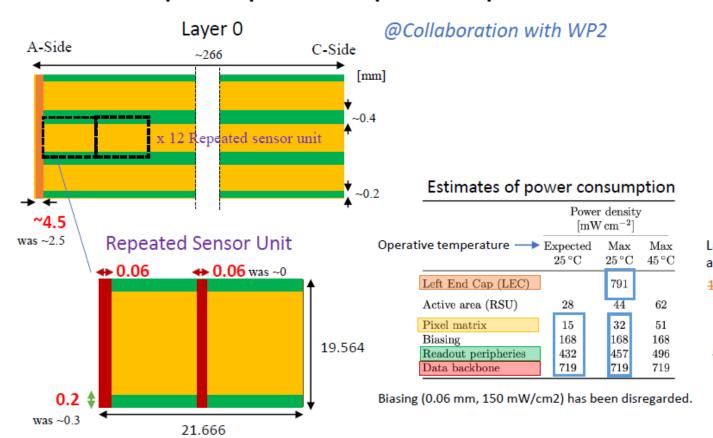

## **ER2: MOSAIX PIXEL SENSOR OVERVIEW**

Figure 3.34: Block diagram of the sensor segment.

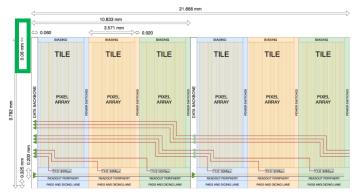

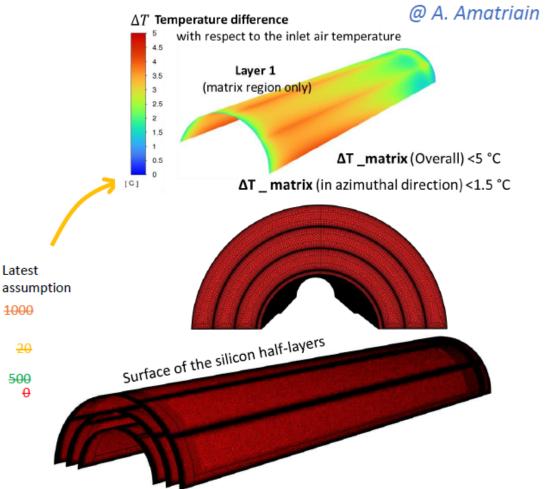

## Thermal analysis: Simulations with updated layout and heat map

Architecture of the bottom half sensor unit (not to scale)

Power density  $[\mathrm{mW\,cm^{-2}}]$ Expected Max  $25\,^{\circ}\mathrm{C}$  $45\,^{\circ}\mathrm{C}$ Left End Cap (LEC) 791 Active area (RSU) 62 28 Pixel matrix Biasing 168 168 432 457Readout peripheries 496 Data backbone 719

Total power dissipated by the 3 layers

inside ITS-3 fiducial volume (1200 cm<sup>2</sup>):

Ptot (fid. vol.) ≈ 50 W

Estimates of power consumption

- Update of the thermal simulation model with latest modifications

- 1. Layout of L0 = 19 mm, L1 = 25.2 mm, L2 = 31.5 mm

- 2. Heat map with all relevant components and power dissipations

- Pixel matrix power dissipation value not fixed → Simulations will be performed with 15 and 30 mW/cm<sup>2</sup>

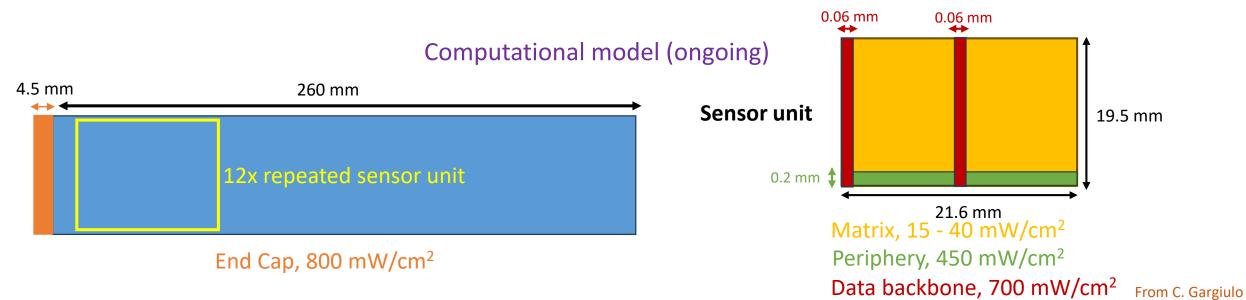

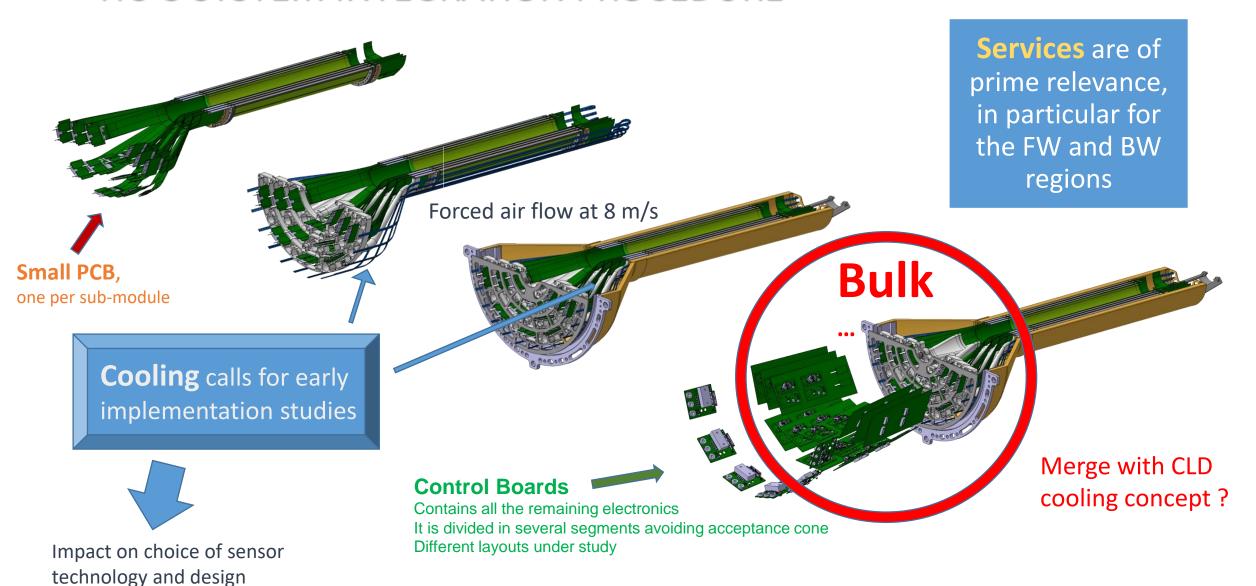

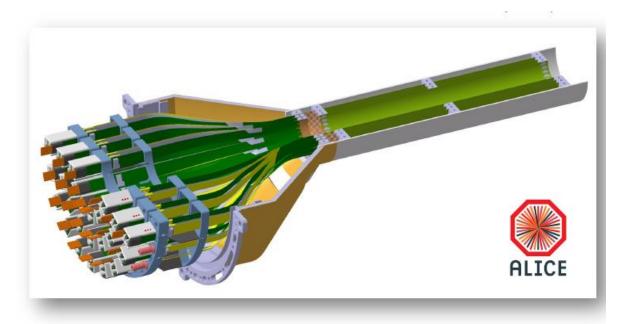

## **ITS-3 SYSTEM INTEGRATION STRATEGY and PROCEDURE**

## **ITS-3 SYSTEM INTEGRATION PROCEDURE**

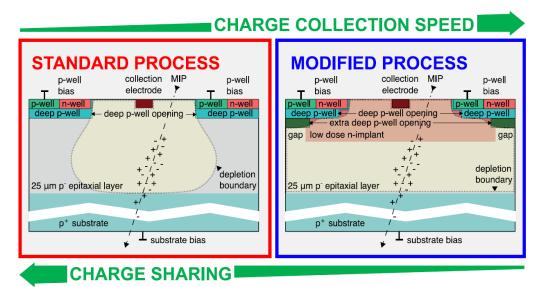

## **FAST CMOS SENSOR R&D**

#### R&D objectives:

- different for BG rejection and PID (ToF)

- depend on radius/surface (small vs large) of the detector to equip

- overlaps slightly (CMOS-)LGAD development

FASTPIX NIM A 1256 (2023) 168641

- FASTPIX: exploratory chip in TJsc 180 nm achieved O(100) ps time resolution with modified EPI

- Several prototypes fabricated in MLR-1 (TPSCo 65 nm) addressing HL-LHC and FCChh

- NAPA : CPS in TPSCo 65 nm for the C3 Higgs-Factory (goal ≈ 1 ns resolution with 25 μm pitch)

- ARCADIA: proto. device (CMOS LF-110) exploring r.o. circuitry options for future fast sensors equiping IDEA/FCCee

## SUMMARY -- OUTLOOK

- Significant progress during last years in the development of CPS & their use in expts (up to 10 m<sup>2</sup>):

- TJsc 180 nm process:

- gets more (full custom) applications beyond ALICE-ITS2 (ALPIDE): CBM/FAIR, Mu3e, Belle-II, ...: MIMOSIS-II for CBM may be a good seed for ILC

- also considered for sub-nanosecond sensor design (FastPix)

- used to investigate curved dices sensor mosaics (SuperAlpide)

& embedded sensor blades

- TPSCo 65 nm process seems validated for tracking devices, with limitations:

- small signal amplitude (thin EPI)

- spatial (& time ?) resolution, fill factor, yield with stitched sensors (for extra-low mat. budget)

- Most of the progress was achieved within the ITS-3 project:

- Validation of new CMOS technology (TPSCo-65) and assessment of its limits/consequences

- Pioneering design methology of wafer scale sensors using stitching rules of foundry (25 cm long CPS),

- Validation of curved, wafer-scale, thin sensor concept (material budget < 0.1 % Xo / layer),</li>

- Realisation of complete, very light, vertex detector design (mechanics, cooling) → impact on FW/BW regions

- Ccl:  $\sigma \approx 3 \, \mu m_s < 0.1 \, \% \, X_0/layer_s < 50 \, mW/cm^2$ ,  $\Delta t \approx O(100) \, ns$  in a single sensor is still a challenge (next slide)

- Sub-ns CMOS sensors: still in early stage of R&D (no large sensor), but promising perspectives identified

- CPS for calorimetry: R&D with TPSCo-65 pursued by several groups (prominent challenge: power suppression)

## COMMENT on SENSOR OPTIMISATION for the EW RUN

- Solution Achieving simultaneously  $\sigma \approx 3 \, \mu m_s < 0.1 \, \% \, X_0 / \, layer_s < 50 \, mW/cm^2$ ,  $\Delta t \approx O(100) \, ns$  within a single sensor seems unlikely with currently available CMOS technologies

- which parametres could be relaxed to preserve the most essential ones for phys.?

- Spatial resol. vs mat. budget: shorter sensors suspected to allow  $\sigma \approx 4.x \, \mu m$  (?) while preserving the asset of large stitched sensors to achieve < 0.1 % Xo / layer (tbc)

- should trigger R&D interest in the ILC community

- **Solution** Power vs  $\Delta t$  for the sake of air cooling at  $\sqrt{S}$  < HZ threshold:

- Higgs-top-EW factory Higgs, top, Z & T/QGC studies (HF comes in addition)

- EW running conditions at FCCee and Giga-Z (polar) are quite different because of the different beam time structures | low machine duty cycle (e.g. Giga-Z) allows to circumvent the conflict

- Double-sided ladders: spatial / time resol. optimised on either side at the expense of mat. budget

- R&D for the ALICE-3 project should provide valuable guidance

- Second Extensions of CMOS technology:

- 3D-sensors (stacking) for small areas (cost, yield!) but extra mat. budget (no bending?)

- More advanced CMOS process: e.g. 28 nm?

# **BACK-UP SLIDES**

### Wire Bonding MOSS on Carrier

**MOSS beam tests**: 1st analyses indicate a spatial resolution  $\approx 5-6 \, \mu m$  (binary charge encoding), close to pitch/ $\sqrt{12}$

- $\rightarrow$  follows from pixel dimensions (22.5 µm x 20.8 µm) constrained by stitching rule induced system architecture design

- → shorter sensors (e.g. 12 cm long) may allow for (somewhat) smaller pixels, i.e. better spatial resolution (tbc)

**Emblematic illustration** of the necessity of a global approach when designing a sensor (experienced designers needed)

# Stitching

# Circuits on wafer

## Thermal analysis: updating layout and power dissipation map

- Update of the thermal simulation model with latest modifications

- 1. Carbon foam position and half-layer dimension.

- Power dissipation map with all relevant components.

#### Updated power dissipation map

#### Computational model (ongoing)

Pixel matrix power dissipation is temperature dependent

→ Simulations will be performed

A compromise is going to be made (Mesh size Vs non-relevant area).

#### TPSCo 65nm: qualified for HEP (synergy between ALICE ITS3 and WP1.2)

- Fully efficient after 10<sup>15</sup> 1MeV n<sub>eq</sub> cm<sup>-2</sup>... at room temperature

- Transistor total ionizing dose tolerance doi: 10.1088/1748-0221/18/02/C02036 and SEU in line with other 65 nm technologies

- Many features not yet explored (wafer stacking, special imaging devices...)

## **ALICE ITS3 REQUIREMENTS**

#### 3 Cylindrical layers

Made with 6 curved wafer-scale single-die

Monolithic Active Pixel Sensors

Radii 18/24/30 mm, length 27 cm

Thinned down to <50 μm

Position resolution ~5 μm

-> Pixels Θ(20 μm)

#### Electro-mechanical integration

No flexible circuits in the active area

-> Distribute supply and transfer data on chip to the short edge

#### Cooling by air flow

-> Dissipate less than 20 mW/cm<sup>2</sup> (in sensitive area)

ALICE ITS3 LoI CERN-LHCC-2019-018 / LHCC-I-034

| Pb-Pb Interaction Rate | 50 kHz                                                    |  |  |

|------------------------|-----------------------------------------------------------|--|--|

| Particle Flux          | 2.2 MHz/cm <sup>2</sup>                                   |  |  |

| Integration time       | < 10 µs                                                   |  |  |

| TID                    | <10 kGy                                                   |  |  |

| NIEL                   | 1×10 <sup>13</sup> 1 MeV n <sub>eq</sub> cm <sup>-2</sup> |  |  |

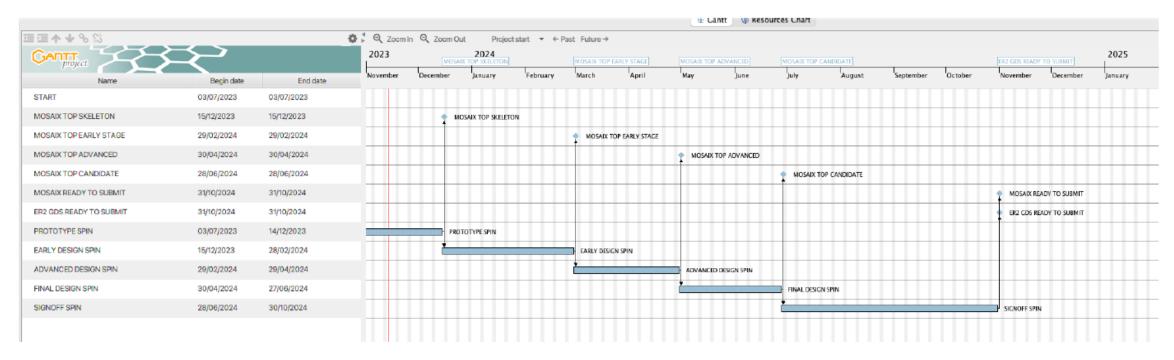

## MOSAIX DESIGN MILESTONES

Design completion (full GDS): 28/06/2024

Final signoff spin and corrections: July-October

Submission: October 2024