## SCIPP R&D on Long Shaping-Time Electronics

SLAC SiD Workshop October 26-28, 2006 Bruce Schumm

### The SCIPP/UCSC ILC HARDWARE GROUP

Faculty/Senior Post-Docs Students

Vitaliy FadeyevJurgen KrosebergGreg HornAlex GrilloGabriel Saffier-Bruce SchummEwingAbe SeidenSeiden

Lead Engineer: Ned Spencer Technical Staff: Max Wilder, Forest Martinez-McKinney

(Students are undergraduates from physics)

# Alternative: shorter ladders, but better point resolution

The LSTFE approach would be well suited to use in short-strip applications, and would offer several potential advantages relative to other approaches

- Optimized for LC tracking (less complex)

- More efficient data flow

- No need for buffering

Would require development of 2000 channel chip w/ bump bonding (should be solved by KPiX development)

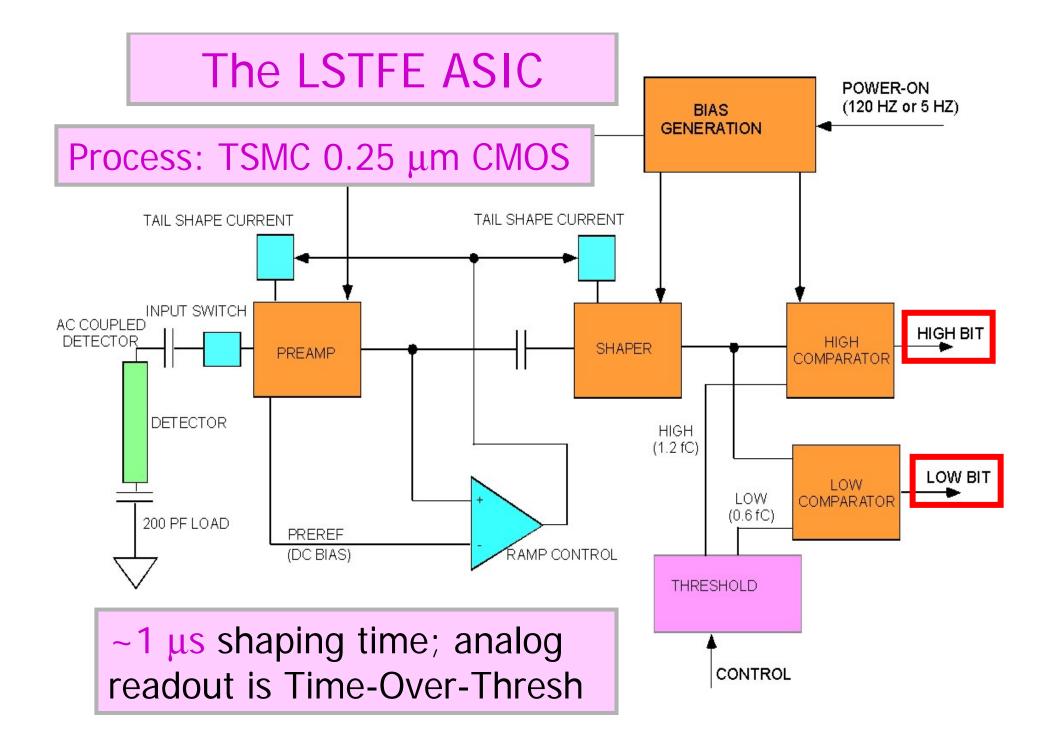

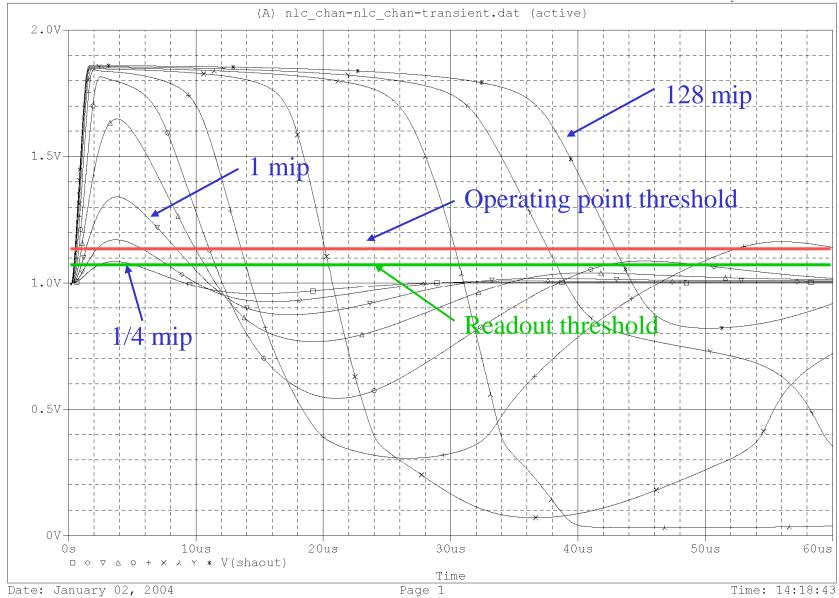

## **Electronics Simulation**

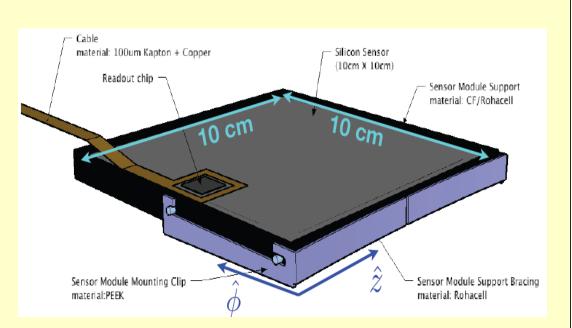

#### **Detector:**

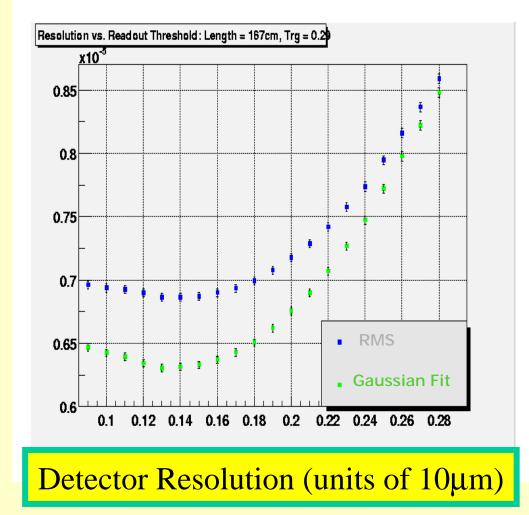

167 cm ladder, 50 μm pitch, 50 μm readout

#### Analog Measurement:

Employs time-overthreshold with 400 ns clock period; lookup table provides conversions back into analog pulse height (as for actual data)

Essential tool for design of front-end ASIC

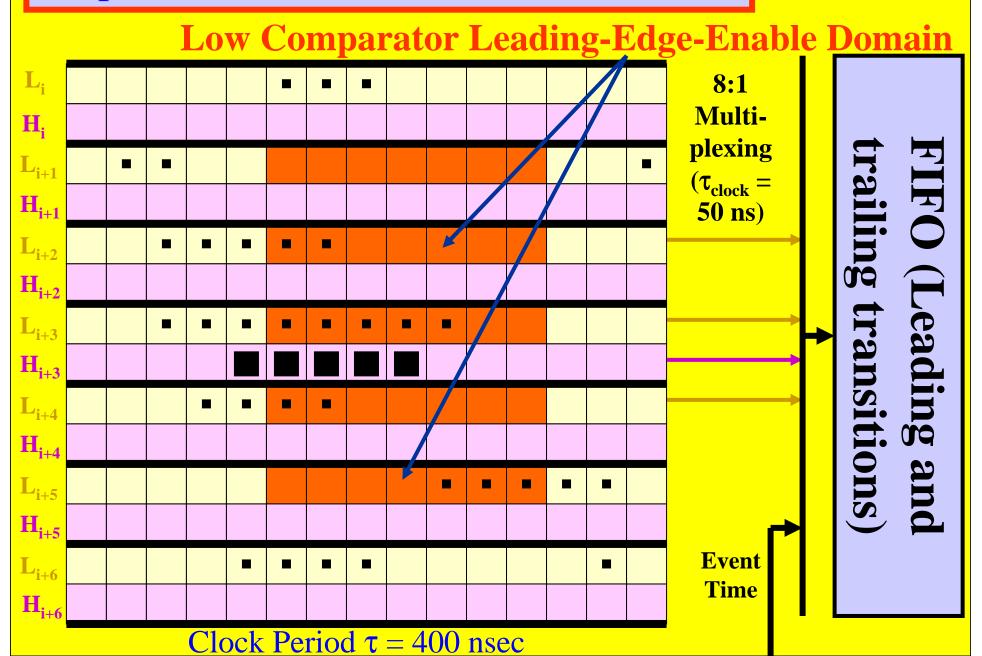

#### Proposed LSTFE Back-End Architecture

## DIGITAL ARCHITECTURE: FPGA DEVELOPMENT

Design permits real-time accumulation and readout of hit information, with dead time limited only by amplifier shaping time

## **INITIAL RESULTS**

## LSTFE-2 chip mounted on readout board

FPGA-based control and dataacquisition system

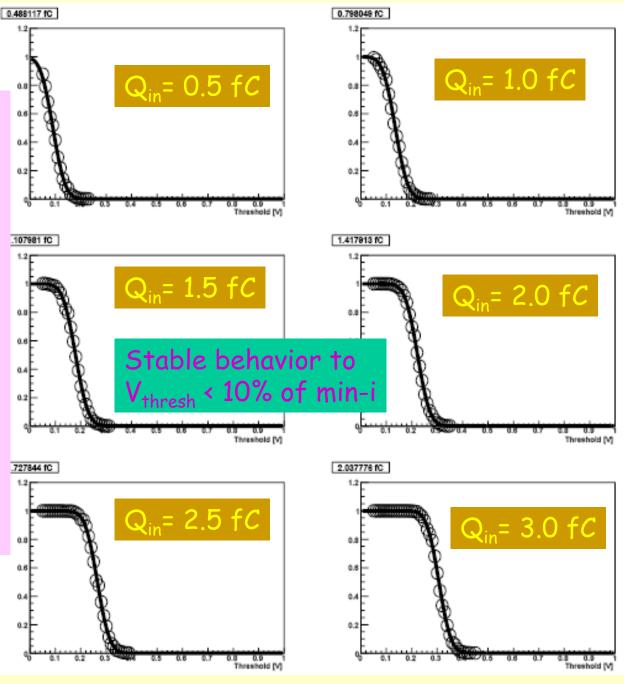

#### Comparator S Curves

Vary threshold for given input charge

Read out system with FPG-based DAQ

Get

1-erf(threshold)

with 50% point giving response, and width giving noise

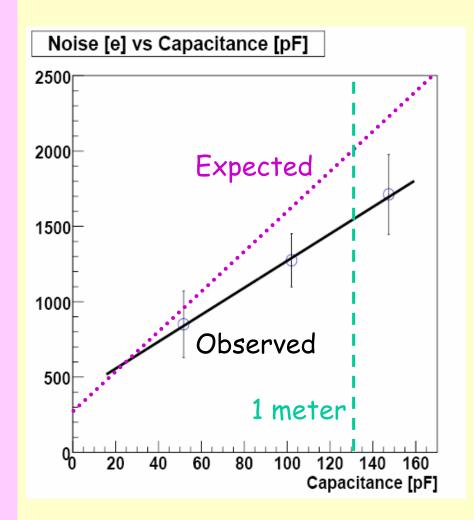

Noise vs. Capacitance (at  $\tau_{shape}$  = 1.2 µs)

Loaded with Capacitor Measured dependence is (noise in equivalent electrons)  $\sigma_{noise} = 375 + 8.9 C$ with C in pF.

#### Connected to Ladder

Noise is approximately 30% worse; are currently exploring long shaping-time shielding requirements

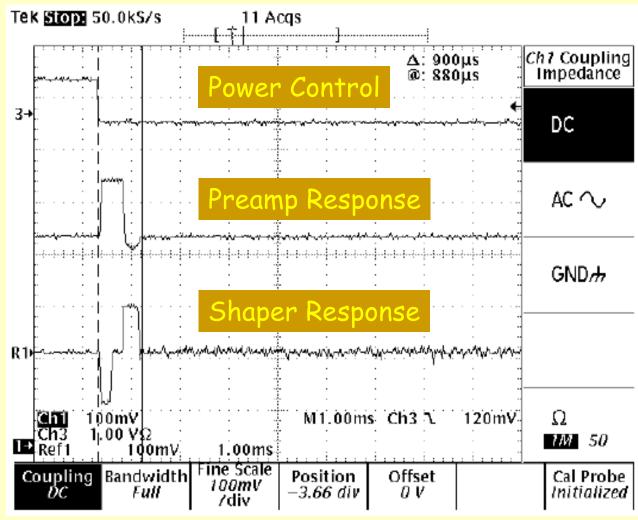

## **Power Cycling**

• As designed: Achieve 40 msec turn-on due to protection diode leakage

• Injecting small (< 1nA) current: Achieve 0.9 msec

LSTFE2 will incorporate active feedback to maintain bias levels of isolated circuitry when chip is "off".

The LSTFE2 is currently under development; submission expected by end of year

- Retain 1.0-1.5  $\mu s$  shaping time

- Further S/N optimization (still geared towards long ladders)

• "Off" state feedback to achieve power cycling goal (< 1 msec switch-on)

64-128 channels, with multiplexing of comparator outputs (pad geometry)