## Chronopixel development status

Nick Sinev, University of Oregon, On behalf of: C. Baltay, W.Emmet, H.Neal, D.Rabinovich – Yale University, J.Brau, O.Igonkina, D.Strom – University of Oregon

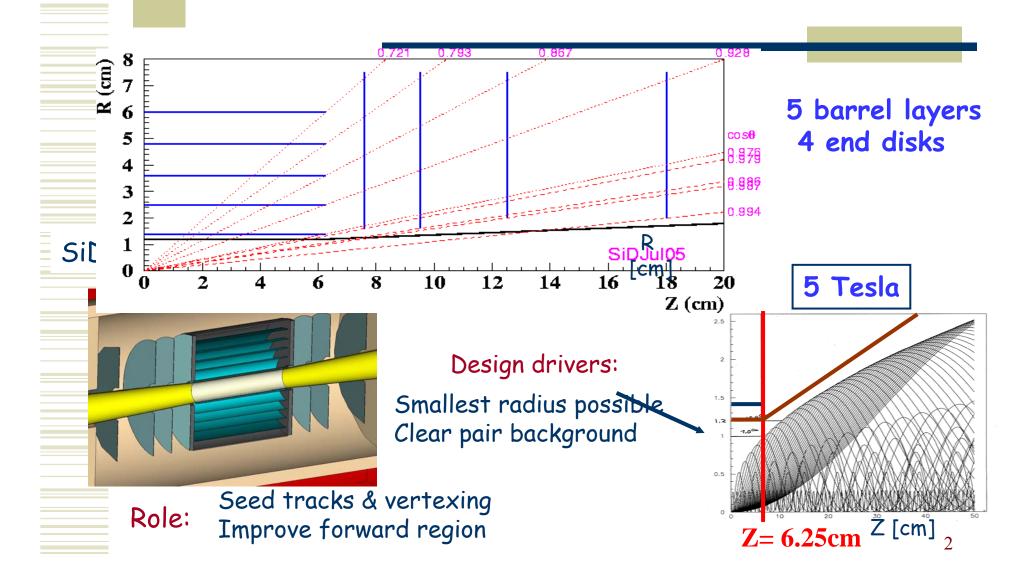

### SiD Vertex Layout

## SiD Vertex Detector

| BARREL |  |

|--------|--|

|--------|--|

- 100 sensors

- 1750 cm<sup>2</sup>

| Layer | Radius | Total Length | No. of Chips | Chin Size        |

|-------|--------|--------------|--------------|------------------|

| Layer |        | 0            | rto. or emps | -                |

|       | (cm)   | (cm)         |              | $(cm^2)$         |

| 1     | 1.4    | 12.5         | 12           | $12.5{	imes}1.2$ |

| 2     | 2.5    | 12.5         | 24           | $12.5{	imes}1.2$ |

| 3     | 3.6    | 12.5         | 20           | $12.5{	imes}2.2$ |

| 4     | 4.8    | 12.5         | 20           | $12.5{	imes}2.2$ |

| 5     | 6.0    | 12.5         | 24           | $12.5{	imes}2.2$ |

Table I: CMOS Detector Barrel Configuration

#### Table II: CMOS Detector Forward Disk Configuration

| Annulus | Inner Radius | Z    | No. of Chips | Chip Size        |

|---------|--------------|------|--------------|------------------|

|         | (cm)         | (cm) |              | $(cm^2)$         |

| 1       | 1.6          | 7.6  | 24           | $1.5{	imes}0.9$  |

|         | 3.1          | 7.6  | 24           | $4.4 \times 2.2$ |

| 2       | 1.6          | 9.5  | 24           | $1.5{	imes}0.9$  |

|         | 3.1          | 9.5  | 24           | $4.4 \times 2.2$ |

| 3       | 2.0          | 12.5 | 24           | $1.1{	imes}0.9$  |

|         | 3.1          | 125  | 24           | $4.4 \times 2.2$ |

| 4       | 2.0          | 18.0 | 24           | $1.1{	imes}0.9$  |

|         | 3.1          | 18.0 | 24           | $4.4 \times 2.2$ |

FORWARD

- 288 sensors

- 2100 cm<sup>2</sup>

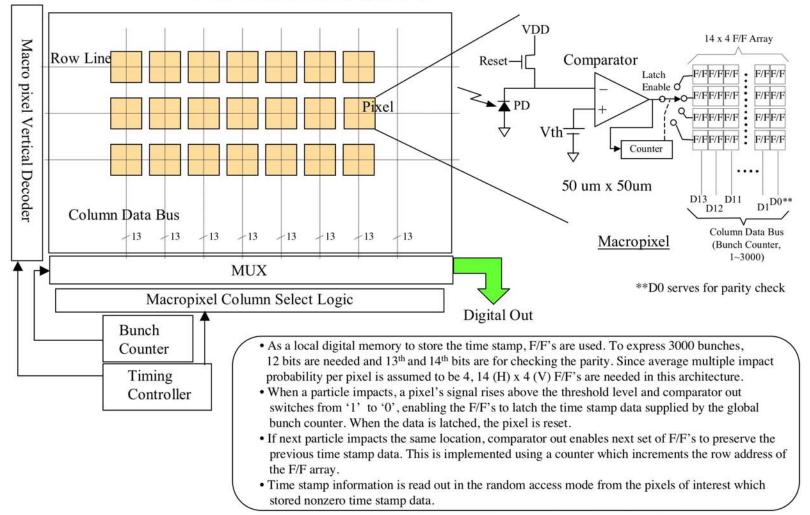

### Macropixel Array Architecture

4

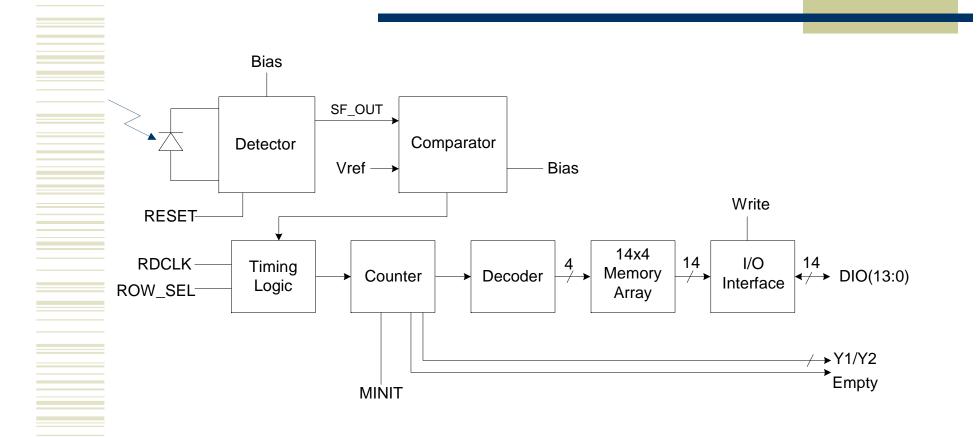

### **Macropixel Block Diagram**

# Read Noise

- Minimum ionizing particle leaves ~ 88e<sup>-</sup> /micron in epitaxial layer

- 15 um thick epi layer 1% inefficiency threshold 375 e<sup>-</sup>, 50% hit sharing 188 e<sup>-</sup>, noise =  $\frac{1}{4} \times 188 = 47 e^{-1}$

- Readout noise scales with pixel capacitance: with 12 μm depletion depth it is 22 fF for 50x50 μm pixels and 3.5 fF for 20x20 μm pixels.

- Electronics noise estimation for 3.5  $fF 32 e^{-1}$

# Power Consumption

Main power consumer is analog part (amplifier + comparator). However, we do not need to keep it all time on. Current estimation for 50x50  $\mu$ m design (0.25  $\mu$ m technology) 15mW/mm<sup>2</sup> (without taking into account duty cycle) for analog part and 0.05 mW/mm<sup>2</sup> for digital part. Assuming duty cycle for analog parts as 1/100 we get ~0.16 mW/mm<sup>2</sup>.

By conservative estimates power per unit of device area will not change by going to smaller pixel size with more advanced technology (goal - 0.045µm feature size by 2010). This is because reduction in capacitance allows smaller current in amplifier.

So, we expect ~ 0.16 mW/mm<sup>2</sup> x 2500 mm<sup>2</sup> chip = 0.4 W / chip.

# Power Dissipation Analysis

|         | Component       | Optimized<br>Power Dissipation | Before<br>Optimization |

|---------|-----------------|--------------------------------|------------------------|

|         | Detector        | 9.9uW                          | 11.7uW                 |

| Analog  | Comparator      | 27.0uW                         | 35.1uW                 |

|         | Sub_tota1       | 36.9uW                         | 46.8uW                 |

|         | Timing Logic    | 0.05uW                         |                        |

|         | Counter/Decoder | 0.07uW                         |                        |

| Digital | Mem. Array      | $\sim 0 \mathrm{uW}$           |                        |

|         | IO Interface    | 0.01uW                         |                        |

|         | Sub_tota1       | 0.13uW                         |                        |

|         | Total           | 37.03uW                        |                        |

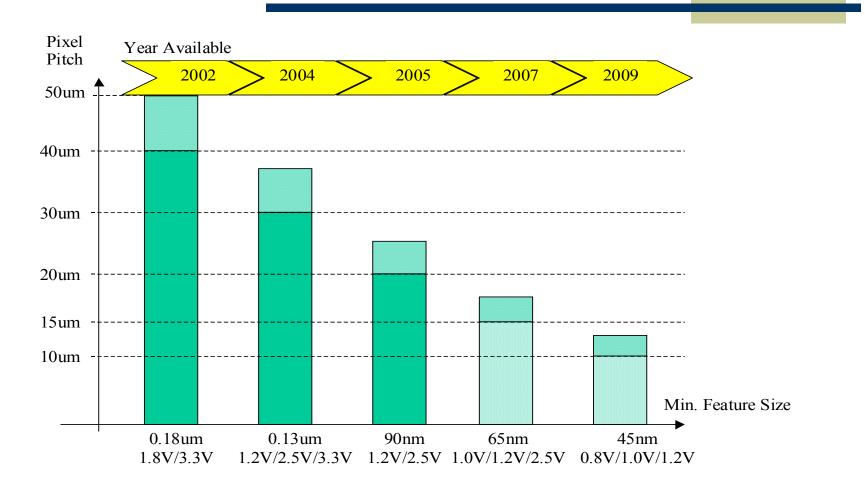

SARNOFF Response to Question on Future Technology Roadmap: Macropixel size estimation vs. Mixed-signal Process Technologies

# CONCLUSION

- Completed chronopixel design

- 645 transistors

- Spice simulation verifies design

- TSMC 0.18 um -> 40-50 um pixel

- Next phase under consideration

- Complete design of macro pixel

- Deliverable –tape out for foundry

- Future

- Fab 50 um pixel chip

- Then, 10-15 um pixel