# Update on KPiXs

David Strom – University of Oregon

- Introduction

- Latest results

- Plans

#### Si-W work – personnel and responsibilities

| Y. Karyotakis | V. Radeka   | B. Holbrook<br>R. Lander<br>M. Tripathi | J. Brau<br>R. Frey<br>D. Strom          | M. Breidenbach<br><b>D. Freytag</b> , N. Graf<br><b>G. Haller, R. Herbst</b><br>T. Nelson |

|---------------|-------------|-----------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------|

| Annecy        | BNL         | UC-Davis                                | Oregon*                                 | SLAC                                                                                      |

| Mechanics     | Electronics | Bump Bonding<br>Cabling<br>Mechanics    | Si Detectors<br>Mechanics<br>Simulation | Electronics<br>Mechanics<br>Simulation                                                    |

\* This work includes contributions from Oregon students Mary Robinson and Asher Tubman.

1

26 October 2006 – David Strom – UO

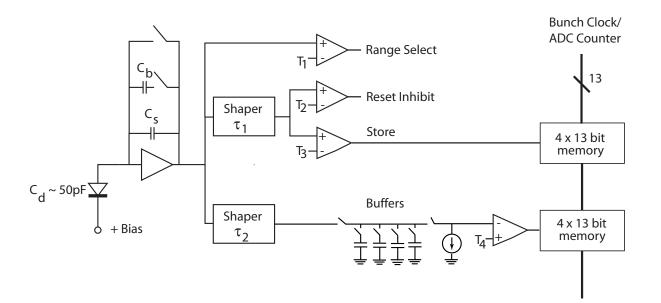

# Extremely Simplified Schematic

- KPiX can store up to four four pairs of analog charges and time stamps per train

- Low noise performance at output of shaper paramount

- Digitization occurs during between trains

- Novel scheme feedback scheme used to get 16 bit dynamic range ( $C_b = 25 \times C_s$ )

2

$\bullet$  Range switching occurs at about 1V

New Features on KPiX 3

- Improved Analog/Digital isolation

- Polarity switching (not shown)

- External trigger for test beam use

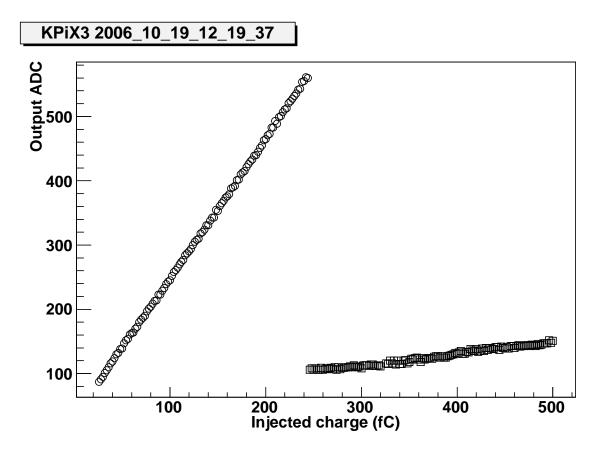

## Novel Feature works:

Range switching level adjusted to occur at 200 fC rather than 400 fC for illustration.

4

Shows whole chain works properly.

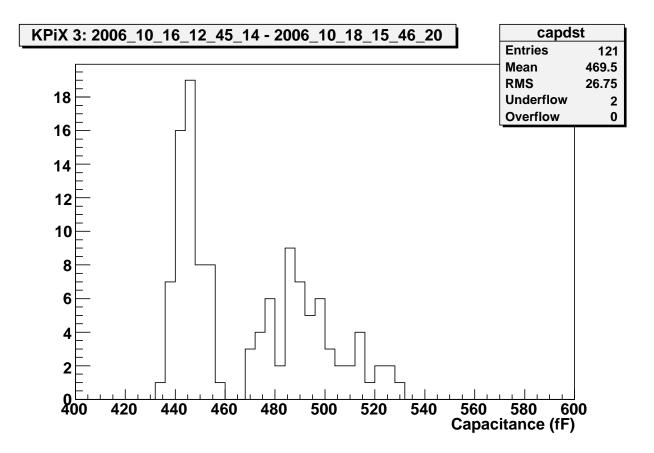

One can adjust the range threshold to measure the charge amp gain, or equivalently the size of its feedback capacitor

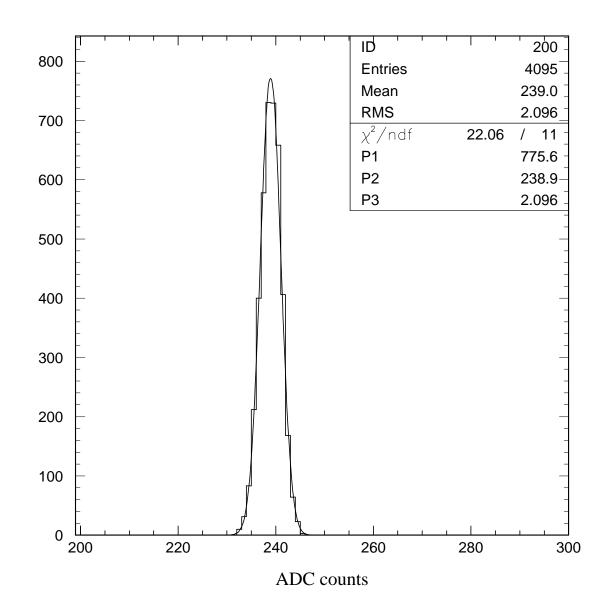

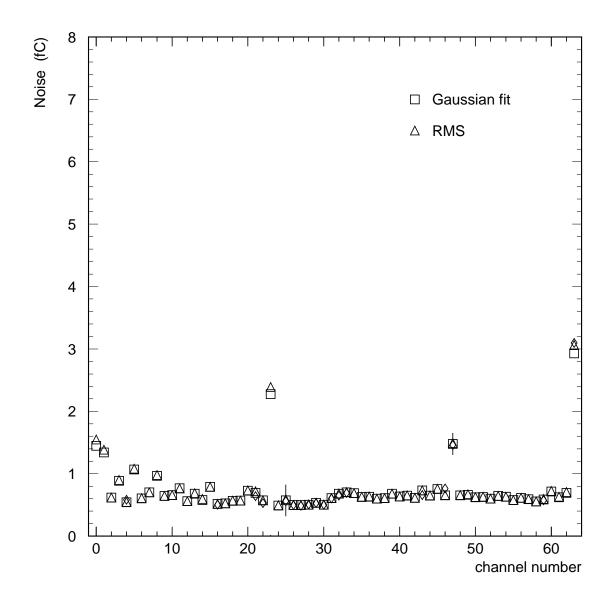

Typical noise in the ADC corresponds to less than 1 fC.

26 October 2006 – David Strom – UO

Some of the outliers are channels with extra connections.

26 October 2006 – David Strom – UO

#### Status

- Still optimizing digital timing of control signals on chip (most things are adjustable).

- Initial tests are done with many internal digital and some internal analog signals brought out for testing

- This allows the design of the chip to be verified, but interferes with low noise testing

- $\Rightarrow$  Have not yet verified expected low noise performance for small signals

8

Fabrication Plans

Submit KPiX4 soon (Nov 15?):

- Improved shaper

- Better current sources for ADCs

- Nearest neighbor logic for tracking

- Improved analog/digital buffering.

- $\Rightarrow$  Allows for much lower digital voltage.

Move to KPiX 1024 when operation of KPiX4 is demonstrated. May require KPiX5.

9