# SiLC ELECTRONICS R&D currently concentrating on the FEE

Two approaches

The TOT approach

The DSM FE and readout electronics

# SCIPP R&D on Time-Over-Threshold Electronics and Long-Ladder Readout

Beijing Linear Collider Workshop Beijing, China

**February 4-8 2007**

**Bruce Schumm**

# The SCIPP/UCSC SiLC/SiD GROUP (Harwdare R&D Participants)

Faculty/Senior

Post-Docs

**Undergrads**

Vitaliy Fadeyev

Alex Grillo

Bruce Schumm

Jurgen Kroseberg Lei Wang Greg Horn Luke Kelley Patrick Au

**Lead Engineer: Ned Spencer**

Technical Staff: Max Wilder, Forest Martinez-McKinney

All participants are mostly working on other things (BaBar, ATLAS, biophysics...)

Students are undergraduates from physics and engineering

#### **FOCUS AND MILESTONES**

Goal: To develop readout generically suited to any ILC application (long or short strips, central or forward layers)

Current work focused on long ladders (more challenging!):

- · Front-end electronics for long (>1 meter) ladders

- · Exploration of sensor requirements for long ladders

- Demonstration (test-beam) of  $< 10 \mu m$  resolution mid-2008

After long-ladder proof-of-principle, will re-optimize (modest changes) for short-strip, fast-rate application

We also hope to play an increasing role in overall system development (grounding/shielding, data transmission, module design and testing) as we have on ATLAS and GLAST

#### **BRIEF SUMMARY OF STATUS**

Testing of 8-channel (LSTFE-1) prototype fairly advanced:

- Reproducible operation (4 operating boards)

- Most features working, with needed refinements understood

- ·A number of "subtleties" (e.g. channel matching, environmental sensitivity) under control

- ·Starting to make progress on fundamental issues confronting long-ladder/high-resolution limit.

Design of 128-channel prototype (LSTFE-2) well underway (April submission)

Now for the details...

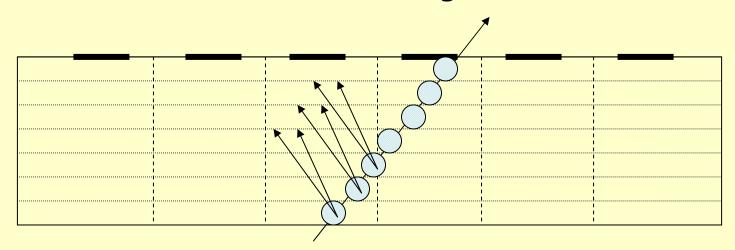

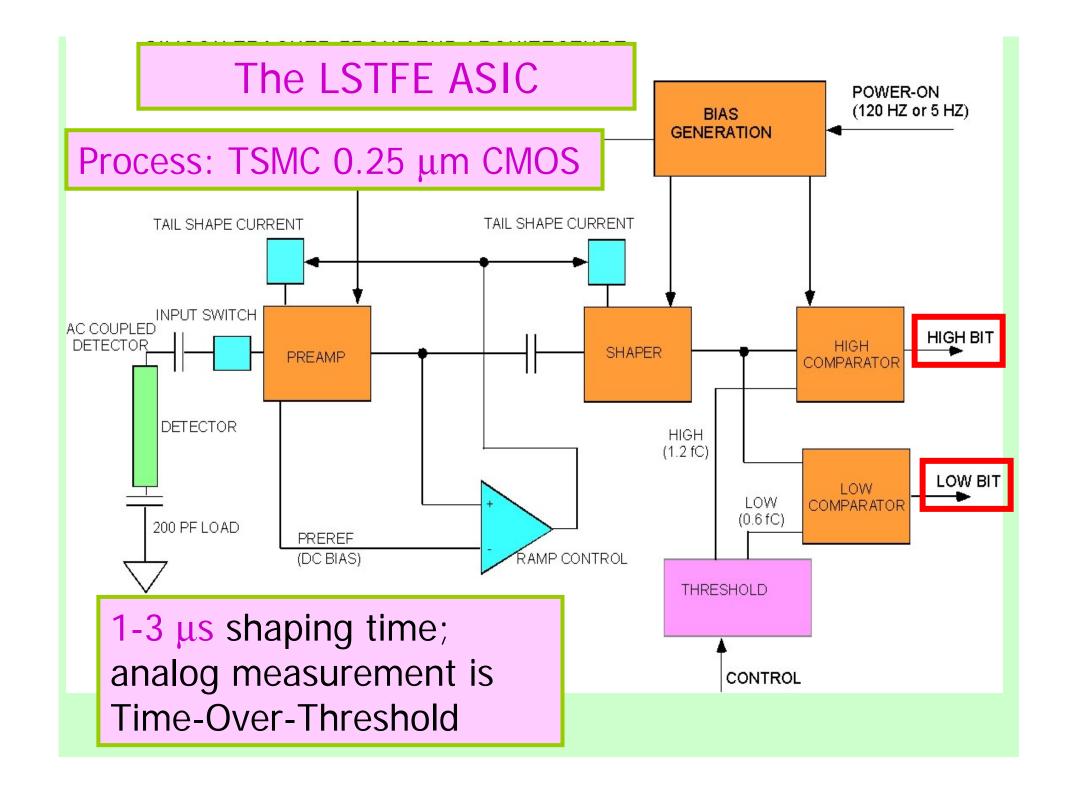

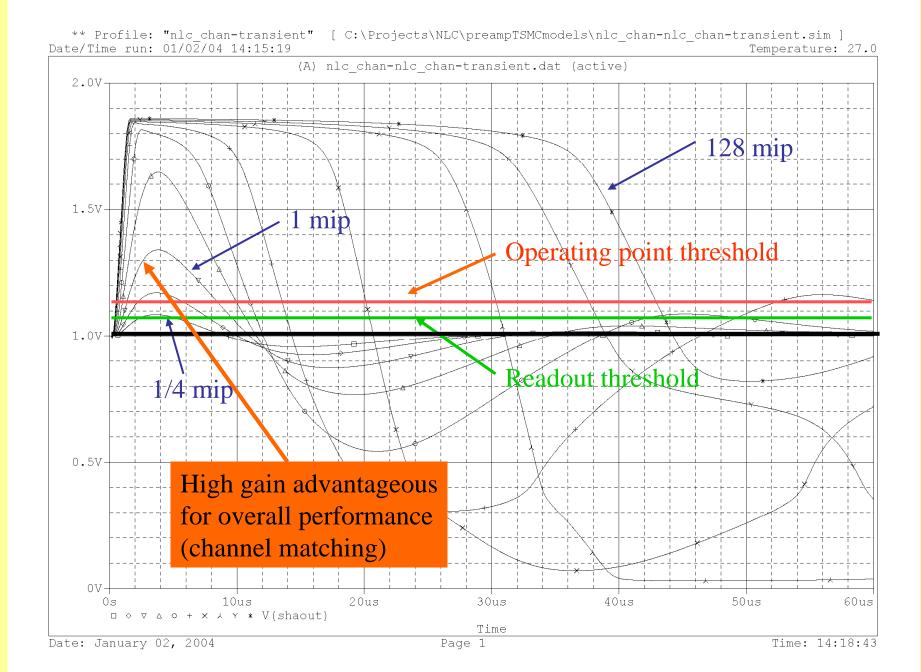

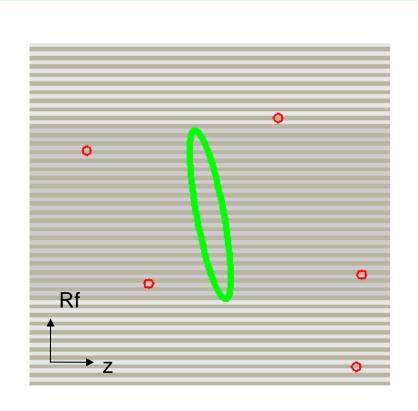

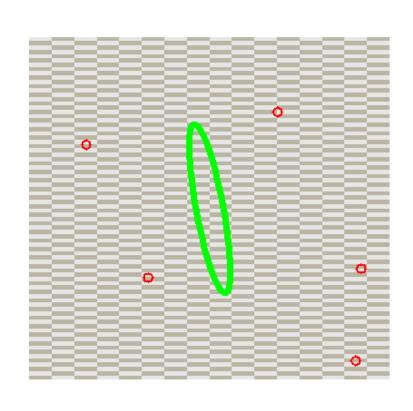

## Pulse Development Simulation

Christian Flacco & Michael Young (Grads); John Mikelich (Undergrad)

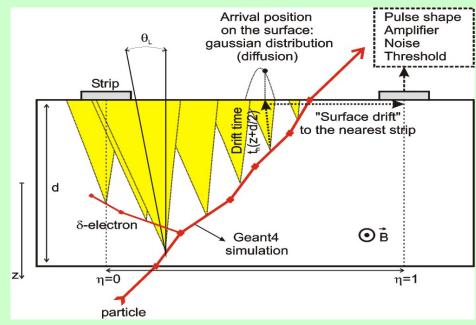

Long Shaping-Time Limit: strip sees signal if and only if hole is collected onto strip (no electrostatic coupling to neighboring strips)

Include: Landau deposition (SSSimSide; Gerry Lynch LBNL), variable geometry, Lorentz angle, carrier diffusion, electronic noise and digitization effects

# Simulation Result: S/N for 167 cm Ladder (capacitive noise only)

Simulation suggests that long-ladder operation is feasible

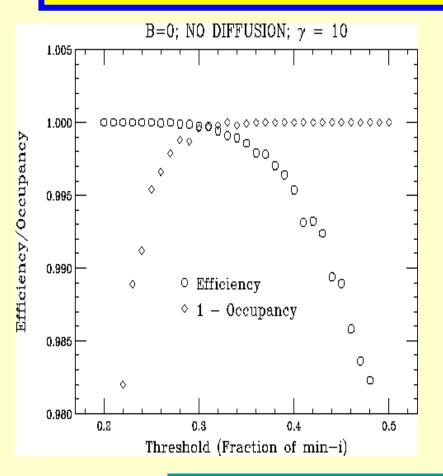

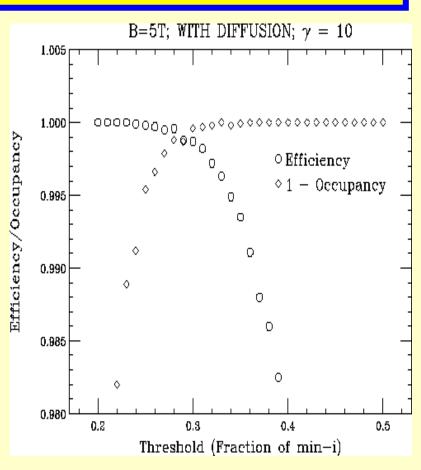

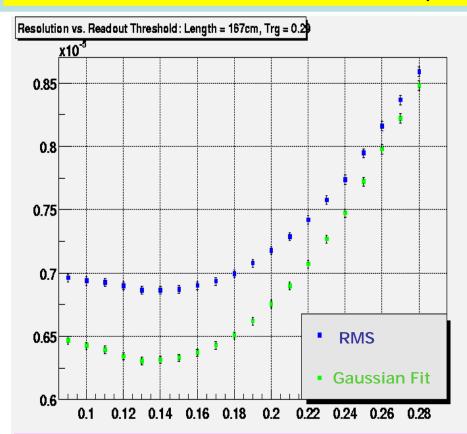

#### **Electronics Simulation: Resolution**

#### **Detector Noise:**

Capacitive contribution; from SPICE simulation normalized to bench tests with GLAST electronics

#### **Analog Measurement:**

Provided by time-overthreshold; lookup table provides conversions back into analog pulse height (as for actual data)

#### Detector Resolution (units of 10µm)

Lower (read) threshold in fraction of min-i (High threshold is at 0.29 times min-i)

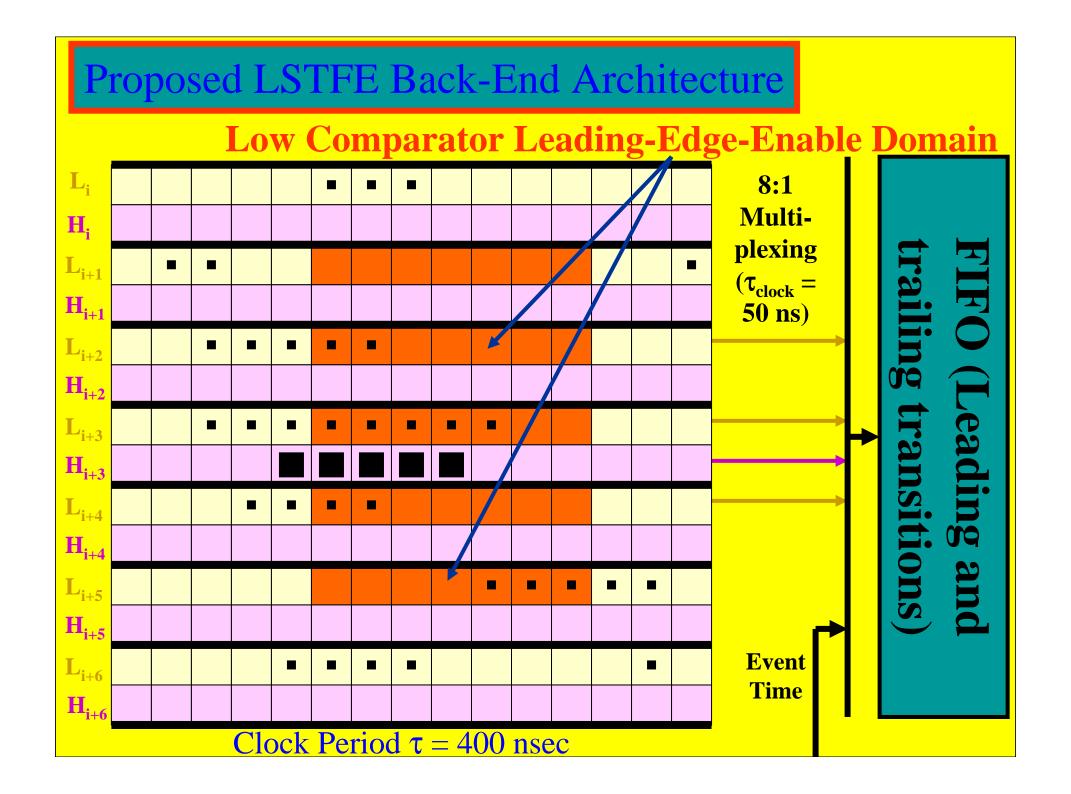

### DIGITAL ARCHITECTURE: FPGA DEVELOPMENT

Digital logic under development on FPGA (Wang, Kroseberg), will be included on front-end ASIC after performance verified on test bench and in test beam.

#### Note on LSTFE Digital Architecture

Use of time-over-threshold (vs. analog-to-digital conversion) permits real-time storage of pulse-height information.

- → No concern about buffering

- → LSTFE system can operate in arbitrarily high-rate environment; is ideal for (short ladder) forward tracking systems as well as long-ladder central tracking applications.

#### DIGITAL ARCHITECTURE SIMULATION

ModelSim package permits realistic simulation of FPGA code (signal propagation not yet simulated)

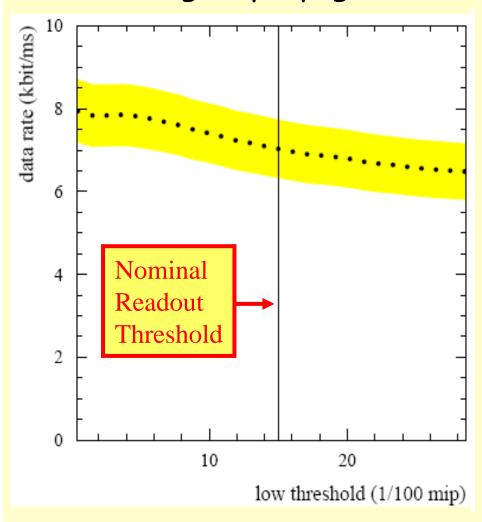

Simulate detector background (innermost SiD layer) and noise rates for 500 GeV running, as a function of readout threshold.

Per 128 channel chip ~ 7 kbit per spill → 35 kbit/second

For entire SiD tracker ~ 0.5-5 GHz data rate, depending on ladder length (x100 data rate suppression)

#### **INITIAL RESULTS**

LSTFE chip mounted on readout board

FPGA-based control and data-acquisition system

#### Note About LSTFE Shaping Time

Original target:  $\tau_{shape}$  = 3 µsec, with some controlled variability ("ISHAPR")

→ Appropriate for long (2m) ladders

In actuality,  $\tau_{shape}$  ~ 1.5 µsec; tests are done at 1.2 µsec, closer to optimum for SLAC shortladder approach

Difference between target and actual shaping time understood in terms of simulation (full layout)

LSTFE-2 will have 3 µsec shaping time

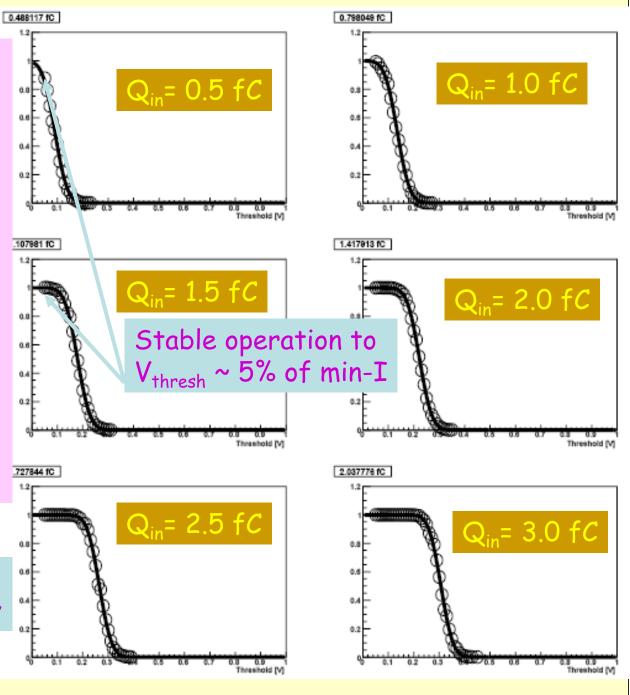

#### Comparator S Curves

Vary threshold for given input charge

Read out system with FPG-based DAQ

Get

1-erf(threshold)

with 50% point giving response, and width giving noise

Hi/Lo comparators function independently

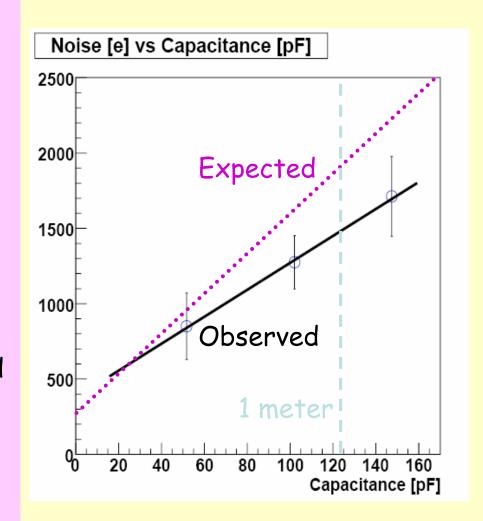

#### **EQUIVALENT CAPACITANCE STUDY**

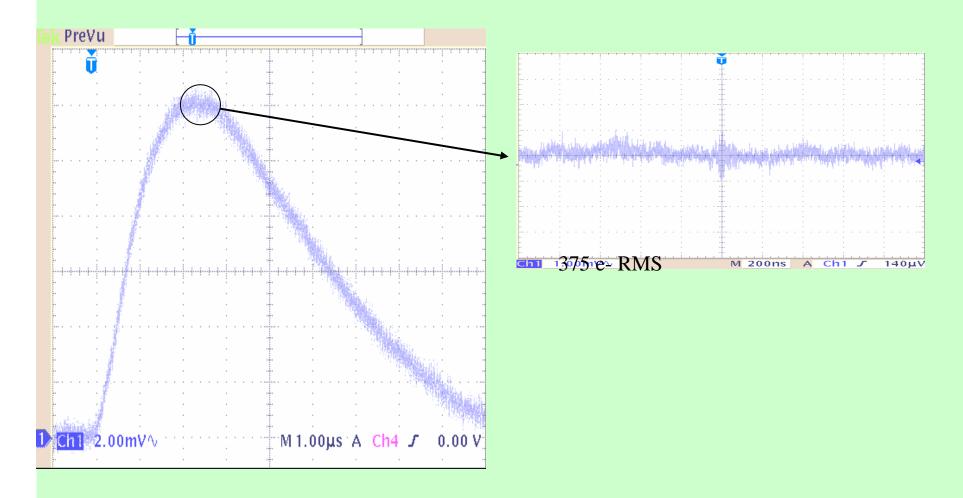

Noise vs. Capacitance (at  $\tau_{shape}$  = 1.2  $\mu s$ )

Measured dependence is roughly (noise in equivalent electrons)

$$\sigma_{\text{noise}} = 375 + 8.9 * C$$

with C in pF.

Experience at 0.5  $\mu m$  had suggested that model noise parameters needed to be boosted by 20% or so; these results suggest 0.25  $\mu m$  model parameters are accurate

→ Noise performance somewhat better than anticipated.

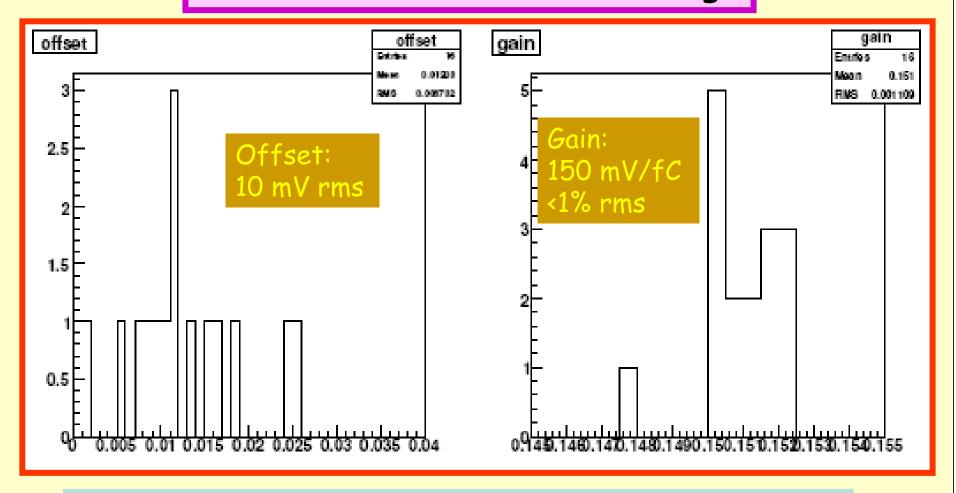

#### Channel-to-Channel Matching

Occupancy threshold of 1.2 fC (1875  $e^-$ )  $\rightarrow$  180 mV

- ± 2 mV (20 e-) from gain variation

- ± 10 mV (100 e<sup>-</sup>) from offset variation

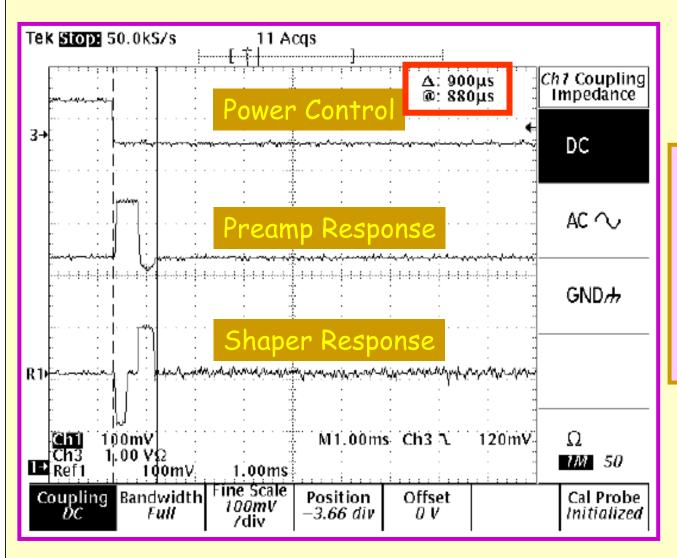

#### Power Cycling

Idea: Latch operating bias points and isolate chip from outside world.

- Per-channel power consumption reduces from ~1 mW to ~1  $\mu$ W.

- · Restoration to operating point should take ~ 1 msec.

#### Current status:

- Internal leakage (protection diodes + ?) degrades latched operating point

- Restoration takes ~40 msec (x5 power savings)

- Injection of small current (< 1 nA) to counter leakage allows for 1 msec restoration.

#### Future (LSTFE-2)

Low-current feedback will maintain bias points;

solution already incorporated in LSTFE-2 design

#### Power Cycling with Small Injected Current

Solution in hand to maintain bias levels in "off" state with low-power feedback; will eliminate need for external trickle current

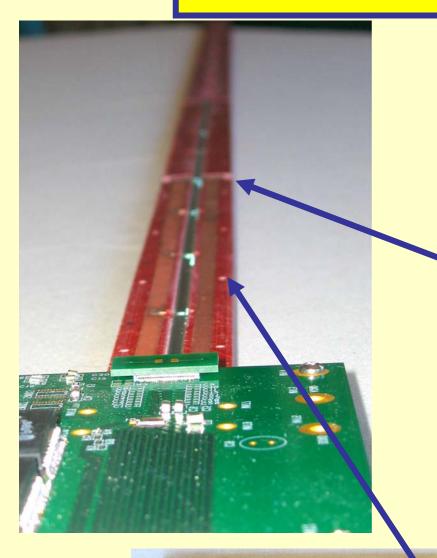

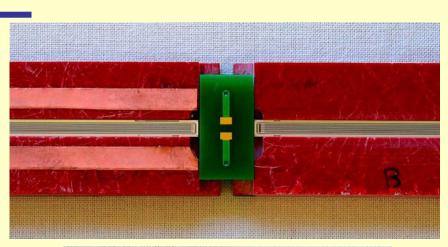

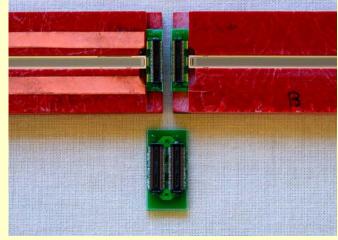

# LONG LADDER CONSTRUCTION

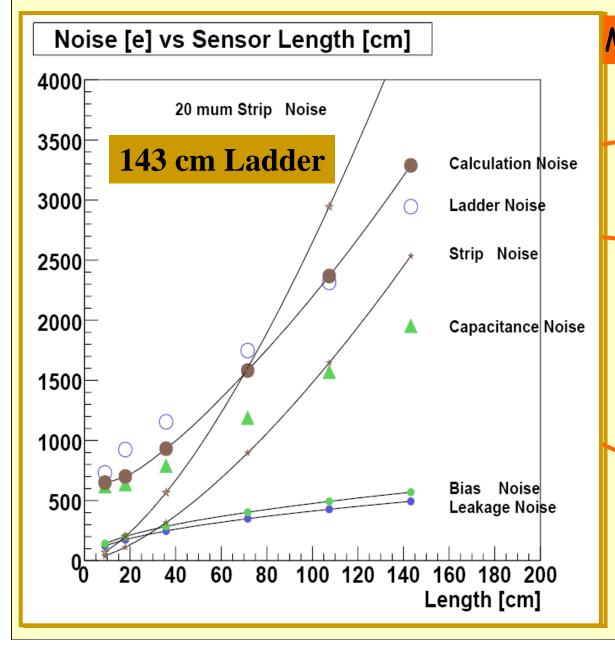

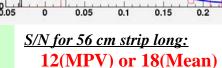

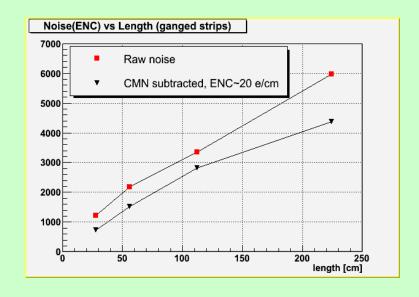

#### LONG LADDER EXPERIENCE

A current focus of SCIPP activity

Using GLAST "cut-off" (8 channel) sensors; 237  $\mu$ m pitch with 65  $\mu$ m strip width

Have now studied modules of varying length, between 9cm and 72cm. [2/1/07: Now have up to 143 cm...]

Measure inputs to estimate noise sources other than detector capacitance:

Leakage current 1.0 nA/cm

• Strip resistance  $3.1 \Omega/cm$

• Bias resistance  $35 M\Omega$  per sensor

All of these should be considered in module design!

Strip resistance for fine pitch could be an issue  $\rightarrow$  are starting careful study and considering options  $\rightarrow$  feedback to detector/module design.

#### Measured Noise vs. Sum of Estimated Contributions

Measured noise

Sum of estimates

Projected Johnson noise for 20 µm strip (not part of estimate)

Estimated Johnson noise for actual 65 µm strip (part of estimate)

#### TIME-OVER-THRESHOLD READOUT SUMMARY

#### The LSTFE readout system is:

- · Universally applicable (long strips, short strips, central, forward, SiD, LDC, GLD, 4<sup>th</sup>...)

- Rigorously optimized for ILC tracking

- · Relative simple (reliability, yield)

- · In a relatively advanced stage of development

- Is now being used as an instrument to understand fundamental principles of long ladder operation, particularly for narrow strips (CDF Layer00 sensors available, being qualified)

# Front-End Digitized Readout using Deep Sub-Micron Technologies: SiTR-XXX chips

```

<sup>2</sup> J. David, <sup>2</sup> M. Dellhot, D. Fougeron, <sup>1</sup>J.F. Genat <sup>2</sup>, R. Hermel <sup>1</sup>, H. Lebbolo<sup>2</sup>, T.H. Pham <sup>2</sup>, F. Rossel <sup>2</sup>, A. Savoy-Navarro <sup>2</sup>, R. Sefri <sup>2</sup>, S. Vilalte <sup>1</sup>

```

<sup>1</sup>LAPP Annecy, <sup>2</sup>LPNHE Paris

And also the collaboration of IMEC-Leuven (Europractice)

E. Deumens, P Malisse

Presently joining Institutes: University of Barcelona & University Ramon Llull IFCA-CSIC/University of Cantabria

Increasing collaborative contacts with CERN

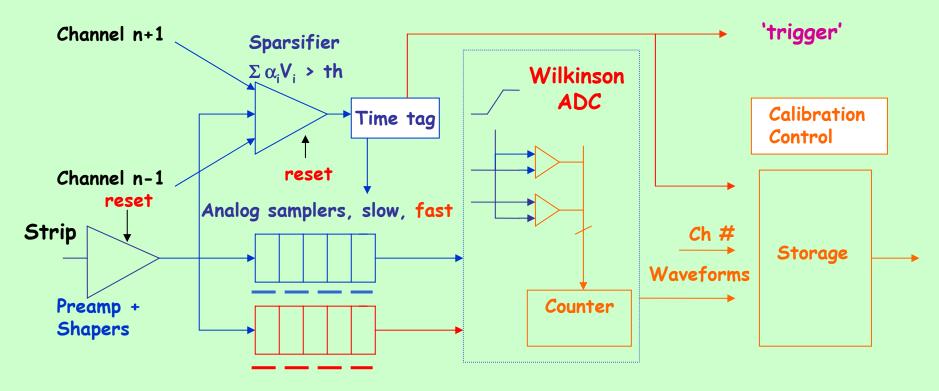

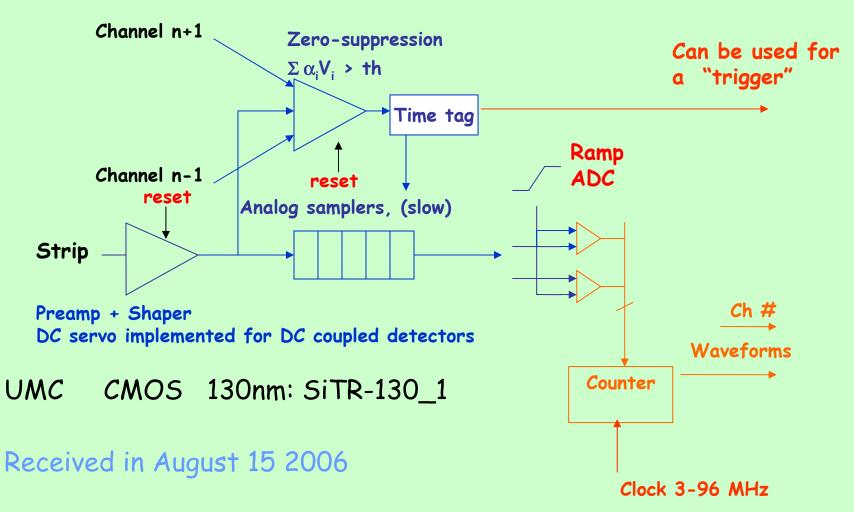

# SiTR chips data processing

• Pulse height: Cluster centroid to get a few  $\mu$ m position resolution Detector pulse analog sampling

Time: Two scales:

Coarse: 150-300 ns for BC identification, 80ns sampling

Shaping time of the order of the microsecond

Fine: nanosecond timing for the coordinate along the strip

10ns sampling

Not to replace another layer or double sided Position estimation to a few cm using pulse reconstruction from samples

Shaping time: 20-50 ns

# Technologies

Silicon detector and VLSI technologies allow to improve detector and front-end electronics integration

#### Front-end chips:

- Thinner CMOS processes 250, 180, 130, 90 nm now available

- SiGe, less 1/f noise, faster

- Chip thinning down to 50 μm

More channels on a chip, more functionalities, less power

#### Connectivity:

- On detector bump-bonding (flip-chip)

- **3**D

Smaller pitch detectors, better position and time resolution. Less material

# SiTR chips integrated functionalities

- Full readout chain integration in a single chip

- Preamp-shaper

- Trigger decision (sparsification with analog sums): \_\_ compact data

- Sampling: Analog pipe-lines

- On-chip digitization (highly multiplexed)

- Buffering

- Digital Processing: Centroids and Least Squares time/amplitude estimation

- Calibration and calibration management

- Power switching

- First production series will be based on 128 channels/chip; the goal is to go to 1024 (or at least 512) channels.

## SiTR Front-End readout Chip goals:

Integrate 512-1024 channels in 90nm CMOS:

```

> Charge Amplifiers: 20-30 mV/MIP over 30 MIP

```

> Shapers: - slow 500 ns - 2 μs

- fast 20-50 ns

> Zero-suppression: threshold the sum of adjacent channels

> 2D analog memory: - 8-16 samples

80 ns and 10 ns sampling clocks

- Event buffer 16-deep

> ADC: 10 bits

> Buffering

> Calibration

> Power switching saves a factor 100-200

ILC timing: 1 ms: ~ 3-6000 trains @150-300ns / BC200ms in between

# SiTR chips Front-End architecture

Charge 1-40 MIP, Time resolution: BC tagging 150-300ns, fine: ~ 1ns

Technologies: Deep Sub-Micron CMOS 180-130nm

Future: SiGe &/or deeper DSM

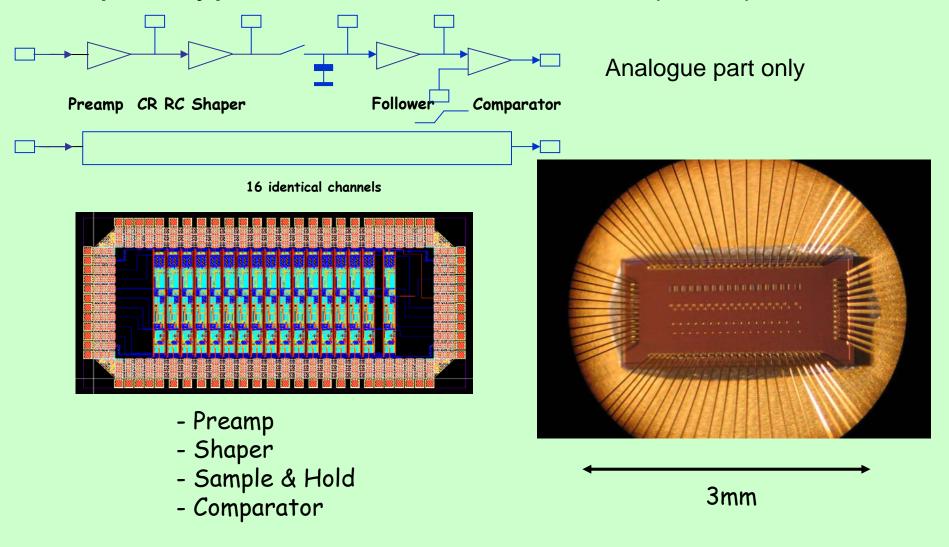

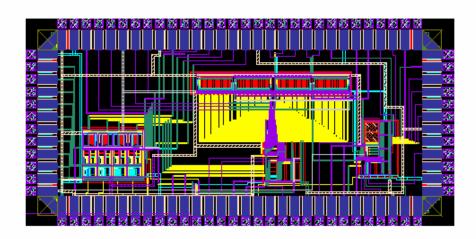

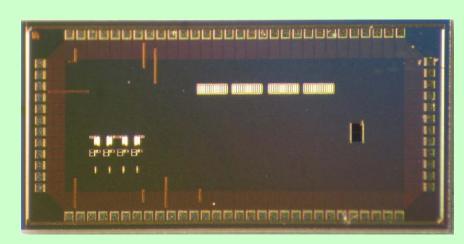

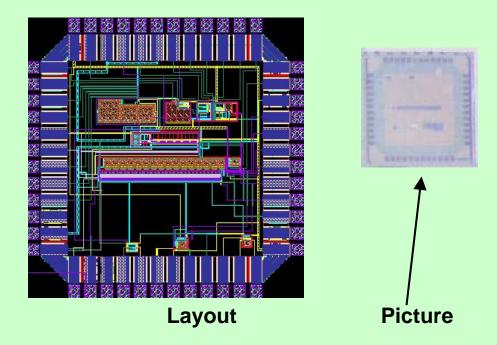

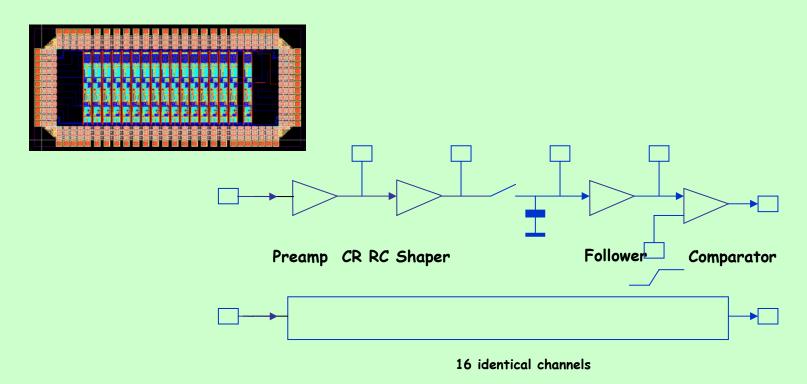

#### First prototype in CMOS UMC 180nm (2005):SiTR-180

16 + 1 channel UMC 180nm chip: SiTR-180 (layout and picture)

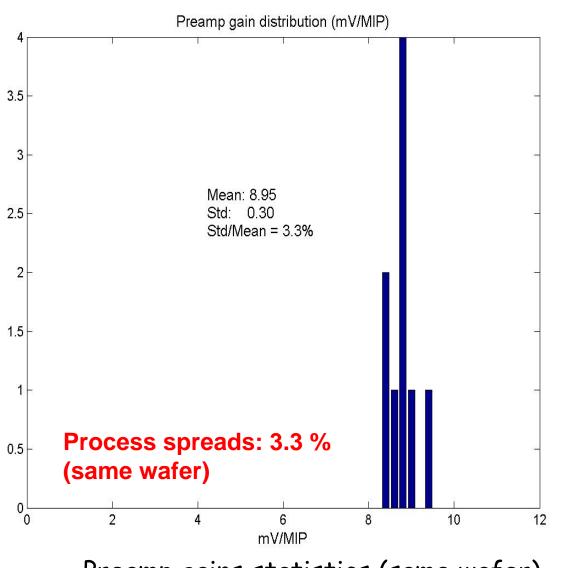

# SiTR-180: Process spreads

Preamp gains statistics (same wafer)

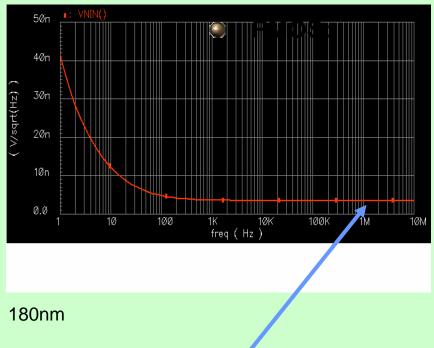

# SiTR-180: Shaper output noise

375 e- +10.4 e-/pF input noise with chip-on-board wiring 275 + 8.9/pFsimulated

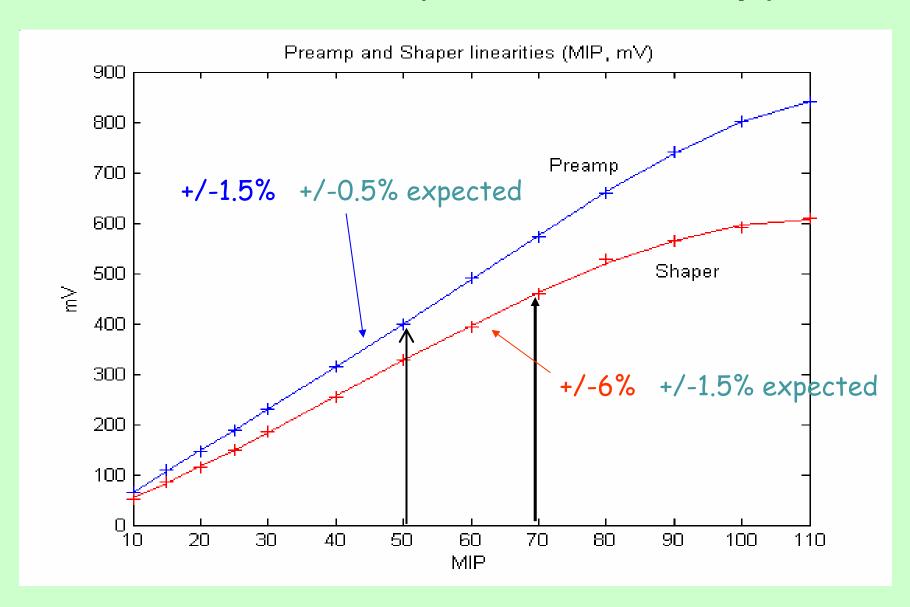

# Linearities (SiTR-180 chip)

#### Functionality tests conclusions on SiTR-180 chips

12 chips tested (end 2005)

The UMC CMOS 180nm process is mature and reliable:

- Models mainly OK

- Only one transistor failure over 12 chips

- Process spreads of a few %

Very encouraging results regarding CMOS DSM

→ go to 130nm

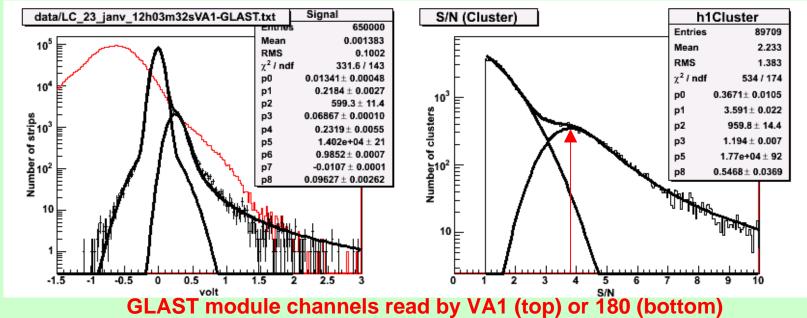

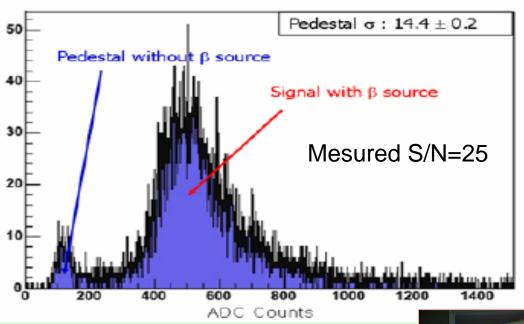

90Sr Source tests with SiTR-180 connected to a Si detector and comparison with VA1 chip from Ideas (see test bench section)

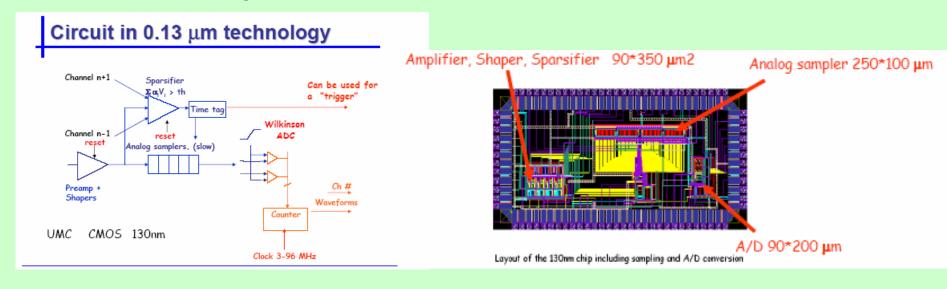

## Front-end in CMOS 130nm

#### 130nm CMOS motivations:

- Smaller

- Faster

- More radiation tolerant (not a real issur at ILC)

- Less power

- Presently dominant in the IC industry

#### Features:

- Design more constraining (Design rules)

- Reduced voltage swing (Electric field constant)

- Leaks (gate/subthreshold channel)

- Models more complex, sometimes still not accurate

# **UMC** Technology parameters

|                                                                                                                                | 180 nm                                         | 130nm                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------|

| <ul> <li>3.3V transistors</li> <li>Logic supply</li> <li>Metals layers</li> <li>MIM capacitors</li> <li>Transistors</li> </ul> | yes<br>1.8V<br>6 Al<br>1fF/mm²<br>Three Vt opt | yes<br>1.2V<br>8 Cu<br>1.5 fF/mm <sup>2</sup><br>ions Low leakage option |

## 130nm 4-channel test chip: SiTR-130

Being tested: Analog OK, Digital under tests

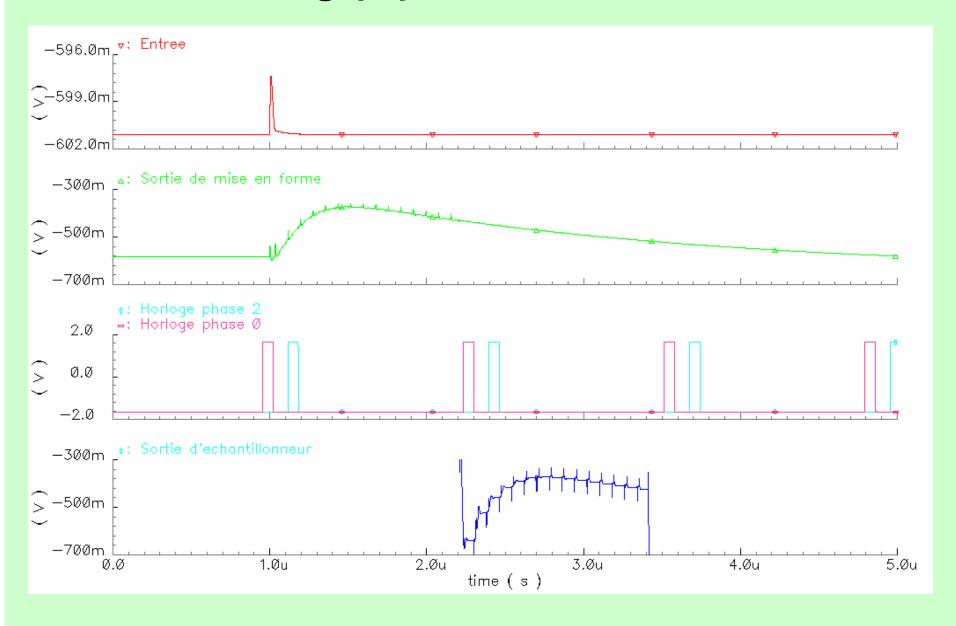

## Analog pipeline simulation

# The SiTR-130\_1 chip

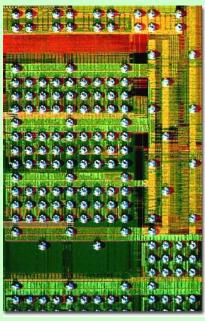

Layout of the 130nm chip including sampling and A/D conversion

**Picture**

180nm 130nm

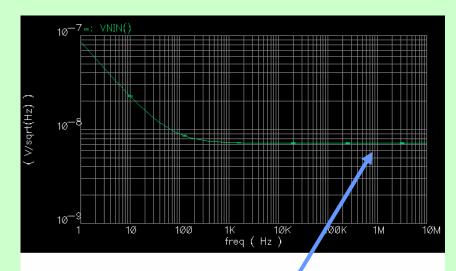

# Possible issues: noise: 130nm vs 180nm (simulation)

gm=944.4uS

1MHz → 3.508nV/sqrt(Hz)

130nm

gm=815.245uS

<u>1MHz</u> → 7.16nV/sqrt(Hz)

Thermal noise hand calculation = 3.42nV/sqrt(Hz)

Thermal noise hand calculation = 3.68nV/sqrt(Hz)

Measurements show 2 times better results

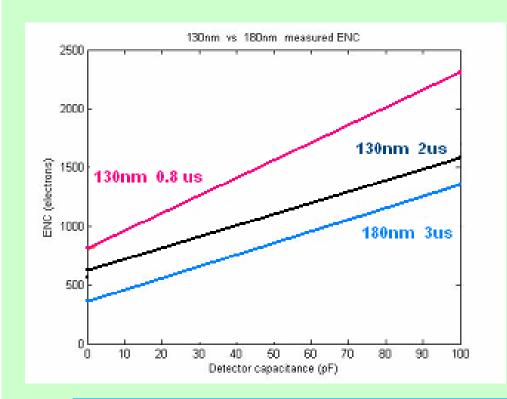

## SiTR-130\_1 tests results

Gain OK: 30 mV/MIP OK Dynamics: 30 MIPs @ 5% OK

Peaking time:  $0.8 - 2\mu s$   $0.7 - 3 \mu s$

Power (Preamp+ Shaper) =  $300 \mu W$

Noise comparative 130nm @  $0.8 \mu s$ : 850 + 14e-/pF

130nm @ 2  $\mu s$ : 625 + 9e-/pF

180nm @ 3  $\mu s$ : 360 + 10.5 e-/pF

## Some issues with 130nm design

- Noise models pessimistic, Silicon actually much better!

- Design rules more constraining

- Some design kits are not fully developed and thus additional effort needed

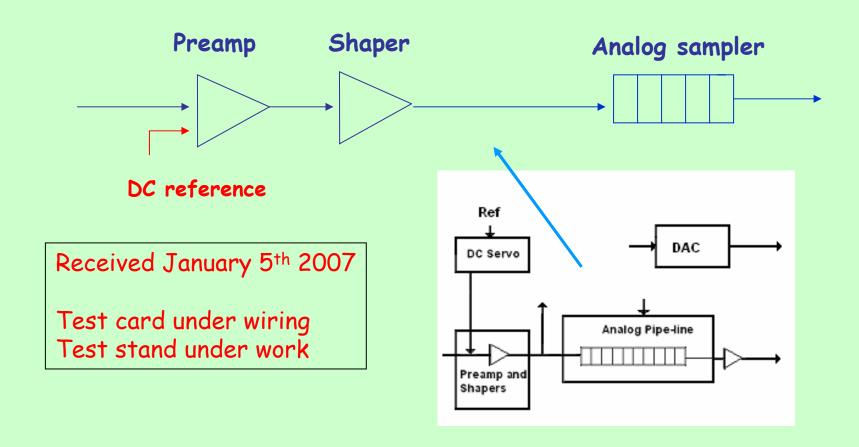

## SiTR-130\_2

One channel version with the SiTR-130\_1 analogue part only, but:

- ServoDC

- Improved pipe-line

- DAC

One channel 1.5 x 1.5 mm<sup>2</sup>

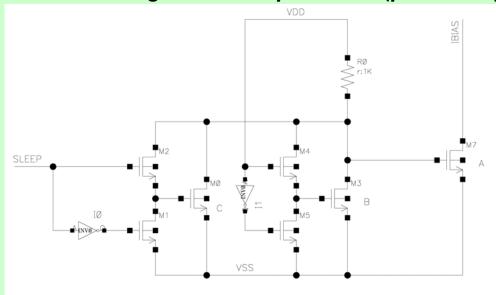

## SiTR-130\_2 architecture

DC servo to accommodate DC coupled detectors, DAC,

Improved pipe-line

# SiTR-130\_1 present conclusions

Good matching wrt simulation

Except noise which is...

much better!

- Still lot of work to test pipe-line & digital

- Statistics from two wafers (70 chips)

# Technology comparisons

#### The questions are:

- 1) At what DSM level to go?

- 2) What founder to choose

Following the presently achieved results and the increasing expertise in the SiLC collaboration (new Institutes joining), there are at disposal within SiLC:

UMC, STMicroelectronics and IBM (via CERN collaboration in EUDET). It is foreseen to have before the end of 2007, a review of 130nm techno in these 3 foundries to compare the performances especially in terms of noise (analogue part)

# Power dissipation budget (measured)

|          | Preamp | Shaper | Zero<br>suppr | Pipe-<br>line | Total<br>Analog | ADC | Logic | Total<br>Digital |

|----------|--------|--------|---------------|---------------|-----------------|-----|-------|------------------|

| 180nm/ch | 90     | 180    |               |               | 270             |     |       |                  |

|          |        |        |               |               |                 |     |       |                  |

| 130nm/ch | 148    | 148    | 198           | 10            | 575             | 66  |       |                  |

| Common   |        |        |               | 100           |                 | 5   | 96    | 101              |

Final goal: ≤ 1 mWatt/channel all included (looks achievable)

## Power cycling: to be implemented next

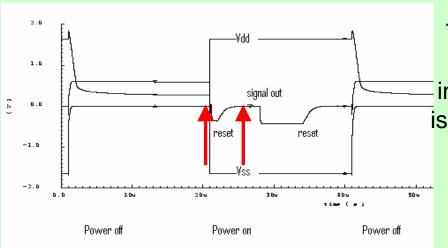

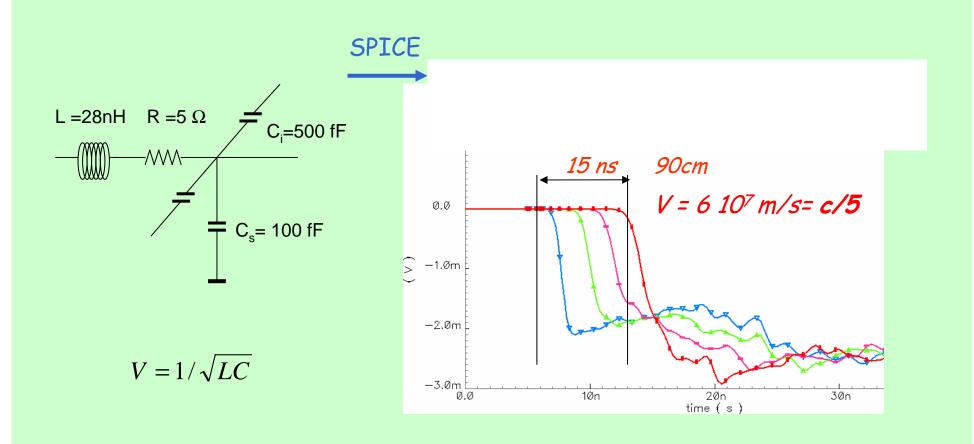

#### Power switching at zero power-off: SPICE SIMULATION only

This option switches the currents to zero.

The simulation shows that, provided the integrating capacitor of the charge amplifier is reset before power-off and after power-on, the whole procedure should take ~ 5 µs.

#### Power switching with some power left (preliminary schema only)

This option switches the current source feeding both the preamplifier & shaper between 2 values to be determined by simulation.

A very small fraction (order 0.1% - 1%), to be determined by simulation studies, of biasing current is held during « power off ». This can be done in a very simple way by switching one more transistor in the current mirror.

## Next developments

- Implement the fast (20-50ns shaping) version in Silicon-Germanium including:

- Preamp + Shaper (20-100ns)

- Fast sampling

- Submit a full 128 channel version in 130nm CMOS including slow and fast analog processing, power cycling, calibration and digital (e.g:amplitude, time and centroid)

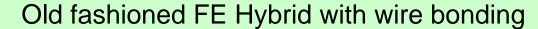

## Chip connection on µstrips

#### **Presently available:**

- Wire bonding (µstrips)

- Only periphery of chip available for IO connections

- Mechanical bonding of one pin at a time (sequential)

- Cooling from back of chip

- High inductance (~nH)

- Mechanical breakage risk

- Flip-chip (pixels)

- Whole chip area available for IO connections

- Automatic alignment

- One step process (parallel)

- Cooling via balls (front) and back if required

- Thermal matching between chip and substrate required

- Low inductance (~0.1nH)

Is this adaptable to ustrips?

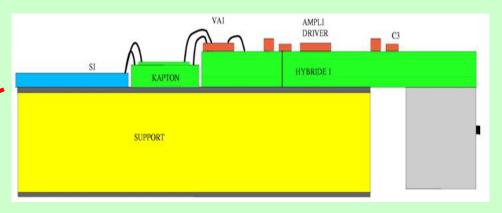

## Towards the novel elementary module

(the electronics side of it)

Important issue in developing a novel elementary module is the direct connection of the FEE on board.

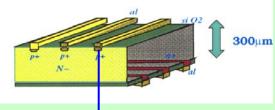

➤ Integrate pitch adapter into sensor, 2nd metal layer for signal routing (see sensor section)

Via (DC coupling)

AL routing & pad area

Oxide

Slicon

> Bump-bonding of readout chip directly onto to sensor

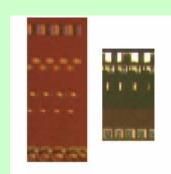

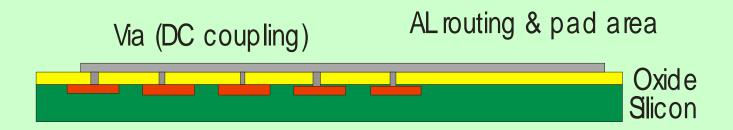

## Bump bonding FEE on detector

IMB-CNM, VTT, HIP, LPNHE, Liverpool (firms)

Design of the fan-in fan-out on the μstrip sensor:

The design is starting in LPNHE based on 50μm single sided 6"sensors, considering 2 cases:

1st case: 128 ch (chips available by end 2007)

2nd case: 1024 channel (chips available later)

Fanin/Fanout design should be ready in 2 months from now.

Have a foundry or a indutrial firm ready to implement it on the sensor (underway: see sensor section)

Bump bonding of the FEE chip: crucial point: have a working chip with the required nb of channels

(SiTR-130\_128 by end 2007)

Cabling => use: Tape Automated Bonding (TAB) or ?????? Don't forget auxiliary electronics that degrades any fancy solution on paper ex: decoupling capacitors

# Cabling, Data Flow and Data transmission: preliminary thoughts

Present idea: daisy chaining several adjacent front-end chips (e.g.4) on the two corresponding single-sided layers, of the same octagonal plane, with micro coax cabling. This would make 6 micro coax cables per octagonal plane read out in parallel by digital fibers in the considered example.

One fiber could serve 2 half octagonal plane.

Using **micro-coax cables** of typically one inch diameter, 300 mW power dissipation at 1 GHz and that can be power cycled. **Kapton cables** are also under consideration. At a later stage in the cabling scheme, i.e. to transmit the information from the edge of the detector to the outside, 6GHz **SCM fiber optic** links are presently considered.

This is under serious investigation because the following main issues /or concerns:

✓ Cabling versus and/or fibres: micro coax are making a real comeback

✓ High multiplexing rate versus redundancy

✓ Technological field that evolves very rapidly (telecom etc..)

#### **OUTLINE**

- > PART I: The Collaboration and R&D Motivations and Goals

- The SiLC Collaboration

- Why R&D on tracking is needed

- Why Silicon Tracking

(A. Savoy-Navarro)

- > PARTII: The R&D objectives

- R&D on Mechanics (V. Saveliev)

- R&D on Sensors (M. Lozano and H.J. Kim)

- R&D on Electronics (B. Schumm and A. Savoy-Navarro)

- > PART III: The R&D Tools

- Simulations (M. Vos)

- Lab Test bench and Test beams (A. Savoy-Navarro)

**Concluding remarks**

### SiLC simulation task force

Valeri Saveliev, Obninsk State University, Russia

Giulio Pellegrini, IMB-CNM, Barcelona, Spain

Juha Kalliospuska, HIP and VTT, Helsinki, Finland

Mikael Berggren, Wilfrid Da Silva, Frederic Kapusta,

LPNHE Paris, France

Zbyneg Drasal, Charles University, Prague, Czech

republic

Bruce Schumm and collaborators, UCSC – Scipp, USA

Winfried Mitaroff, Meinhard Regler, Manfred Valentan,

HEPHY Vienna, Austria

Marcel Vos, Carlos Mariñas, IFIC Valencia, Spain

**Korean Group collaborators**

## **Outline**

- what simulations and why?

- microscopic simulations

- macroscopic simulations (fast and full)

- status of available tools

- glossary of results

- outlook

## Introduction

In this phase, simulations plays a major role in guiding the R&D.

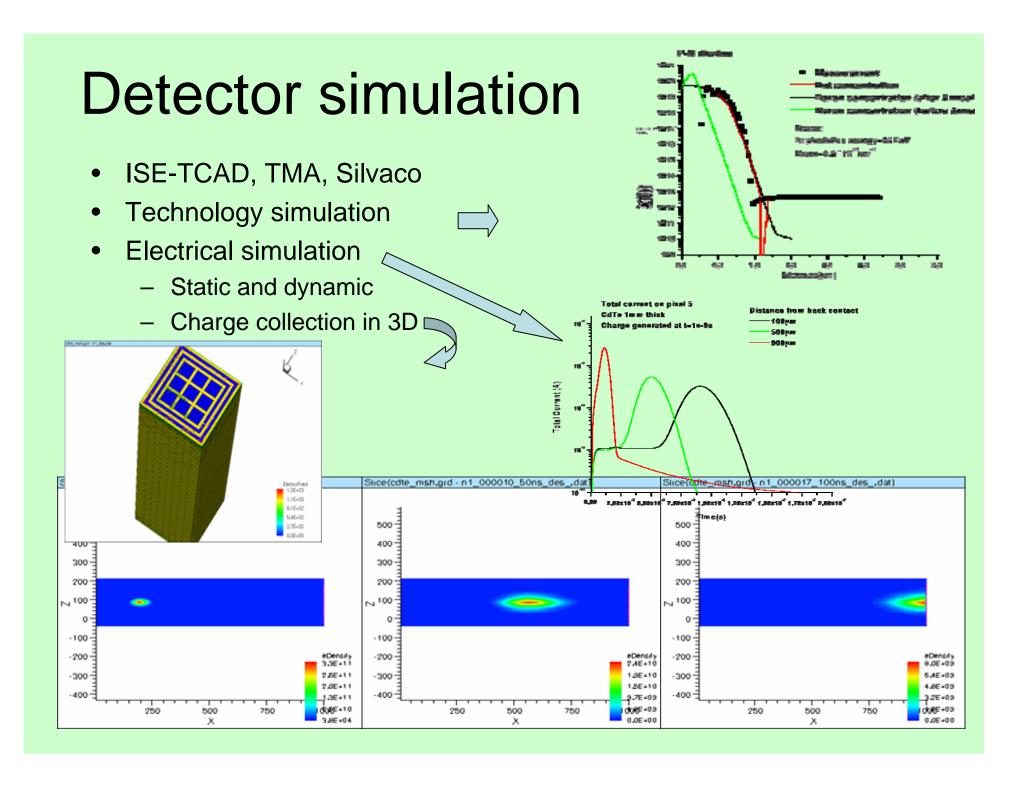

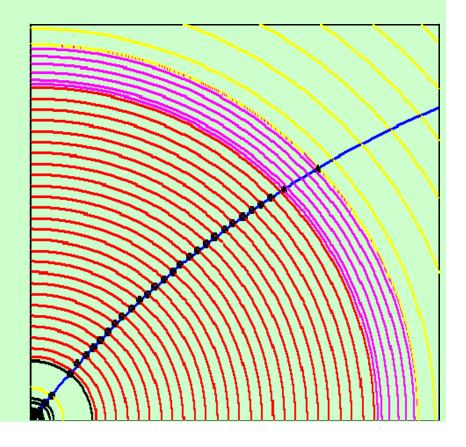

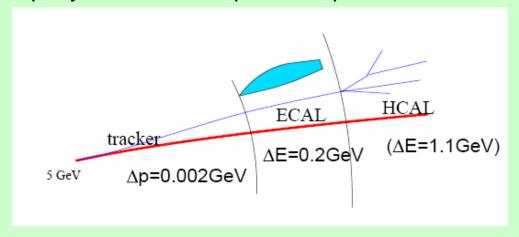

"Microscopic" simulations, representing in detail the signal formation in the sensors and how it is processed in the Front End electronics, lead to enhanced understanding of the basic process of (new) technologies, allow to validate and optimize designs.

"Macroscopic" detector *simulations* allow to relate the detector design parameters (layout, technology) to the overall physics performance of the experiment. The *simulation* package should be accompanied by a sophisticated *reconstruction* framework. Monte Carlo production (GRID) infrastructure is required.

Needless to say, the whole system will be thoroughly validated (against beam and system tests) and meticulously kept up-to-date.

A flexible simulation and reconstruction framework, provides invaluable guidance to the detector design:

- studies of physics topologies will be used to draw up detector requirements

- the impact of design variations can reliably be predicted

## Microscopic simulation

#### Read-out electronics design:

Behavioral models: Simulink, ADS

Functional and system: Level System Verilog, System C

Logical and RTL: VHDL, Verilog

Electrical circuits: SPICE, Spectre

Several SiLC institutes have access to electronics design software and experienced engineers

Thermal model of ATLAS – SCT barrel mstrip module

# Digitization

The bridge between microscopic and macroscopic worlds.

Digitization step in the "full" simulation should represent our best understanding of the detector response. As the Front End and sensor design emerges, and results from (beam) tests of prototypes become available, this information is going to find its way into the simulation software.

$Geant 4\ simulation\ in\ \underline{http://www-ucjf.troja.mff.cuni.cz/diploma\_theses/reznicek}\ \underline{-dipl.pdf}$

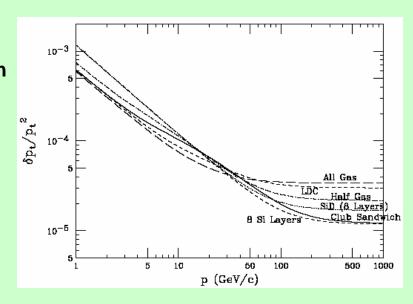

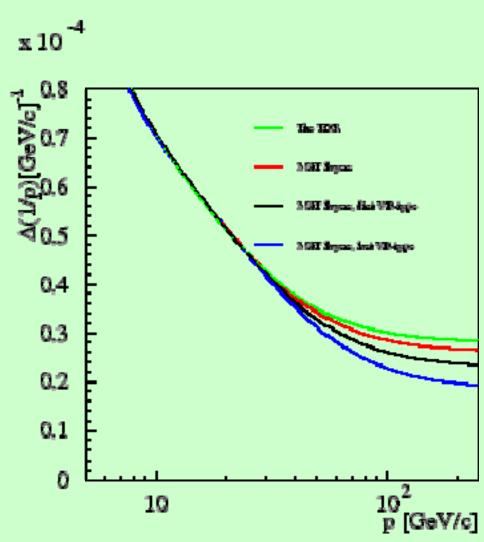

## Macroscopic simulation

### Fast simulation:

Provides a reliable estimate of "ideal" parameter resolutions for a given layout.

# Macroscopic simulation: SGV

#### Simulation a grande vitesse, M. Berggren, LPHNE, Paris

Analytical calculation of track parameter resolution from geometry LCIO output module (B. Jefferey, Oxford) allows to compare full and fast simulation outcome on the same footing.

The program has a long history, and has been thoroughly validated against a running experiment (DELPHI).

# Macroscopic simulation: LiCToy

LiCToy, M. Regler, M. Valentan, R. Fruehwirth, LPHNE, HEPHY, Vienna

Fast simulation tool for detector design.

Position measurements are simulated at the intersections of an ideal helix trajectory and a simplified geometry.

Sophisticated Kalman filter track fit, including material effects, yields the parameter covariance matrix.

Validation against experiment and other simulators ongoing.

http://wwwhephy.oeaw.ac.at/p3w/ilc/talks/06\_SiLC\_Barcel/MK\_LiCToy.ppt http://wwwhephy.oeaw.ac.at/p3w/ilc/reports/LiC Det Toy/UserGuide.pdf

LCDTRK (Bruce Schumm, SCIPP): analytical determination of momentum resolution for a given layout, space point resolution, material burden

http://ww.slac.stanford.edu/~schumm/lcdtrk20011204.tar.gz

excellent example: hep-phys-0511038

GLD fast simulation (Korea): Kalman filter fit of space points from fast simulation

Fast simulation provides important feed-back to layout optimization:

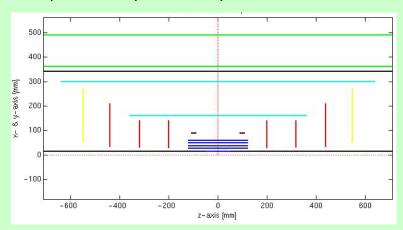

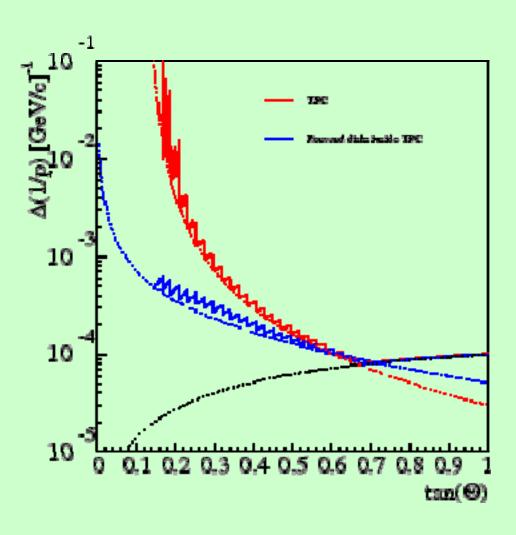

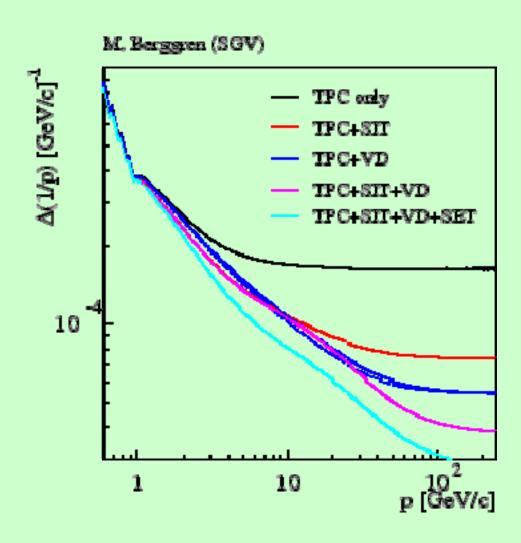

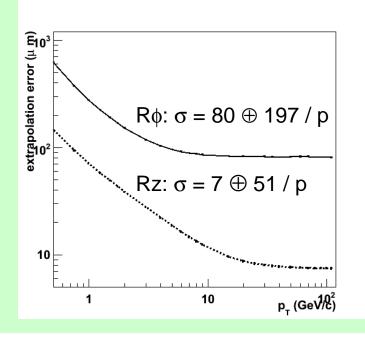

SGV simulation (M. Berggren) of the LDC tracker central region

Momentum resolution for 4 different SIT scenarios.

2-3 layers -> marginal differnce improved space point resolution yields substantial gain (especially for outer SIT layer)

SGV simulation (M. Berggren) of the LDC tracker central region

Impact of silicon (FTD) disks on momentum resolution on forward tracking.

To maintain an adequate performance in the forward region, the TPC must be complemented by silicon.

SGV simulation (M. Berggren) of the LDC tracker central region

Silicon envelope for the TPC: a precise measurement extending the lever arm improves resolution for large momentum.

## Macroscopic simulation: full

## Full simulation:

Full detail in detector geometry.

GEANT4 description of particle interactions with detector.

Detector response ("digitization").

Full simulation only provides guidance if complemented by a sophisticated reconstruction framework, with realistic implementations of central algorithms.

## Macroscopic simulation: full

Several (regional) frameworks exist:

Europe: Mokka (<a href="http://www-flc.des.de/ilcsoft/ilcsoftware/Mokka/">http://www-flc.des.de/ilcsoft/ilcsoftware/Mokka/</a>), MySQL

geometry description, GEAR

America: SLIC (<a href="http://www.lcsim.org/software/slic">http://www.lcsim.org/software/slic</a>), XML-based GDML

Asia: Jupiter

Geometry implementation: LDC in Mokka, SiD in SLIC and Mokka, GLD in

Jupiter

SiLC is closely following the unified geometry

description effort

Digitization: in progress

## Macroscopic simulation: full

Using GRID and LCIO several data samples are accessible:

- For various relevant signal topologies

- For pair-background due to beamstrahlung (\*)

- For the main detector concepts

(\*) generated using GUINEA-PIG, simulated for LDC geometry, nominal machine parameters, anti-DID field, Adrian Vogel, Desy

## Pattern recognition

Tracking environment: the challenge to pattern recognition should be studied in detail following the ILC physics benchmarks, in particular and for example:

- jet topologies:

- Highest possible total multiplicity: tt

- · Highest possible collimation: tau jets

- Highest energy jets: light quark antiquark

- for Non-prompt tracks (long-lived particles, photon conversions) pose a special challenge which will be studied by SiLC:

- SIT or FTD in LDC

- SIT and FIT in GLD

- first SiD layers

issue: resolve ambiguities without the VXD

Forward physics: comparison between two tracking strategies (gas+Si vs Si)

-Background rejection through precise BCO tagging

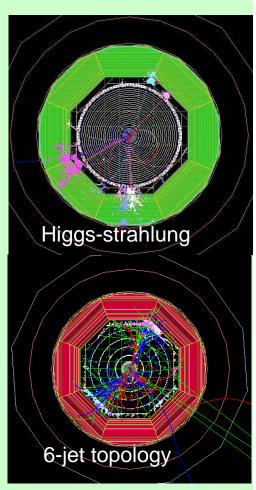

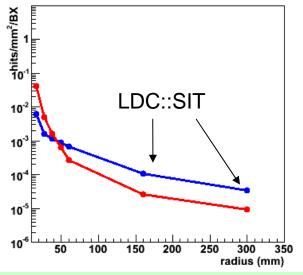

Pattern recognition

Occupancy: # hits/mm2/BX

red: contribution from pair background

blue: dense signal topology (tt)

Convolute with detector design (cell size, bunch crossing ID)

Occupancy: # hits/channel

(ZH -> mumu bb)

Pattern recognition

Convolution of search window with occupancy yields contamination or confusion.

Crucial layout parameters: distance VXD – silicon and VXD lever arm (for all concepts), distance TPC-silicon and material

Use a Kalman filter to predict the search window

## Search window

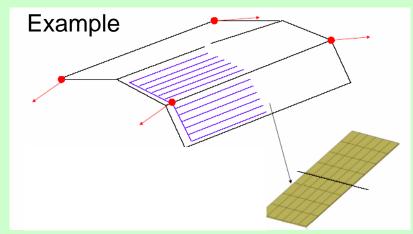

Example of interplay between search window and technology: compatible hits in single sided silicon mstrip detector vs pixel detector.

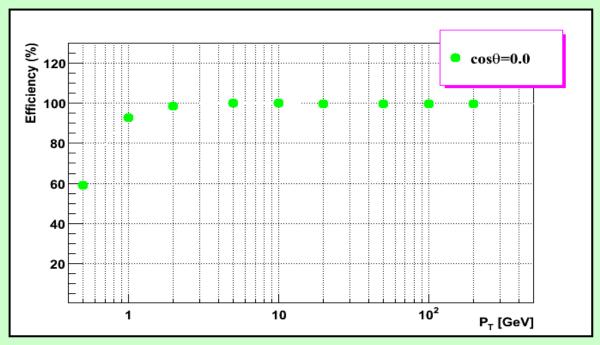

## Reconstruction

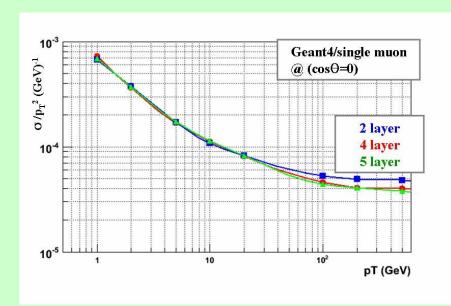

Low p<sub>T</sub> tracks clearly present a challenge to reconstruction software and detector.

Single-muon study of the GLD concept (Korean Group).

## Outlook

The SiLC simulation taskforce is taking shape

Microscopic, and fast and full simulation tools in place

#### Effort needed on:

- understand background levels and its uncertainties and dependence on machine/detector parameters

- digitization

- pattern recognition:

- feedback to technology (cell size optimization for innermost layers)

- feedback to layout (disks with radial strips vs. XUV)

- embed SiLC effort in global ILC simulation & reconstruction framework

# Lab test bench & test beams for Si trackers R&D

#### **Needed tools because:**

Lab test benches of different types are a first approach towards experiencing in more realistic ways various real life conditions. The test beams are their indispensable continuation and extension to ensure that the device will satisfy the requirements and/or verify how much it satisfies them.

Test beams allow identifying new problems, not yet anticipated even at Lab test bench. Test beams allow combining several sub detectors.

Lab test bench and test beams give feedback to the simulations (refining them).

o Most (if not all) the Institutes participating to SiLC have Lab test bench facilities. All intend joining the SiLC test beam programme.

o Both the continuous needed evolution of the Lab test bench and the construction and running of the test beams are requesting lot of efforts (FTE) and of financial support.

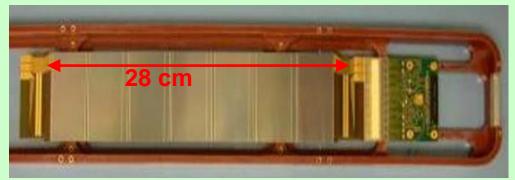

#### **LAB TEST BENCH: results**

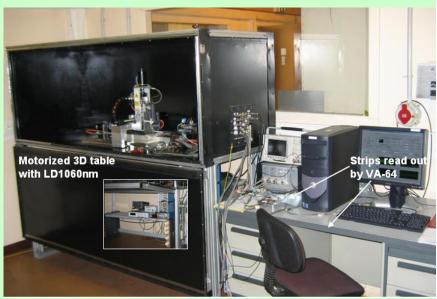

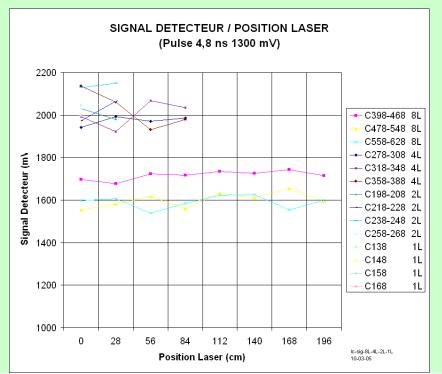

(LPNHE + U. Geneva, CU Prague)

Detector with  $\mu$ strips of L= 28 cm x (N=1,4)  $VA\_64hdr$  readout chips from IDEAS.

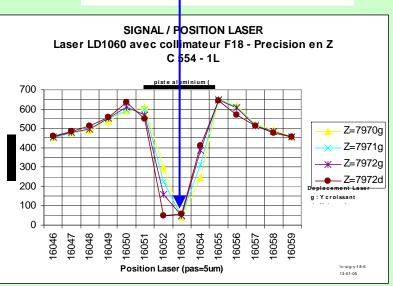

#### > Characterization with LD1060

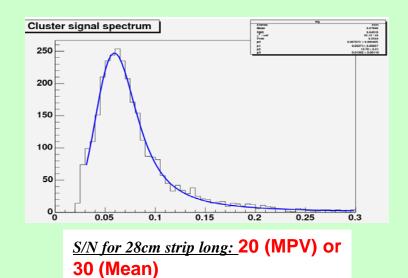

## Signal-to-noise ratio vs µstrip length

#### > Characterization S/N with a radioactive source

Cluster spectrum, 2L strips

40

30

20

10

## Before leaving for the test beam in DESY: tests the functioning of the modules & associated FEE

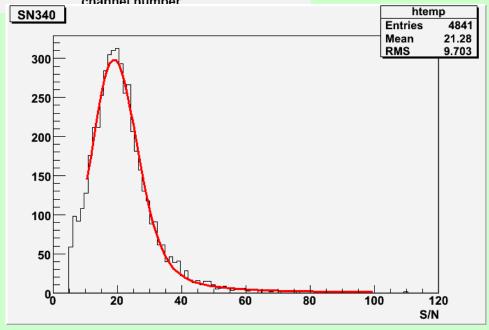

## S/N measured with SiTR-180 (after t.b.)

W. Da Silva, J. David, F. Kapusta, F. Rossel (LPNHE)

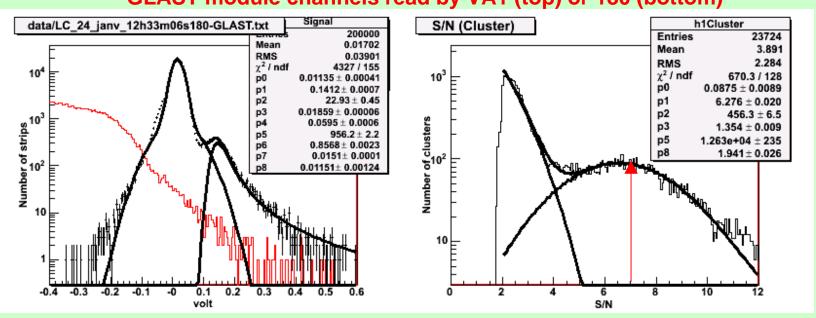

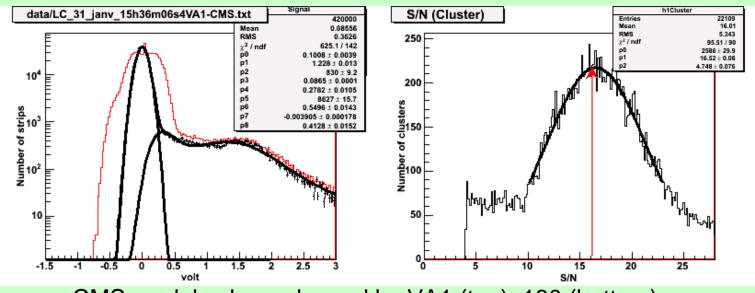

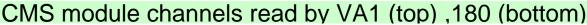

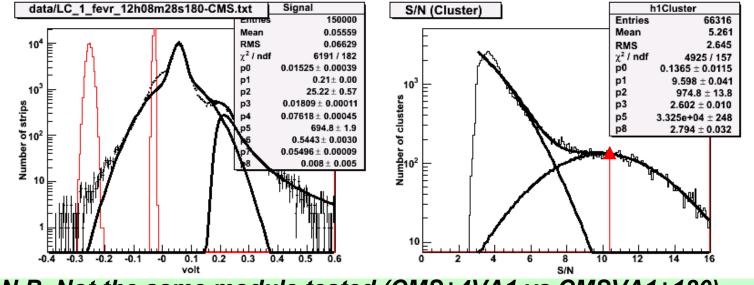

## S/N measured with SiTR-180 W. Da Silva, J. David, F. Kapusta, F. Rossel (LPNHE)

N.B. Not the same module tested (CMS+4VA1 vs CMSVA1+180)

## Coordinate along the strip

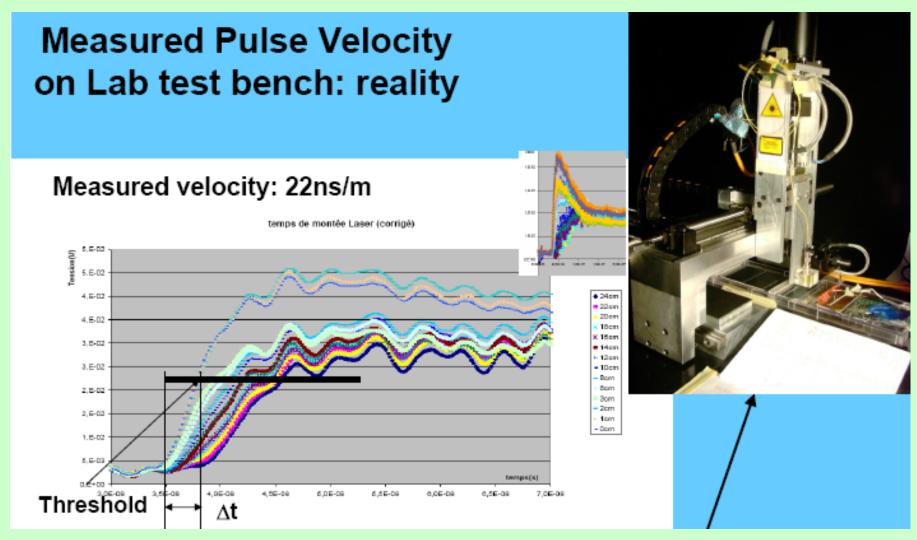

J.F. Genat (LPNHE)

1 ns time resolution is 6 cm

#### Jacques David et Francois Rossel (LPNHE)

Measured velocity: 5.5cm/ns Measured moving a laser diode along 24 cm at LPNHE Lab test bench with first module prototype Now: Improving the Lab test bench measurement using Radioactive Source Will start design of the fast FEE in one of the next chips.

## Characterization of new sensors (Korean group)

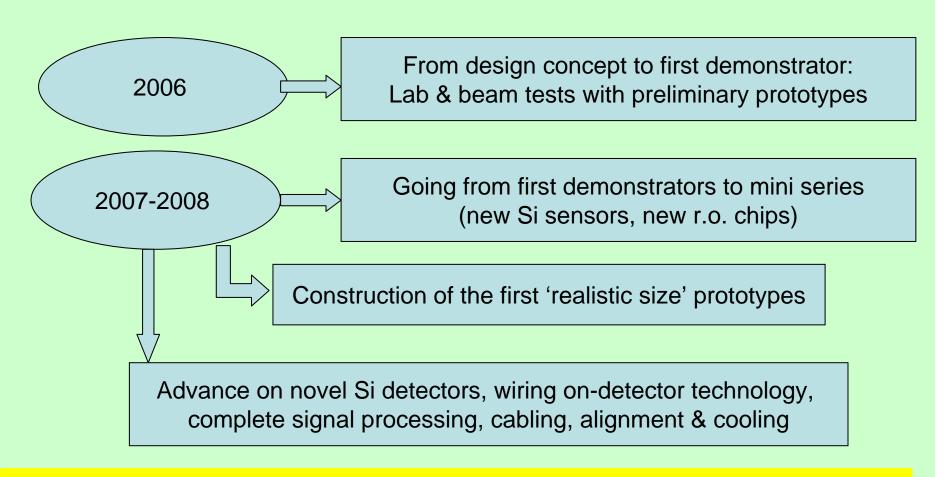

## SiLC Roadmap & Scientific Objectives

23/10-3/11/2006 DESY 1-6 GeV e-S/N: 180nm/ VA1, two 30cm strip modules & one 90cm strip module -April 07: DESY 130nm

-July 07: CERN 2 mod.

new sensors+VA1-130nm

-Nov. 07: CERN cont'd

-2008: Full size Si detector

pro.; combined tests(small

calo, F.C. +TPC,B field)

with various Si prototypes

and 128 ch chips

2009: FNAL(CERN)

Combined tests with

final protos of Si

tracker, calo and TPC

new foundry FE chips,

cooling and alignment

protos and new chips

<u> 2006\/</u>

2007

2008

2009

Preparation test beam 07: 130nm chips & detector protos

Prepa test beam 09:new chips & new detector protos, cooling & alignment

To be delivered: VDM FE readout chips to equip test beam prototypes

Large area Silicon tracking structure prototypes

Cooling & alignment systems

Series of testbeams Si alone or combined (see Roadmap)

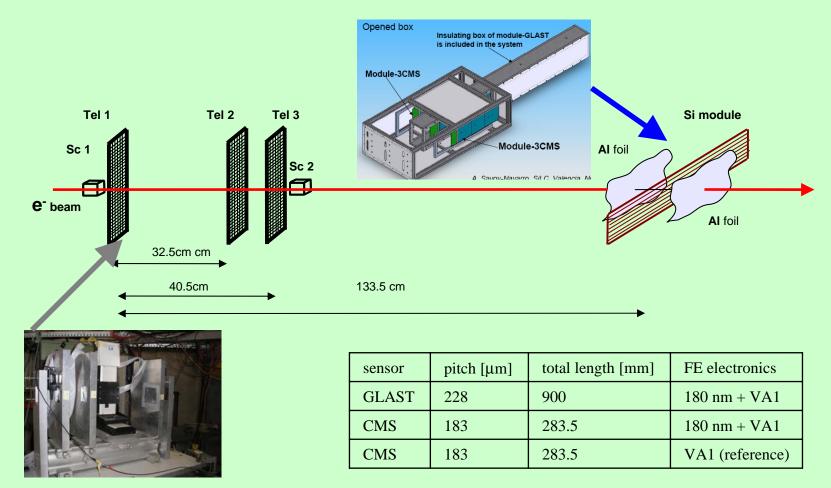

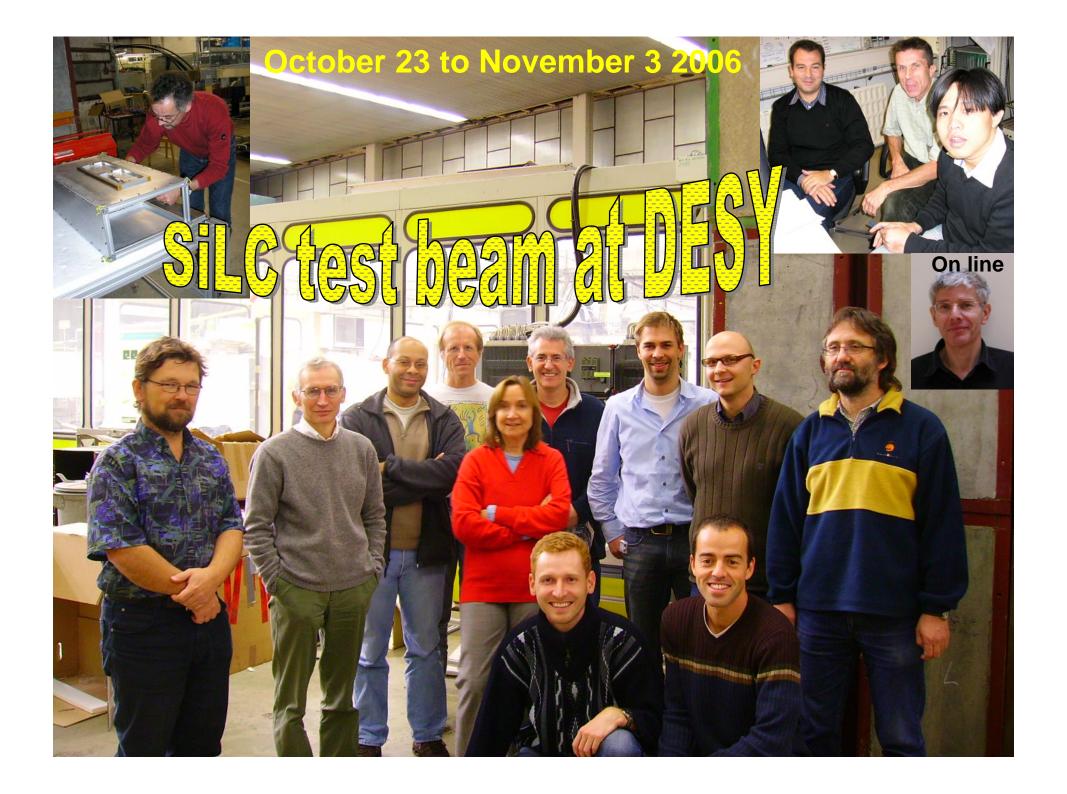

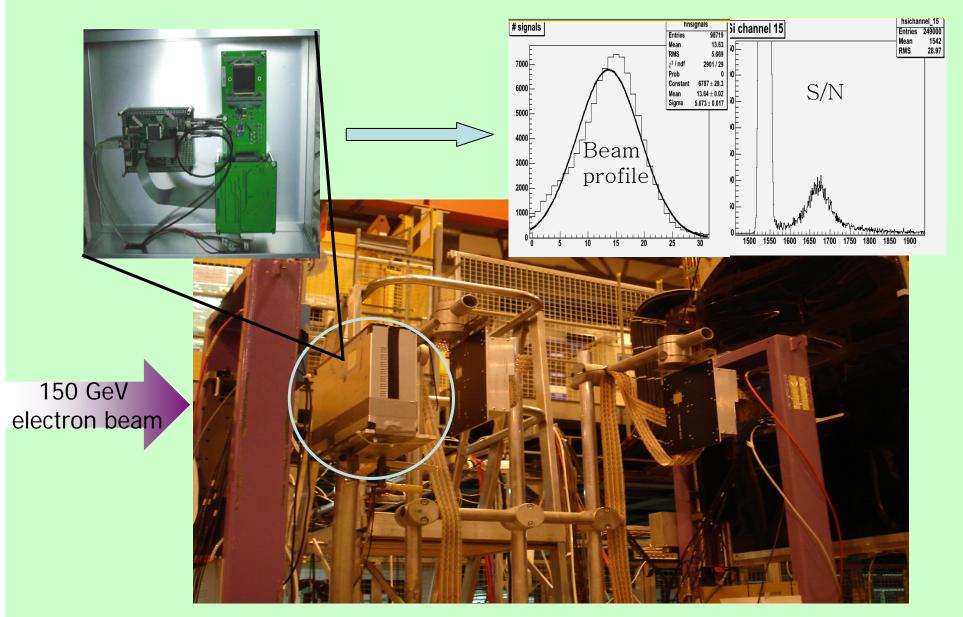

#### SiLC Test beams @DESY in 2006

- 1-6 GeV e- beam, no B, from Oct. 23 to Nov. 3; this will be pursued April 07; goals:

- > Test the complete new test set-up (modules, read out electronics, DAQ)

- Compare new first FEE prototypes (SiTR-180/130,wrt to reference: VA1)

- Measure S/N

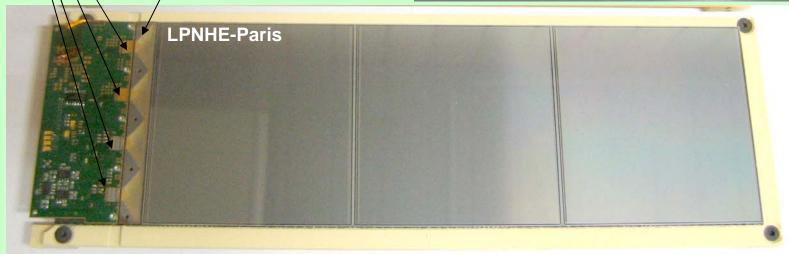

#### **Detector prototypes**

#### CERN(A.Honma), IEKP-Karlsruhe, LPNHE-Paris, IEHP-Vienna, Hamamatsu

Assembly

3 CMS sensors 28

cm strip long

Read out:

VA1+180UMC r.o

and all VA1 r.o.

2 modules fabricated in Paris, bonding CERN on automated CMS system (Collab CERN-LPNHE)

Assembly: Module = 10 GLAST sensors 90 cm strip long

**Bonding**

The full construction done at IEKP

R.O.

Pitch adapter +

VA1 + 180UMC

provided by Paris

## Front-end chip: SiTR-180 first prototype

- Low noise amplification + pulse shaping

- Sample & hold

- Comparator

- No power cycling yet

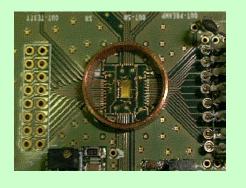

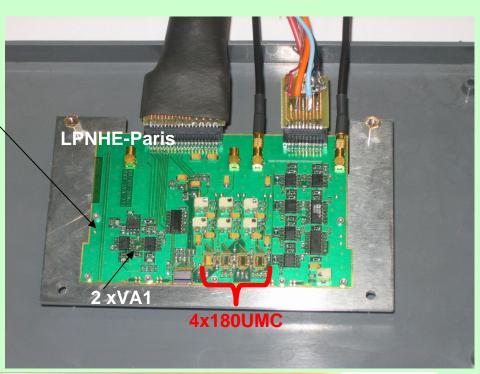

#### **Readout Electronics: LPNHE Paris**

2 VA1 + 4x 180UMC channels: hybrid R.O. card under test

4 VA1 r.o card

➤ VA1 r.o. card ready

➤ 2 hybrid r.o. cards:

VA1+180UMC ready

Both being tested at

Paris Lab test bench

Pitch adapter

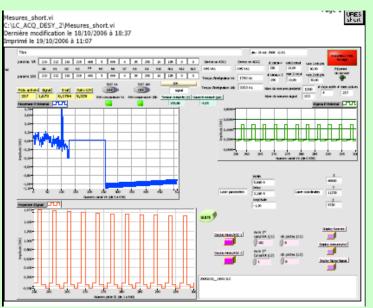

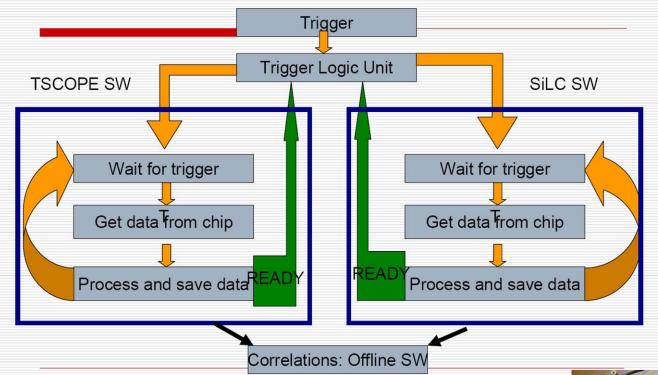

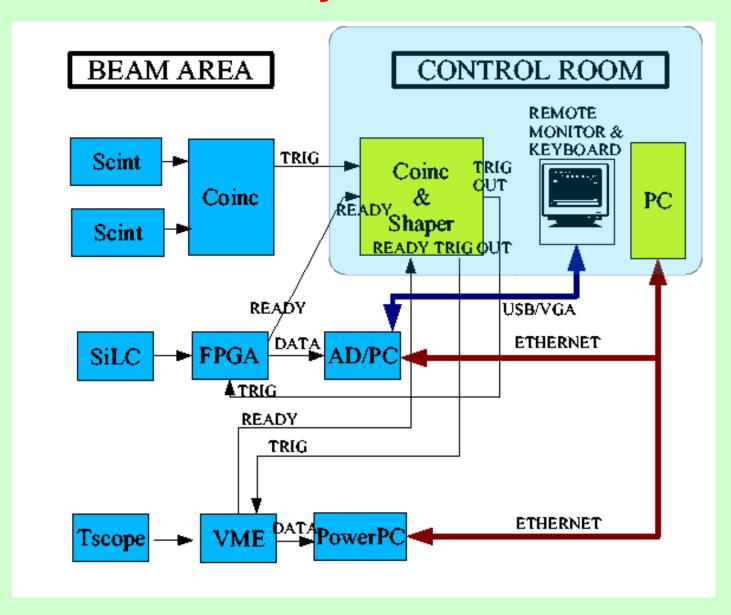

#### **DAQ:** hardware & software

LPNHE-Paris:

Rebuilt its DAQ test bench To be used both for

- ➤ Tests @ Lab t.b. before

- >Tests @DESY t.b.

Adapted to

- ❖new R.O. electronics

- and to be linked to DAQ of the beam telescopes.

#### DESY and CU-Prague:

Use of the existing hardware and software developed by DESY for the beam telescopes implementing a very basic trigger logic for connecting the two DAQ systems.

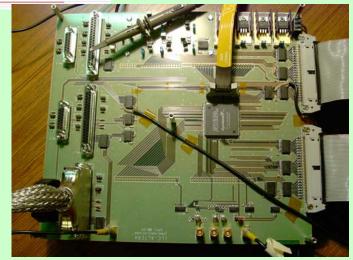

#### Tests at the Lab Test bench before DESY

- Complete upgrade of the Paris Lab test bench

- Characterization of the new readout chips (VA1 and 180UMC)

- Characterization of the new Si modules:

- → 2 x 3CMSmodule

- → One long strip module

- > Test of the functioning of the new DAQ hardware

- → New command card

- → New Altera card

- → Effect of 15 m long cable between Altera & detector R.O.

- > Test 2 DAQ's running in parallel (beam telescope and Si detector R.O.)

- Test analysis packages with Lab test bench runs

All these tests were performed at the Paris Lab test bench since end of September till October 20.

Tests were pursued at the Lab test bench after the first round at DESY for further investigations and completion of the measurements.

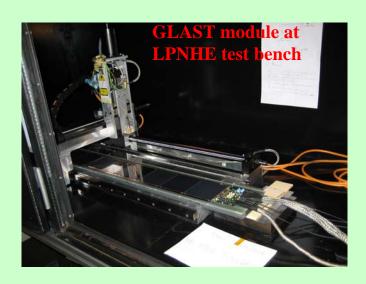

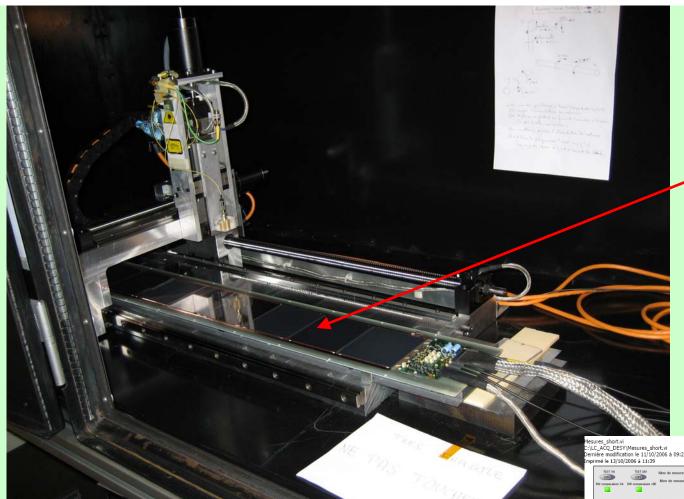

GLAST module sitting on the Lab test bench

Modules and readout electronics were tested on Lab test bench in Paris, before going to DESY., as for example, the GLAST module or the CMS-4VA1 module

# Preparation for the DESY test beam October 23 to Nov 5, 2006 Sharing of tasks

- Construction of the detector prototypes: CERN, IEKP-Karlsruhe, LPNHE-Paris & IHEP Vienna, Hamamatsu providing the sensors)

- Mechanics: DESY,LPNHE Paris, IFIC Valencia

- FE and readout electronics: LPNHE-Paris

- DAQ hardware: DESY for beam telescopes, LPNHE-Paris for SiLC

- DAQ software: DESY, LPNHE-Paris, CU Prague

- Test in test bench prior to go to test beam: LPNHE-Paris, IEKP Karlsruhe, CU Prague,

- Beam Telescopes and Beam infrastructures: DESY, OSU Obninsk,

CU Prague, IFCA.

- Analysis tools: CU Prague, OSU Obninsk, LPNHE Paris

- Participation to the run: HIP Helsinki, IEKP Karlsruhe, OSU Obninsk, LPNHE Paris, CU Prague, IFIC Santander and contribution of DESY (beam & telescopes)

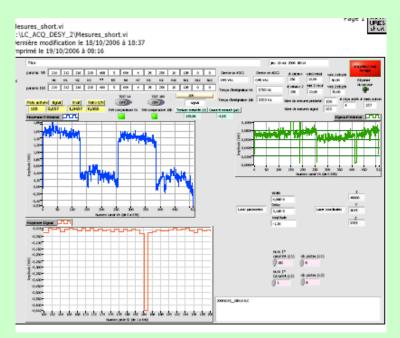

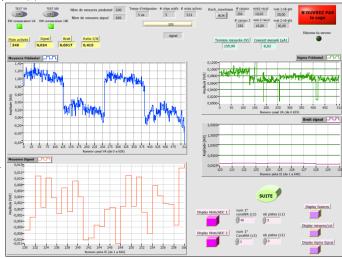

## Test beam DAQ system in DESY for SiLC

Test set-up 1: Two CMS modules

First one read out by 4VA1

Second one read out by

VA1&180nmUMC

Test set-up 2: one GLAST module read out by VA1&180nmUMC

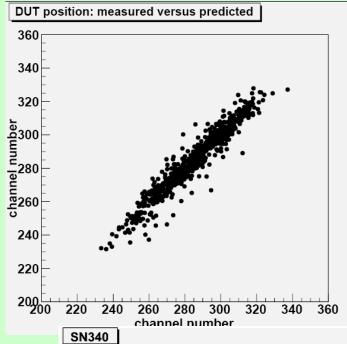

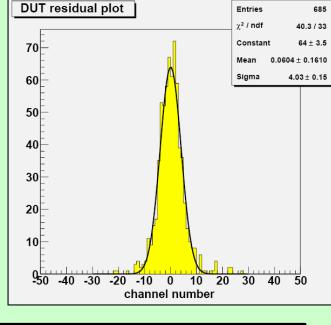

## **DESY Beam test analysis**

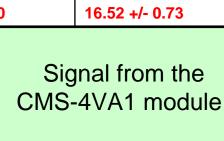

Correlation beam telescopes & Silicon detector, based on the CMS-4VA1 module

| Bias<br>voltage | S/N (MPV)      |

|-----------------|----------------|

| 200             | 13.62 +/- 0.33 |

| 260             | 15.79 +/- 0.29 |

| 299             | 15.70 +/- 0.25 |

| 350             | 16.52 +/- 0.73 |

### Beam Test at CERN (Korean team)

Test on Single sided 5" wafer prototype (ETRI)

#### 2007 Workpackages for SiLC/EUDET

WKP 0: Beam test in DESY (April 2007) with 130nm preprototypes.

WKP 1: Beam tests at CERN (July 2007)= « Rehearsal » for November run:

- 2 modules made of new single-sided sensors readout: VA1(ref)+ 130nm(preproto)

- 3D-planar module test

WKP2: Beam test at CERN (Nov. 2007)

- Prototype 60x60cm2, new single-sided sensors, lecture VA1+130nm,

- First test beam of UCSC long ladder + TOT FE readout chip

- Expected to have first alignement systems (Michigan & IFCA)

- Expected to have first cooling system

- Other SiLC collaborators will join these beam tests and foresee to bring other detector prototypes.

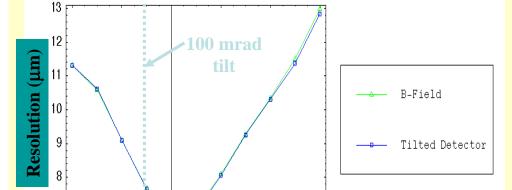

#### SCIPP ToT readout: Testbeam Plans (Dreams?) for Late 2007

#### CDF Layer 00 Sensors

Dimensions: type A: 1.48x7.84 cm<sup>2</sup>

type B: 0.85x7.84 cm<sup>2</sup>

Depletion V oltage: 60 V < Vdep < 100 V

Uniformity of  $V_{dep}$ : < 20%

Biasing scheme: Poly resistors on both sides

RMS ( $\mu$  m) vs. Field Strength/Detector Tilt

**Entrance Angle (B=0)**

Poly resistor values:  $4.5 \pm 0.5 \text{ M}\Omega$ passivation: SiO<sub>2</sub> 0.5  $\mu$ m thick

implant strip width: 8 μm implant depth: >1.0 μm

doping of implant: > 1·10<sup>14</sup> ions/cm<sup>3</sup>

width of Al strips : 7-8  $\mu$ m thickness of Al strips: >1  $\mu$ m resistivity of Al strips: < 20  $\Omega$  cm

10

by Bruce Schumm (SCIPP&UCSC)

2-3 µsec shaping time plus ~10 daisychained sensors → stringent requirement on leakage current, bias resistance

Single CDF LOO sensor may be satisfactory, but "long" ladder may be single sensor plus equivalent capacitive load.

SCIPP simulation for ToT readout of long ladder:

Expect 7  $\mu$ m resolution, but with strong dependence on entrance angle (efficiency also).

Want to explore this in testbeam run.

## Implementing new 130 nm chip: SiTR-130\_1

Implies lot of work: quite challenging!

Testing the full functionality: analogue component, pipeline, digitization included in this chip

- Rebuild a DAQ hardware and software for this new processing of the detector information.

- Test it on the Lab test bench before going to test beam

## Transitions of phase:

In 2006, the first SiLC test beam has triggered the unification of the European collaborative efforts.

The 2007 SiLC beam tests will include the contributions of Asia and US

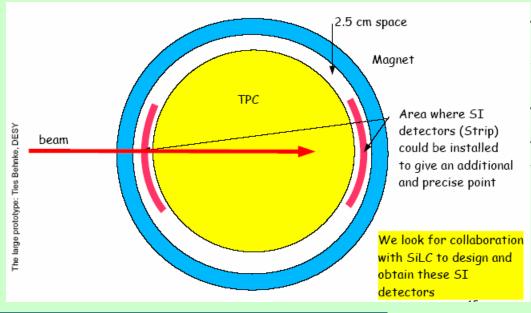

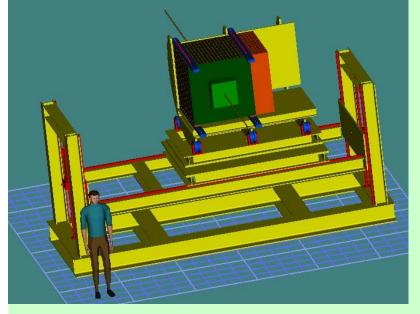

## 2008 & beyond: combined test beams

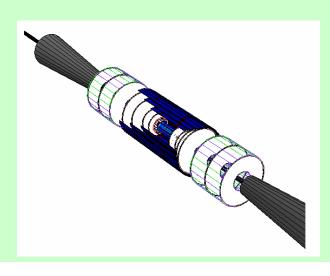

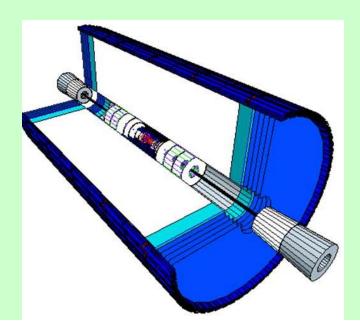

Testbeam with TPC Field Cage & strip layer surrounding it: SET(LDC)

Test beam with pixel detectors: tests on internal tracking region & Vertex + Silicon tracker

Testbeam with Si-W calorimeter & few Silicon strip layers in front: experience particle flow

## Concluding REMARKS

- SiLC has made impressive advances especially this last year and half, on all R&D fronts.

- The new R&D era that SiLC has started this last year is demanding another scale of means in terms of money and people.

- SiLC is attracting more and more institutions but most importantly more FTE that are collaborating to the work

- What is clearly needed is the support from all our funding agencies and thus a strong support of this panel will be essential

# We are very much indebted to the valuable contributions of all our collaborators; a special thanks to:

David Gascon, Carlos Lacasta, Angeles Faus, Juan Fuster, Maria del Carmen Alabau, Beppe Giraudo, Ivan Vila, Jean Francois Huppert, Mikael Berggren, Frank Hartmann, Thomas Bergauer, Alberto Ruiz, Martin Frey, Giulio Pellegrini, Juha Kalliopuska, Simo Eranen, Nick Van Remortel, Risto Orava, Hwanbae Park, Tim Greenshaw, Wilfrid Da Silva, Frederic Kapusta, Zdenek Dolezal, Peter Kvasnicka, Peter Kodys, Zbiniek Drasal, Winfried Mitarof, Manfred Krammer, Jacques David, Francois Rossel, Thanh Hung Pham, Marc Dhellot, Rachid Sefri, Herve Lebbolo, Fougeron, Richard Hermel, Martin Frey, Guillaume Daubard, Didier Imbault, Christophe Evrard, Philippe Repain, Patrick Ghislain, Colette Goffin, Andrée Guimard, Erwin Deumens

Without whom all these achieved results, presentations and the write up of the proposal would not have been possible.

Many thank to all of them