# Status and plans for DHCAL in Europe

Vladimir Ammosov IHEP, Protvino

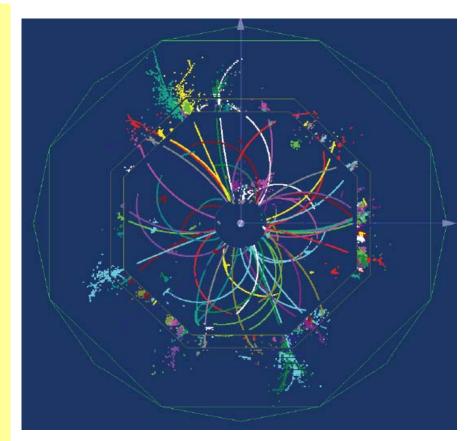

### DHCAL motivation for ILC

- Particle Flow Approach requires high longitudinal and transverse granularity in calorimetry for precise jet measurement

- It implies highly segmented steel sandwich calorimeter (HCAL) for hadrons

- Digital Hadron Calorimeter (DHCAL) may provide fine segmentation (~1cm<sup>2</sup>) with simplest read out system which is enough for neutral hadron pattern recognition and µ ID

### Gaseous active medium candidates

#### IHEP (Protvino) + collaborators

LAPP (Annecy) + collaborators

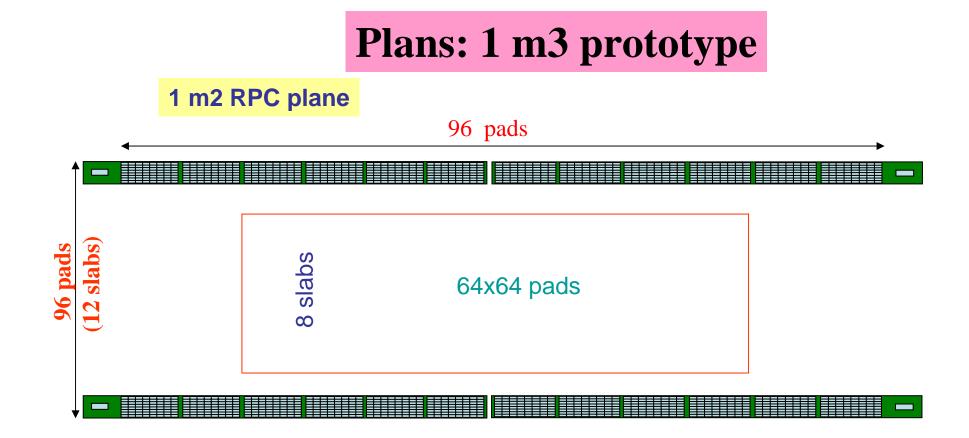

## 1m<sup>3</sup> DHCAL prototype

- It is needed to validate gaseous approaches, read out scheme; to compare with MC smulations and Sc. HCAL

- If 1x1 cm2 cells and 40 layers with 20 mm steel plates as absorber then ~400,000 channels are needed

- Collaboration between IPNL, LAL, LLR, LAPP, Saclay – France; CERN; CIEMAT- Spain; IHEP-Russia is forming to perform this within CALICE and EUDET framework

- Biggest challenge (and cost) read out electronics is responsibility of IPNL, LAL, LLR FE ASIC is needed

- This is as 2<sup>nd</sup> step towards the ILC

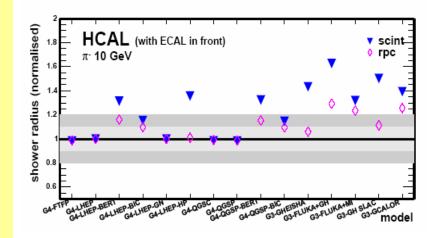

Comparison of hadron shower simulation codes by G Mavromanolakis

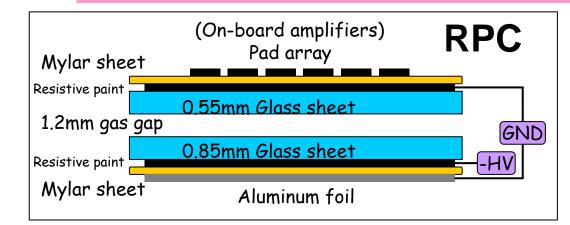

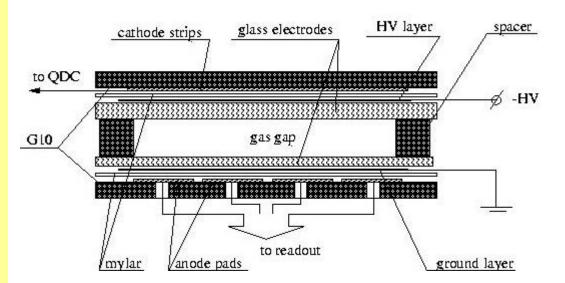

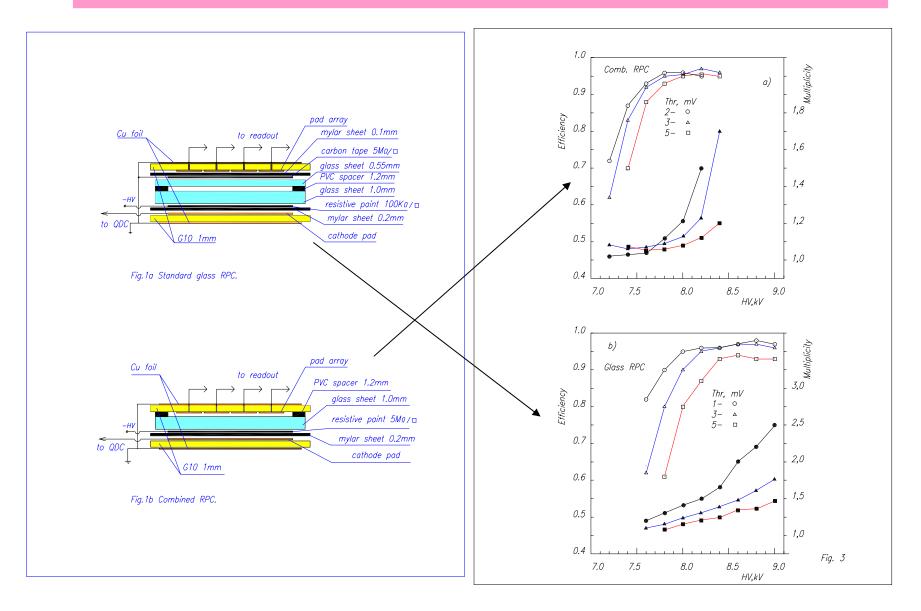

### Status: RPC performance and design

1.2 mm monogap glass RPC, saturate avalanche mode 98% eff , 1 kV plateau, ~1.4 mult Combined RPC – mult < 1.1</p>

| Ν | Item                | Thick, mm |

|---|---------------------|-----------|

| 1 | Anode printed board | 1.0       |

| 2 | Insulated mylar     | 0.05      |

| 3 | Graphite coverage   | 0.05      |

| 4 | Glass anode         | 0.55      |

| 5 | Gas gap             | 1.2       |

| 6 | Glass cathode       | 0.85      |

| 7 | Graphite coverage   | 0.1       |

| 8 | Insulated mylar     | 0.2       |

| 9 | Cathode PB          | 0.5       |

|   | Thickness budget    | 4.5       |

|   | Max thickness       | <8.0      |

|   | <b>Room for FEE</b> | ~ 3.5     |

|   |                     | ~ 3.5     |

Anode PCB – internal surface for pads, external one for RO electronics Cathode PCB – internal surface for long strips for QDC read out (control)

# **Combined RPC**

# Status: 1m2 RPC plane

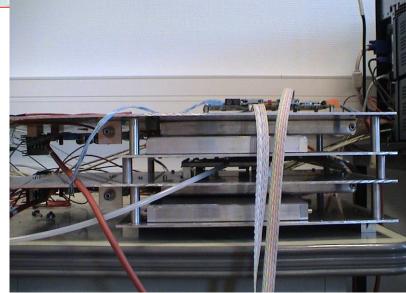

### Test of 1 m2 RPC plane

Cosmic ray trigger Using scint counters 96x6 cm2 2 counters - top 1 counter – bottom

TFE/IB/SF6=90/5/5 gas mixture

robust design, eff~94%, non uni <2%

February 13, 2007

V.Ammosov DESY, CALICE meeting

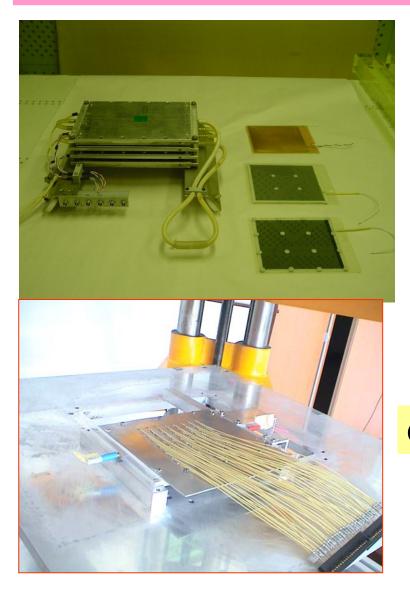

### **IPNL test bench**

### 2 GRPCs 8x8 pads is built with IHEP

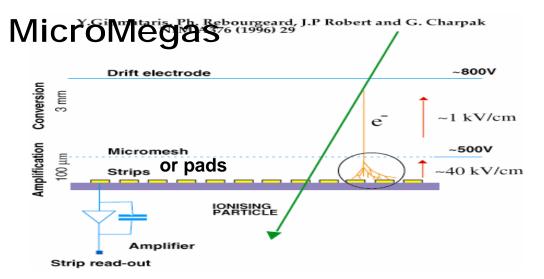

### **µMEGAS**s

8X8 pads is built with Saclay 6X16 pads is built with CERN

February 13, 2007

V.Ammosov DESY, CALICE meeting

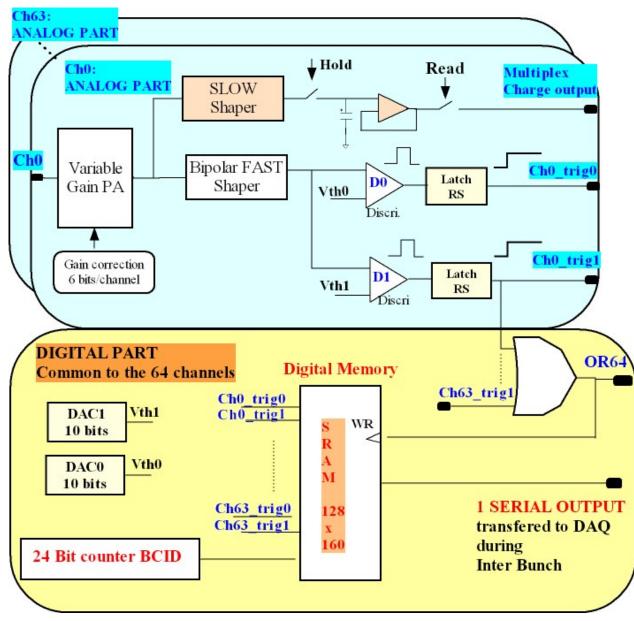

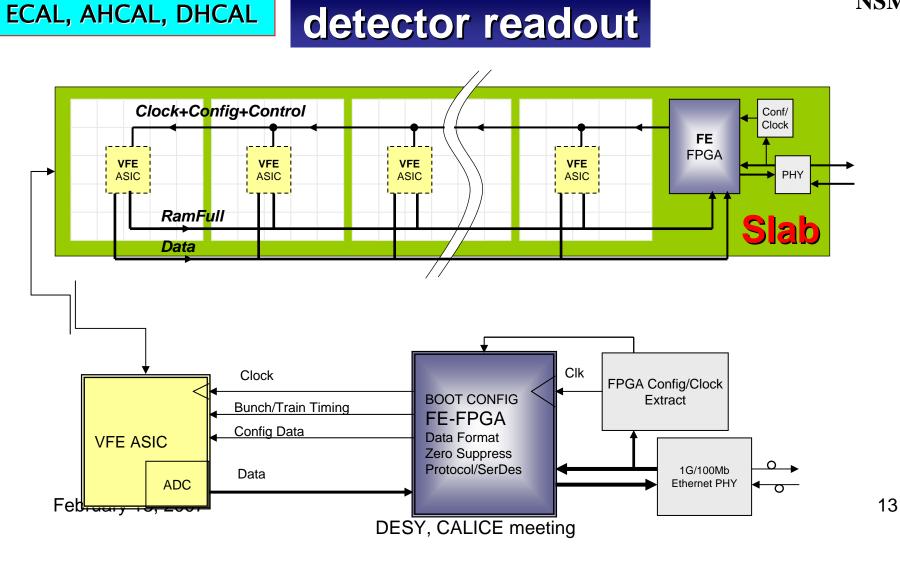

### **ASIC - HaRDROC architecture**

NSM

- Full power pulsing

- Digital memory: Data saved during bunch train.

- Only one serial output

- Store all channels and BCID for every hit. Depth = 128 bits

- Data format : 128(depth)\*[2bit\*64ch +24bit(BCID)+8bit(He ader)] = 20kbits

- Sequential readout @ 1 MHz

February 13, 2007

DESY, CALICE meeting

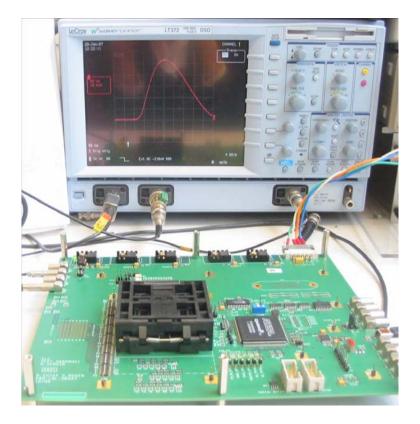

### **HaRDROC Status**

- 1-st iteration ASICs received end of December 06

- Testboard in Orsay to evaluate the analog performance of one HARDROC

- First analog measurements are in good agreement with expected results

- 7 testboards have been produced and will be available at the end of February to be sent in labs (IPN Lyon, LLR, Londres, Protvino...)

NSM

February 13, 2007

V.Ammosov DESY, CALICE meeting

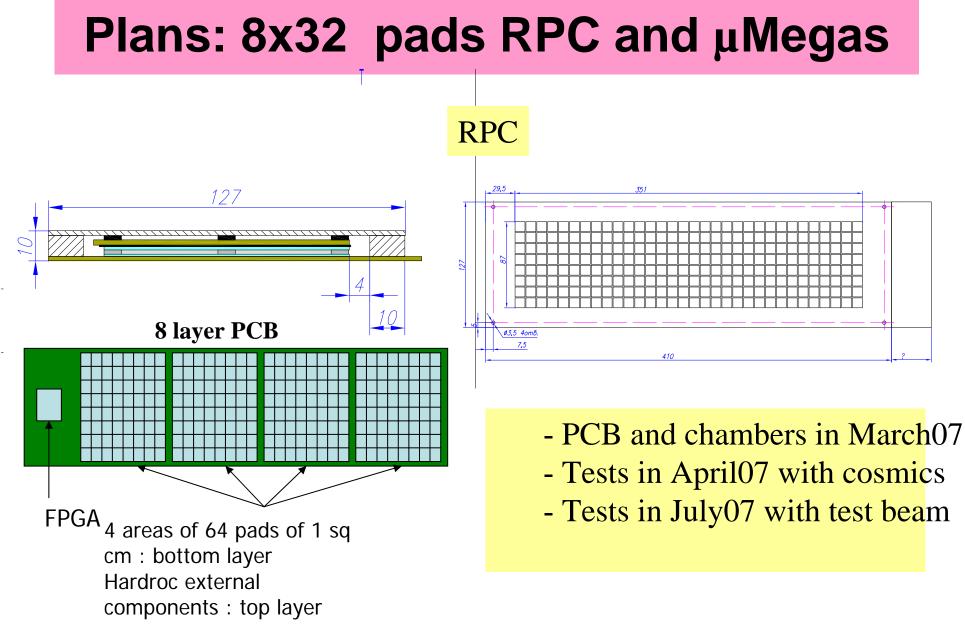

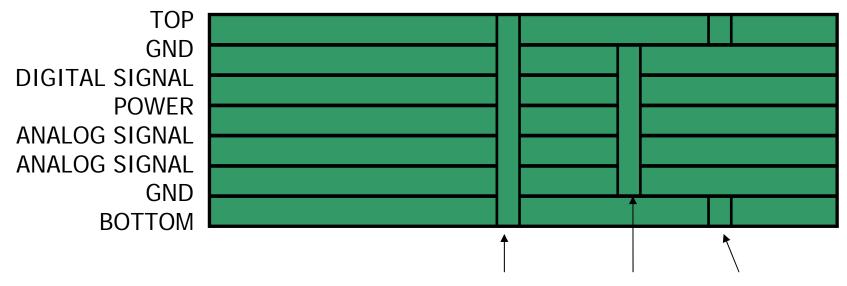

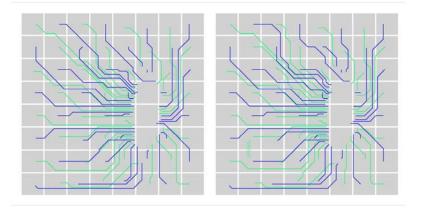

### **PCB Layout in 8 layers (solution1)**

#### Hervé MATHEZ

Through via Blind via Buried via

Digital architecture towards 2nd generation DAQ

NSM

96x96 pads  $\rightarrow$  64x64 pads ?

2 times less expensive but pure comparison with Sc. HCAL?

## Summary

- It seems that European collaboration for DHCAL is created

- DHCAL R&D was carried out already for

- RPC: is done

- MicroMegas: is in progress

- 8x32 pads RPC and μMegas chambers to validate readout system

- Tests in April07 with cosmics

- Tests in July07 with test beam

- ~1m<sup>3</sup> prototype

- 1<sup>st</sup> RPC and  $\mu$ Megas 1m2 planes at the end of 2007

- full stack at the end of 2008

- to decrease the cost it is desirable to consider lower lateral chamber dimensions (64x64 pads for example)

#### More close collaboration is needed

### Is 8x32 pads PCB optimal ?

#### Alternative proposal:

• 8x8 pads PCB as basic unit

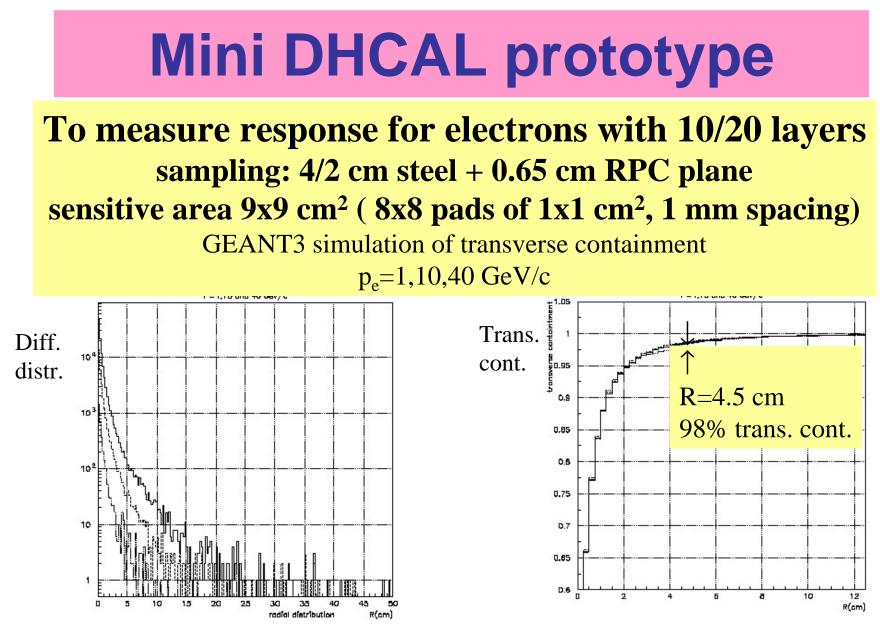

Can be used for existing 8x8 pads chambers, ANL 16x16 pad RPC, Mini DHCAL prototype to measure response for electrons with 10/20 layers with 64 pad RPCs

• 8x16 pads PCB to check all cross talks

Can be used with 8x16, 16x16 (ANL), 8x32 pad chambers Approach for 1m2 RPC can be checked

For IHEP RPCs design should be used for inside and outside gas volume options

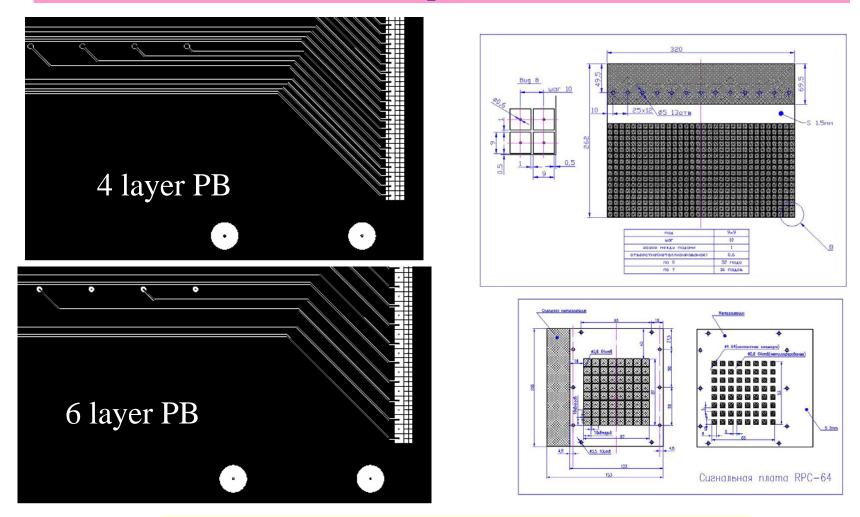

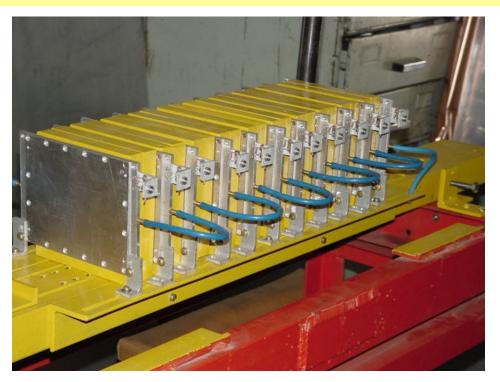

# 64 pads RPC

### 64 pads RPC as basic unit

# 64 pads RPC

### As element of 1m2 RPC plane with 10000 ch.

- Is ASIC on board or on side ?

- If ASIC is on side anode pads PB is designed

- Open or closed from anode ?

- Combined 64 pads RPC ?

- Gas system

- HV system

- Slow control (temperature, pressure)

- Charge read out from cathode

- Full acquisition (anode pads and cathode)

# **Anode pads PB**

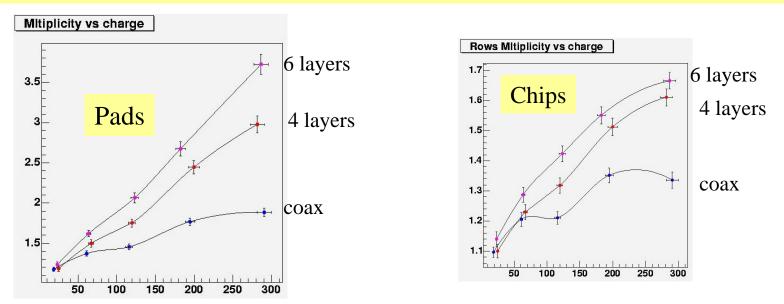

### **Prototyping of anode printed board for 64 pads of 1 cm2** with printed lines to side:

- 1. 2 layer PB huge cross talks

- 2. 4 and 6 layer PBs CT is still larger than for coaxial cables

# **Anode pads PB**

Decided to return to 2 layer PBs with coaxial cables

February 13, 2007

V.Ammosov DESY, CALICE meeting

21

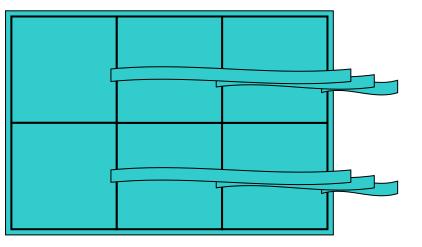

# Mini DHCAL prototype

Goal – first digital measurements of electromagnetic showers and comparison with simulations.

Usage of minimal number of RO channels ! (640/1280 ch.)

Most hard case for digital calorimetry !

February 13, 2007

V.Ammosov DESY, CALICE meeting

# Readout summary

|                             |                           |                 | <b>_</b> |          |

|-----------------------------|---------------------------|-----------------|----------|----------|

|                             | Item                      | DCAL            | KPix     | HaRDROC  |

| FE ASIC                     | Current version           | v2              | v3       | v1       |

|                             | Current ch#<br>/final ch# | 64/64           | 64/1024  | 64/64    |

|                             | Test                      | Almost done     | Ongoing  | Started? |

|                             | Additional submission     | No              | Yes      | ?        |

|                             | Overall status            | Almost done     | Ongoing  | Ongoing  |

| Readout<br>system<br>for PS | Conceptual design         | Done            | No       | No       |

|                             | FE board                  | Design finished | No       | No       |

|                             | Concentrator              | Design started  | No       | No       |

|                             | Data Collector            | Design ongoing  | No       | No       |

|                             | Trigger Timing<br>module  | Specified       | No       | No       |

|                             | DAQ software              | Started         | No       | No       |

<del>n rahanng pornito, givon oarront progrooo</del>

- The 1<sup>st</sup> PS stack would (naturally) be: RPC + DCAL based readout

February 13, 2007

DCAL readout will be validated through in the slice test (Apr.07, MTBF)

# **Costs and Funding**

A) Slice test is funded by LCDRD06, LDRD06 and ANL-HEP, and Fermilab funds

B) Prototype section not yet funded, but...

| Stack                     | Item  | Cost      | Contingency | Total     |

|---------------------------|-------|-----------|-------------|-----------|

| RPC stack                 | M&S   | 607,200   | 194,600     | 801,800   |

|                           | Labor | 243,075   | 99,625      | 342,700   |

|                           | Total | 850,275   | 294,225     | 1,144,500 |

| GEM stack <sup>*</sup>    | M&S   | 400,000   | 165,000     | 565,000   |

| * Reusing most            | Labor | 280,460   | 40,700      | 321,160   |

| of the RPC<br>electronics | Total | 680,460   | 205,700     | 886,160   |

| Both stacks               | M&S   | 1007,200  | 359,600     | 1366,800  |

|                           | Labor | 523,535   | 140,325     | 663,860   |

|                           | Total | 1,530,735 | 499,925     | 2,030,660 |

Proposal for supplemental funds for \$500k/year over two years submitted to DoE With continuing resolution, it is not very promising ... wait one more year?

# DHCal test beam plan

- US RPC + GEM: staged approach

- Feb.- Mar. 2007: GEM chamber characteristics run at Fermilab MTBF

- This will be done using 100 channel ADLink PCI based DAQ card

- April 2007: "slice test" at Fermilab MTBF

- Slice test: mini-calorimeter stack (~10 layers)

- Active medium: 8 RPCs + 2 GEMs, 16x16cm<sup>2</sup> active area in each chamber

- Absorber: 4mm copper + 16mm steel

- Validate DCAL chip + readout system for prototype section

- Readout system as close as possible to the 1m<sup>3</sup> prototype section

- Limited data/simulation comparison

- Later 2007:

- RPC: finish slice test, analyze data, prepare for prototype section

- GEM: continue on R&D, some beam test with KPix chip

- 2008: construction and test of prototype section (if funding permits)

- Construct 1<sup>st</sup> prototype section: RPC + DCAL readout

- European RPC effort: join the effort and supply part of the RPC's

- Detailed test program in Fermilab test beam

- Construct 2<sup>nd</sup> prototype section: GEM + ? Readout

- MicroMegas

- 2007: construct 1 50x50cm<sup>2</sup> chamber for beam test <u>Feb2008</u><sup>3</sup>, construct 1 layer of 100 x 100 cm<sup>2</sup> prototype DESY, CALICE meeting

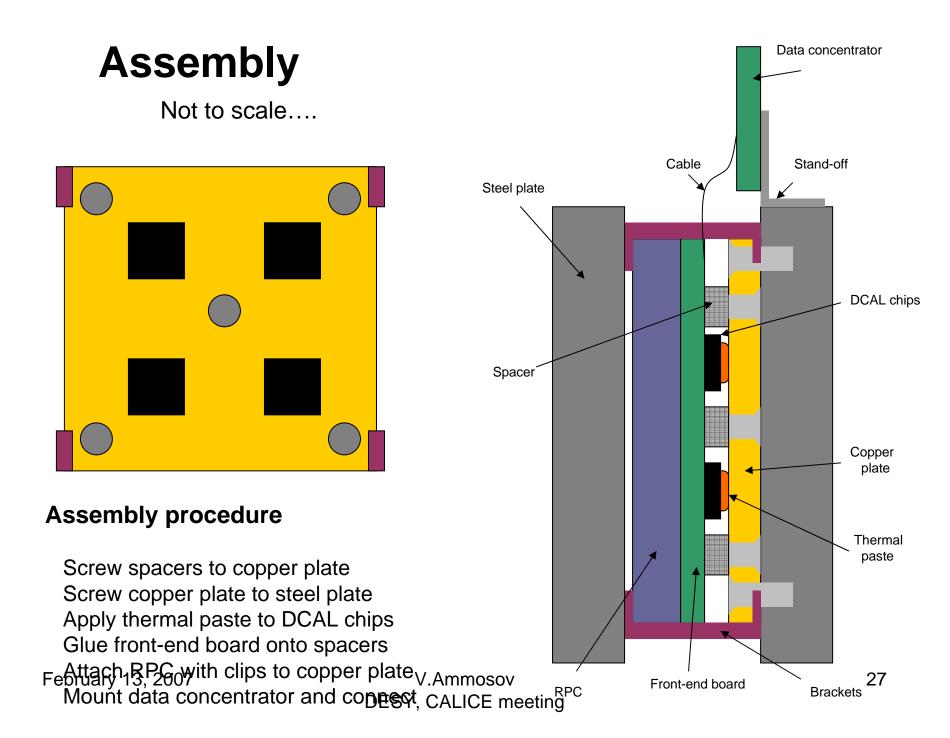

### Pad board and FE board (1) G Drake (ANL) FE board

#### New Concept

#### Split old 'Front-end board'

Pad board

'front-end board' highly complex and difficult blind and buried vias + large board => (almost) impossible to manufacture split into two boards to eliminate buried vias

0

#### Pad boards

four-layer board containing pads and transfer lines can be sized as big as necessary relatively cheap and simple vias will be filled

#### **Front-end boards**

eight-layer board 16 x 16 cm<sup>2</sup> contain transfer lines, houses DCAL chip expensive and tough to design

#### Connections

board to board with conductive glue on each pad (being tested)

26

| • | HV<br>Gas mixin<br>Beam telescope | Test FNAL unit with filters<br>Explore acquiring premixed gases<br>Build one 4x4 cm2 counter | lowa<br>UTA | Iowa |

|---|-----------------------------------|----------------------------------------------------------------------------------------------|-------------|------|

| • | Mechanical structure              | Build absorber stack<br>Think about glue dispenser<br>Find scanning table                    | ANL         |      |

| • | ASIC testing                      | Complete testing                                                                             |             | ANL  |

| • | Pad boards                        | Test gluing                                                                                  |             | ANL  |

| • | Front-end boards                  | Complete design                                                                              |             | ANL  |

| • | Data concentrators                | Complete design                                                                              |             | ANL  |

| • | Data collectors                   | Complete schematic                                                                           | Boston      |      |

| • | Timing and trigger module         | Decide on CAEN module/identify programmer                                                    |             |      |

| • | DAQ software                      | Acquire VME-PCI bridge<br>Start programming                                                  | ANL         |      |