# **DHCAL Progress Report**

José Repond Argonne National Laboratory

CALICE Technical Board Review, DESY, April 19 – 20, 2007

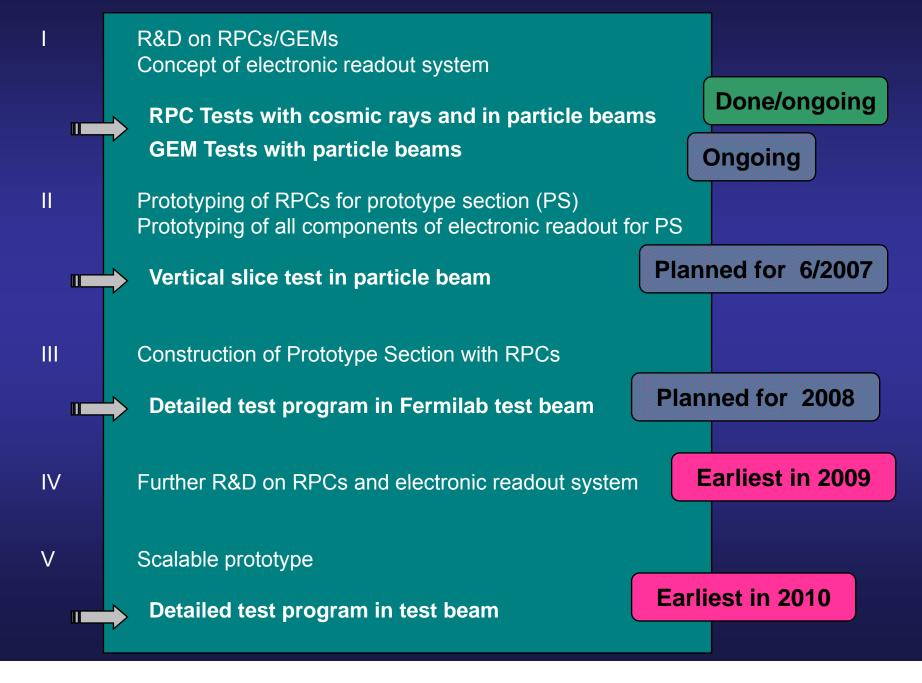

### **Staged approach**

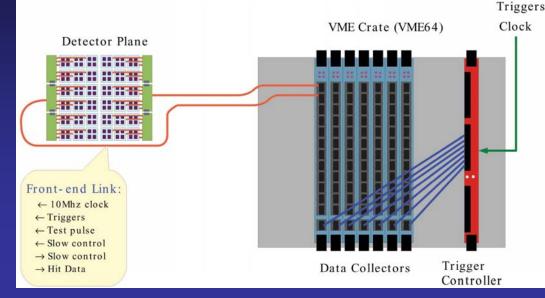

# **Vertical Slice Test**

Uses the 40 DCAL ASICs from the 2<sup>nd</sup> prototype run

Equip ~10 chambers with 4 DCAL chips each

256 channels/chamber ~2500 channels total

Chambers interleaved with 20 mm copper - steel absorber plates

Electronic readout system (almost) identical to the one of the prototype section

Tests in MTBF beam planned for Spring 2007

$\rightarrow$  Measure efficiency, pad multiplicity, rate capability of individual chambers

$\rightarrow$  Measure hadronic showers and compare to simulation

Validate RPC approach to finely segmented calorimetry Validate concept of electronic readout

| Responsibilities and colla                   | Argonne                  |                                       |

|----------------------------------------------|--------------------------|---------------------------------------|

| Task                                         | Responsible institutes   |                                       |

| RPC construction                             | Argonne, (IHEP Protvino) | BOSTON                                |

| GEM construction                             | UTA                      | UNIVERSITY                            |

| Mechanical structure (slice test)            | Argonne                  |                                       |

| Mechanical structure (prototype section)     | (DESY)                   | (DESY) CALLE                          |

| Overall electronic design                    | Argonne                  | Calorimeter for ILC                   |

| ASIC design and testing                      | FNAL, Argonne            | the France Halls                      |

| Front-end and Pad board design & testing     | Argonne                  | 🛟 Fermilab                            |

| Data concentrator design & testing           | Argonne                  |                                       |

| Data collector design & testing              | Boston, Argonne          | THE UNIVERSITY OF IOWA                |

| Timing and trigger module design and testing | FNAL                     |                                       |

| DAQ Software                                 | Argonne, CALICE          |                                       |

| Data analysis software                       | Argonne, CALICE          | ИФВЗ                                  |

| HV and gas system                            | Iowa                     |                                       |

| Beam telescope                               | UTA                      | The University of Texas<br>ARLINGTON. |

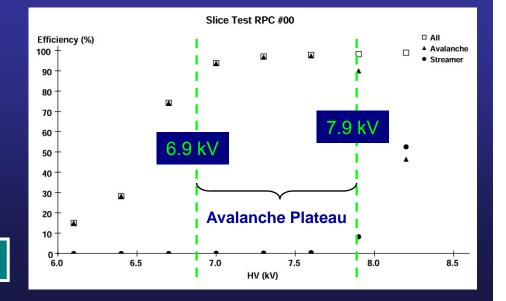

# **RPC** construction and testing (US)

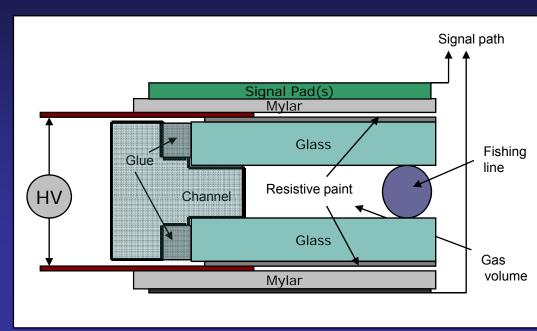

#### New design with simplified channels

Argonne

1<sup>st</sup> chamber assembled and tested

→ Excellent performance

Thickness ~3.5 mm (w/out pads)

2<sup>nd</sup> chamber assembled and tested

→ Excellent performance

3<sup>rd</sup> - 6<sup>th</sup> chamber being assembled

Material in hand for remaining chambers

# **RPC** construction and testing (Russia)

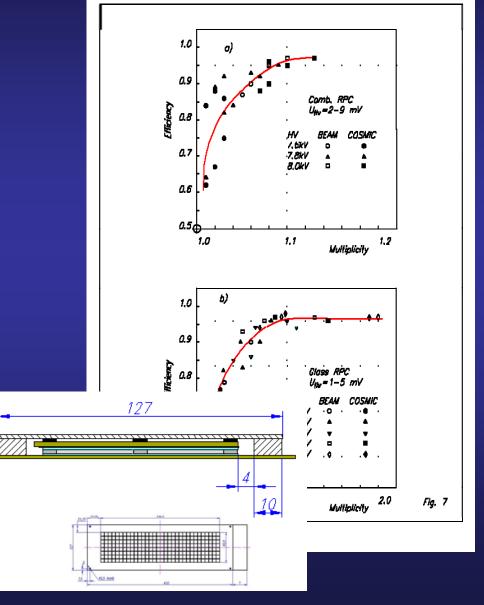

#### **Measurements with 1-glass plate chambers**

Pad multiplicity ~1.1 for an efficiency of 95% Confirms results obtained at ANL Long term tests ongoing

#### Constructed 4 chambers with 8x32 pads

One sent to Lyon for testing Others waiting for MAROC chip + FE-board Successfully tested with strip readout

#### Preparation for 1 m<sup>2</sup> chamber construction

Preparation of facility Cosmic ray test stand being assembled Design being finalized

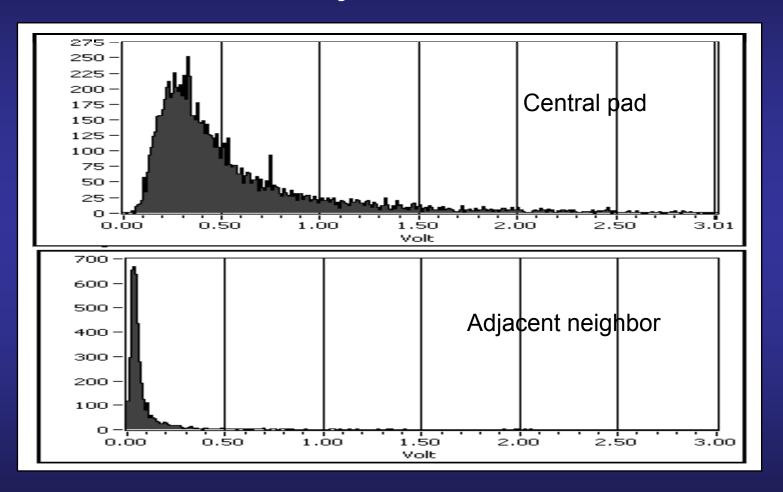

# **GEM** construction and testing

#### Chamber characteristics run

30 x 30 cm<sup>2</sup> foils from 3M

32 1 x 1 cm<sup>2</sup> readout pads

Analog readout with FNAL front-end and ADLink ADC card

#### Data runs

As the secondary user March 21 - 27As the primary user April 4 - 10

#### Goals

Measurements of gains, efficiency, pad multiplicity, noise rate, rate capability and uniformity of the response as function of gas mixture and HV

After increase of Voltage (drift gap)  $\rightarrow$  needed to reduce charge collection time

Data being analyzed: additional data taking needed?

# **Preparation for Slice Test**

#### **GEM** foils

4 sets of 3M foils HV tested

#### 2 chambers

Will be equipped with DHCAL readout electronics All components identical to RPC electronics 16 x 16 channels/chamber

Waiting for FE-board...

#### 2 chambers

Will be equipped with KPiX chip (not a slice test!) 8 x 8 channels/chamber

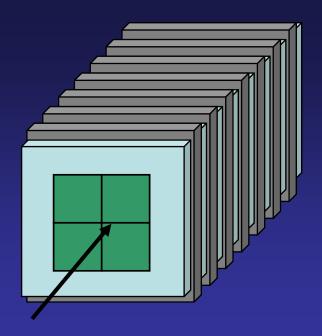

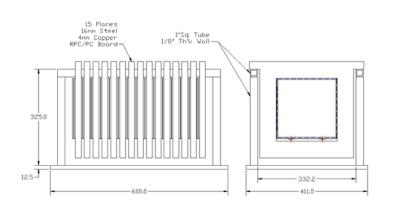

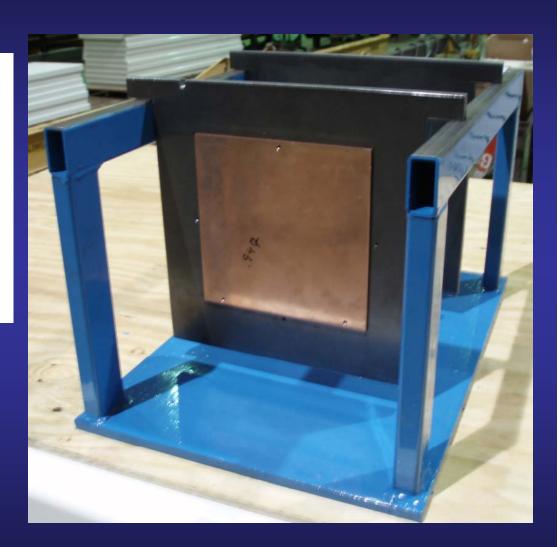

# **Mechanical: Stack for Vertical Slice Test**

Stack is assembled

Design accommodates 20 x 20 cm<sup>2</sup> RPCs as well as 30 x 30 cm<sup>2</sup> GEMs

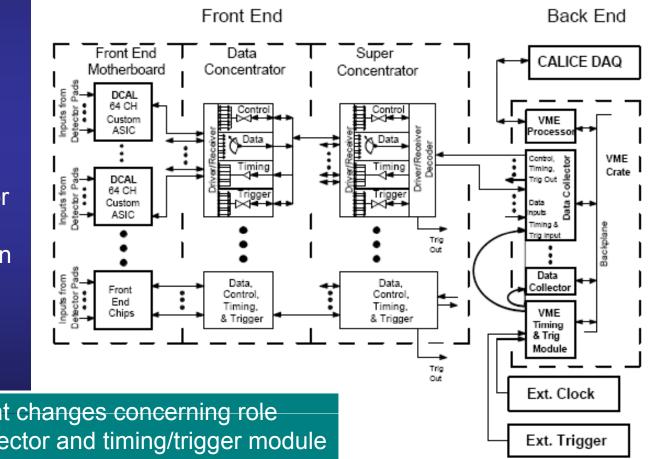

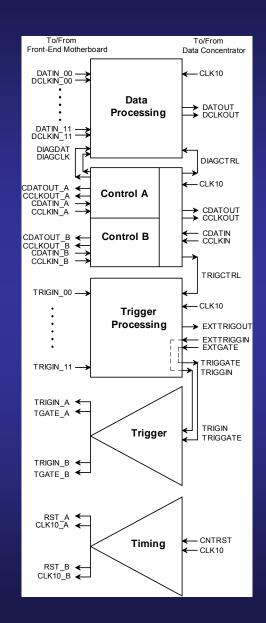

### **Electronic Readout System for Prototype Section**

40 layers à 1 m<sup>2</sup>  $\rightarrow$  400,000 readout channels More than all of DØ in Run I

- Front-end ASIC

- Pad and FE-board

- Ш Data concentrator

- Super Concentrator IV

- VME data collection V

- Trigger and VI timing system

Some recent changes concerning role of data collector and timing/trigger module

# **DCAL** chip

#### Design

- $\rightarrow$  chip specified by Argonne

- $\rightarrow$  designed by FNAL

### 1<sup>st</sup> version

- $\rightarrow$  extensively tested with computer controlled interface

- $\rightarrow$  all functions performed as expected

### Redesign

- $\rightarrow$  decrease of gain by factor 20 (GEMs) or 100 (RPCs)

- $\rightarrow$  decoupling of clocks (readout and front-end)

#### 2<sup>nd</sup> version

→ submitted on July  $22^{nd}$ → 40 chips in hand

### Test board

- $\rightarrow$  redesign of test board (changes in pin layout etc.) complete

- $\rightarrow$  boards fabricated

- $\rightarrow$  chip mounted on test board

### Testing (1/40)

$\rightarrow$  tests ~completed

CALICE Calorimeter for ILC

Reads 64 pads Has 1 adjustable threshold Provides Hit pattern Time stamp (100 ns) Operates in External trigger or Triggerless mode

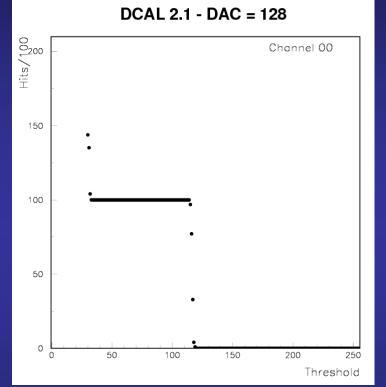

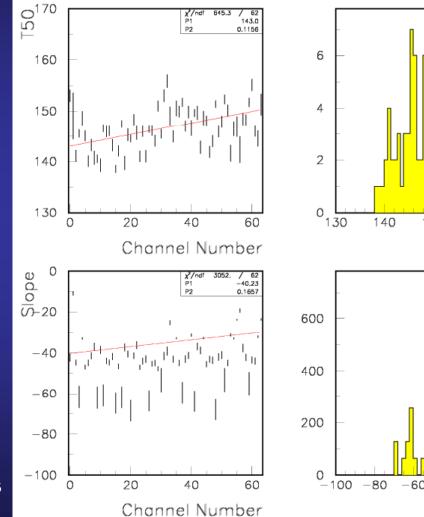

# **DCAL2** Testing I: Internal pulser

102 64

146.4

Entries

Threshold scans...

All channels OK, except Channels #31/32 show some anomalies (understood, no problem)

DCAL 2.1 - DAC = 192H

Mean RMS 3.990 150 160 170

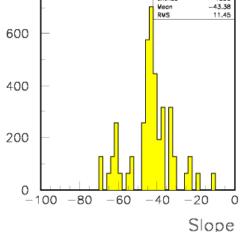

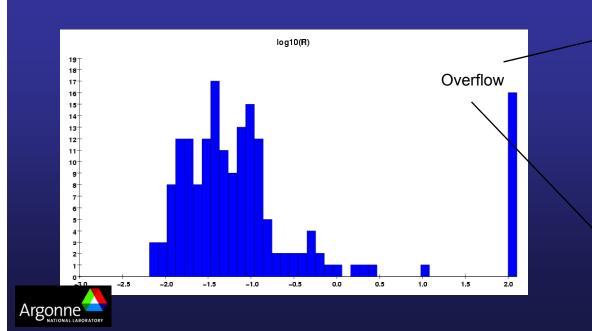

# **DCAL2** Testing II: Internal pulser

Ratio of high to low gain

$R = 4.6 \pm 0.2$

(roughly as expected)

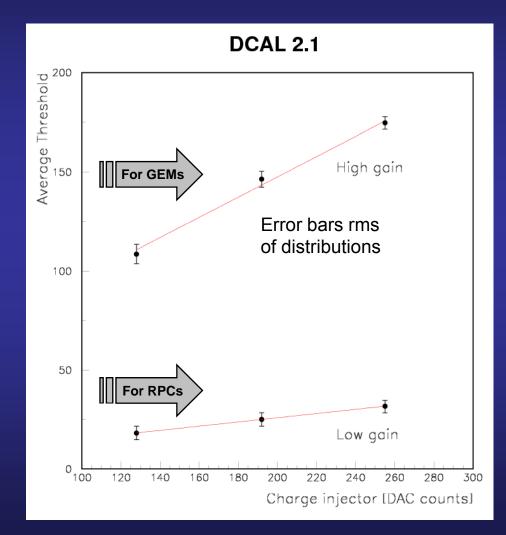

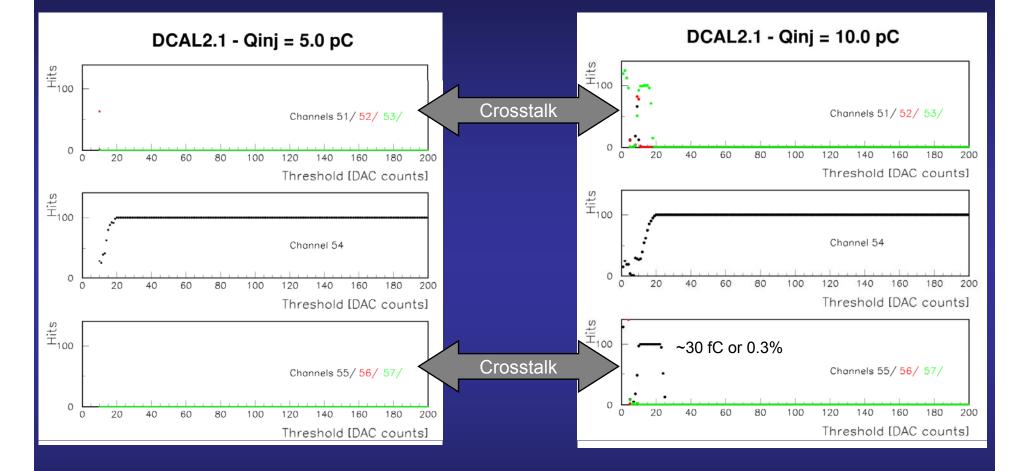

# **DCAL2** Testing III: External pulser

# **DCAL2** Testing IV: external pulser

Chips can be used for vertical slice test Small modifications still necessary for production

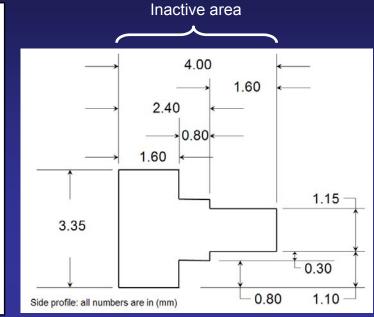

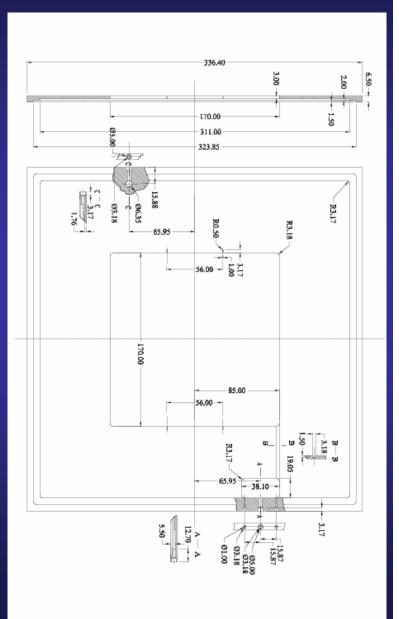

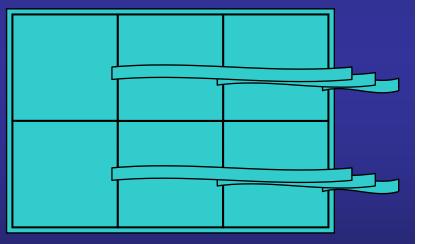

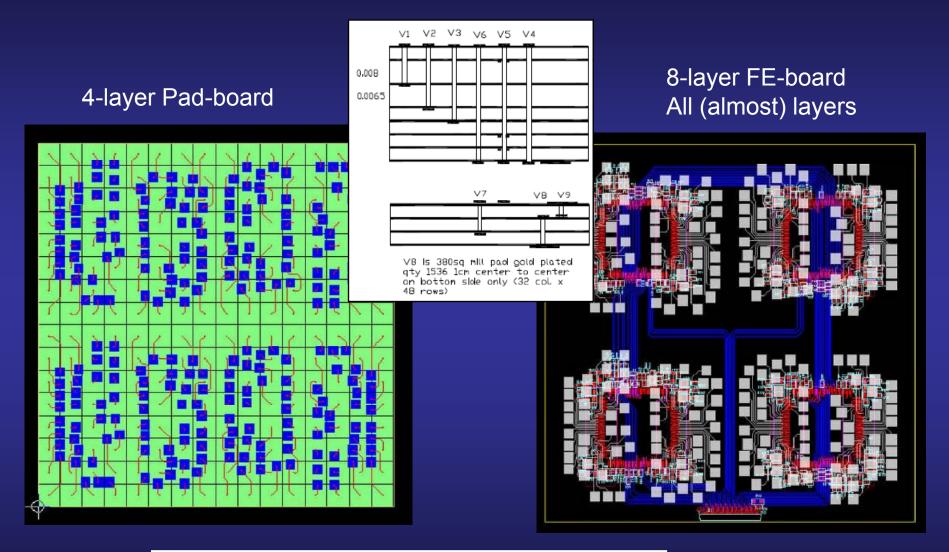

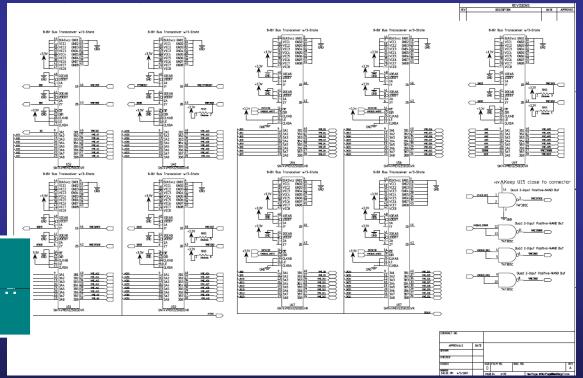

# Pad- and Front-end Boards I

### **New Concept**

### Split old 'Front-end board'

Pad board

FE board

'front-end board' highly complex and difficult blind and buried vias + large board => (almost) impossible to manufacture split into two boards to eliminate buried vias

#### Pad boards

four-layer board containing pads and transfer lines can be sized as big as necessary relatively cheap and simple vias will be filled

### **Front-end boards**

eight-layer board 16 x 16 cm<sup>2</sup> contain transfer lines, houses DCAL chips expensive and tough to design

### Connections

board to board with conductive glue on each pad cables for connection to data concentrators

# **Pad- and Front-end Boards II**

Design completed  $\rightarrow$  most intricate so far by Argonne group

# **Pad- and Front-end Boards III**

Front-end board: fabricated and (partly) assembled Test-board (computer interface): fabricated and assembled Testing software: to be adapted from previous DCAL2 tests

> The very first minute of life was a complete failure. Nothing worked. The signals were wrong everywhere. The fuses were blowing, couldn't talk to the PC interface board, cables were wrong, signals backward and scrambled, nothing worked.

So, everything was normal and as expected.

Tests started this week FE-board showing signs of life..

Pad-board: design completed Fabrication: received *reasonable* quotes

Waiting for OK from Front-end board

# **Gluing Tests**

Performed test with test boards Glued two boards to each other → strips of Mylar for constant gap size

Resistance <~0.1  $\Omega$ Glue dots small (~2 mm) and regular Edges lifted off  $\rightarrow$  non-conductive epoxy

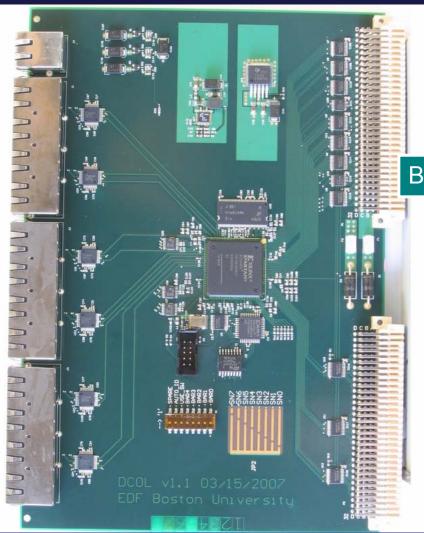

### **Data concentrator boards**

Design completed **Boards fabricated** 1/10 board assembled

Test board fabricated and assembled Tests to begin next week...

# **Timing and trigger module**

Provides clocks and trigger signals to individual DCOL boards

Schematic completed

Need 1 module for both the

Vertical Slice Test and the 1 m<sup>3</sup> Prototype Section

Board layout ongoing Fabrication next week... F/W 25% complete

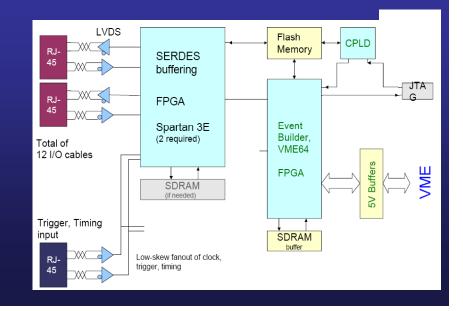

# Data collector boards

### **Functionality**

Receives data as packets

Timestamp (24 bits) + Address (16 bits) + Hit pattern (64 bits)

Groups packets in buffers (by matching timestamps)

Makes buffers available for VME transfer

Monitors registers (scalars)

Provides slow control of front-end

Allows read/write to DCAL chips or data concentrator boards

#### Need

unit for Vertical Slice Test

units for Prototype Section

Test board purchased Testing software ready Testing begun...

### Board fabricated and assembled

# Beam telescope, HV, and gas

#### CALICE Calorimeter for ILC

### **Beam telescope**

6 counters  $(3 \times (1 \times 1 \text{ cm}^2) + 1 \times (4 \times 4 \text{ cm}^2) + 2 \times (19 \times 19 \text{ cm}^2)$ Mounted on rigid structure Counters and trigger logic tested  $\rightarrow$  A.White

### HV modules

Need separate supplies for each chamber Modules (from FNAL pool) being tested

With additional RC-filter perform similarly to our Bertan unit in analog tests (RABBIT system) Digital tests satisfactory too

### Gas system

Need manifold for 10 chambers (in hand!) Will purchase pre-mixed gas (quote in hand)

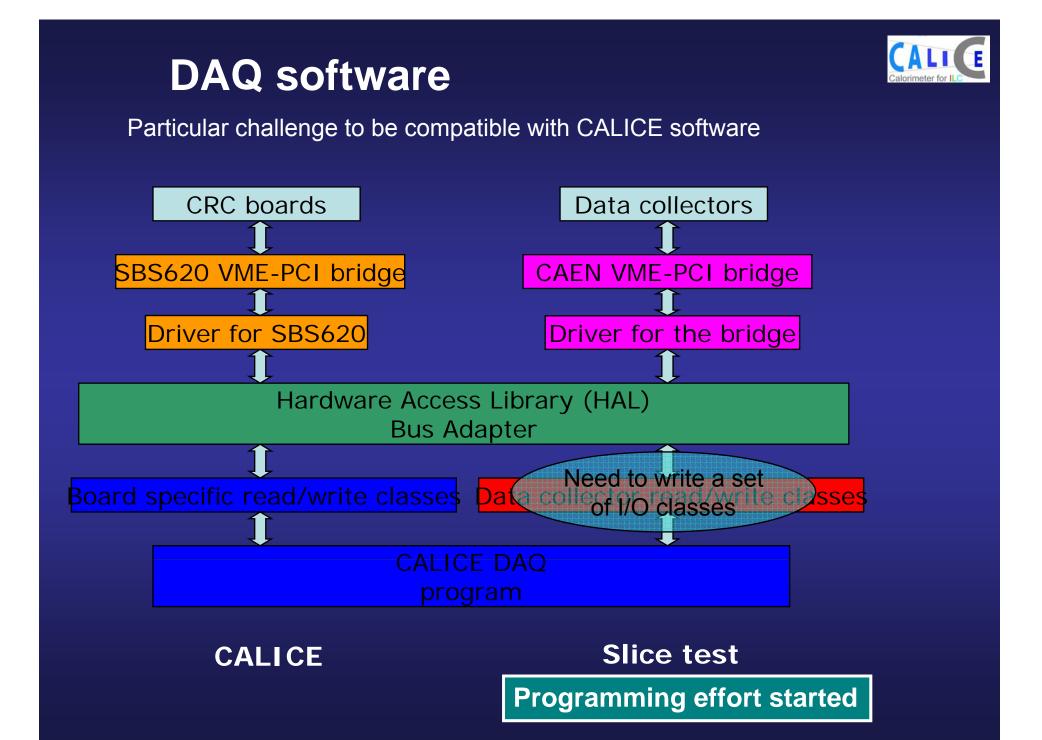

#### **Based on**

VME hardware interface and PCI-VME interface CERN HAL library CALICE DAQ framework (→ combined data taking) ROOT running on CERN Linux OS

#### **Two configurations**

Vertical Slice Test with 10 x 4 ASICs or 2560 channels Prototype Section with 40 x 144 ASICs or 400k channels

#### Data archived for offline analysis

Contains: run metadata, hit patterns & addresses & timestamps Configuration data stored in SQL database Data will be converted to LCIO format

#### DAQ software will be used

For hardware debugging In cosmic ray and charge injection tests In FNAL test beam

#### **Status**

HAL based testing and debugging system running Toy version of CALICE DAQ running with *old* VME hardware

#### **Next steps**

Define operations for new hardware Define data structure (binary files) Define data structure (offline)

# **Data Analysis**

#### For Vertical Slice Test only

#### Online histograms

Important in debugging phase Part of CALICE DAQ software DHCAL specific plots to be added

Σ<sub>all</sub>hit versus time

Σhit versus chamber

2dhisto of chamber hits (all layers)

2dhisto of chambers hits (per layer)

{Chamber efficiency and pad multiplicity}

#### II Analysis of binary files

Important in debugging phase Event display (to be adapted from CALICE-AHCAL) Track segment finder

#### III Conversion to LCIO

Standard for LC data bases Conversion to be done by CALICE expert (not urgent for VST, but necessary for later tests)

### Programming will start soon...

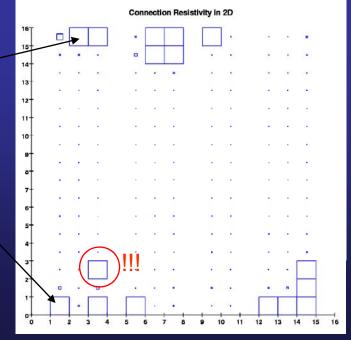

### **Track Segment Finder**

Loops over layers 1 - 8 Loops over hits in layer i Determines #neighboring hits N<sub>i</sub> Searches for aligned hits in layer i+2,3,4,5 Determines #neighboring hits around aligned hit

$N_{i+2}$ ,  $N_{i+3}$ ,  $N_{i+4}$ ,  $N_{i+5}$ ( $N_i$  = 0 ...no aligned hits)

Looks for aligned hits in layer i+1 Determines #neighboring hits N<sub>i+1</sub>

Efficiency of layer i+1

$N_{i+1}$  > 0.and. $N_{i+2}$  > 0(.and. $N_{i+3}$  > 0)

N<sub>i+2</sub>>0(.and.N<sub>i+3</sub>>0)

Pad multiplicity of layer i+1

$N_{i+1}$ , for  $N_i=1.and.N_{i+2}=1(.and.N_{i+3}=1)$

| Component                                     | February                                                              | March                                                       | April                         |                                                                      | Мау                 |                       | June                             |

|-----------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------|---------------------|-----------------------|----------------------------------|

| ASIC                                          | Complete testing<br>Provide new packing scheme<br>Order 40 additional |                                                             |                               |                                                                      | Test                | Test with cosmic rays | Move to MT6<br>Test in test beam |

| Gluing                                        | Test with regular epoxy                                               | Test with conductive epoxy                                  | Test with real b              | Develop gluing procedure<br>Test with real boards<br>Glue all boards |                     |                       |                                  |

| Pad boards                                    | Specify dimensions<br>Complete design                                 |                                                             | Order for RPCs                | 5                                                                    |                     |                       |                                  |

| Front-end boards                              | Complete design<br>Order 15                                           | Fabricate<br>Assemble                                       | Test                          | Test                                                                 |                     |                       |                                  |

| Interface board<br>(to test FE-boards + ASIC) | Complete design                                                       | Fabricate<br>Assemble                                       |                               |                                                                      |                     |                       |                                  |

| Data concentrator                             |                                                                       | Complete design<br>Fabricate<br>Assemble                    | Test                          | l v                                                                  | l<br>/ersior        | n from                | 4/9/2007                         |

| Data concentrator test board                  |                                                                       | Complete design<br>Fabricate<br>Assemble                    |                               |                                                                      |                     |                       |                                  |

| Data collector                                | Complete design<br>Acquire crates                                     | Fabricate<br>Assemble                                       | Test                          | -                                                                    |                     |                       |                                  |

| Data collector test board                     |                                                                       | Acquire<br>Write software                                   |                               |                                                                      |                     |                       |                                  |

| Timing & trigger module                       | Discuss with FNAL                                                     | Design                                                      | Fabricate<br>Assemble<br>Test |                                                                      |                     |                       |                                  |

| Software                                      | Acquire PC                                                            | Complete standalone<br>development (with 'old'<br>VME card) | Complete deve<br>DCOL         | lopment with                                                         |                     |                       |                                  |

| RPCs                                          | Complete #1                                                           | Test #1<br>Test #2                                          | Buil#3-6<br>Test #3-6         |                                                                      | Build #7-10<br>Test |                       |                                  |

| Offline                                       | Propose concept                                                       | Develop plan                                                | Write software                |                                                                      |                     |                       |                                  |

# Comparisons...

Identical

|                    | VST                                                   | PS                                               | ILCD                           |

|--------------------|-------------------------------------------------------|--------------------------------------------------|--------------------------------|

| RPCs               | 20 x 20 cm <sup>2</sup>                               | 32 x 96 cm <sup>2</sup>                          | Variable                       |

| DCAL chips         | 64 inputs<br>No power pulsing                         | 64 inputs<br>No power pulsing                    | > 64 inputs???                 |

| Front-end boards   | 4 ASICs/board<br>No optimization in<br>thickness/cost | 4 ASICs/board<br>No optimization in<br>thickness | >4 ASICs/board<br>Token rings? |

| Pad boards         | 16 x 16 cm <sup>2</sup>                               | 32 x 48 cm <sup>2</sup>                          | Variable                       |

| Data concentrator  | Input = 4 ASICs                                       | Input = 12 ASICs                                 | ?                              |

| Super concentrator | Not used                                              | Input = 6 Data<br>concentrator                   | ?                              |

| Data collector     | 12 inputs                                             | 12 inputs                                        | ?                              |

| Timing module      | 1 unit                                                | 1 unit                                           | Needed?                        |

| н                  | 1/chamber                                             | 1/3 chambers                                     | ?                              |

| Gas lines          | 1/chamber                                             | 1/3 chambers?                                    | ?                              |

|                    | Conservative<br>design                                | Some<br>optimization                             | Highly<br>optimized            |

# Conclusions

### Going full speed!!!

### - Vertical slice test

Concentrated effort with

monthly meetings (whole effort) weekly meetings (ANL group)

All parts coming together (no apparent late comer)

Goal Cosmic ray test sin May 2007 Measurements in test beam in June 2007

#### - Prototype section

Expensive! (New revised cost estimate soon) Funding appears possible. This year will receive

\$250k + \$175k for RPC+electronics \$50k + \$? for GEM R&D

Goal  $\rightarrow$  RPC stack in 2008

# **P.S.** Do we need the prototype section?

Marty Breidenbach Adam Para GEANT needs cross sections, not calorimeter measurements Gas calorimetry is an old art (we can't learn anything new) Shower size measurements already exist

MINOS ~ TCMT 4 x 100 cm<sup>2</sup> strips versus 1 x 1 cm<sup>2</sup> pads Factor 400 !!! Scintillator versus gaseous TCMT RPC pad board (to scale)

# **Backup Slides**

# Funding

### LCRD funds for 2006

| RPCs (ANL, Boston, Chicago, Iowa) | \$98k |

|-----------------------------------|-------|

| GEMs (UTA, Washington)            | \$60k |

#### Supplemental LCRD funds for 2006/7

| Avai | lab | le <sup>.</sup> | fun | ds |

|------|-----|-----------------|-----|----|

|      |     |                 |     |    |

\$1,200k/year?

Submitted pre-proposal for RPC/GEM DHCAL

Requested \$1,200k for 2006 ~\$800k for 2007

- 2006 build RPC-DHCAL continue R&D on GEMs

- 2007 test RPC-DHCAL at MTBF build GEM stack

- 2008 test GEM-stack

DOE asked us to submit proposal for \$500k/year (done)

### **Costs and Funding**

A) Slice test is funded by LCDRD06, LDRD06 and ANL-HEP, and Fermilab funds

B) Prototype section not yet funded, but...

| Stack                  | Item  | Cost      | Contingency | Total     |

|------------------------|-------|-----------|-------------|-----------|

| RPC stack              | M&S   | 607,200   | 194,600     | 801,800   |

|                        | Labor | 243,075   | 99,625      | 342,700   |

|                        | Total | 850,275   | 294,225     | 1,144,500 |

| GEM stack <sup>*</sup> | M&S   | 400,000   | 165,000     | 565,000   |

| * Reusing most         | Labor | 280,460   | 40,700      | 321,160   |

| of the RPC electronics | Total | 680,460   | 205,700     | 886,160   |

| Both stacks            | M&S   | 1007,200  | 359,600     | 1366,800  |

|                        | Labor | 523,535   | 140,325     | 663,860   |

|                        | Total | 1,530,735 | 499,925     | 2,030,660 |

Proposal for supplemental funds for \$500k/year over two years submitted to DOE Help from ANL (LDRD), ANL-HEP, FNAL expected...