1

## **DIF for ECAL**

some Technical aspects - Mechanics - Signals

### DIF working group

#### R. Cornat - LPC

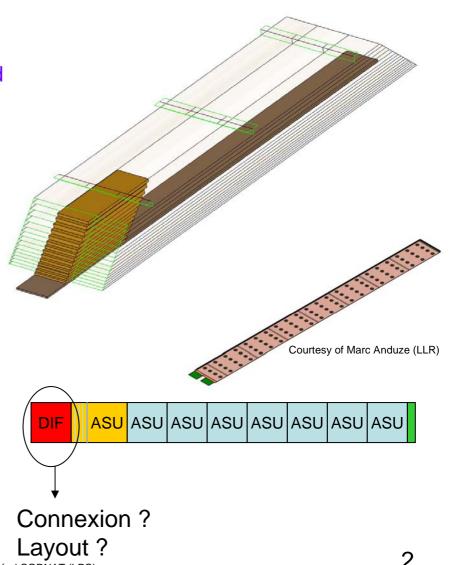

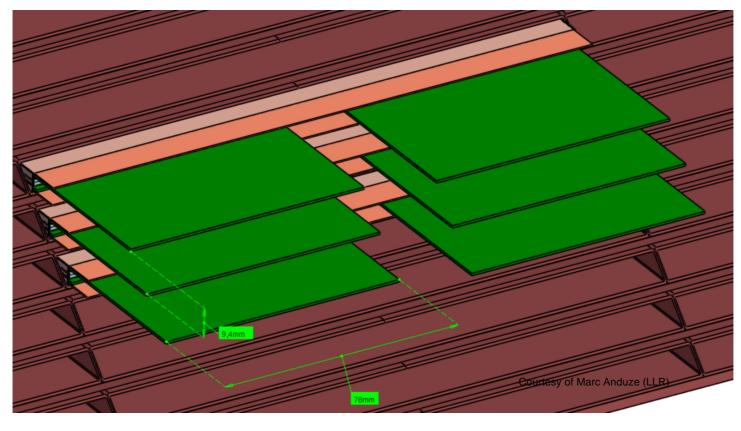

# EUDET Module (ECAL)

Concept : to be the most representative of the final detector module

- 15 Detector slabs with FE chips integrated —

- 1 long and complete slab (L=1.5m)

- 14 short slabs to obtain a complete tower of detection (typ. L=30 cm?) and design of compact outlet.

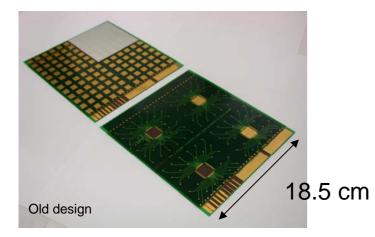

#### SLAB:

- 1 termination cap

- 7 stadard ASUs (Active Sensor Unit)

- 18.5 x 18.5 cm2

- 4 wafers of 18x18 pixels

- 4 SKIROC chips per wafer (81 channels each)

- 1 termination ASU

- variable length according to the layer

- 15 layers

- DIF

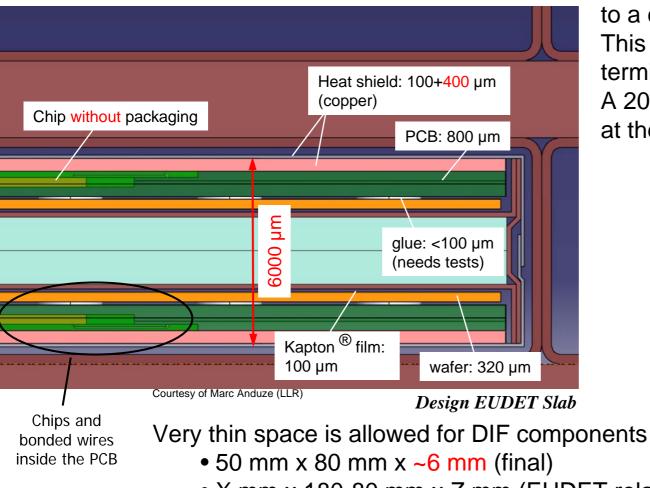

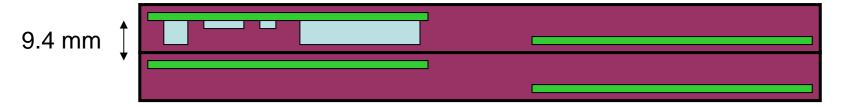

# Mechanical constraints for the DIF

The expected alveolar thickness

is 6.5 mm

Heat shield has to be connected to a cold pipe This pipe crosses DIF and/or termination ASU A 20 mm hole must be foreseen at the end of the SLAB

20 mm

• X mm x 180-80 mm x Z mm (EUDET relaxed constraints/options)

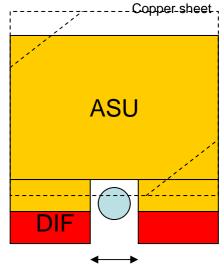

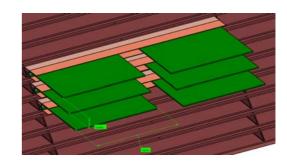

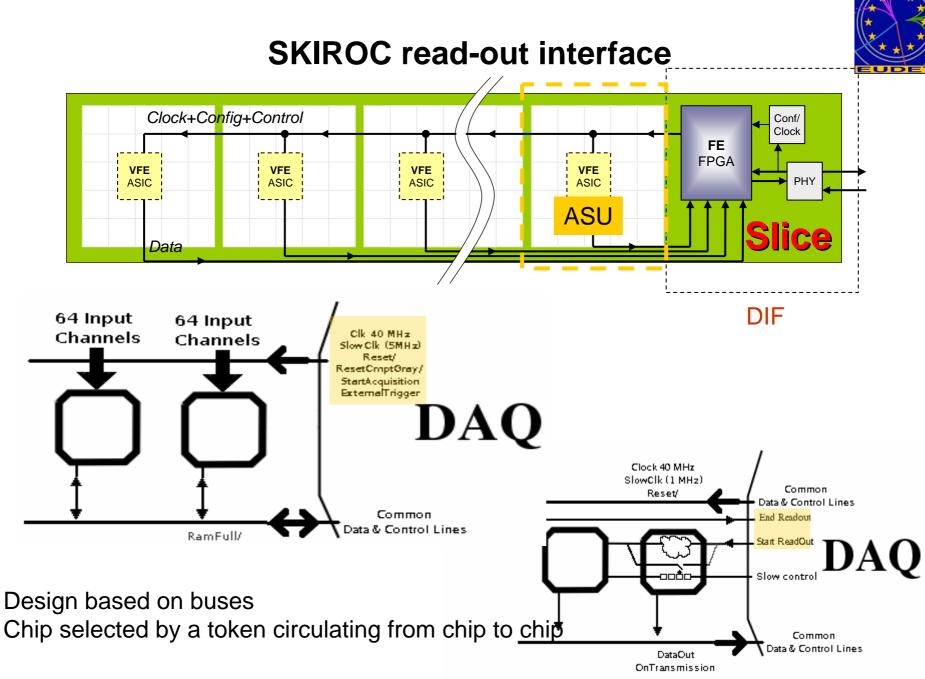

# Last ASU of SLAB - DIF

- DIF options

- Common DIF with additional adapter specific to the detector (power, ...)

- Adds a connector

- Differs from "ILC" version

- Rigidity of the end of the SLAB not ensured

- But...common DIF

- Mostly common DIF

- Shared designs

- But remains specific to detector

- DIF location

- Full width

- Poor 3 mm space allowed for DIF components

- Half width (see next transparency)

# Mechanical constraints for the DIF

#### 6 to 7 mm allowed for components but reduced width

# ASU edge connector

ASU will be glued edge to edge Glue provides electrical contact

Glue dot diameter reach 2 mm allowing a maximum number of contacts of about 3/cm.

Power supplies contacts extend by about 8 cm 25 to 30 signal contacts are allowed for a whole SLAB

### **SLAB-DIF** connector

### System requirements

- High Voltage

- Power

- Bias

- Clock, Control and Commands (CCC)

- Slow control

- Read-out

- Probe

- Reliability

- Power dissipation

- Testability

- Signal integrity

- Timing

- Mechanical constraints

- Successive versions of ROC chips

#### ASU/SLAB connector I/O LPC 22/06/07 CAT NAME GND 3.3V POWER BIAS REFERENCE clkp 40MHz DHCAL Category¤ Signal Function I/O-for- Valid-ECAL¶ AHCAL 1 (HARDROC) slab on¤ (SKIROC) (SPIROC)ª operation control reset\*< global-reset-of-complete-ASI LVCMOS LVCMOS LVCMO5 pwr.ong power-cycling control\* 0 high LVCMO5≈ LVCMO5\* LVCMO5# start-data-acquisition 0 LVCMOS<sup>®</sup> LVCMOS StartAcoto highe start-ADC-conve lo. LVCMOS start conv high 0 no trig erase active analogue column high Val Evt external-validation of event high LVCMOS\* LVCMOS trig\_exto RAZ\_Chro external-trigger\* high LVDS reset-for-internal-RS-flip-flops high (discriminator outputs)= slow control clk\_sc\* slow-control shift-reg. clock LVCMO5\* LVCMOS LVCMOS rising 1MHzr LVCMO5\* LVCMOS LVCMOS srin\_sco data input of slow control high reg.-chain= ASats analogue pipeline full-Oo higho 101 digital RAM fulls 0.0 high RamFulls LVCMOS stops current acquisition if an HC RAM is full= RamFull\_exte lø high bypass in bypass for token signal for ð readout= readouto Ou bypass out bypass-for-token-signal-fo high readout= debugging 10 LVCMOS hold exte external channel trigger= la high Raz chn into Ο¤ Out Tria into Ø spy-RS-outputs× Oø RS trig0¤ -10 RS\_trig1= spy-RS-outputs\* O¤ -10 spy discrim. outputs= TrigO¤ O¤ -10 Trig1¤ spy-discrim. outputs= O¤ -12 Power¤ Ø Ø positive supply a +3.5V (digital + analog)× Ø -10 additional supplys +5V (DAC)= D2 -12 GND a common-arounds -0 detector bias¤ HV≈ Ø -12 Calibration and a Ø Monitoring¤ Sensor Powerp Power for temperature a -10 monitors Temps output of temperature Ο¤ -10 monitors Trigger\_Power¤ ×. power for trigger logic× -12 power for charge injection Charge\_Powers -10 circuits¤ LED Powers power for light calibration 10 -10

**VCALIB**®

Trigger¤

CTesta

302

2

system

signal

system¤

charge injection#

analogue level of calibration

fast-trigger-of-calibration

X -0

risina

10 -12

### **ASU-DIF ASU** connector

#### This list already includes 25 signals !

close to the limit

Discussions for optimization, reliability, ... are ongoing

Next step is to finalize system level integration (architecture, ...) for EUDET prototype

LVCMOS

LVCMOS<sup>®</sup>

Ø

Ø

10

0

power

power<sup>3</sup>

power¤

0

10

10

10

CC .

ö

32

(4)sIVCMOS(4)

LVCMOS (4)

(4)¤

12

powero

powers

powers

Ø

Ø

XX.

×2

10

ö

ö

302

power(?)

power (

power (

power (4)¤

power (1)¤

power (2)¤

power(2)¤

power (2)¤

analogue

### Conclusion

Stringent mechanicals constraints

Choices should be done to remains close to what a final version could be

#### DIF task force

- to identify common part of the designs (ECAL, AHCAL, DHCAL)

- to work on system level integration

- manage all constraints (feasibility, reliability, tests...)

Firsts steps to list SLAB-DIF interface signals and optimisation

Specifications document at system level by the end of this year