Guide

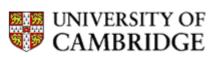

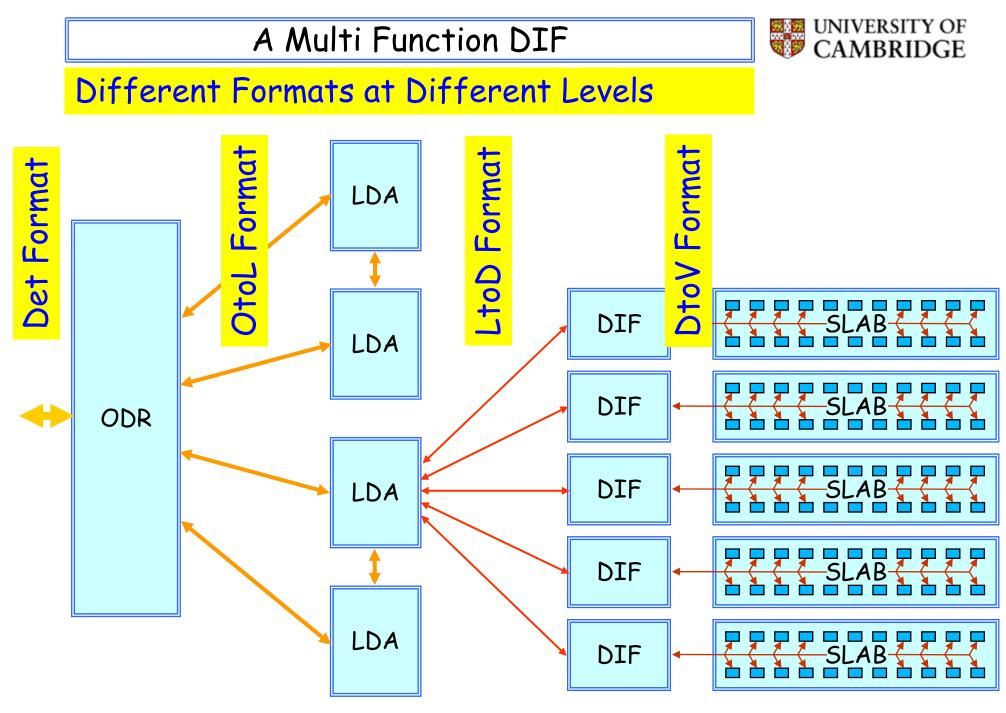

- .ODR-LDA-DIF-SLAB

- . Multitude of Signals

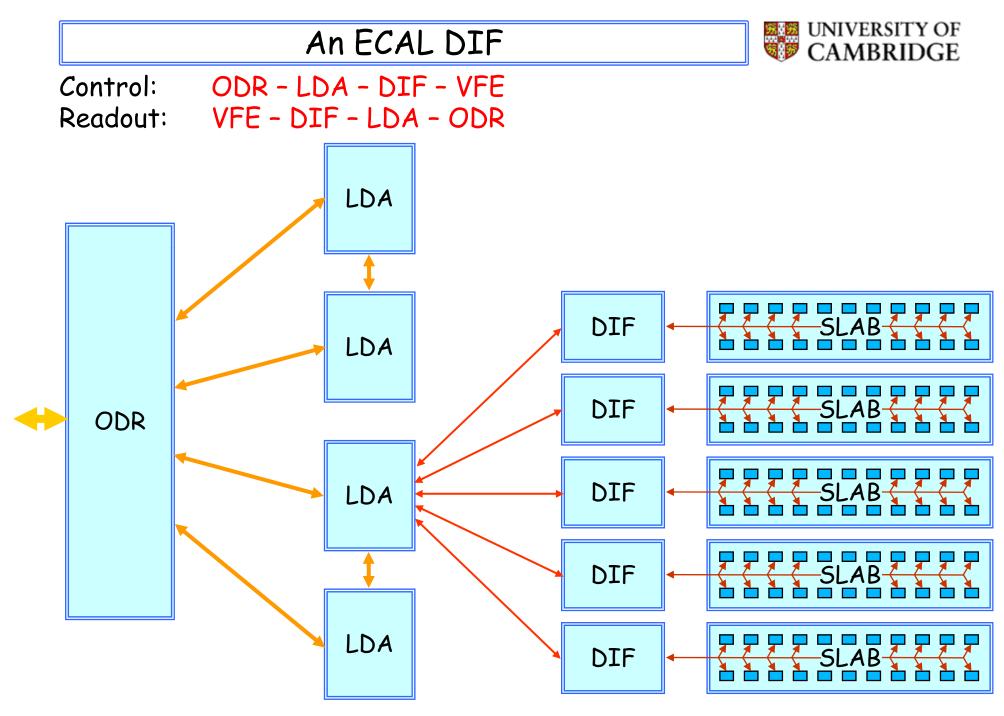

- Multi-Purpose ECAL DIF Model for Lab & Testbeam :

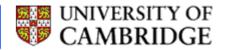

- Hardware = DIF + Adapter Card

- Firmware = DIF + Personality

- . Physical Arrangement for Prototypes

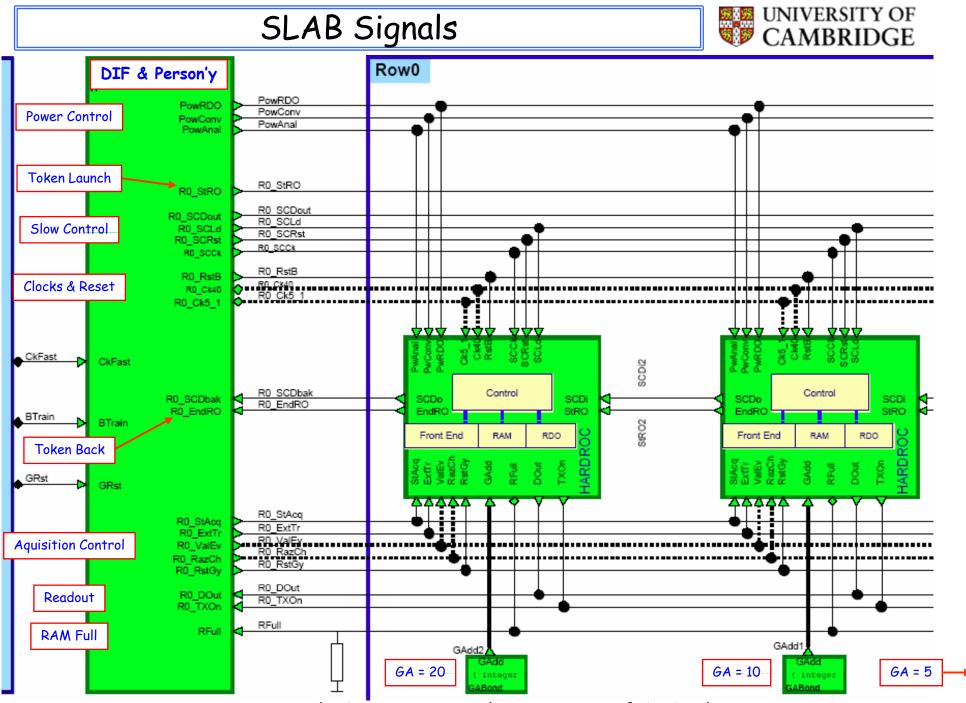

- SLAB signals :

- ECAL with SPIROC / HARDROC +

- . Simulation

- Special Lines:

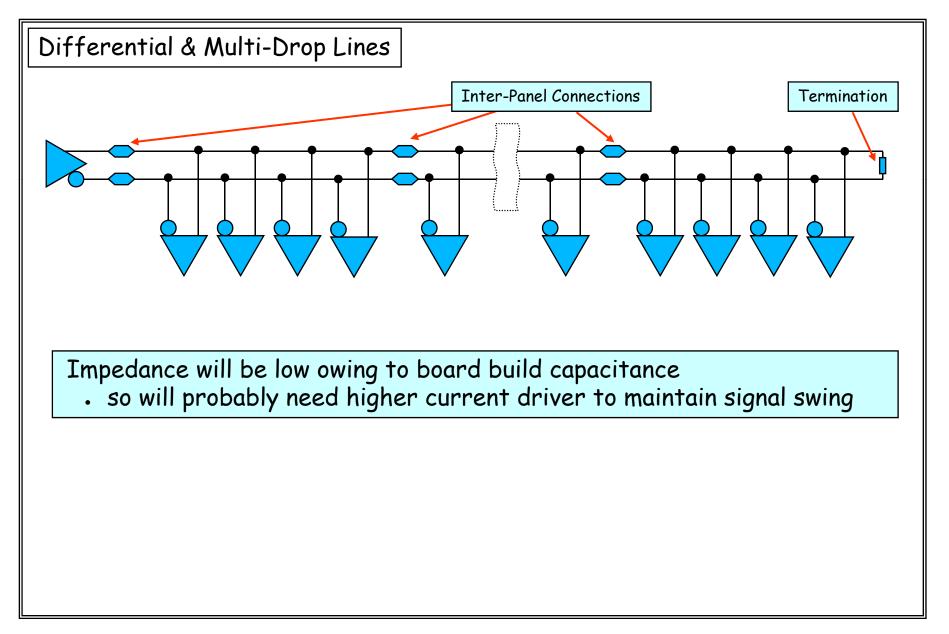

- Differential & Multi-Drop : Clocks,,, : Slab-end Termination

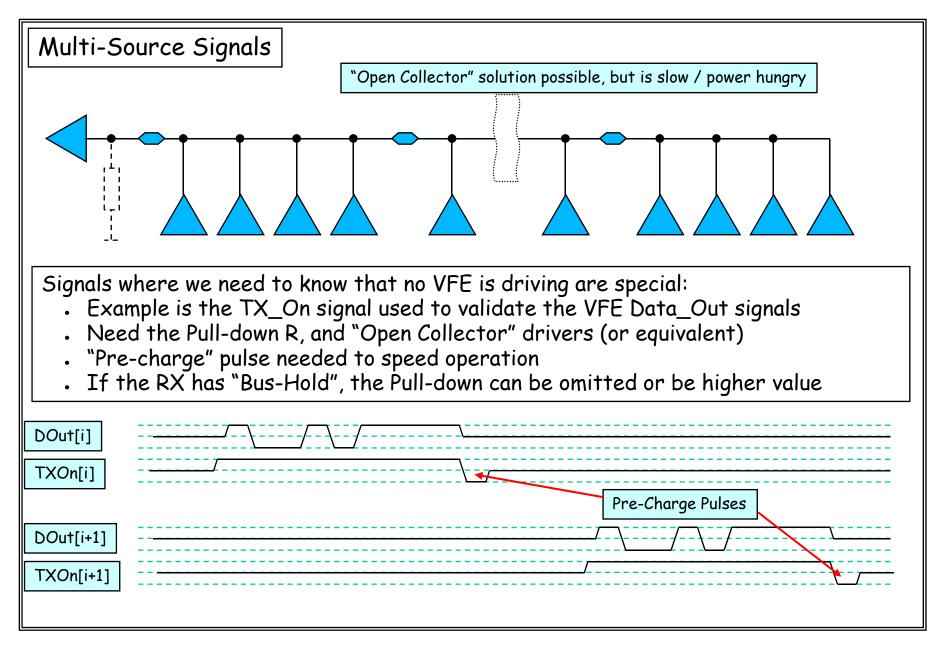

- Multi Source : Readout Data, TXOn,,,

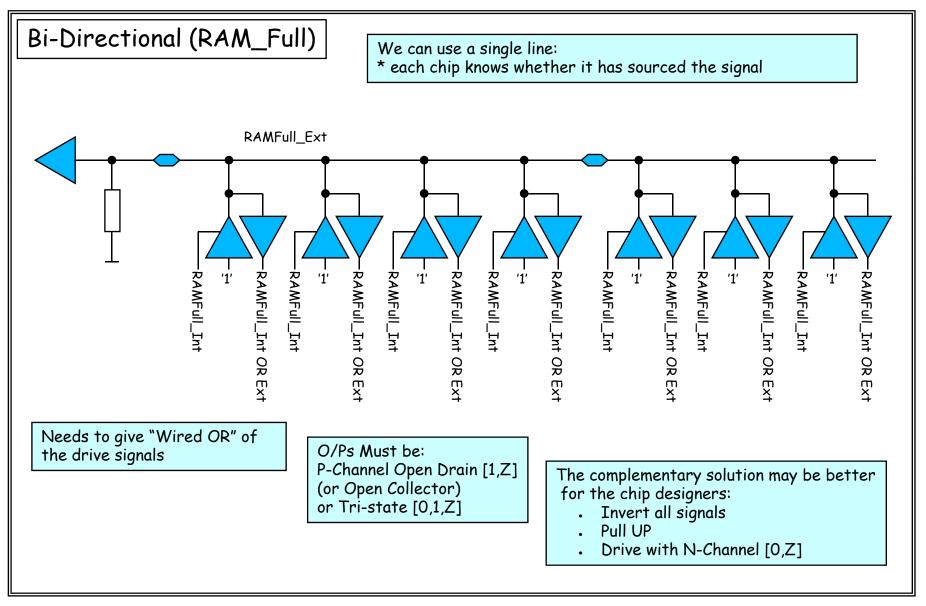

- Bidirectional : RAM Full (also Multi Drop) does "wired OR" polarity?

- Minimal Set

- Ext Trigger ??

- . Clock and Control?? needs CDR (PLL ?)

- . Slow Control :

- SPI, SPI-like, JTAG, I2C, I2C-like ??

- Broadcast ?

- Synchronous ?

- Chip Geographical Addresses : how: bonds, serial chain?

- . Redundancy : how? What cost? Needed?

Maurice Goodrick & Bart Hommels , University of Cambridge

#### A Multi Function ECAL DIF

### A Multi Function ECAL DIF - Physical

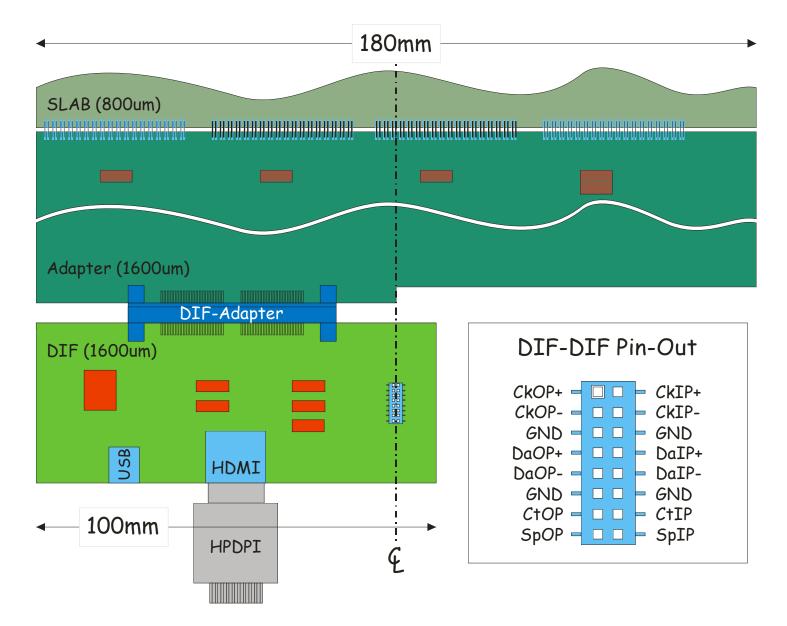

#### A Multi Function ECAL DIF - Stacking

UNIVERSITY OF

CAMBRIDGE

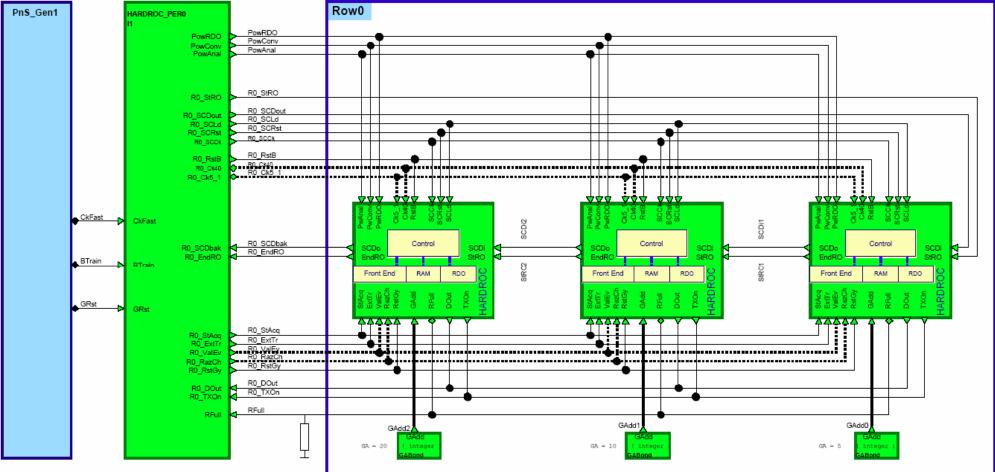

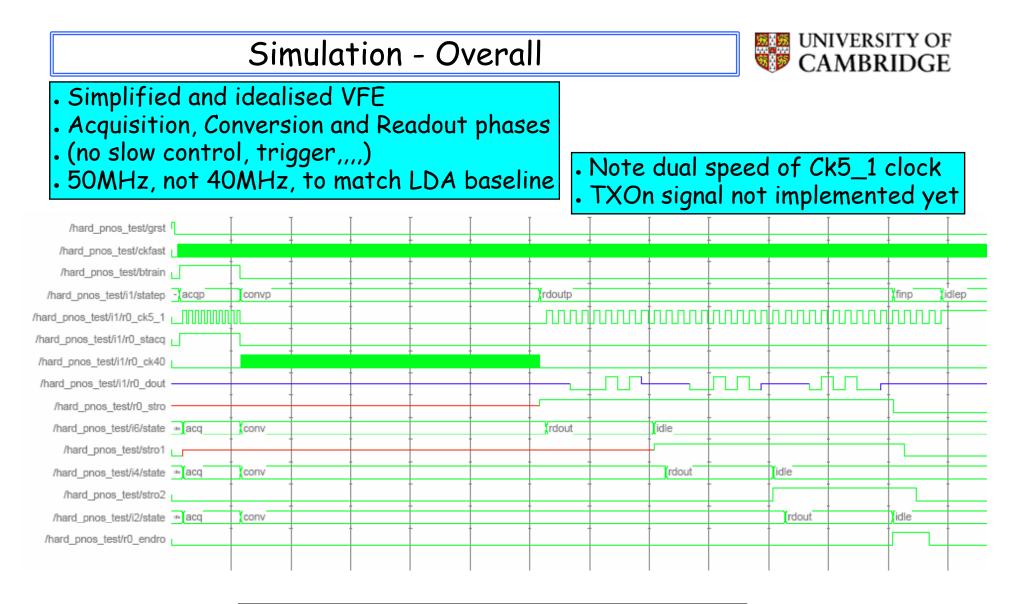

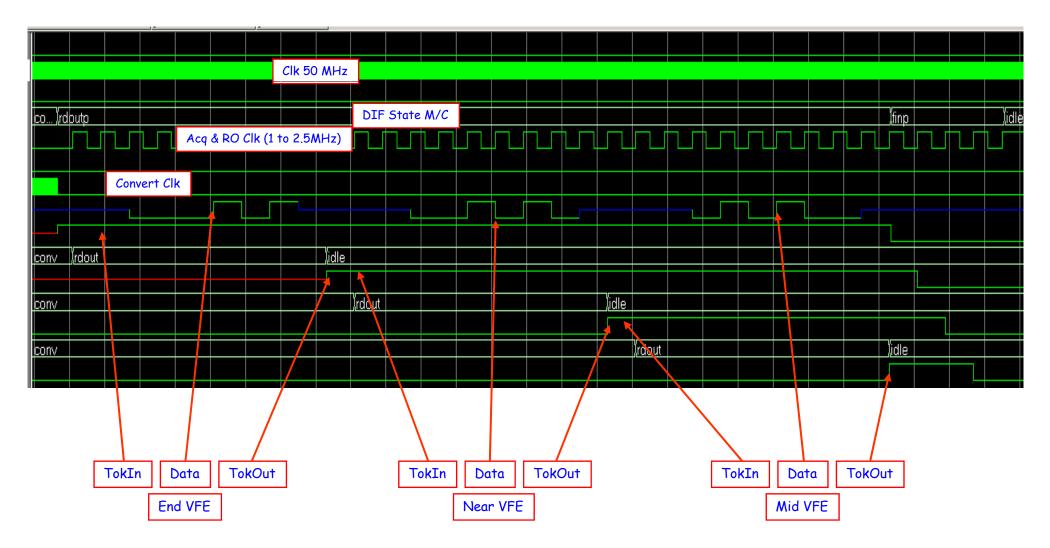

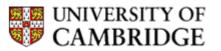

#### Simulation - 1 Row of "HARDROCs"

DIF & Pers

Will progress to using the HARDROC VHDL

Will add other signals

Will add slow controls

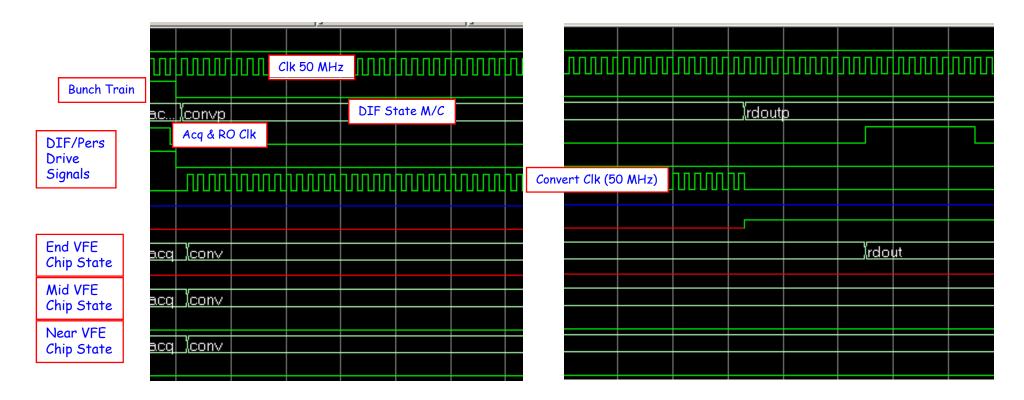

#### Simulation - Acquisition Phase

#### The first Ck5\_1 clock edge with Bunch\_Train TRUE causes VFEs to go into Acquire mode

|                           | 11'   |       |          | . <u>j</u>  |             |     |         |        |       |  | <br> |       |          |        |     |       |     |        |     |               |

|---------------------------|-------|-------|----------|-------------|-------------|-----|---------|--------|-------|--|------|-------|----------|--------|-----|-------|-----|--------|-----|---------------|

| st/g Global R             | eset  |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       |     |        |     |               |

| st/ckfast                 | 0     |       |          |             | Clk 50 M    | ٨Hz | תתתת    | תתתח   | โกกกก |  | תחחת | เกกกก |          | າມມາມ  |     | າກການ |     | INNN   |     |               |

| st/b <mark>Bunch</mark> T | rain  |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       |     |        |     |               |

| st/i1/statep              | idlep | idlep |          | <u>lacq</u> | 0           |     | DIF St  | ate M/ | С     |  |      |       |          |        |     |       |     |        |     | ,,<br>(con∨p  |

| DIF/Pers                  | 1     | Aco   | q & RO ( | Clk         |             |     |         |        |       |  |      | 5 MHz | : - 10 E | 3Xs sh | own |       |     |        |     |               |

| Drive                     | 0     |       |          |             |             |     | Start A | cqis'n |       |  |      |       |          |        |     |       |     |        |     |               |

| Signals                   | 0     |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       | Con | vert ( | Clk |               |

| st/i1/r0_dout             | Z     |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       |     |        |     |               |

| st/r0_stro                | In    |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       |     |        |     |               |

| End VFE<br>Chip State     | lle   | idle  |          |             | <u>acq</u>  |     |         |        |       |  |      |       |          |        |     |       |     |        |     | ∫con∨         |

|                           | -     |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       |     |        |     |               |

| Mid VFE<br>Chip State     | lle   | idle  |          |             | <u>lacq</u> |     |         |        |       |  |      |       |          |        |     |       |     |        |     | <u>l</u> conv |

| Near VFE                  | -     |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       |     |        |     |               |

| Chip State                | lle   | idle  |          |             | <u>lacq</u> |     |         |        |       |  |      |       |          |        |     |       |     |        |     | <u>¦con∨</u>  |

| st/rU_endro               | TU I  |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       |     |        |     |               |

|                           |       |       |          |             |             |     |         |        |       |  |      |       |          |        |     |       |     |        |     |               |

The first Ck40 clock edge with Bunch\_Train FALSE Causes VFEs to go into Convert mode

#### Simulation - Convert Phase

The DIF issues 4096 + n clocks to ensure all VFEs do conversion The VFEs will in general finish conversion early, and can power-save

The first Ck5\_1 clock edge with Token\_In TRUE causes VFEs to go into Readout mode

Line Specs

Line Specs

#### Line Specs

- Inter Panel connection is going to be DIFFICULT

- Probably limited to a few per cm of panel width ( so ~ 100 total inc power)

- . These connections are going to effect yield and reliability

- More signals = More Noise ??

- Redundancy schemes are likely to increase the number of signals by some factor (2, 1.5?)

- . Inter Panel connection is going to be DIFFICULT

- Probably limited to a few per cm of panel width ( so ~ 100 total inc power)

- . These connections are going to effect yield and reliability

- More signals = More Noise ??

- Redundancy schemes are likely to increase the number of signals by some factor (2, 1.5?)

## ?? How ??

- In principle very few signals can be used to operate the VFEs

- Moving the functionality of the "Personality" into the VFE does this

- "Flexible Clock" line could be used for further reduction

- . Inter Panel connection is going to be DIFFICULT

- Probably limited to a few per cm of panel width (so ~ 100 total inc power)

- . These connections are going to effect yield and reliability

- More signals = More Noise ??

- Redundancy schemes are likely to increase the number of signals by some factor (2, 1.5?)

## ?? How ??

- . In principle very few signals can be used to operate the VFEs

- . Moving the functionality of the "Personality" into the VFE does this

- . "Flexible Clock" line could be used for further reduction

## ?? What Cost ??

- Need to freeze operation into Silicon loss of flexibility

- Potentially more vulnerable to VFE failure

- . Inter Panel connection is going to be DIFFICULT

- Probably limited to a few per cm of panel width (so ~ 100 total inc power)

- . These connections are going to effect yield and reliability

- More signals = More Noise ??

- Redundancy schemes are likely to increase the number of signals by some factor (2, 1.5?)

## ?? How ??

- . In principle very few signals can be used to operate the VFEs

- . Moving the functionality of the "Personality" into the VFE does this

- . "Flexible Clock" line could be used for further reduction

# ?? What Cost ??

- . Need to freeze operation into Silicon loss of flexibility

- Potentially more vulnerable to VFE failure

# ?? Worth It ??

- Very large reduction in Signals

- Probably only way to have redundancy routing with acceptable connections

- 1. Do we need it? ... can we live with, say, 1% dead Slabs?

- 2. Detector Wafers and Interconnections fail, not ASICs

- 3. If the SLAB connections are in rows (6?), is a dead row important?

- 4. Could redundancy be done at the level of the Panel?

Other Issues

- .Ext Trigger ?? & other prompt signals

- . Clock and Control?? needs CDR (PLL ?)

- Slow Control :

- . SPI, SPI-like, JTAG, I2C, I2C-like ??

- Broadcast?

- Synchronous ?

- Chip Geographical Addresses : how: bonds, serial chain?

- . Chip Temp Monitoring?

- . Chip Serial Numbers?

- Panel Serial Numbers?

- . Current and Voltage Monitoring ?

- Maximising Reliability :

- By design

- . By QA and Environmental Testing

#### Spare Slides Follow

Heap of Slides from previous talks

Maurice Goodrick & Bart Hommels , University of Cambridge

## Environments

- Test Slab in the Lab WP2.2 core work

- EUDET prototype in the lab

- EUDET prototype in Test Beam

- Next ASICs

- . ILC environment

### **Control Requirements**

- . Clock

- Fast Controls

- . Slow Controls

- VFE specific

- Slab specific

- Broadcast

## Data Path Requirements

- Accumulated Rates

- . Adding Source Addresses

- Calibration ???

- VFE DIF LDA ODR chain: Architecture / Function / Hierarchy

- model as per Manchester workshop of 14-May-2007

- existing set-up mirrors this to some degree

- needed for prototype and EUDET slabs

- needed for final ECAL, HCAL and DAQ

- It is very worthwhile adopting this model at this at this stage:

- behavioural description is key:

- . will check the viability of the scheme

- . will allow fine tuning of the model

- will allow different flavours for different tasks (Test Panel, EUDET Prototype, ...

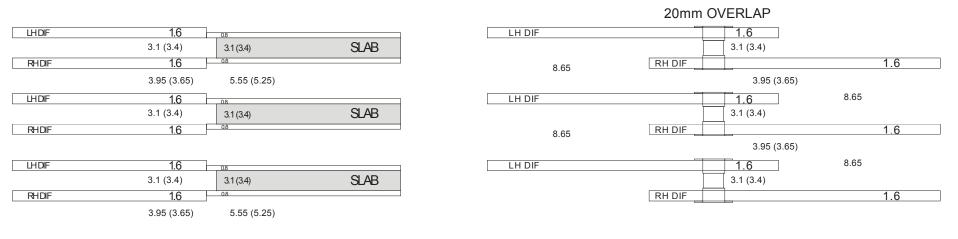

Card Spacing: based on Marc Anduze's ECAL Module design

#### NOMINAL SPACINGS (ADAPTER CARDS IGNORED)

Side View

**Rear View**

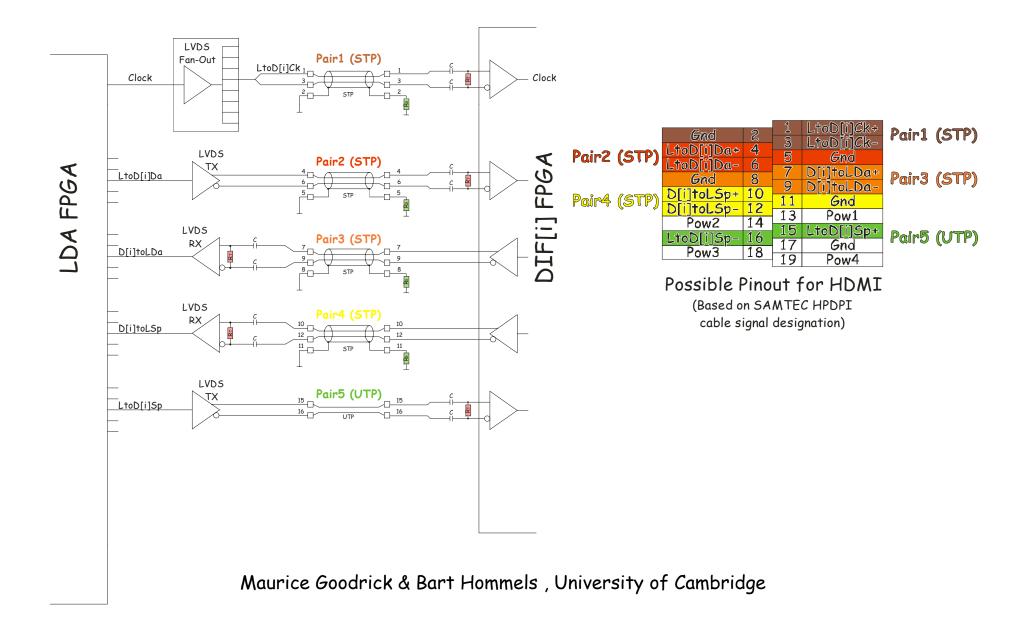

#### LDA-DIF Cable and Connector