# Electronics Developments for SITRA

Silicon strips readout using Deep Sub-Micron Technologies

#### Jean-François Genat

on behalf of

A. Comerma-Montells<sup>3</sup>, W. Da Silva<sup>1</sup>, J. David <sup>1</sup>, M. Dhellot<sup>1</sup>, D. Fougeron<sup>2</sup>, D. Gascon <sup>3</sup>, R. Hermel<sup>2</sup>, J-F. Huppert<sup>1</sup>, F. Kapusta<sup>1</sup>, H. Lebbolo<sup>1</sup>, T.H. Pham<sup>1</sup>, F. Rossel<sup>1</sup>, A. Savoy-Navarro<sup>1</sup>, R. Sefri<sup>1</sup>, S. Vilalte<sup>2</sup>

<sup>1</sup>LPNHE Paris, <sup>2</sup>LAPP Annecy, <sup>3</sup>UEB Barcelona

Work in the framework of the SiLC (Silicon for the Linear Collider), R&D Collaboration and the EUDET I3-FP6 European Project

1

EUDET Annual meeting October 8-10<sup>th</sup> 2007 Ecole Polytechnique Palaiseau, France

# Outline

| • | Detector data         | 2  |

|---|-----------------------|----|

| • | Technologies          | 5  |

| • | Front-End Electronics | 7  |

| • | 4-channel 130nm chip  | 11 |

| • | 128-channel chip      | 30 |

| • | Conclusion            | 39 |

### Silicon strips detector

#### Assume:

- A few 10<sup>6</sup> Silicon strips

- 10 60 cm long,

- Thickness 200–500 μm

- Strip pitch 50–200 μm

- Single sided, AC or DC coupled

- Strixels ?, 3D ?

#### Millions of channels: Integration of k-scale channels readout chips

### Silicon strips data at the ILC

#### Pulse height: Cluster centroid to get a few µm position resolution Detector pulse analog sampling

Time: 150-300 ns for BC identification, 80ns sampling Shaping time of the order of the microsecond

# Outline

| • | Detector data         | 2  |

|---|-----------------------|----|

| • | Technologies          | 5  |

| • | Front-End Electronics | 7  |

| • | 130nm chip            | 11 |

| • | 128 channels chip     | 30 |

| • | Conclusion            | 39 |

### Technologies

Silicon detector and VLSI technologies allow to improve detector and front-end electronics integration

#### Front-end chips:

- Thin CMOS processes 130, 90 nm available from Europractice (IMEC, Leuven)

- Chip thinning down to  $50 \,\mu m$

More channels on a chip, more functionalities, less power

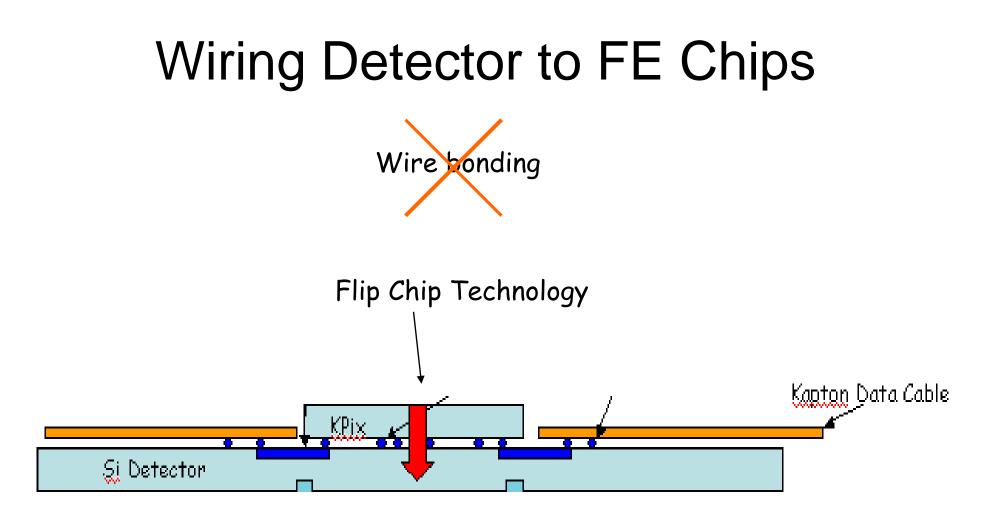

#### Connectivity:

- On detector bump (stud)-bonding (flip-chip) 50-100 μm pads

- 3D interconnections even less...

#### Smaller pitch detectors, better position and time resolution. Less material

# Outline

| • | Detector data         | 2  |

|---|-----------------------|----|

| • | Technologies          | 5  |

| • | Front-End Electronics | 7  |

| • | 130nm chips           | 11 |

| • | 128-channel chip      | 30 |

| • | Conclusion            | 39 |

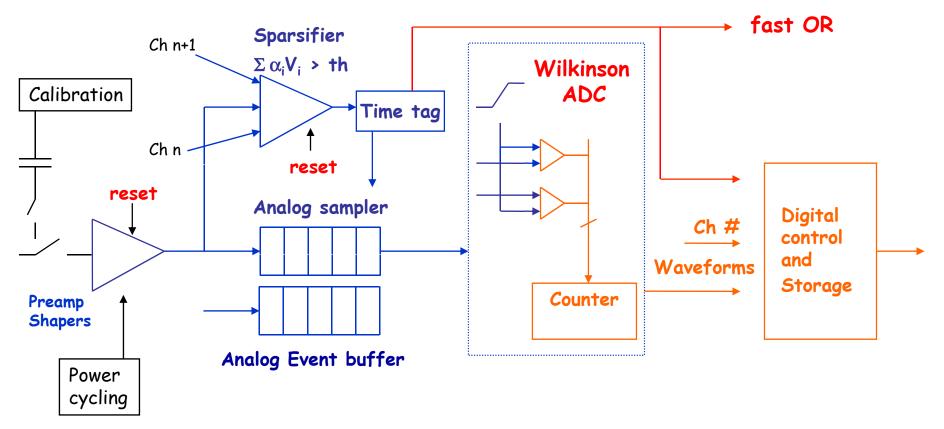

### Integrated functionalities

#### Full readout chain integration in a single chip

- Preamp-shaper

- Trigger decision on analog sums :

- Sampling:

- Analog event buffering:

- On-chip digitization

- Sparse data scan Analog pipe-line occupancy: 8-16 deep event buffer 10-bit ADC

- Buffering and pre-processing:

Centroids, Least square fits, Lossless compression and error codes

- Calibration and calibration management

- Power switching (ILC duty cycle)

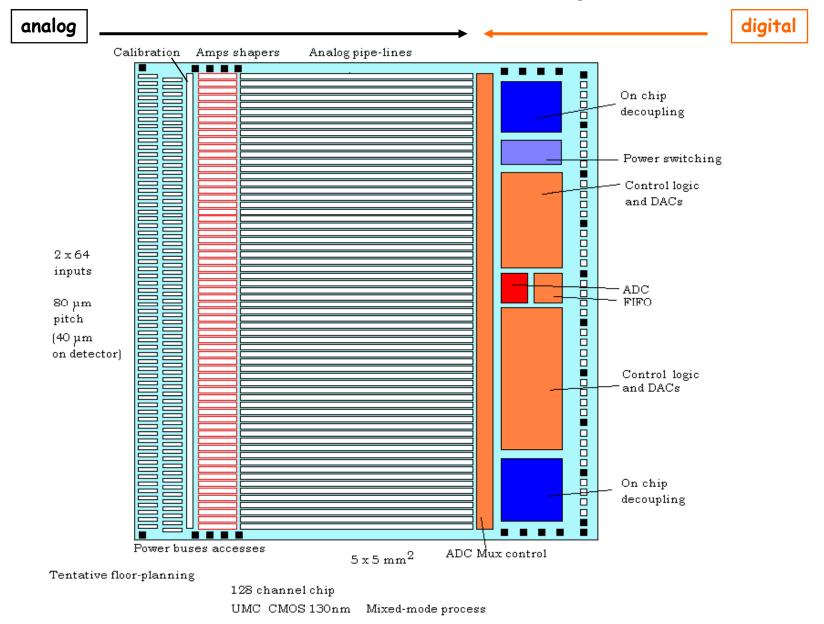

- Presently 128 channels in 130nm CMOS under design at LPNHE/LAPP/UEB having in view 512-1024 channels

### Front-End Chip goals

#### Integrate 512-1024 channels in 90nm CMOS:

|                  | Amplifiers:     | - 30 mV/MIP over 30 MIP range                                                                                   |

|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------|

|                  | Shapers:        | - Two ranges: 500ns-1μs, 1μs-3μs                                                                                |

|                  | Sparsifier:     | - Threshold the sum of 3-5 adjacent channels                                                                    |

|                  | Samplers:       | <ul> <li>8 samples at 80ns sampling clock period</li> <li>Event buffer 8-16 deep</li> </ul>                     |

| $\triangleright$ | Noise baseline: | ·                                                                                                               |

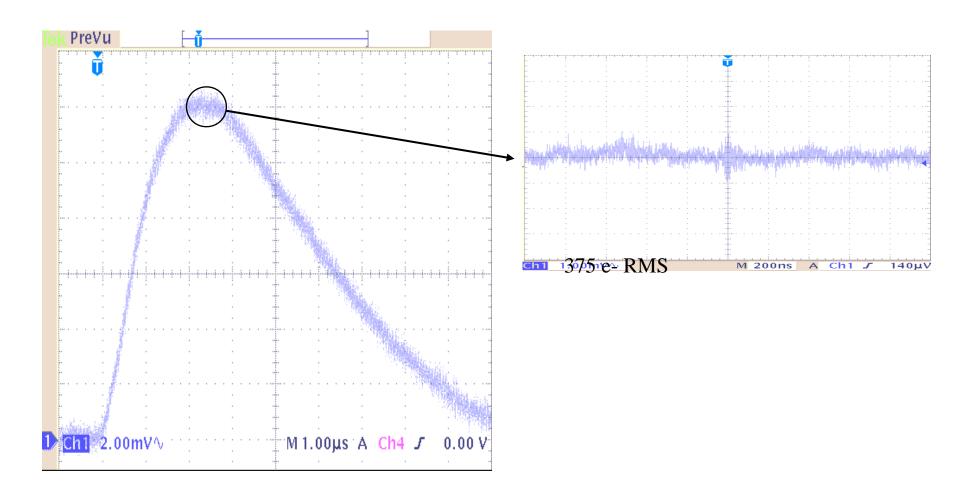

|                  |                 | Measured with 180nm CMOS:<br>375 + 10.5 e-/pF @ 3 µs shaping, <b>210µW power</b><br>S/N = 20 @ 90cm long strips |

- > ADC: 10 bits

- Buffering, digital pre-processing

- > Calibration

- Power switching can save a factor up to 200

#### ILC timing: 1 ms: ~ 3-6000 trains @150-300ns / BC 199ms in between

#### Foreseen Front-end architecture

Charge 1-30 MIP, Time resolution: BC tagging 150-300ns 80ns analog pulse sampling

Technology: Deep Sub-Micron CMOS 130-90nm

# Outline

| • | Detector data         | 2  |

|---|-----------------------|----|

| • | Technologies          | 5  |

| • | Front-End Electronics | 7  |

| • | 130nm chips           | 11 |

| • | 128 channels chip     | 30 |

| • | Conclusion            | 39 |

# History

| ۹ | 2004-2006 | 180nm chip:         | OK with radio-active source                                               |

|---|-----------|---------------------|---------------------------------------------------------------------------|

| ٩ | 2006-2007 | 130nm 4-channel:    | Beam tests this week at CERN                                              |

| ٩ | 2007      | 130nm 1-channel:    | Improved analog pipe-line, calibration                                    |

| • | 2007-2008 | 130nm 128 channels: | True mixed design<br>All analog blocks validated<br>Digital under design. |

| ٩ | 2009      | k-channels chip     |                                                                           |

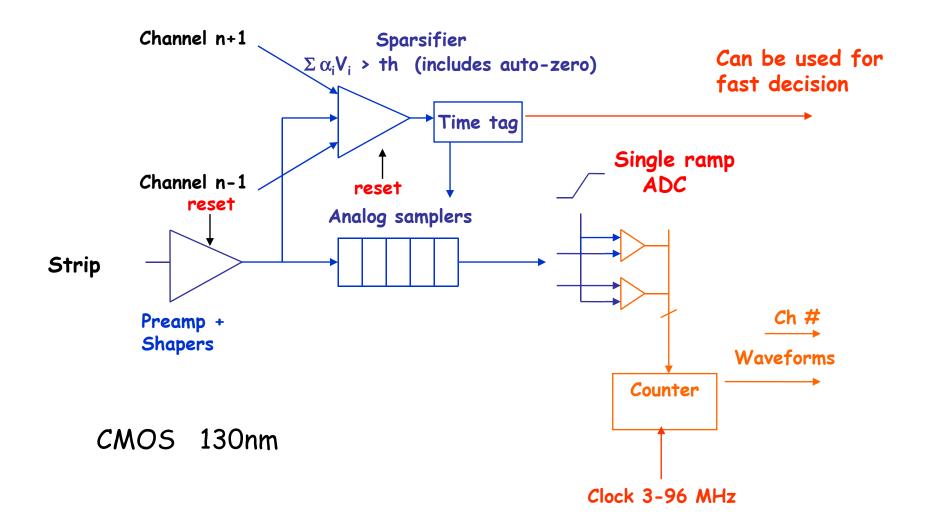

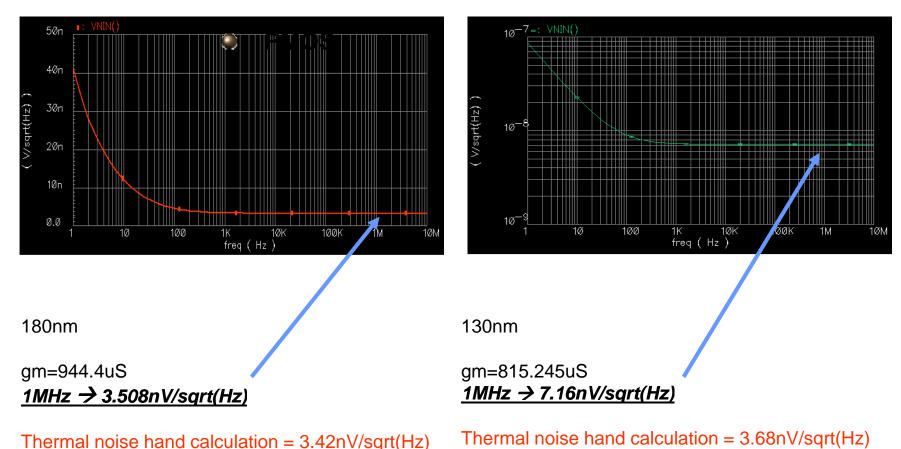

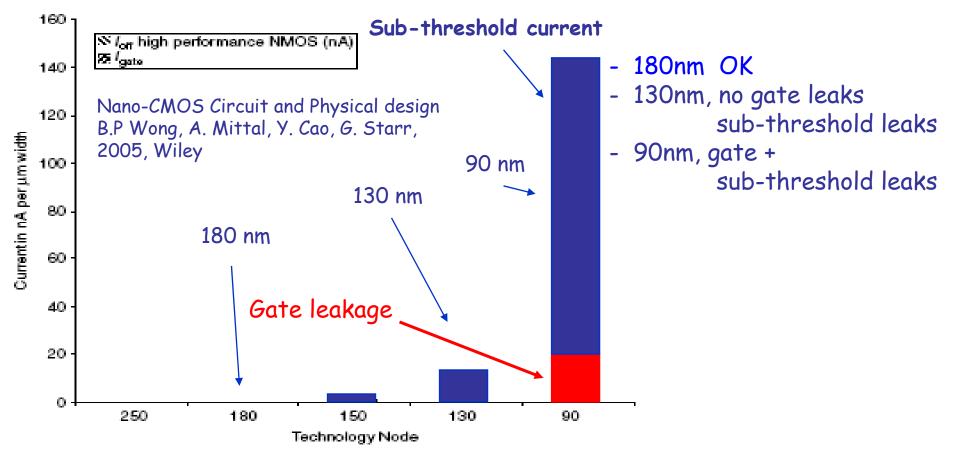

### Front-end in 130nm

130nm CMOS:

- Smaller

- Faster

- Less power

- Will be (is) dominant in industry

- (More radiation tolerant)

Drawbacks:

- Reduced voltage swing (Electric field constant)

- Noise slightly increased (1/f)

- Leaks (gate/subthreshold channel)

- Design rules more constraining

- Models more complex, not always up to date

Millions of channels: Integration of k-scale channels readout chips

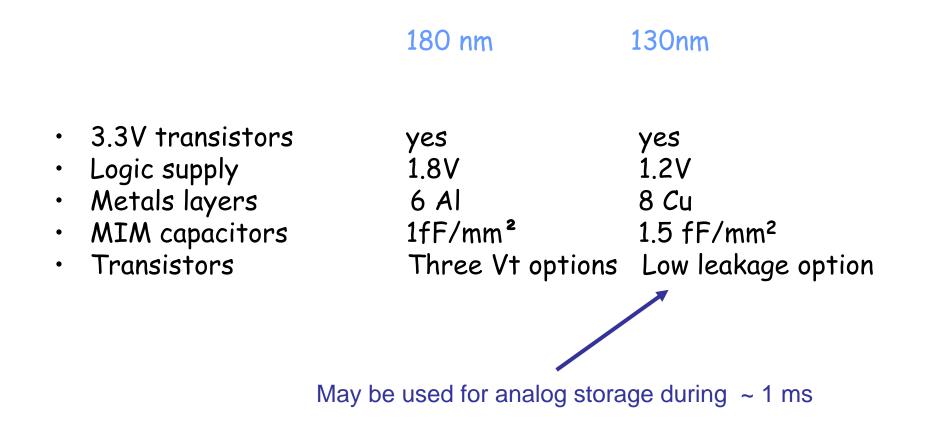

## UMC CMOS Technology parameters

### 2006-7 Chips

#### 130nm CMOS

#### Both under test

Chip -1 4 channels

- Preamp-shapers + Sparsifier

- Pipeline 1

- ADC

- Digital

- Chip -2 One channel

- Preamp-shapers + Sparsifier

- DC servo

- Pipeline 2 (improved)

- DAC

- Test structures: MOSFETS, passive

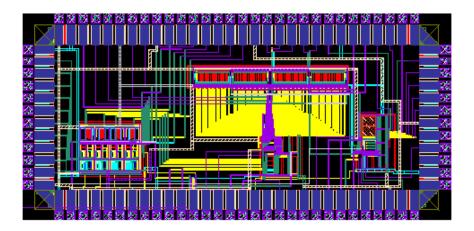

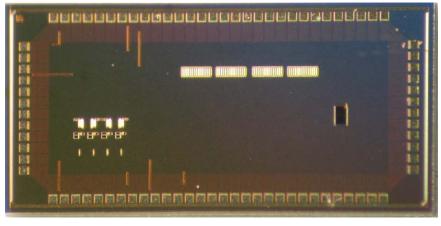

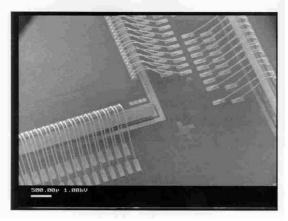

### 4-channel 130nm Silicon

180nm 130nm

Layout of the 130nm chip including sampling and A/D conversion

Picture

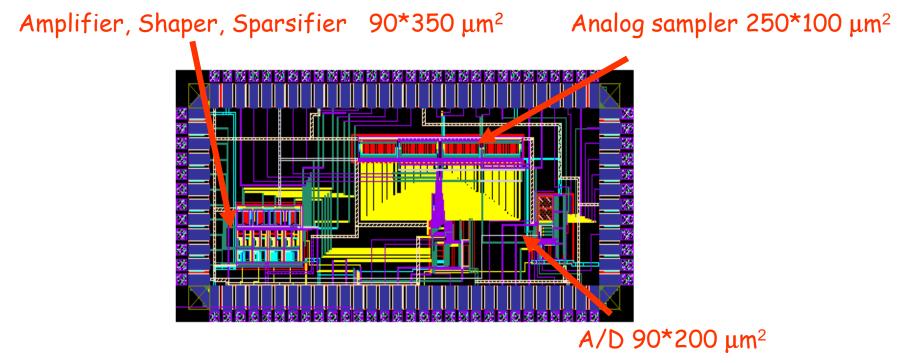

### 4-channel chip layout

Layout of the 130nm chip including sampling and A/D conversion

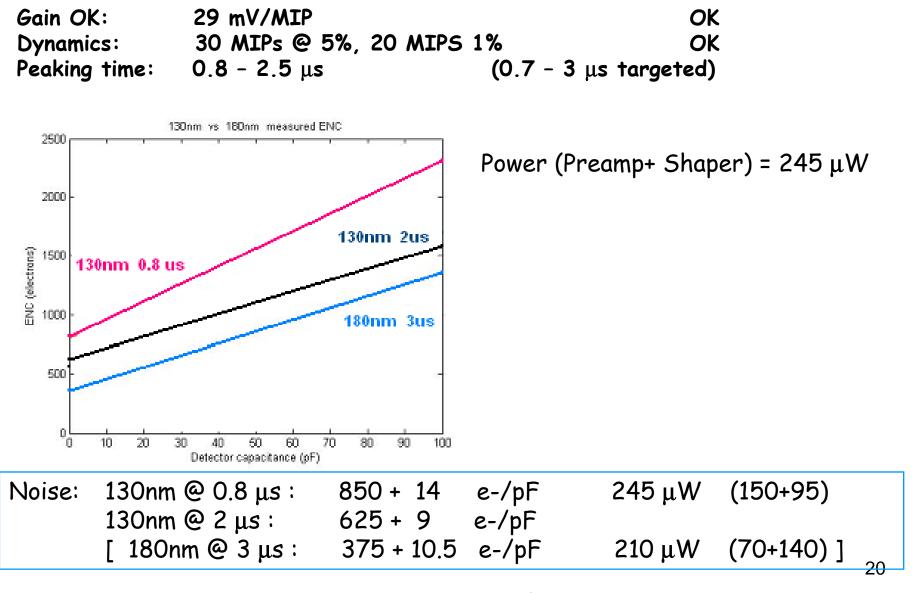

#### Measured gain - linearities **Results** Preampli and Shaper's Linearity 1200 shaper output \* - fited shaper output + Preampli output Preamp output fited preampli output 1000 Mode Acquisition 800 Echantillon J. The Détect. crête (< 250Me/s) Output(mV) Enveloppe 16 600 Moyenne 16 Ch2 20.0mVΩ%M 2.00μs A Ch4 J 112mV 400 **T** 50.00 % Réinit. retard Réglage auto. Mode Fréquence d'échantillonnag 500MEch/s horizont horizonta 200 Mode Acquisition Echantillon Détect. crête (< 250Me/s) 20 25 35 5 10 15 30 40 Input(MIPs) Enveloppe 16 Preamp and Shaper: Moyenne Gain = 29mV/MIP Ch1 20.0mV∿∿ M 2.00µs A Ch4 J 112mV Shaper output **T** 50.00 % Dynamic range = 20MIPs 1% Réinit Résol Réglage auto. Mode Fréquence d'échantillonnage 500MEch/s retard horizont 30 MIPs 5% Peaking time = $0.8-2.5\mu s / 0.5-3\mu s expected$ Jean-François Genat, EUDET Annual Meeting October 8-10<sup>th</sup> 2007 Palaiseau

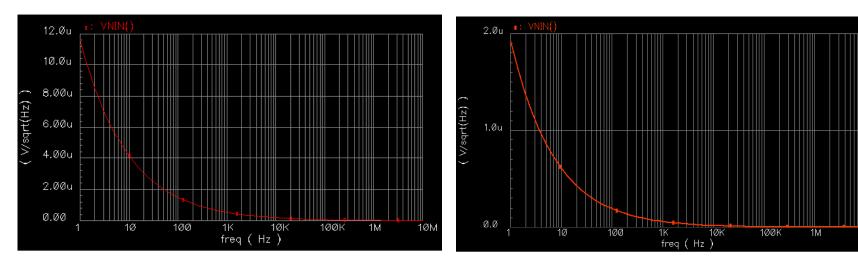

#### 130nm vs 180nm chip noise results

Jean-François Genat, EUDET Annual Meeting October 8-10th 2007 Palaiseau

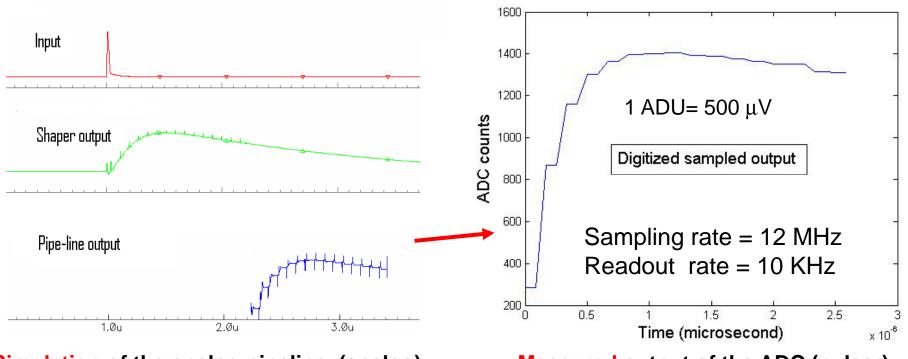

### Digitized analog pipeline output

**Simulation** of the analog pipeline (analog)

**Measured** output of the ADC (pulser)

Waveform distorted due to 1pF parasitic capacitance of the output pad connected for analog diagnostics on 2 out of four channels

Traces cut using IFB to get all shaper channels operational to ADC for beam tests

Chip 2 includes a voltage buffer between shaper and ADC

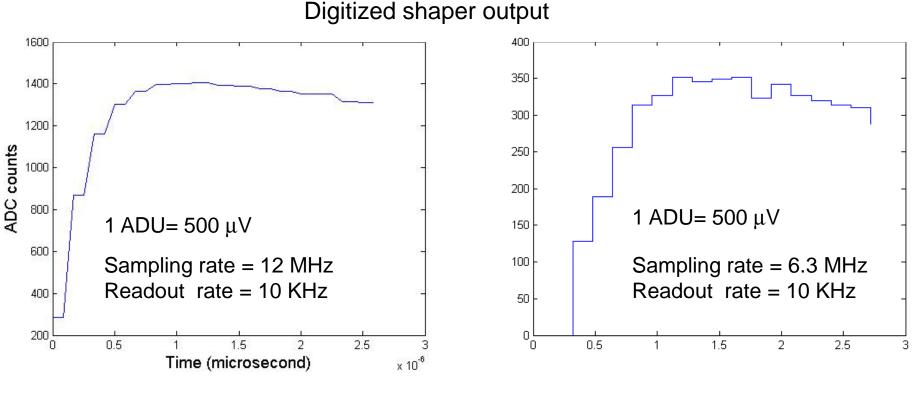

### Digitized analog pipeline output Laser response of detector + 130nm chip

From pulser

From Laser diode + Silicon detector

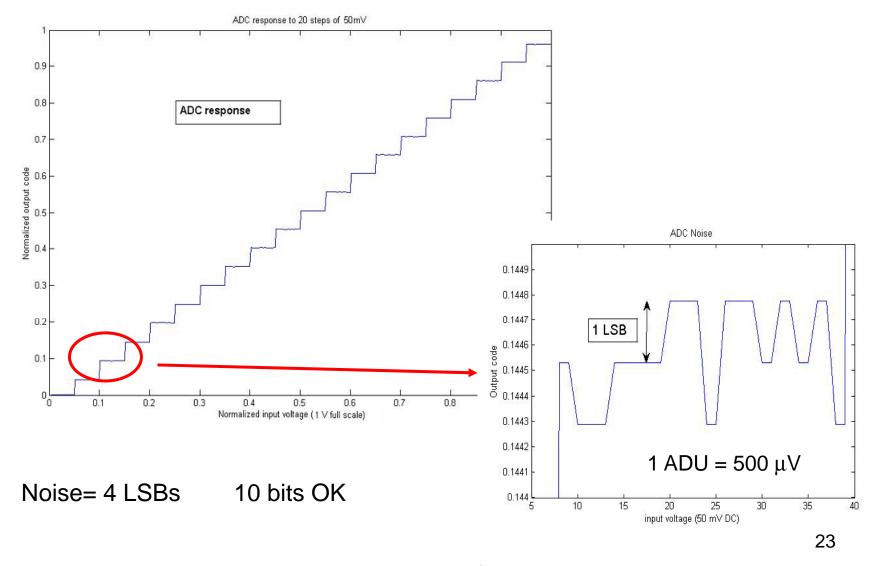

#### **ADC** evaluation

Jean-François Genat, EUDET Annual Meeting October 8-10th 2007 Palaiseau

#### 130-1 chip's tests to come

- Lab tests: Measure ADC extensively

- Linearities Integral, differential

- Noise Fixed pattern, random

- Speed Maximum clock rate

- Accuracy Effective number of bits

- Beam tests at CERN next week

#### 130 nm-2

LAPP Annecy le Vieux R. Hermel, D. Fougeron LPNHE Paris T-H. Pham, R. Sefri

One channel test version in 130nm including:

- Preamp + shaper

- Improved pipeline (output buffer)

- Calibration channel (calibration caps)

- Calibration DAC

Presently under test at LAPP Annecy:

If OK, all analog blocks will be validated for a multi-channel version in 130nm aiming to read a full detector in 2008

130-2 tests under work (LAPP Annecy)

Measure improved pipeline extensively

Denis Fougeron's (LAPPAnnecy) design

| Linearities |                                                            |

|-------------|------------------------------------------------------------|

| Noise       | Integral, differential                                     |

| • NUISE     | Pedestal fixed pattern, random noise<br>Maximum clock rate |

| Droop       |                                                            |

| ADC Driving | Hold data for 1 ms at the ILC                              |

### Some issues with 130nm design

- Noise likely modeled pessimistic, but measured quite acceptable

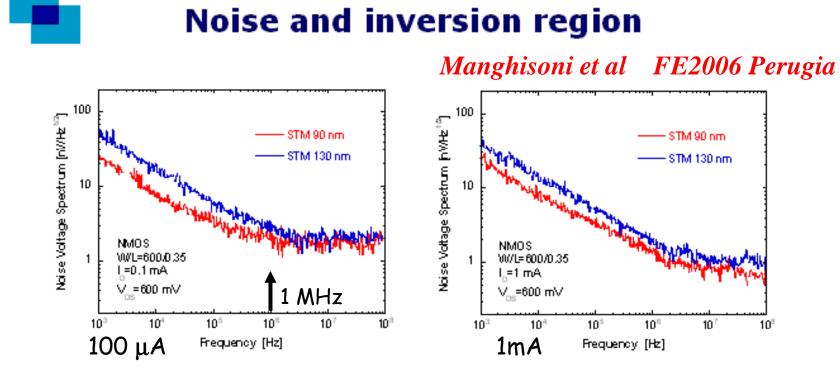

90nm could be less noisy (Manghisoni, Perugia 2006)

- Lower power supplies voltages reducing dynamic range

- Design rules more constraining

- Some (via densities) not available under Cadence Calibre (Mentor) required.

- Low Vt transistors leaky (Low leakage option available at regular Vt)

Manageable, UMC design kits user friendly, Europractice very helpful.

### 130-90nm noise evaluation (STM process)

At low drain current both devices work in the weak inversion region → channel thermal noise is roughly the same for both devices

- At high drain current, a significant difference in the channel thermal noise can be detected ← device from the 90 nm technology works closer to weak inversion region.

- Better 1/f noise performance provided by the STM 90 nm technology

VI International Meeting on Front-End Electronics, Perugia, May 18th 2006

12

# Outline

| • | Detector data         | 2  |

|---|-----------------------|----|

| • | Technologies          | 5  |

| • | Front-End Electronics | 7  |

| • | 130nm chips           | 11 |

| • | 128-channel chip      | 29 |

| • | Conclusion            | 38 |

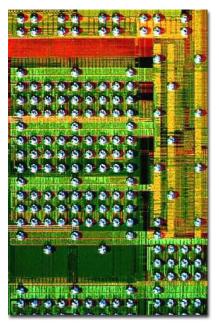

#### Goal: Equip a full detector

- Experience from lab test bench + laser/source and 2007 beam-tests

- Full 128-channels with :

- Preamp-shapers

- Sparsifier

- Pipeline (8-sampling + 8-deep event buffer)

- 12bits ADC

- Digital

- Calibration

- Power cycling

#### Improvments wrt chip 130-1:

- Increase order of the shaper to 3 should reduce noise by 20-30% at a moderate increase in DC power.

- Pipeline (8-sampling + 8-deep event buffer) includes a buffer to drive the ADC.

- Full digital control

- Full calibration and channel disable

- Power cycling

Paris, September 27-28th 2007 A. Comerma (Barcelone), Thanh Hung Pham, JFG Tentative specs for a Silicon strips 128-channel readout chip

I/O

| <u>Preamp</u>     |                   |             |        |     |              |

|-------------------|-------------------|-------------|--------|-----|--------------|

| 128               | Inputs            |             |        | 128 |              |

| 128               | Outputs           |             |        |     |              |

| 1                 | Bias_preamp       | Control DAC | 6 bits |     |              |

| 1                 | V_ref             | "           | "      | 1   |              |

| 1                 | Bias_buf "        | "           | "      | 1   |              |

| <u>Shaper</u>     |                   |             |        |     |              |

| Inputs            | 3                 |             |        |     |              |

| 128               | Outputs           |             |        |     |              |

| 1                 | Bias_shaper       | "           | "      | 1   |              |

| 2                 | V_pole, v_zero    | "           | "      | 1   |              |

| <b>Sparsifier</b> |                   |             |        |     |              |

| 3 x 128           | Inputs            |             |        |     |              |

| 128               | Outputs           |             |        |     |              |

| 1                 | Auto-zero control |             |        |     |              |

| 1                 | Bias_sum_1        | "           | "      | 1   |              |

| 1                 | Bias_sum_2        | "           | "      | 1   |              |

| 1                 | Bias_comp         | "           | "      | 1   |              |

| 1                 | Threshold         | "           | "      | 1   | 4 more pages |

| 128               | Outputs           |             |        |     |              |

#### Chip splits in 14 functional blocks

### Connexion to detector and external

#### Layout allows :

- Wire-bonding

- Stud-bonding

- Bump-bonding

- Even 3D interconnect...

### Planned Digital Front-End

- Chip control

- Buffer memory

- Processing for

- Calibrations

- Amplitude and time least squares estimation, centroids

- Raw data lossless compression

- Tools

- Cadence DSM Place and Route tool

- Digital libraries in 130nm CMOS available

- Synthesis from VHDL/Verilog

- SRAM

- Some IPs: PLLs

#### Need for a mixed-mode simulator

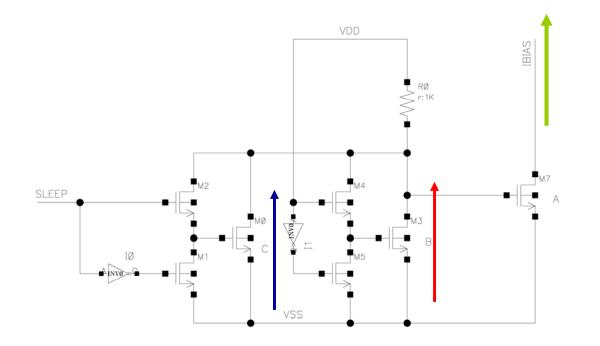

### Power cycling

Switch the current sources between zero and a small fraction ( $10^{-2}$  to  $10^{-3}$ ) of their nominal values

This option switches the current source feeding both the preamplifier & shaper between 2 values:

*Zero* or a *small fraction* (0.1% - 1%) of biasing current is held during « power off ».

#### Zero-power option tested on 180nm chip (slow, but works)

#### Schedule

| Nov '07      | - Complete 130-1 and -2 chips tests                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------|

| December '07 | - Complete analog and digital blocks                                                                                 |

| January '07  | - Merge                                                                                                              |

| February '08 | - Submission, test bench development                                                                                 |

|              | <ul> <li>Card development for TPC+Silicon tests</li> </ul>                                                           |

| May '08      | - Tests: lab                                                                                                         |

| July '08     | <ul> <li>Connexion to HPK detectors</li> <li>Tests with HPK detectors: laser, source</li> <li>Beam tests.</li> </ul> |

September '08 - OK

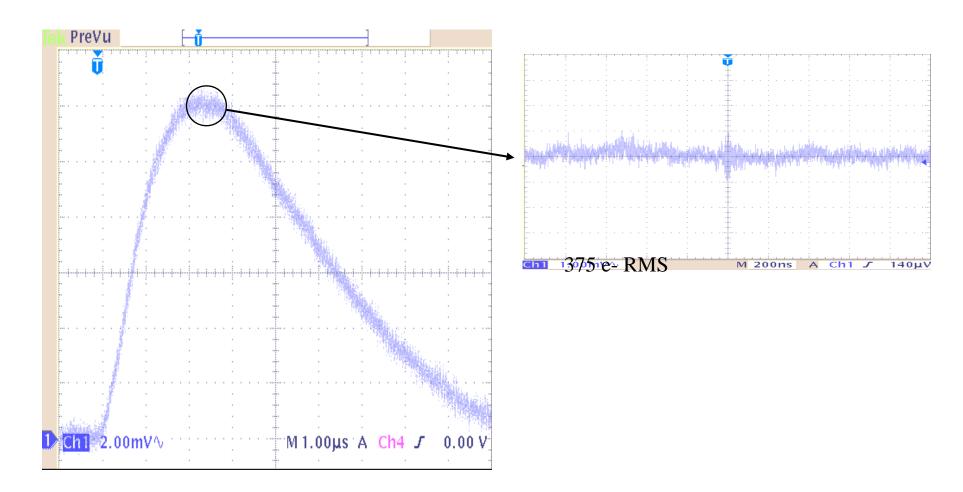

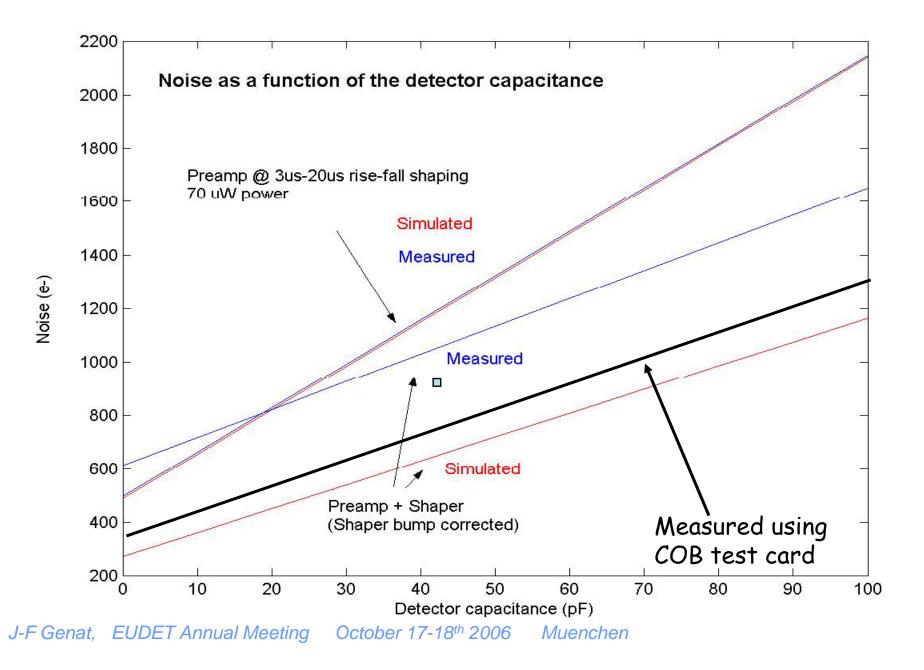

## Shaper output noise

375 e- +10.4 e-/pF input noise with chip-on-board wiring 275 + 8.9/pFsimulated

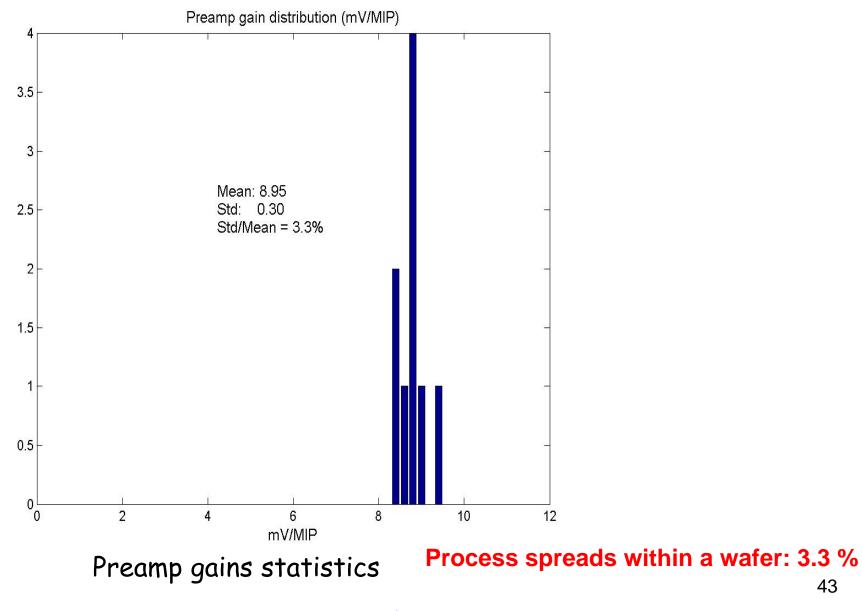

# **Tests Conclusions**

12 chips tested ('05)

The UMC CMOS 180nm process is mature and reliable:

- Models mainly OK

- Only one transistor failure over 12 chips

- Process spreads of a few %

Beam tests in October '06 at DESY

Encouraging results regarding CMOS DSM

\_\_\_\_\_ go to 130nm

#### Conclusion

These CMOS 130 designs and first test results demonstrate the feasibility of a highly integrated front-end for Silicon strips (or large pixels) with

- DC power under  $500\mu$ W/ch

- Silicon area under 50 x 1000  $\mu^2$ /ch

The End ...41

Jean-François Genat, EUDET Annual Meeting October 8-10<sup>th</sup> 2007 Palaiseau

# Backup

### **Process spreads**

J-F Genat, EUDET Annual Meeting October 17-18<sup>th</sup> 2006 Muenchen

## Shaper output noise

375 e- +10.4 e-/pF input noise with chip-on-board wiring 275 + 8.9/pFsimulated

# **Tests Conclusions**

12 chips tested ('05)

The UMC CMOS 180nm process is mature and reliable:

- Models mainly OK

- Only one transistor failure over 12 chips

- Process spreads of a few %

Beam tests in October '06 at DESY

Encouraging results regarding CMOS DSM

\_\_\_\_\_ go to 130nm

# Possible issues: noise: 130nm vs 180nm (simulation)

#### **PMOS**

Thermal noise measured by Wladimir Gromov (NIKHEF) with IBM130nm OK 46

J-F Genat, EUDET Annual Meeting October 17-18th 2006 Muenchen

# **Transistors** leaks

- Gate-channel due to tunnel effect

- Through channel when transistor switched-off

J-F Genat, EUDET Annual Meeting October 17-18<sup>th</sup> 2006 Muenchen

Courtesy: Marty Breidenbach (Cal SiD)

#### **OR (later)**

# Noise summary (180nm)

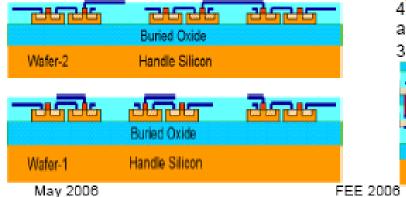

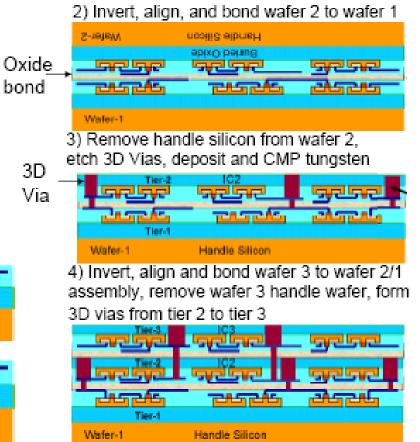

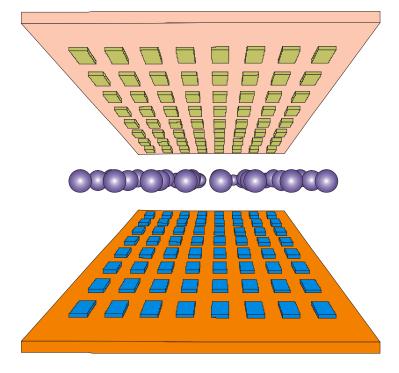

# 3D Wiring Process flow for 3D Chip

- 3 tier chip (tier 1 may be CMOS)

- 0.18 um (all layers)

- SOI simplifies via formation

- Single vendor processing

1) Fabricate individual tiers

#### Courtesy: Ray Yarema, FEE 2006, Perugia

J-F Genat, EUDET Annual Meeting October 17-18th 2006 Muenchen

36

#### Manuel Lozano (CNM Barcelona) Chip connection

- Wire bonding

- Only periphery of chip available for IO connections

- Mechanical bonding of one pin at a time (sequential)

- Cooling from back of chip

- High inductance (~1nH)

- Mechanical breakage risk (i.e. CMS, CDF)

- Flip-chip

- Whole chip area available for IO connections

- Automatic alignment

- One step process (parallel)

- Cooling via balls (front) and back if required

- Thermal matching between chip and substrate required

- Low inductance (~0.1nH)

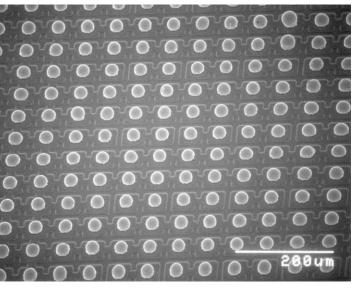

#### *Manuel Lozano (CNM Barcelona)* Bump bonding flip chip technology

- Electrical connection of chip to substrate or chip to chip face to face flip chip

- Use of small metal bumps

bump bonding

CNM

Process steps:

- Pad metal conditioning:

Under Bump Metallisation (UBM)

- Bump growing in one or two of the elements

- Flip chip and alignment

- Reflow

- Optionally underfilling

J-F Genat, EUDET Annual Meeting O

October 17-18<sup>th</sup> 2006

52

#### *Manuel Lozano (CNM Barcelona)* Bump bonding flip chip technology

- Expensive technology

- Especially for small quantities (as in HEP)

- Big overhead of NRE costs

- Minimal pitch reported: 18  $\mu$ m but ...

- Few commercial companies for fine pitch applications (< 75  $\mu$ m)

- Bumping technologies

- Evaporation through metallic mask

- Evaporation with thick photoresist

- Screen printing

- Stud bumping (SBB)

- Electroplating

- Electroless plating

- Conductive Polymer Bumps

- Indium evaporation

# Noise: 130nm vs 180nm (simulation)

#### NMOS :

130nm W/L = 50u/0.5u Ids=48.0505u,Vgs=260mV,Vds=1.2V gm=772.031uS,gms=245.341uS,gds=6.3575uS **1MHz --> 24.65nV/sqrt(Hz)**

100MHz --> 5nV/sqrt(Hz) Thermal noise hand calculation = 3.78nV/sqrt(Hz) 180nm W/L=50u/0.5u Ids=47uA,Vgs=300mV,Vds=1.2V gm=842.8uS,gms=141.2uS,gds=16.05uS **1MHz --> 4nV/sqrt(Hz)**

10MHz --> 3.49nV/sqrt(Hz) Thermal noise hand calculation = 3.62nV/sqrt(Hz) 54