### EUDRB: the data reduction board of the EUDET pixel telescope

Lorenzo Chiarelli, Angelo Cotta Ramusino, Livio Piemontese, Davide Spazian Università & INFN Ferrara

Presented by Concezio Bozzi

## Context

- The EUDET JRA1 project: a pixel-based beam telescope to test pixel sensors suitable for the ILC

- In 2007: build and operate a "demostrator" telescope

- Beam test campaign at DESY (June, August) and CERN (September)

- MAPS sensor for demonstrator: MimoTEL, 256x256, 30μm x 30μm pitch

- For the final telescope (2008), aim at a **sensor** which has sparsification ON THE CHIP to reduce, with the bulk of data, also its readout time.

- To test such sensors, we have designed a DAQ electronics which

- can support all VMEBus transfer modes up to the 2e-sst

- ...AND can implement real-time sparsification on the readout board...

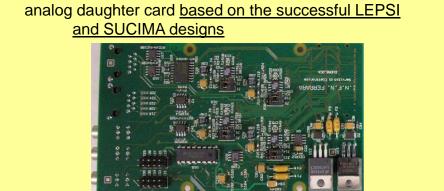

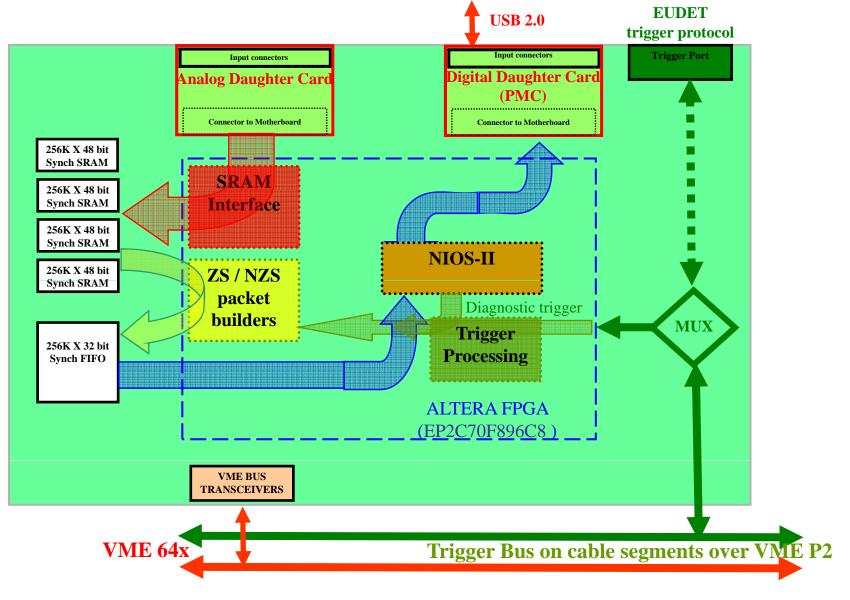

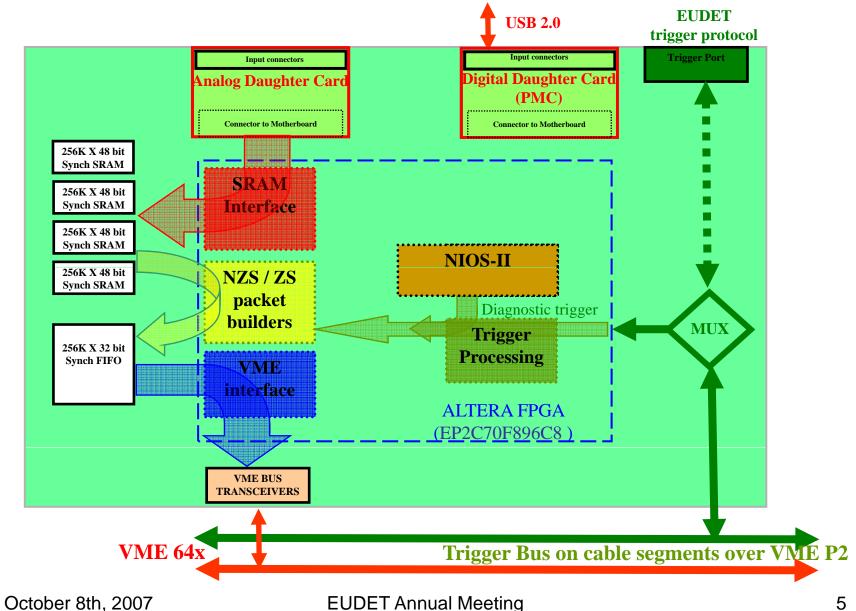

#### A VME64x/USB2.0-based DAQ card for MAPS sensors

mother board built around an ALTERA Cyclonell FPGA (clock rate: 80MHz) and hosting the core resources and Interfaces (VME64X slave, USB2.0, EUDET trigger bus)

#### NIOS II, 32 bit "soft" microcontroller (clock rate: 40MHz) implemented in the FPGA for

- on board diagnostics

- on-line calculation of pixel pedestal and noise

- remote configuration of the FPGA via RS-232, VME, USB2.0

#### Two readout modes:

Zero Suppressed readout to minimize the readout dead-time while in normal data taking.

Non Zero Suppressed readout of multiple frames for debugging or off-line pedestal and noise calculations

#### digital daughter card drives/receives control signals for the detectors and features a USB 2.0 link

#### Data Flow for benchtop DAQ (slow) via USB2.0

#### Data Flow for data taking via VMEBus

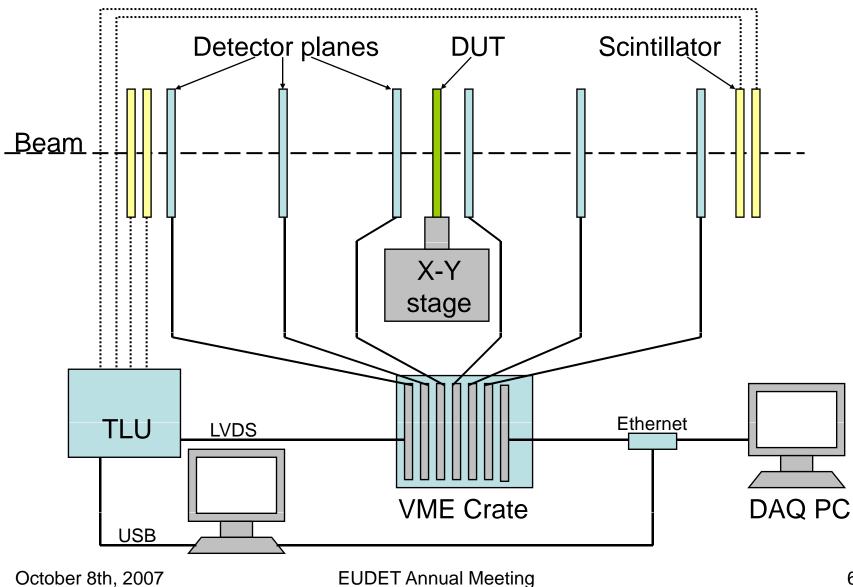

#### Beam test overview

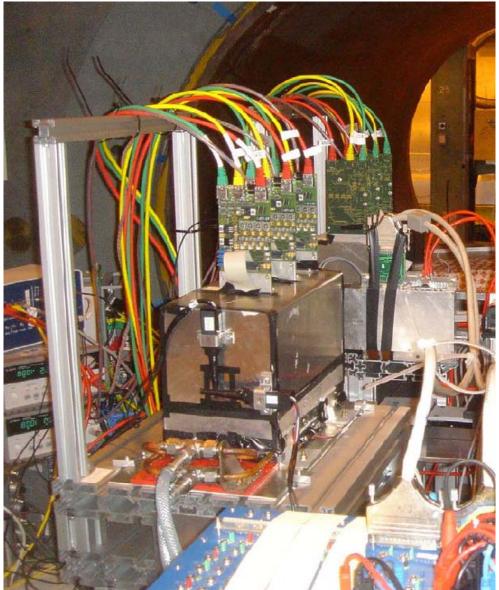

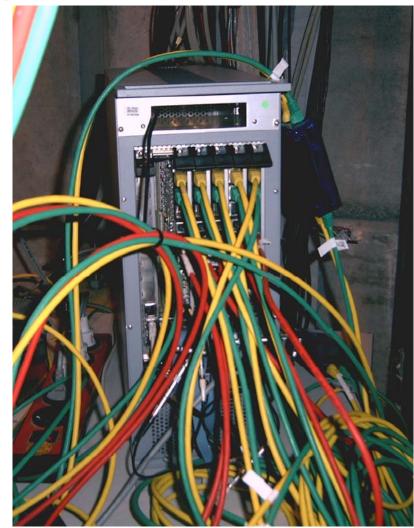

### Beam test (CERN)

VME crate with 5 EUDRBs

**EUDET** Annual Meeting

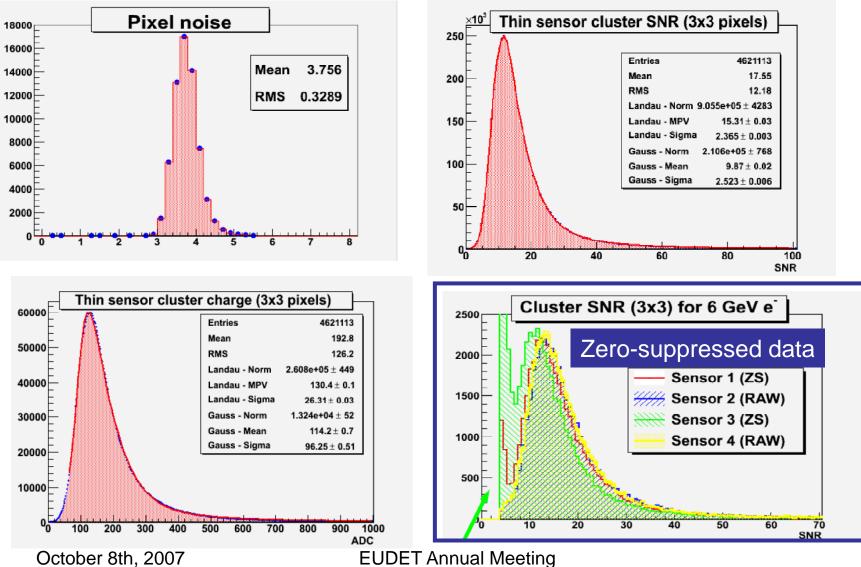

## Preliminary results (P. Roloff, A. Bulgheroni)

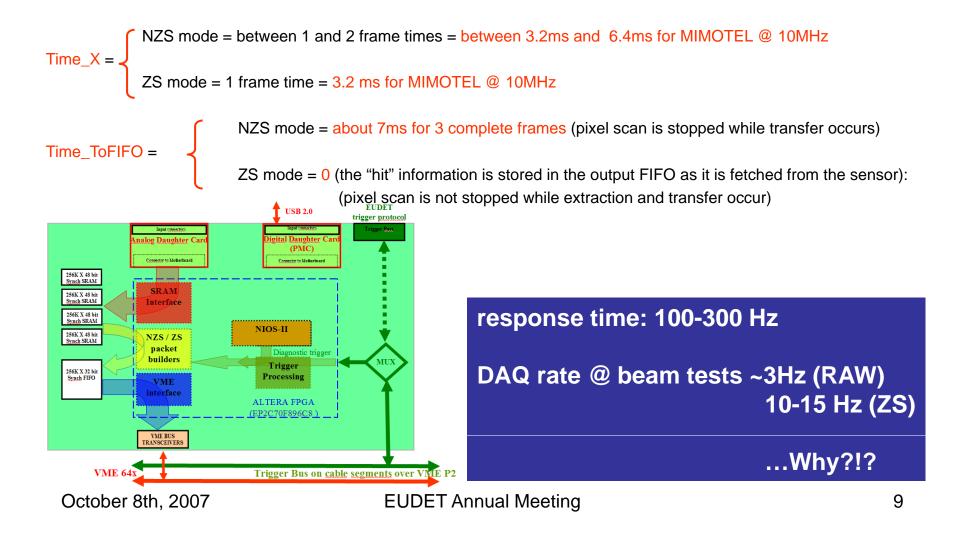

#### Trigger response times

Trigger response time = Time from trigger to event data packet ready in the output FIFO = Time\_TtoDRdy

Time\_TtoDRdy = time to extract data from sensor (Time\_X) + time to transfer event data into output FIFO (Time\_ToFIFO)

#### Single MBLT transfers (8B/block)

| 📆 TLA - [Waveform 1]                        |                                           |             |

|---------------------------------------------|-------------------------------------------|-------------|

| 🚟 File Edit View Data System Window Help    |                                           | _ 8 ×       |

| 🗃 🖬 📰 🛐 💦 💡 Status Idle                     | Run A                                     | Tek         |

| <u></u>                                     |                                           |             |

| C1: 180ns 📫 C2: 367ns 📫 Delta Time, 187ns 🐳 | 🗖 Lock Delta Time                         |             |

| AM(0-5) C1: 08 C2: 08 Delta:                | a: 00                                     |             |

| T                                           | 2                                         |             |

| Sample -216.000 ns                          | 684                                       | 4.000 ns    |

| AM(0-5) 3F                                  |                                           | <u> </u>    |

| ADDRESS(31-0)                               |                                           |             |

| nBERR(0)                                    |                                           |             |

| nLONGWORD(0)                                |                                           | <u></u>     |

| nDTACK(0)                                   |                                           |             |

| nIACK(0)                                    |                                           |             |

| nDS0(0)                                     |                                           |             |

| nDS1(0)                                     |                                           |             |

| nWRITE(0)                                   |                                           |             |

| nAS(0)                                      |                                           | <u> </u>    |

| d(150) FFFF 💥 5116                          | 5 X FFFF X 0000 X FFFF X 0000 X FFFF X 00 | 001         |

| C2(1)                                       |                                           |             |

| C2(0)                                       | <u></u>                                   |             |

|                                             | <u> </u>                                  |             |

|                                             |                                           | -           |

|                                             |                                           | <u>_</u>    |

|                                             |                                           |             |

|                                             | Te                                        | ktronix //. |

Detail of the MBLT block read.

The cycle time between two successive transfers is 187ns (-> 42 MB/s peak transfer rate, compared to the maximum theoretical rate of 80MB/s claimed by the standard). This time is made up of

•(a) Delay from nDS0, nDS1 active to nDTACK active: about 60ns. It is determined by the EUDRB.

(b) Delay from nDTACK active to nDS0, nDS1 unactive : about 50ns. It is determined by the VME CPU

•(c) Delay from nDS0, nDS1 unactive to nDTACK unactive : about 30ns. It is determined by the EUDRB.

·(d) Delay from nDTACK unactive to nDS0, nDS1 active : about 50ns. It is determined by the VME CPU

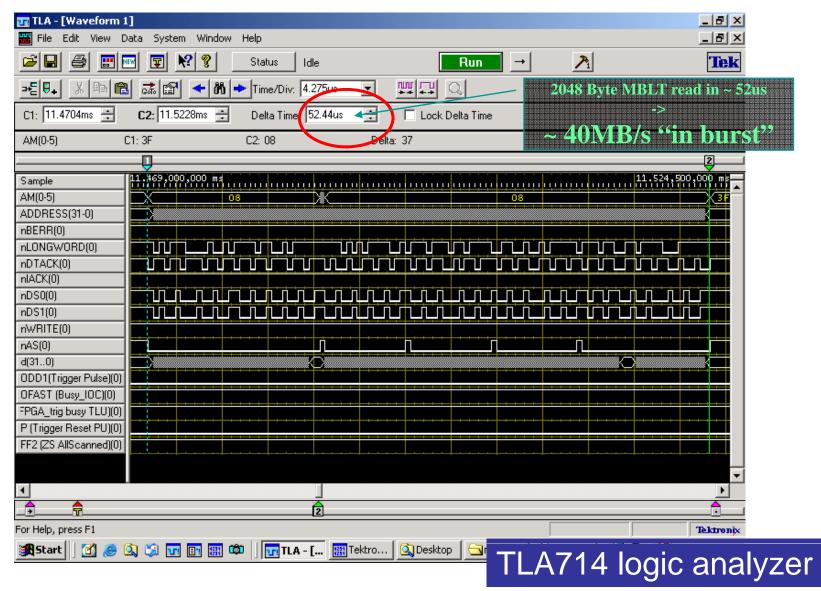

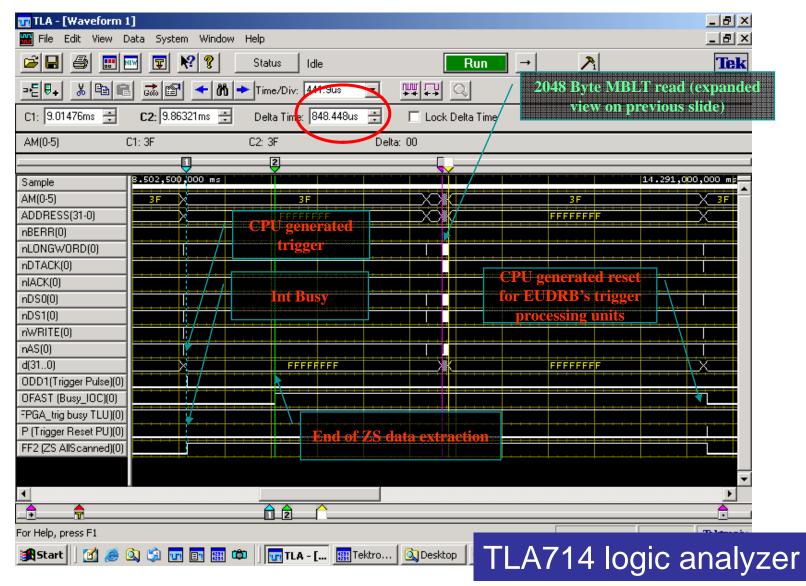

#### Reading a 2048 Byte MBLT

### Including the VME CPU...

## Next steps

- On the VME side:

- Understand the ~2ms dead time between single transfers (check of "DataReady Flag, Clear of EUDRBs after readout, pedestal/threshold setting etc..) on the VMEBus. This is due to the VME CPU.

- Implement slave-termination of MBLT transfers data through the VMEBus. Presently we must use zero-padding termination because of a bug in the software driver for the PCI-VME bridge chip (Tsi 148) residing on the VME CPU board.

- On the EUDRB side:

- implement 2e-VME transfers (up to 320MB/s nominal transfer speed)

- start thinking configuration for the final sensors

- Items with lower priority (real bottlenecks are above):

- write several ZS events on the FIFO and extract data only when the FIFO is full (multi-event mode)

- implement MBLT in write mode (for pedestal and thresholds)

- write ZS and NZS data for the same event. Is this still needed?

- Status of new production (8 boards)

- Boards are in Ferrara, tests starting

- Will send them back to Artel afterwards

- Artel will ship to Geneva

# Conclusion

- EUDRB successfully used in beam tests at DESY (June, August) and CERN (September)

- Hunting for better performance:

- VME CPU is the real bottleneck at the moment

- Some improvements on the EUDRB side also possible