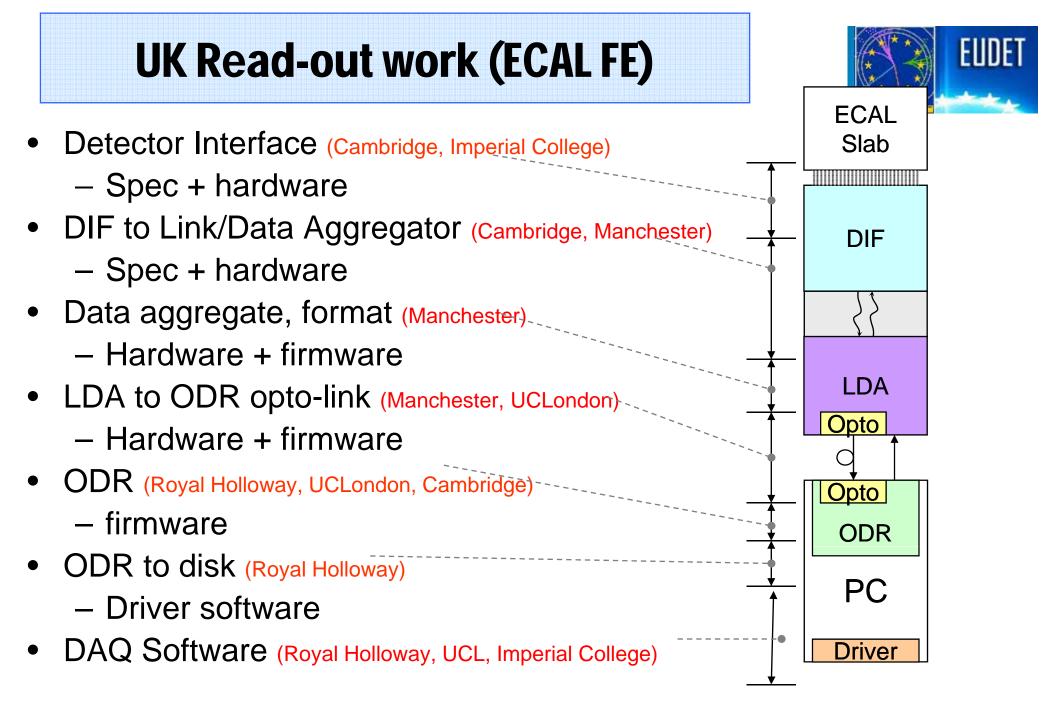

# **JRA3: DAQ Overview**

### Objectives System Overview Status of DAQ Components Outlook

Imperial College London

## **DAQ objectives**

- Perform DAQ tasks for a ILC Calorimeter Detector using a scalable system built from commercial off-the-shelf components

- Build a small-scale version of the DAQ to read out the EUDET calorimeter module

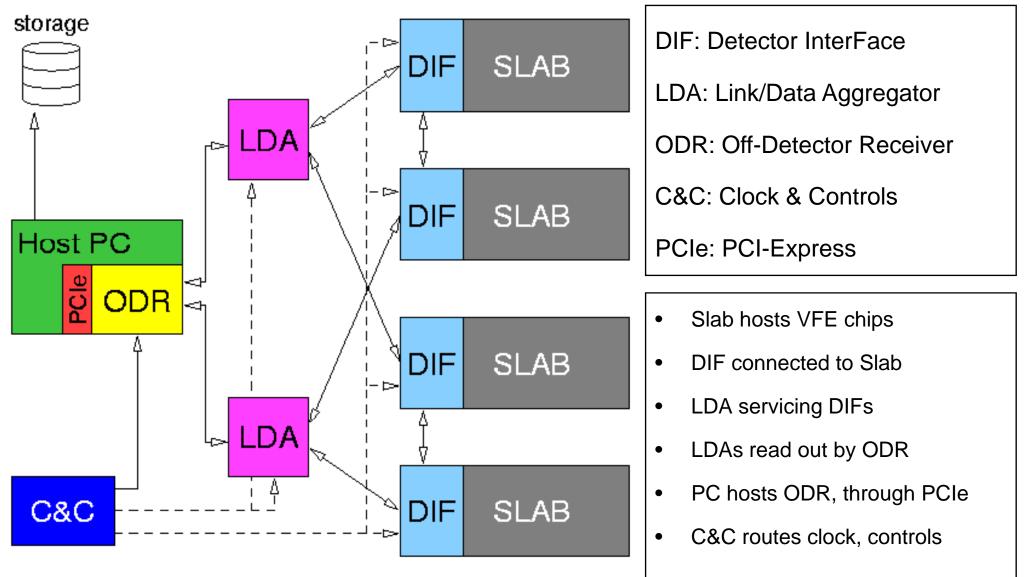

## **DAQ architecture**

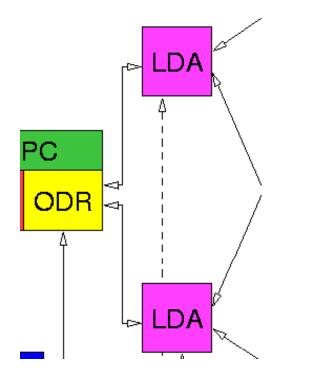

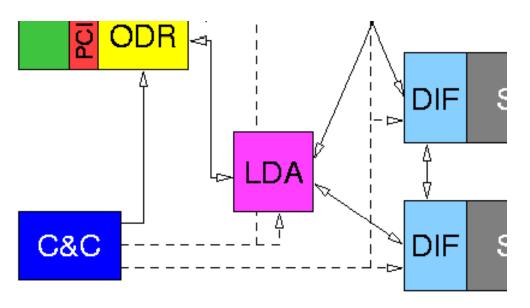

### ODR is the interface between DAQ and the 'PC-world'

storage

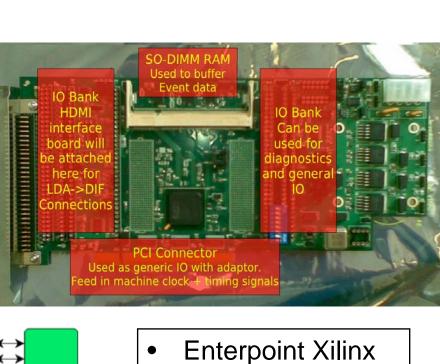

- ODR is a commercial FPGA board with high speed serial interfaces and a PCIe host bus (Virtex4-FX100, PCIe 8x, etc.)

- Customised firm- and software: DMA driver pulls data off the onboard RAM, writes to disk

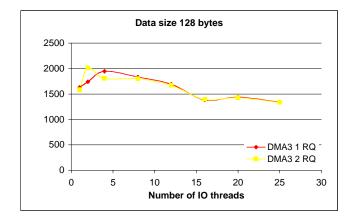

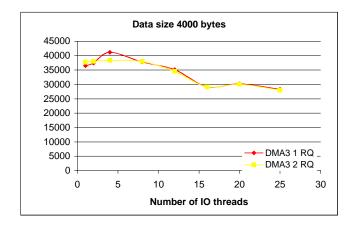

## **ODR Data Rate Studies**

- Data rate studies lead to identification of bottlenecks

- Re-iterate on firmware, software

- Firmware update to full-width (and speed) data path

- Plans: firmware development and integration of

- High-Bandwidth DDR2 RAM controller

- Hi-Speed data links (Gbit Eth/TLK2501)

EUDET

## Link/Data Aggregator

### LDA interfaces many DIFs with few high-speed links

- Handles dataflow from DIFs

- Manages commands to & from both DIFs and ODRs

- Robustness through simplicity:

- Unaware of exact data content

- Abuse-resistant through design

# LDA prototype

Event storage

DDR2 Memory Controller

Clock and Control Signal Interface

Prototype is a commercial FPGA board with customised firmware and hardware add-ons:

High-bandwidth link to ODR

LDA

Machine

Decoder/State

TX/RX Buffers

and Logic to

do prompt

Decoding

Many links towards DIFs

LDA<->ODR

USB 2.0 Physical Interface

Physical Interface

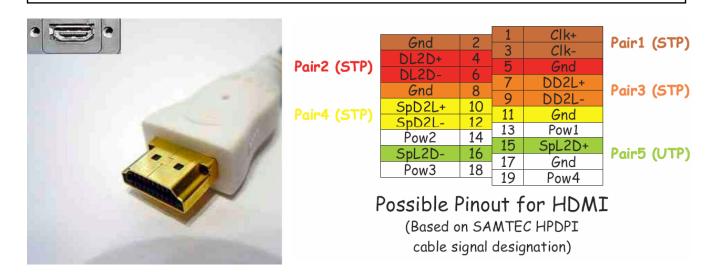

HDMI

board

inks

Interface

10 HDMI

Multiple copies of these

DIF

l per

SERDES(s

HDMI link

State Machine

EUDET

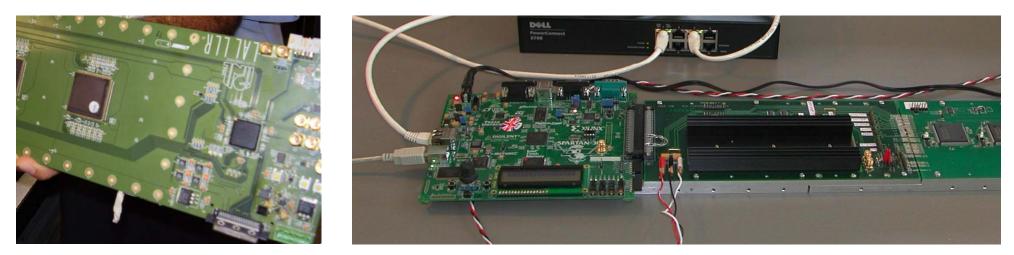

### Spartan3 based dev. board

(including PCI)

## **Clock & Controls Distribution**

- C&C unit provides machine clock and fast commands through ODR and LDA towards DIF

- Possibly partial integration with ODR

- Fast Controls: encoded commands on the LDA-DIF link

- Slow Controls/Configuration: block transfers on LDA-DIF link

- Low-latency fast signals: distributed 'directly'

### **Detector InterFace**

EUDET

- Sits at the end of detector slab PCB

- Directly connected to the Front-End chips

- Integral part of the detector

Various prototypes developed for specific tasks

## **LDA-DIF communication**

Clock: provide machine clk + synchronisation

Data: large block transfers from DIF to LDA

Fast control commands: immediate action

Block transfers for confguration of VFE chips

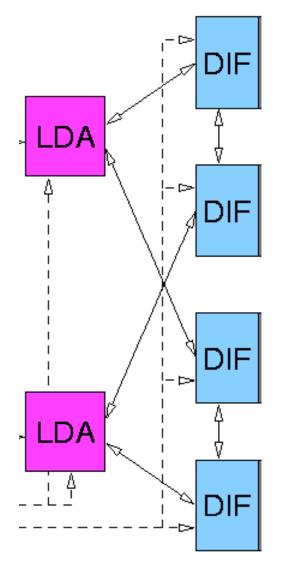

## **LDA-DIF link**

LDA-DIF link:

- Serial link running at multiple of machine clock

- 50Mbps (raw) bandwidth minimum

- robust encoding (8B/10B or alike)

- anticipating about 10 DIFs on an LDA

- LDAs serve even/odd DIFs for redundancy

10-10-2007 EUDET Annual Meeting, Ecole Polytechnique, Paris

## **DIF** implementation

- The Slab is an integral part of the detector

- The LDA and ODR are transparent wrt detector type

- The DIF and its interface to the slab is detector-specific

- Large parts of the DIF firmware must be generalised

- *DIF hardware should support firmware* to profit from common developments

- DIF working group: AHCAL, ECAL, DHCAL + DAQ

- DIF wg to address common problems and share knowledge, experience, and VHDL code

## **DAQ Software**

- Aim for modular, upgradeable software components

- Compilation of list of EUDET DAQ requirements

- Investigation of existing frameworks used, both in HEP and industry:

- EPICS

- ACE

- DOOCS

- So many nice features to choose from.... not easy!

## **JRA3: DAQ Outlook**

- Hardware and firmware development ongoing in many areas, software is being investigated

- DIF working group formed to address common issues, centralize VFE-DAQ discussion and avoid triplication of work

- Development ongoing for all components in a full system chain: Software, ODR, LDA, DIF, Slab