# Deep submicron readout chip development

#### Jean-François Genat Thanh Hung Pham

on behalf of

D. Fougeron, <sup>1</sup>R. Hermel <sup>1</sup>, H. Lebbolo <sup>2</sup>, R. Sefri, <sup>2</sup>

<sup>1</sup>LAPP Annecy, <sup>2</sup>LPNHE Paris

SiD phone meeting August 3d 2007

# Outline

- Goals in CMOS 130nm

- Present results

- Chip 2 and further tests

- Next chip

### Status and Goals

|                                                      |               | This chip  |  |  |

|------------------------------------------------------|---------------|------------|--|--|

| Full readout chain integration in                    | a single chip | yes        |  |  |

|                                                      |               |            |  |  |

| - Preamp-shaper                                      | yes           |            |  |  |

| <ul> <li>Zero-suppression decision (three</li> </ul> | yes           |            |  |  |

| - Pulse sampling: Analog pipe-line                   | yes           |            |  |  |

| <ul> <li>On-chip digitization: ADC</li> </ul>        | yes           |            |  |  |

| <ul> <li>Buffering and pre-processing:</li> </ul>    | no            |            |  |  |

| Centroids, least squares fits                        |               |            |  |  |

| <ul> <li>Lossless compression and error</li> </ul>   | no            |            |  |  |

| <ul> <li>Calibration and calibration mana</li> </ul> | no            |            |  |  |

| - Power switching (ILC timing)                       | no            |            |  |  |

| • CMOS 130nm                                         | 2006-7        | yes        |  |  |

|                                                      | 2008          | /          |  |  |

|                                                      | 2000          | -          |  |  |

| <ul> <li>512-1024 channels planned</li> </ul>        |               | 4 channels |  |  |

### Targeted

| Amplifier:  | 30 mV/MIP gain          |

|-------------|-------------------------|

| Shaper:     | 700ns-3 µs              |

| Sparsifier: | threshold on analog sum |

| Sampler:    | 16-deep                 |

| ADC:        | 10-bit                  |

|             |                         |

Noise:

۲

۲

۲

۲

۲

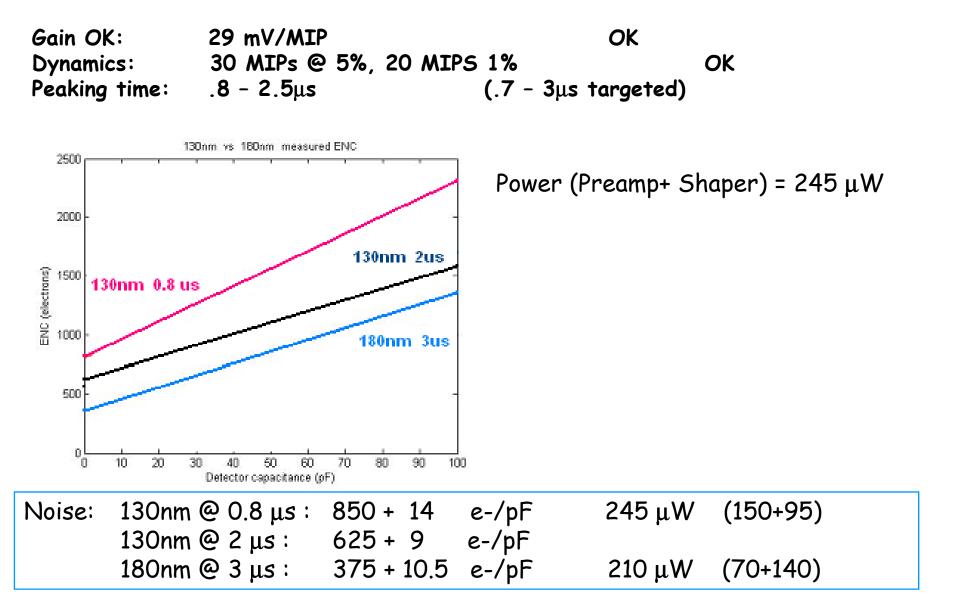

Measured with 180nm CMOS: 375 + 10.5 e/pF @ 3 µs shaping, 210µW power

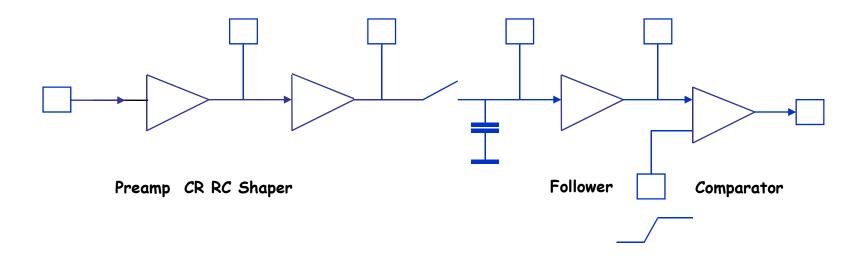

### Front-end in 130nm

130nm CMOS:

- Smaller

- Faster

- Lower power

- Will be (is) dominant in industry

- (More radiation tolerant)

Drawbacks:

- Reduced voltage swing (Electric field constant)

- Leaks (gate/subthreshold channel)

- Design rules more constraining

- Models more complex, not always up to date

- Crosstalk (digital-analog)

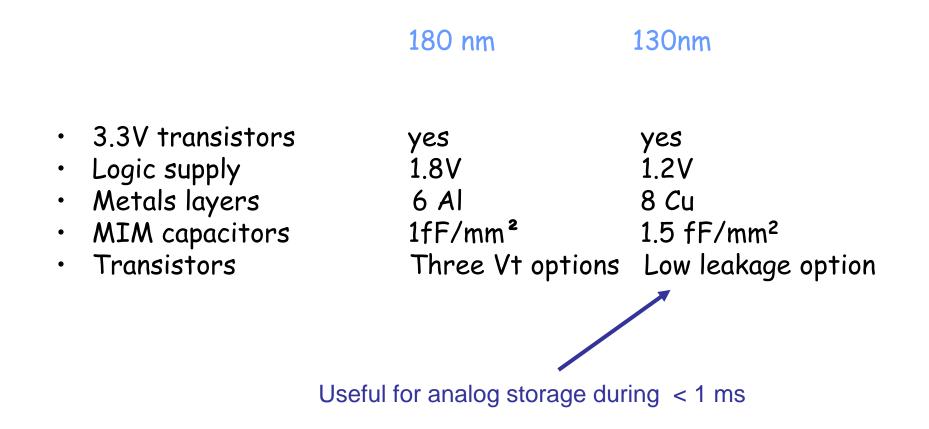

### UMC Technology parameters

# 2006-7 Chips Summary

130nm

| Under test          | Chip        | #1                                   | (4 channels)                      |  |

|---------------------|-------------|--------------------------------------|-----------------------------------|--|

|                     | -<br>-<br>- | Preamp<br>Pipeline<br>ADC<br>Digital | e-shapers + Sparsifier<br>e 1     |  |

| (Almost) Under test | _           | #2                                   | (One channel)                     |  |

|                     | -<br>-<br>- | DC serv<br>Pipeline<br>DAC           | 2                                 |  |

|                     | -           | Test st                              | Test structures: MOSFETS, passive |  |

J-F Genat, SiD Phone meeting, August 3d 2007

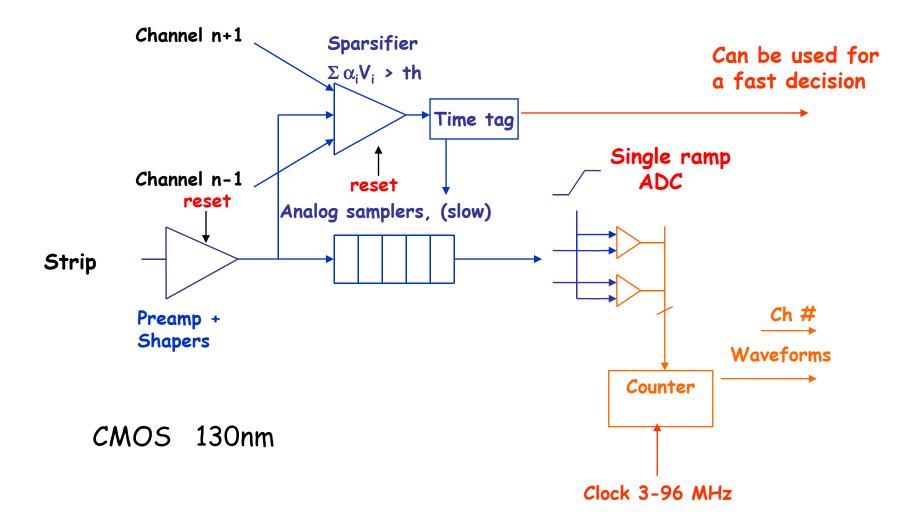

### 4-channel chip

# Outline

- Goals in CMOS 130nm

- Present results

- Chip 2 and further tests

- Next chip

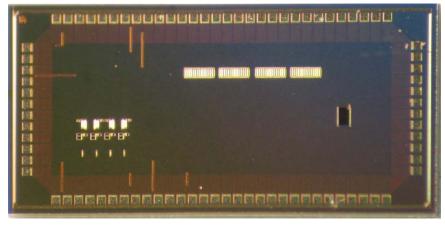

# Silicon

180nm 130nm

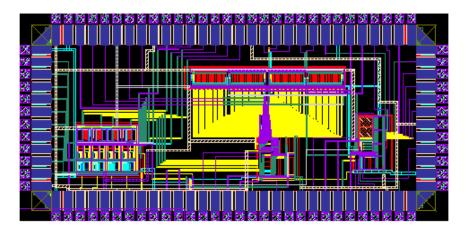

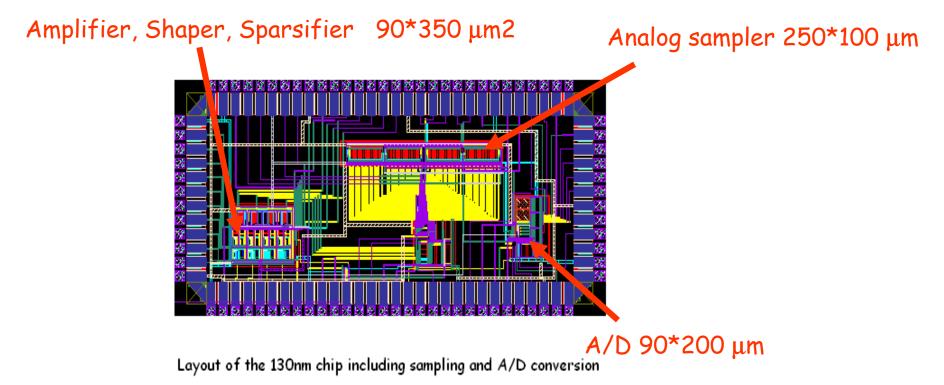

Layout of the 130nm chip including sampling and A/D conversion

Picture

### 130nm chip

#### LAYOUT :

Thanh Hung Pham, SiD Phone meeting, August 3d 2007

# Outline

- Goals in CMOS 130nm

- Present results

- Chip 2 and further tests

- Next chip

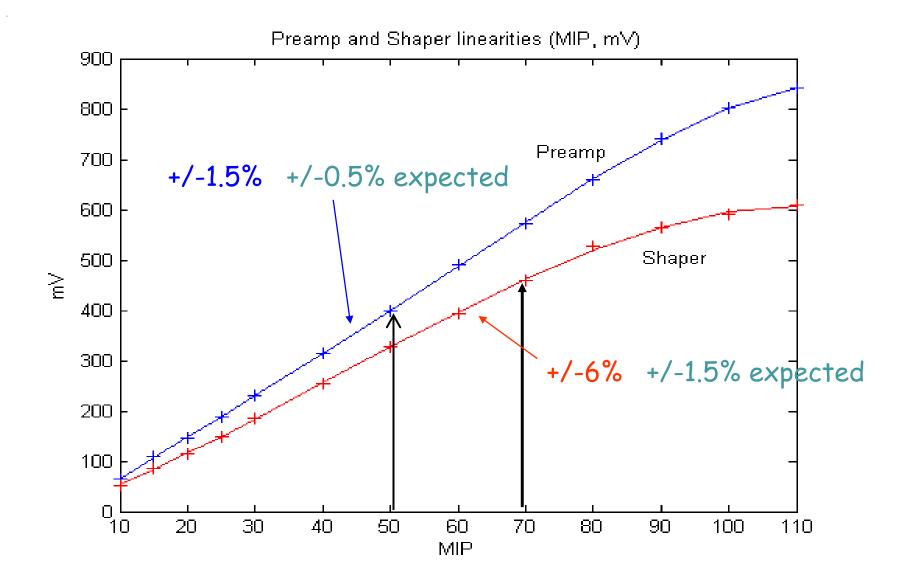

### Linearities 180nm chip

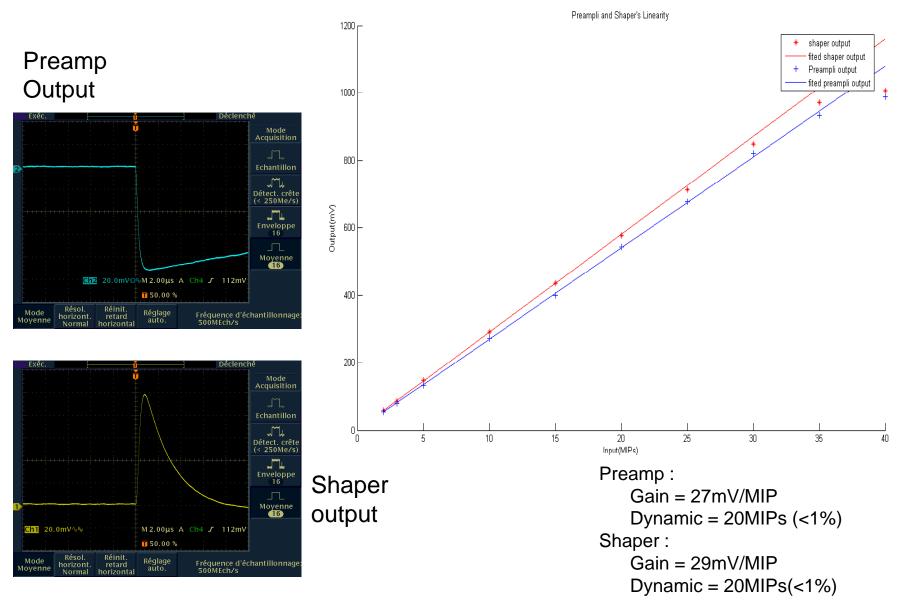

### Chip 130nm MEASUREMENT : GAIN - LINEARITY

Thanh Hung Pham, SiD Phone meeting, August 3d 2007

### 130nm chip noise results

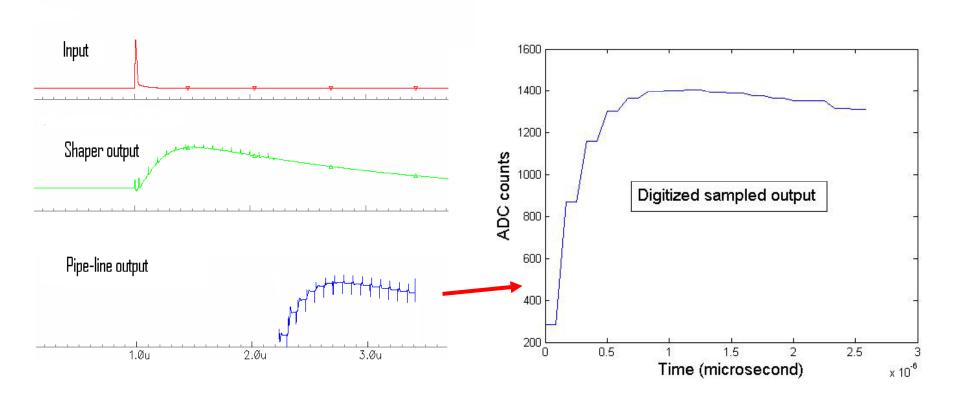

#### Analog pipeline output

Simulation of the analog pipeline

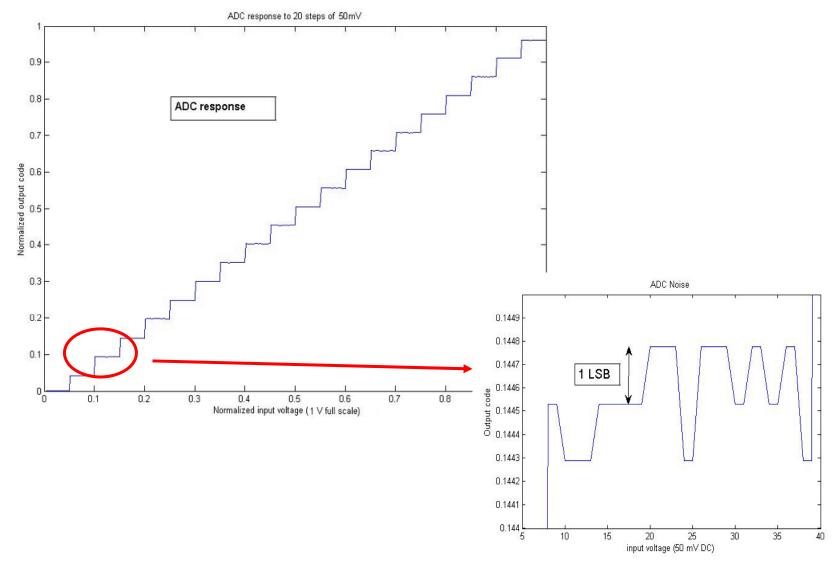

Measured output of the ADC

1 ADU= 500  $\mu$ V

#### ADC noise

# Outline

- Goals in CMOS 130nm

- Present results

- Chip 2 and further tests

- Next chip

### 130-1 tests to come

#### Measure ADC extensively

- Linearities

Integral, differential

- Noise

Fixed pattern, random

- Speed: Maximum clock rate

- Effective number of bits

#### 130nm Chip 2

#### LAPP Annecy le Vieux (D. Fougeron)

One channel test version in 130nm including:

- Preamp + shaper

- Improved pipeline (output buffer)

- Calibration channel (calibration caps)

- Calibration DAC

Chips presently under test

If OK, all analog blocks will be validated for a multi-channel version in 130nm aiming to read a real detector.

#### 130-2 tests to come (LAPP Annecy)

Measure improved pipeline extensively

Denis Fougeron's (LAPP) design

- Linearities

Integral, differential

- Noise

Fixed pattern, random

- Speed

Maximum clock rate

- Droop Hold data for 1ms at the ILC

# Outline

- Goals in CMOS 130

- Present results

- Chip 2 and further tests

- Next chip

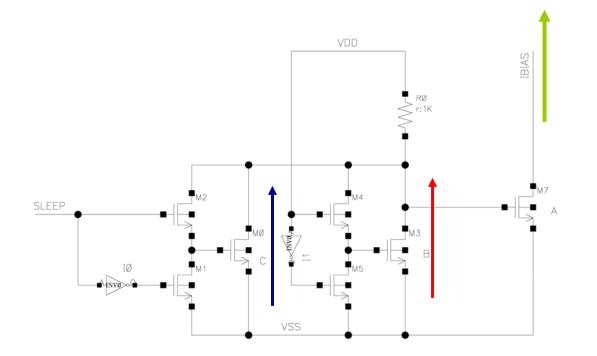

### Power cycling

Switch the current sources between zero and a small fraction (10<sup>-2</sup> to 10<sup>-3</sup>) of their nominal values

This option switches the current source feeding both the preamplifier & shaper between 2 values to be determined by simulation. Zero or a small fraction (0.1% - 1%) of biasing current is held during « power off ».

### Zero-power option tested on 180nm chip with a 2 ms deadtime under improvement

# Chip 130nm-3

#### Equip a detector

- Experience from lab test bench (laser + source) and

2007 beam-tests

- 130nm chips 1 + 2

- 128 channels with :

- Preamp-shapers + sparsifier

- Pipeline

- ADC

- Digital

- Calibration

- Power cycling

### Planned Digital Front-End

- Chip control

- Buffer memory

- Processing for

- Calibrations

- Amplitude and time least squares estimation, centroids

- Raw data lossless compression

- Tools

- Digital libraries in 130nm CMOS available

- Synthesis from VHDL/Verilog

- SRAM

- Some IPs: PLLs

- Need for a mixed-mode simulator

#### Some issues with 130nm design

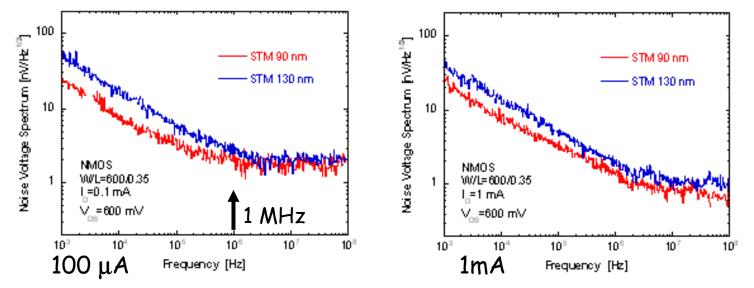

- Noise likely modeled pessimistic, but measured acceptable 90nm could be less noisy (Manghisoni, Re, Perugia 2006)

- Lower power supplies voltages reducing dynamic range

- Design rules more constraining

- Some (via densities) not available under Cadence Calibre (Mentor) required.

- Low Vt transistors leaky (Low leakage option available at regular Vt)

Manageable, UMC design kits are user friendly, Europractice very helpful.

### 130-90nm noise evaluation (STM process)

#### **Noise and inversion region**

L. Ratti et al FE2006 Perugia

12

At low drain current both devices work in the weak inversion region → channel thermal noise is roughly the same for both devices

- At high drain current, a significant difference in the channel thermal noise can be detected ← device from the 90 nm technology works closer to weak inversion region.

- Better 1/f noise performance provided by the STM 90 nm technology

#### Conclusion

These CMOS 130 designs and first test results demonstrate the feasibility of a highly integrated front-end for Silicon strips (or large pixels), at:

- DC power under  $500\mu$ W/ch

- Silicon area under 100 x 500  $\mu m^2/ch$

The End ....