## The EUDET Data Reduction Board (EUDRB)

(firmware version EUDRB\_MIMOx)

## On behalf of JRA-1 collaboration

A. Cotta Ramusino<sup>1</sup>

## ILC-VXD Workshop at VillaVigoni, Menaggio, April 22, 2008

#### Abstract

The EUDET Data Reduction board was developed at INFN-Ferrara in collaboration with University of Insubria-Como and INFN-Roma 3 to read out motherboard Monolithic Active Pixel Sensors (MAPS). The ("EUDRB\_MoBo") is a VME64x slave in 6U Eurocard format. The motherboard supports one "analog" ("EUDRB\_DCA") and one "digital" ("EUDRB\_DCD") daughter cards with PCI Mezzanine Card (PMC) format. The EUDRB DCD provides detector timing signals and it is also provides the EUDRB with a USB2.0 port for diagnostic and stand-alone data acquisition. The EUDRB-DCA has 4 single-ended/differential analog inputs and it is based on the design developed by IPHC (Institut Pluridisciplinaire Hubert-Curien) and the SUCIMA collaboration. The EUDRB has been so far employed with the IPHC MIMOSA-5, MIMOSTAR 2 and MIMOTel devices.

The "EUDRB\_MIOx" version of the firmware extends the functionality of the EUDRB card to include handling for the MIMOSA18 sensor and improves its rate capability

<sup>&</sup>lt;sup>1</sup> INFN,Ferrara, Italy

## 1 Introduction

The EUDET Data Reduction board (EUDRB) was developed at INFN-Ferrara, in collaboration with University of Insubria in Como and the INFN - Roma3, to read out Monolithic Active Pixel Sensors (MAPS).

The board generates detector timing signals in LVDS logic levels and provides analog to digital conversion of the 4 analog single-ended/differential input with 12bits resolution at a sampling frequency currently selectable between 15MHz and 11.25MHz. The EUDRB also features an output port (with TTL signalling levels) to configure detectors with JTAG programmable features. The motherboard has 4 banks of 256k x 48bit SRAM memories providing storage for up to 3 full frames for a 1Mpixel sensor like the MIMOSA-5 by IPHC. On this collected data the EUDRB performs Correlated Double Sampling (CDS), Pedestal Subtraction and Threshold Comparison on to reduce the data size for the events selected by the experimental trigger. The EUDRB may however provide the full frame information when the "raw" operating mode is selected. The EUDRB features a 256k x 32bit FIFO memory to provide temporary storage for data selected by a trigger and waiting to be readout. Both a VME and a USB2.0 interface are implemented; the EUDRB may be used for reading out MAPS both in stand-alone mode on a bench-top and in a standard VME-based data acquisition system.

The trigger input port on the front panel of the EUDRB was designed to interface it to the EUDET Trigger Logic Unit (TLU) and a trigger bus is also foreseen to distribute/receive trigger information over the free lines of the VME J2 connectors by means of a private bus on falt cable. Two LEMO connectors on the front panel of the EUDRB can be used to synchronize the data collection operations over a pool of boards.

The operation of the EUDRB is controlled by an ALTERA Cyclone II Field Programmable Gate Array (FPGA) device in which a NIOS-II microcontroller is also implemented to do initialization, housekeeping and diagnostic. An 8 MByte serial configuration device EPCS64 is used to store both the FPGA configuration information and the microcontroller code. At power up the FPGA loads its configuration from the EPCS64 and begins operation; the first task executed by the NIOS-II is to copy its ROM-resident code from the EPCS64 to its 1MByte program/data RAM and then jump to executing the code in RAM.

The FPGA handles the operations related to data collection, trigger servicing and I/O port interfacing with sequencers and logic blocks described in VHDL code or schematic diagrams. The FPGA project files are processed by the ALTERA Quartus development system to produce a configuration file (with a **.sof** extension). The development of the NIOS-II firmware is instead carried out using the ALTERA NIOS-IDE, an Eclipse-based framework; the compilation of the C-source code produces a loadable file (with a **.elf** extension). The "FLASH PROGRAMMER" tool of the NIOS-IDE is used to store both the .sof and the .elf files in the EPCS64 configuration device via the JTAG port of the FPGA.

The present description of the EUDRB refers then to a EUDRB loaded with the "EUDRB-MIMOX" combination of the TopLevel\_MIMOX.sof + EUDRB\_MIMOX.elf file developed by the writer for the commissioning of the demonstrator telescope at DESY and CERN.

The URL for the compressed file containing the whole project is (work on it still in progress):

#### http://www.fe.infn.it/u/cotta/ILC/EUDET/EUDRB-MIMOx/TopLevel\_MIMOx\_temp.rar

## 2 EUDRB hardware: an overview

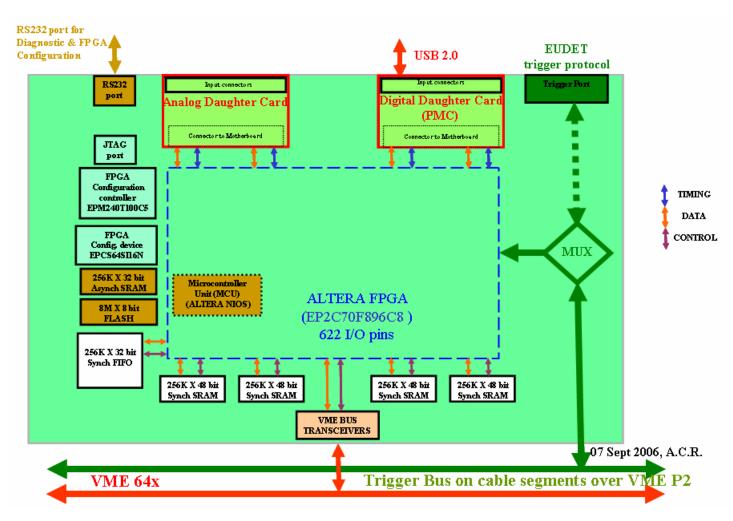

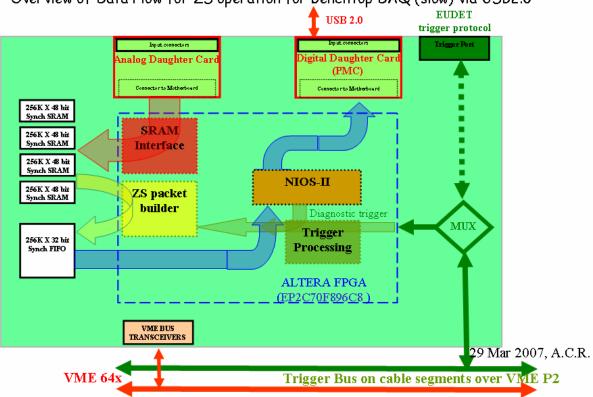

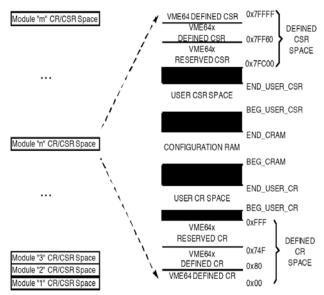

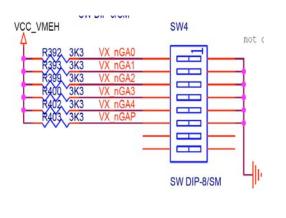

The figure on the following page represents a block diagram of the EUDRB.

## 2.1 EUDRB Motherboard (EUDRB\_MOBO)

The larger green block represents the motherboard (EUDRB\_MoBo) and the resources supported by it:

- the ALTERA EP2C70F896C8 FPGA (dashed blue outline) with the NIOS-II block in evidence. Details of the sequencers and logic blocks implemented in the FPGA are given in a later section

- the four banks of 256k x 48bit SRAM whose function is to hold the pixel voltage samples recorded during the last three scans of the four MAPS submatrices. The SRAM also hold values of pedestal (6bits) and threshold (6bits) which are specific to each pixel

- the 256k x 32bit FIFO used as temporary storage for the data requested with a trigger pending the readout through the VME or USB2.0 port

- utilities:

- the 256k \* 32bit SRAM used as program/data memory by the NIOS-II

- the 1M \* 8bit Flash (non volatile) memory which could be used by the NIOS to store permanent data (i.e. default pedestal/threshold values)

- the configuration device EPCS64

- the configuration controller based on an ALTERA EPM240T100 which provides an alternate method for bootstrapping the FPGA

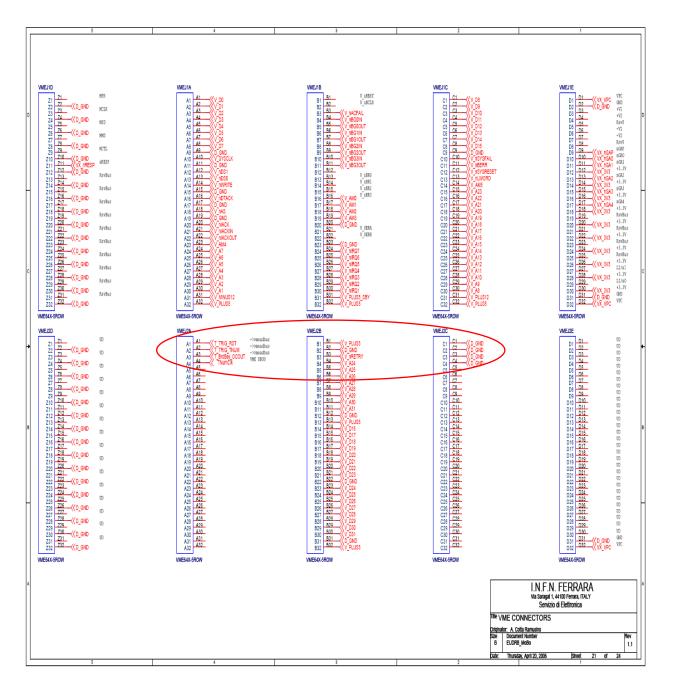

- the "EUDET TLU" ports: the front panel port to connect the EUDRB directly to the EUDET Trigger Logic Unit. An EUDRB connected to the TLU will act as the "TLU-Interface" for all the EUDRBs in a VME crate. The "TLU-Interface" fans out the trigger informations to other EUDRBs via a private bus on a cable segment installed on the free pins of the VME P2 connectors

- the RS-232 port which allows a simple and direct connection of the NIOS-II to an host PC for lower level diagnostics and debugging

## 2.2 EUDRB Digital Daughter Card (EUDRB\_DCD)

The EUDRB\_DCD is a board with standard PCI Mezzanine Card (PMC) format and PMC compatible connectors toward the EUDRB\_MOBO.

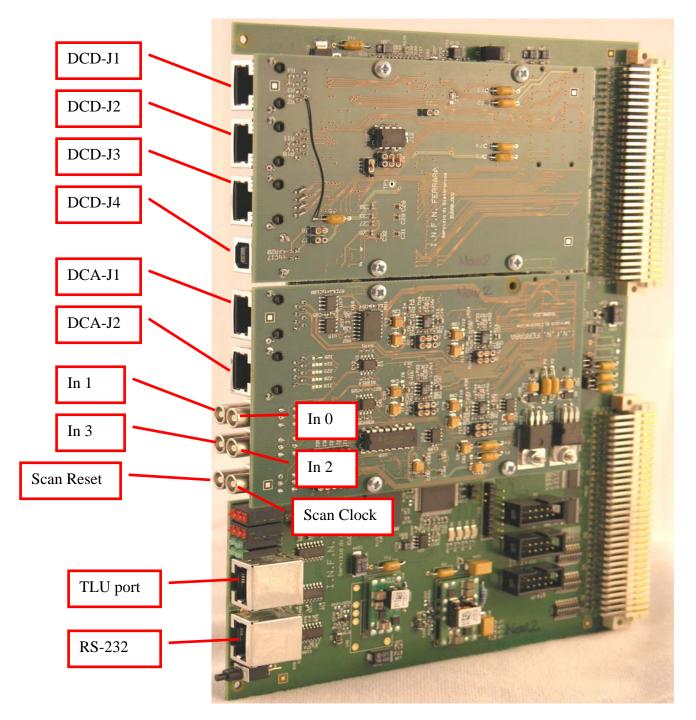

On the front side of the EUDRB\_DCD four connectors are available, whose pin definition is reported in Fig. 2.3.

The EUDRB\_DCD features a Cypress CY7C68013A-56PVXC, which, like in the MAPS readout boards designed by the SUCIMA collaborations, provides a relatively simple way of interfacing the EUDRB's FPGA to an USB2.0 bus, via the front panel connector J4.

The CY7C68013A-56PVXC holds its bootstrapping data into a 24LC128 128kbit serial EEPROM. The EUDRB\_DCD then provides an I/O port with single ended 3.3V TTL signal levels (connector J1, RJ45) to control the configuration of sensors with features programmable via a JTAG interface, like the IPHC MIMO\*2.

The J2 connector provides detector timing signals (Scan Clock and Scan Reset) in LVDS format.

For driving the MIMOTel sensor used in the demonstrator telescope an interface board has been developed at INFN Ferrara ("MIMOTel level adapter") which translates the voltage levels of the JTAG signals from the EUDRB\_DCD J1 connector, rearranges connector pin

Fig. 2.1 EUDRB 's block diagram

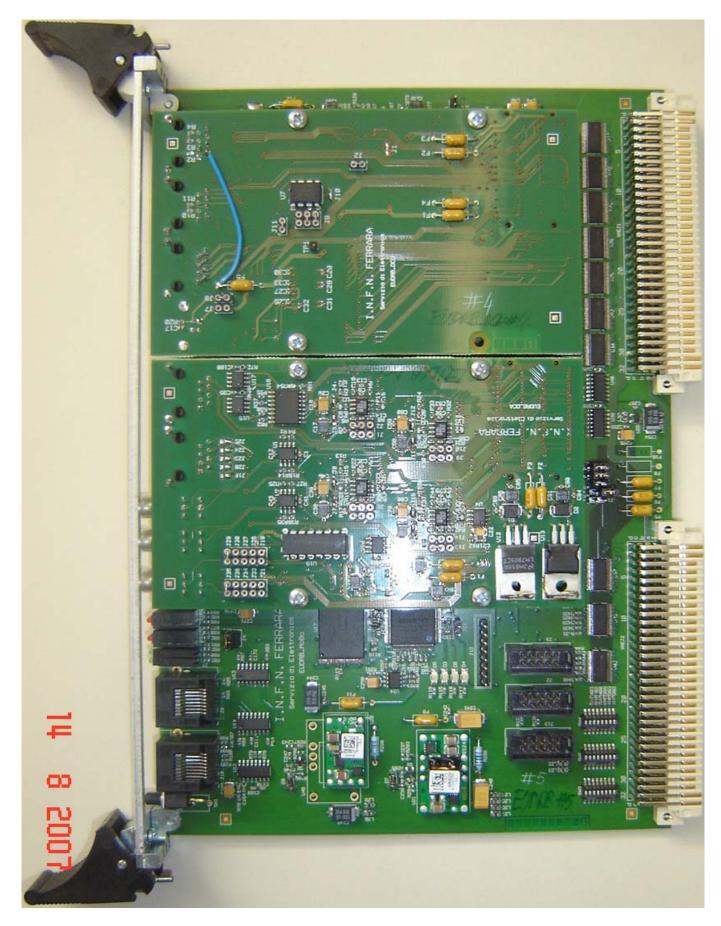

Fig. 2.2 EUDRB's top view with daughter cards installed

| DIGITAL DAUGHTER CARD connector pinout<br>DIMENSIONS 75 x 130 mm | ALTERNATE PINO<br>FOR M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MSTAR_TINS / MKOFF2 000 | MSTAR_TDI/OFAST 0/0<br>GND |            |                         | ALTERNATE PINOUT OF CONNECTOR D. 12 (B-45) | FOR MIMOSTAR / MIMOSA 5 | r no. Signal Name Type Standard<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_N6_CLRPID_<br>NSTAR_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N6_CLRPID_N | GND         | GND<br>MSTAR_CLK10Xp/ 0/0 | MISTAR_CLK1DXn/ 0/0 LVDS<br>MISTAR_SYNCp/M5_METP 0/0 LVDS | 00                                                | ALTERNATE PINOUT OF CONNECTOR D_J3 (RJ-45) | FOR MIMOSTAR / MIMOSA 5 / MIMO-ROMA Type Standard | 555      |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LVDSOUT1p/LVDSOUT1p/MR_SOF_OUTp 1/1 |                               | PINOUT OF CONNECTOR D_J4 (USB-B)<br>FOR MIMOSTAR / MIMOSA 5 / MIMO-ROMA | or no. Signal Name Type Standard<br>1 + 5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - DATA<br>- DATA<br>- DATA               |     |                                                                                                   |     | June 26th 2007, A.C.R.                                                                            |     |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|------------|-------------------------|--------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------|-----------------------------------------------------------|---------------------------------------------------|--------------------------------------------|---------------------------------------------------|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|---------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------|-----|

| ANALOG DAUGHTER CARD connector pinout<br>DIMENSIONS 75 x 130 mm  | PINOUT OF CONNECTOR A_J1 (R.J.45)<br>Signal Name Type Standard RJ.45 conductor no<br>Jacoton Jacoton | : <u> </u>              | In analog<br>In analog     | lin analog | lon analog<br>In analog | PINOUT DE CONNECTOR A 12 (BL-45)           |                         | Signal Mane (normal/atternate) (1) Type Standard RJ-45 conductor no<br>(1) Atternate printicions to hive the MIMOSA V with analogicand alone analong LVTTL 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                           | Out /Out analog/LVTTL                                     | DAC_OUT4 / CDS_TP Out / Out analog/LVTTL 8<br>GND |                                            | تە                                                | goine in | IECTOR A_J4 (LEMO) | Signal Name Type Standard 5<br>ASGLIp In analog 6<br>ASU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                     | NNECTOR A_J5 (LEMO)<br>e Type | ASGi2p In analog<br>GND                                                 | USB-B conductor no USB-B conduct | ASGLAP In analog ASGLAP In analog ASGLAP |     | PINOUT OF CONNECTOR A_J7 (LEMO)<br>Signal Name<br>External Pixel Scan Control NamoROMA) In analog | GND | PINOUT OF CONNECTOR A_J8 (LEMO)<br>Signal Name<br>External "Start Of Frame" (MIMO-ROMA) In analog | GND |

| MOTHER BOARD connector pinout<br>DIMENSIONS 233 x 160 mm         | PINOUT OF CONNECTOR MOBO_J1 (RJ-45)<br>Signal Name Type Standard RJ-45 con<br>Trinveshier Tronokinner P 1 UNIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ber_N I LVDS            |                            | 00         | 0 LVDS                  | PINOUT OF CONNECTOR MOBO -1/2/81-45)       |                         | Signal Name Type Standard RU-45 con<br>Spare/UDS_IN P I LUDS 1 (1)<br>Spare/UDS_IN I LUDS 1 (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power power | 0 LVDS                    | GND Power power 5<br>RU_TX 0 RS-232 6                     | RS-232                                            |                                            | IEMOcom                                           | - 0      |                    | 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 11000 |                                     | LENOcon                       | - 6                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LENOcon                                  | J . | LEMOcon                                                                                           | 2   | LEMOcon                                                                                           | 7   |

|                                                                  | RJ-45 conductor no.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - (1 (7)                | ৰ জ                        | 001        | ~ 00                    |                                            |                         | RJ-45 conductor no.<br>1<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100.        | 4 v                       | 9 1 - 1                                                   | œ                                                 |                                            |                                                   |          |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |                               |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |     |                                                                                                   |     |                                                                                                   |     |

Fig. 2.3 EUDRB's front panel connectors pinout

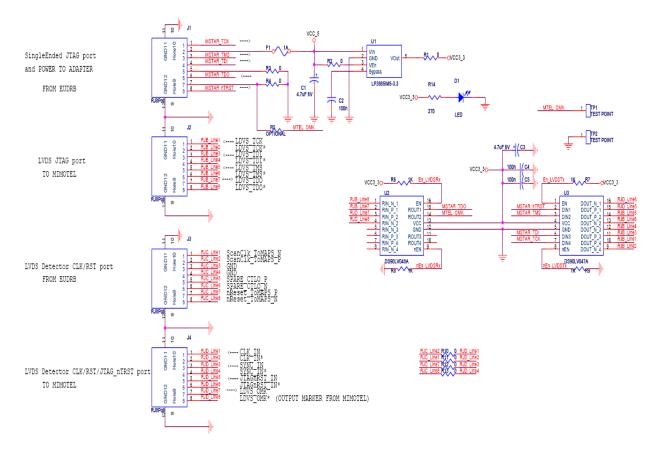

definitions and drives the output signals through two RJ45 connectors to the MIMOTel. Fig. 2.4 shows the electric diagram of the "MIMOTel level adapter".

The J3 connector receives detector timing signals (Scan Clock and Scan Reset) in LVDS format from an external source (like a sensor's proximity board or another EUDRB). This feature has not been used in the demonstration telescope because a different port, on the analog daughter card) for such synchronization signals has been used.

Fig. 2.4 MIMOTel level adapter electric diagram

## 2.3 EUDRB Analog Daughter Card (EUDRB\_DCA)

The EUDRB\_DCA is a board with standard PCI Mezzanine Card (PMC) format and a pair of IEEE-1386 PMC connectors toward the EUDRB\_MOBO; the signals assignment on this connectors is not compatible with the PMC standard.

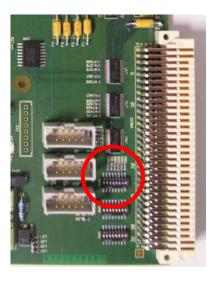

On the front side of the EUDRB\_DCA two RJ45 connectors are available, whose pin definition is reported in Fig. 2.3; there are also 6 LEMO connectors, as shown in Fig. 2.5.

The EUDRB\_DCA J1 is the port for the differential analog input signals, which are usually buffered and driven differentially by the sensors proximity board along a four-pair shielded twisted cable, to reduce noise pick-up.

The EUDRB\_DCA J2 is an output port which could provide four channel of polarization voltages or four static signals to the MIMOSA-5 detector to configure its operating mode.

The main task of the EUDRB\_DCA is to digitize the four input signals. The design of the ADC stage and its ADC driver is based on the designs developed by the IPHC in Strasbourg and the University of Cracow and exploited by the SUCIMA collaboration.

The four A/D converters used on the board are of the type AD9226 by Analog Devices. The AD9226 resolution is 12 bit and its sampling frequency can reach 65MHz.

The AD9226's differential inputs (with a 2V dynamic range) are driven by a buffer stage based on the differential amplifier AD8138. The buffer stages also take care of translating the single ended inputs from the LEMO connectors into the differential format; this option can be enabled by modifying solder-jumpers on the analog daughter card.

Fig. 2.5 EUDRB connectors

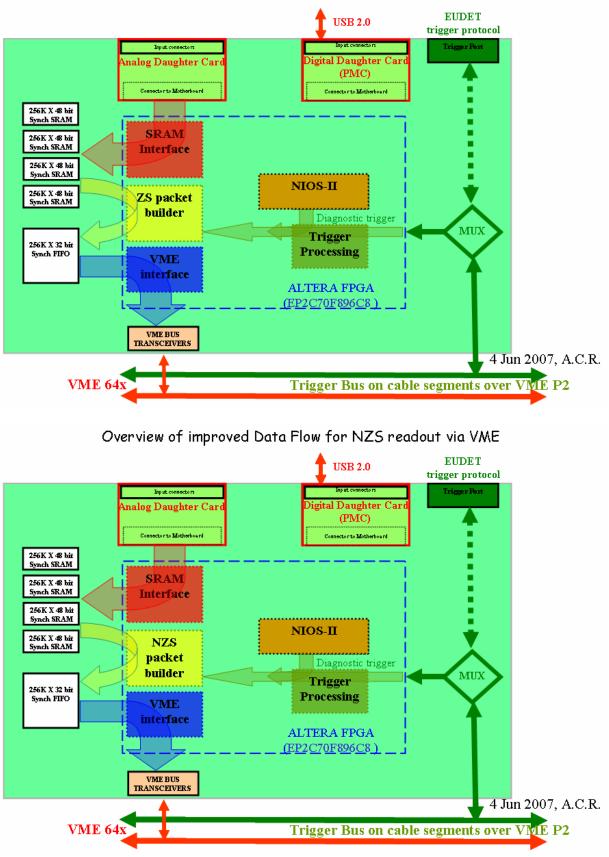

## 3 EUDRB operation: an overview (EUDRB\_MIMOx firmware)

The main tasks of the EUDRB are:

- a) to configure the operating mode and parameters of the sensor via its JTAG port; this task is performed by the NIOS-II (not needed for MIMOSA18)

- b) to provide the sensor with the scan clock and a scan reset (which could be periodical for sensors like the MIMOSA-5) for initialization of the sensor's pixel addressing resources

- c) to sample and A/D convert the pixel voltage levels as they sequentially appear at the analog inputs at the pace set by the scan clock signal

- d) to store the voltage samples in the frame buffers, i.e. the four banks of 256K \* 48bit SRAM described in the overview

- e) to respond to a trigger according to one of the following two operating modes :

- "raw" mode:

when a trigger is received by the board the scan is continued for a number of cycles equal to the frame size. Then the scan stops and the contents of the pixel memories are formatted and transferred to the output FIFO.

For the EUDRB\_MIMOx <u>only two samples are transferred to the output</u> <u>FIFO for each pixel</u>: the sample BEFORE the trigger and the sample AFTER. The samples data is formatted into a packet which includes a header and a trailer. For this reason <u>the total event size is 4 long words larger than</u> <u>the output FIFO size</u>. For this reason I have decided, for the time being, to drop out from the event packet the samples concerning pixel (255,255) of <u>each subframe</u>. The sensor scan resumes as soon as one event has been written to the output FIFO and the board can thus receive a new trigger while the readout of the previous event is pending.

• "zero suppressed" mode:

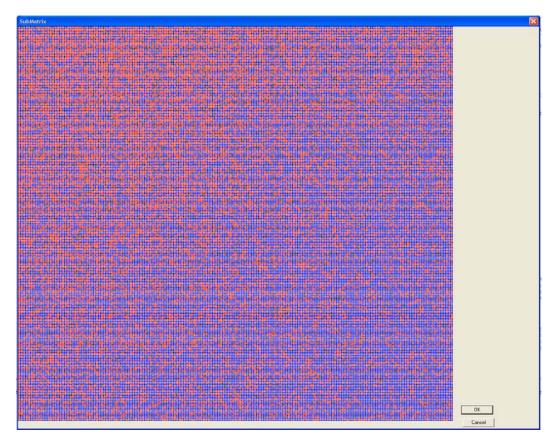

the scan clock does never stop in this mode. When the trigger is received by the EUDRB the boards records the address of the pixel currently being sampled (the "pivot" pixel) and starts calculating on-the-fly the CDS for every pixels acquired afterwards for a number of clock cycles equal to the submatrix pixel count. If the result of the CDS for a pixel is above its <u>specific</u> threshold after correcting for its <u>specific</u> noise pedestal, then the pixel address and its signals are stored in the output FIFO. The pixel specific values for threshold and pedestal are stored in the pixel memories along with pixel data and need initialization via USB or VME before stating the actual zero-suppressed (ZS) data taking.

With the EUDRB\_MIMOx firmware the zero-suppression process is carried on by four "MIMOx\_CDS sequencers" working in parallel, one for each of the inputs, i.e one per sub-matrix. Each "MIMOx\_CDS sequencer" is equipped with a FIFO (internal to the FPGA and 1024 words deep) which stores locally the ZS data pending its transfer to the Output FIFO (256K words deep). The 4 de-randomizing FIFOs are continuously scanned by the sequencer described in the module "MIMOx\_ZSFIFOBuffer" which then writes the ZS data from any sub-matrix to the output FIFO. If any of the de-randomizing FIFOs were filled in this process by an event with an anomalous multiplicity its FULL condition would appear as information in the trailer of the event data packet.

When the EUDRB receives the first trigger it sets the BUSY signal (preventing new triggers) only for the time needed for the scan for "hit" pixel.

As soon as the scan is over and the results stored in the output FIFO by the "MIMOx\_ZSFIFOBuffer" module the BUSY is released and the EUDRB is ready to take another trigger.

If a second trigger arrives while the first has not been yet readout it is still processed immediately by the "MIMOx\_CDS Sequencers" and "hit" data stored in the local FIFO.

The BUSY signal however stays ON until the event in the output FIFO is read and the "MIMOx\_ZSFIFOBuffer" can transfer data of "hit" pixels from the local FIFOs to the output one.

In this way the operating rate of the DAQ system based on EUDRBs should reach the limit imposed by the sensor scan time.

f) to transfer the data requested by the trigger to the data acquisition system through the active output bus, either the VME or the USB2.0. The EUDRB prepared for the commissioning of the demonstrator telescope features a slave interface to the VME bus capable of transferring readout data in MBLT (Multiplexed Block Transfer) mode at a peak rate of about 40MB/s during the MBLT cycle.

The EUDRB can also be readout via the USB2.0. In the configuration prepared for the demonstrator telescope's first test beam the data is extracted from the output FIFO and moved to the USB2.0 link by the NIOS-II rather than by a dedicated sequencer described in VHDL. While this mode is useful when debugging the board because it allows an easy and deterministic way (the NIOS-II code can be written in C language) to custom-process the data as it is transferred, it does not allow to exploit the full bandwidth of the USB2.0 bus.

Overview of Data Flow for ZS operation (mode for real data taking)

Fig. 3.1 Schematic representation of data flow for ZeroSuppressed and raw modes

## 3.1 LED indicators

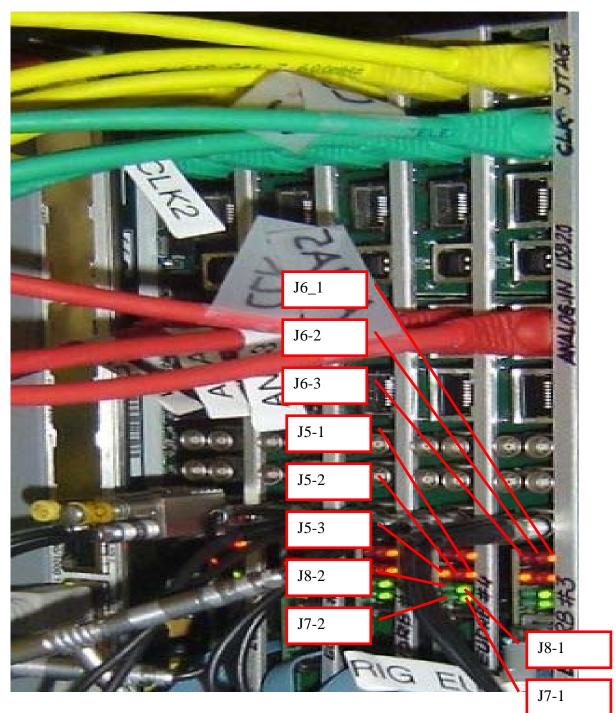

The part reference on the EUDRB\_MOBO electric diagram, the signal source and the meaning of each LED indicator is reported in the table below. The location of the LED indicators is shown in the picture in Fig. 3.1.

| PartRef | SignalSource | Meaning when lit                                                   |

|---------|--------------|--------------------------------------------------------------------|

| J6-3    | FPGA.L25     | A command to the NIOS-II has been received via the VME port.       |

|         |              | The LED is turned off by the NIOS-II at the end of the execution.  |

| J6-2    | FPGA.M22     | A flash on this LED means that the EUDRB has acknowledged a        |

|         |              | VME transaction                                                    |

| J6-1    | FPGA.N21     | The NIOS-II can be controlled via the VME or the USB port. If the  |

|         |              | LED is OFF (when jumper J4 is removed) then the NIOS-II is         |

|         |              | expecting commands from its UART connected to the EUDRB's          |

|         |              | RS-232 port                                                        |

| J5-3    | FPGA.E13     | The JTAG configuration of the detector has been performed, the     |

|         |              | detector has been provided with the scan clock and reset and the   |

|         |              | post-reset time has expired. The detector should thus be ready for |

|         |              | data taking.                                                       |

| J5-2    | FPGA.E23     | The NIOS-II has been commanded to generate an internal fake        |

|         |              | trigger for diagnosing the EUDRB trigger response                  |

| J5-1    | FPGA.L24     | The VME interface holds one event to transfer or which is being    |

|         |              | transferred                                                        |

| J8-2    | FPGA.C29     | The EUDRB is operating in Zero Suppressed mode                     |

| J8-1    | Jumper J4.2  | The NIOS-II can be controlled via the VME or the USB port. If the  |

|         |              | LED is OFF (when jumper J4 is removed) then the NIOS-II is         |

|         |              | expecting commands from its UART connected to the EUDRB's          |

|         |              | RS-232 port                                                        |

| J7-2    | U18.55       | Not used                                                           |

| J7-1    | U24.6        | Power OK: all supply voltages are on. The LED goes off also while  |

|         |              | pushing the reset pushbutton                                       |

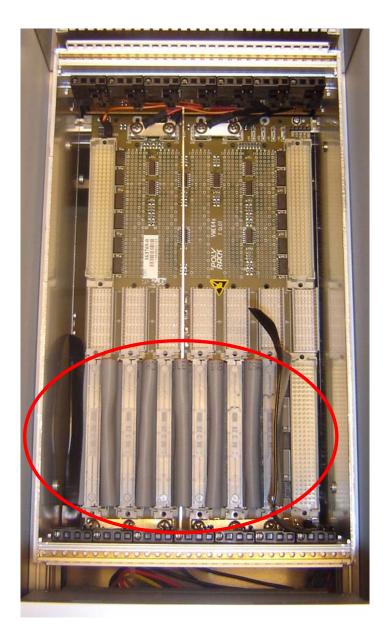

Fig. 3.2 Detail of the DAQ crate in the DESY testbeam

## 4 EUDRB FPGA: the "hard-coded" functions

The development system for the ALTERA FPGAs accepts entries in form of both:

• Schematics (file with an extension .bdf),

showing the interconnections among different functional units, be they simple primitive or blocks representing complex units fully described at lower levels of the hierarchy. Interconnections in a schematics are made by "wires" and their labels

• Text,

describing the functionality of a module in the hardware description language of choice, VHDL in this case. The VHDL description file (extension .vhd) can then be associated to a symbol which can be entered and interconnected in the schematic view

Both entry methods have been used in the design of the ALTERA FPGA installed on the EUDRB.

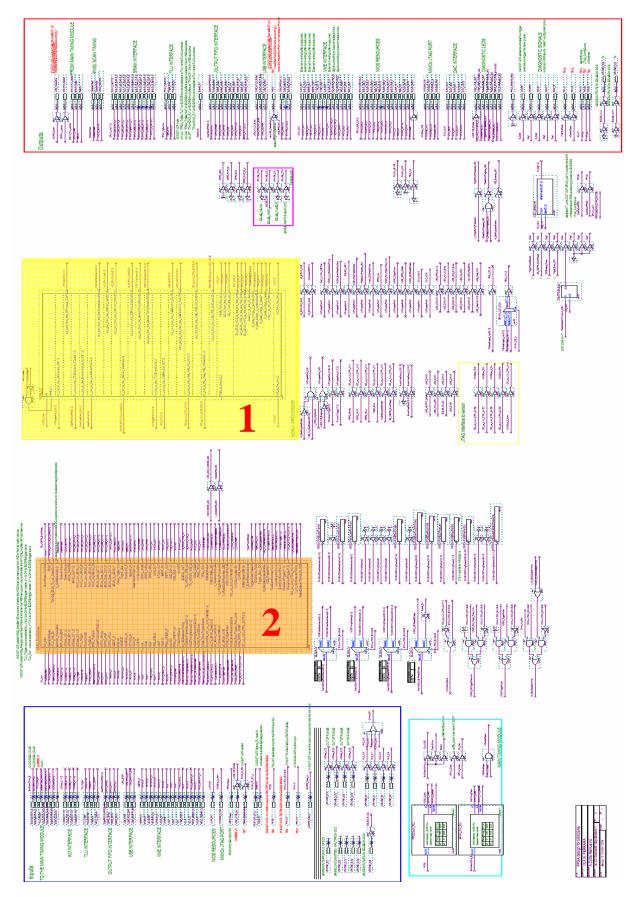

The "TopLevel\_MIMOx.bdf" schematic of **Fig. 4.1** represents the top of the hierarchy of design files making up the whole project; it shows how the functional blocks associated with different aspects of the EUDRB operation are interconnected.

The whole design hierarchy can be recovered from the archive with the URL indicated in the introduction.

The main modules have been indicated by coloured block in Fig. 4.1, to help identifying them and their area of influence in the data flow diagram presented above.

#### 4.1 The "MAPS\_uC" block (1)

This block of the "TopLevel\_MIMOx.bdf" schematic represents the set of VHDL files which describe the behaviour of the NIOS-II embedded microcontroller. The NIOS-II source files are automatically generated by a the "SOPC Builder" Wizard integrated into the ALTERA QUARTUS II design framework. Besides creating the VHDL source files, which are compiled together with all the other files in the project hierarchy to synthesize the logic network, the "SOPC Builder" creates a system description file (with extension .ptf) which is then used by the "ALTERA NIOS IDE" (Integrated Development Environment) to create the header files and the library links needed when compiling the C-source code for the NIOS-II.

A later chapter gives a little more detail on the NIOS-II firmware and operation.

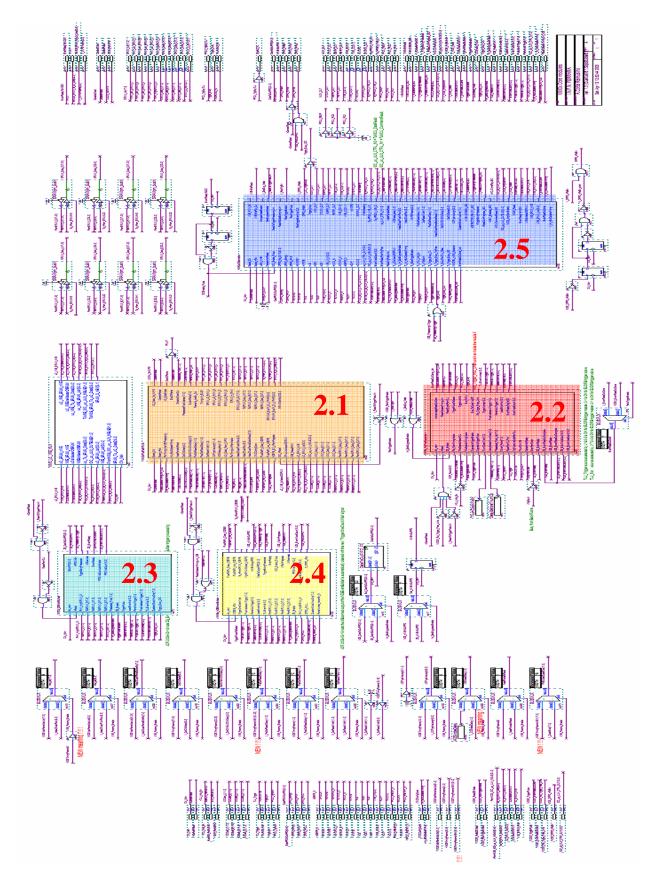

#### 4.2 The "MIMOx\_CoreModules" block (2)

This block, shown in **Fig. 4.2**, is the "container" of all the VHDL description for the resources controlling the EUDRB operation.

The "MIMOx\_CoreModules" can easily be singled-out from the entire project to be developed and simulated independently from the NIOS-II block for faster turn-around times.

The resources involved in the control of specific tasks are described each in a well definite block. A brief description of the modules in which the "MIMOx\_CoreModules" is partitioned follows below.

#### 4.2.1 The "MIMOxPixelsToSRAMs" block (2.1)

This block contains the VHDL description of the resources generating the detector timing signals, controlling the A/D conversion of pixel voltage samples and controlling the subsequent storage of A/D output in the pixel frame buffer memories.

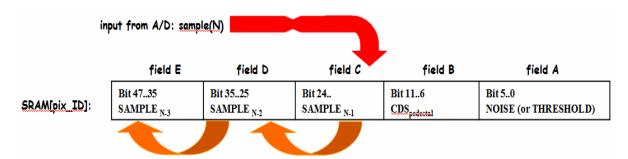

It is worth noting here how the "MIMOxPixelsToSRAMs" unit operates on the frame buffers, with the help of the following diagram:

Each memory location, 48 bit wide, is associated with one pixel of the sensor and it holds the values of the last three pixel voltage samples, encoded in a 12bit field. The memory word also holds the values of the pixel pedestal, i.e. the baseline value of the result of the CDS operation, and the threshold that decides whether the pedestal-corrected signal after the CDS is to be considered a "hit" and, as such, copied into the output FIFO (along with the pixel coordinate).

This memory organization follows the standard already established by the designers of the data acquisition boards developed at the IPHC in Strasbourg and by the University of Cracow collaborating at the SUCIMA project. These previous designs only provided storage for two pixel samples, resulting in a memory word of just 32bit.

The addition of the storage for a further pixel sample should provide more information on the history of the pixel voltage in a wider interval around the trigger time, which could be useful when characterizing new sensors.

## 4.2.2 The "MIMOxTrigProcSequencer" block (2.2)

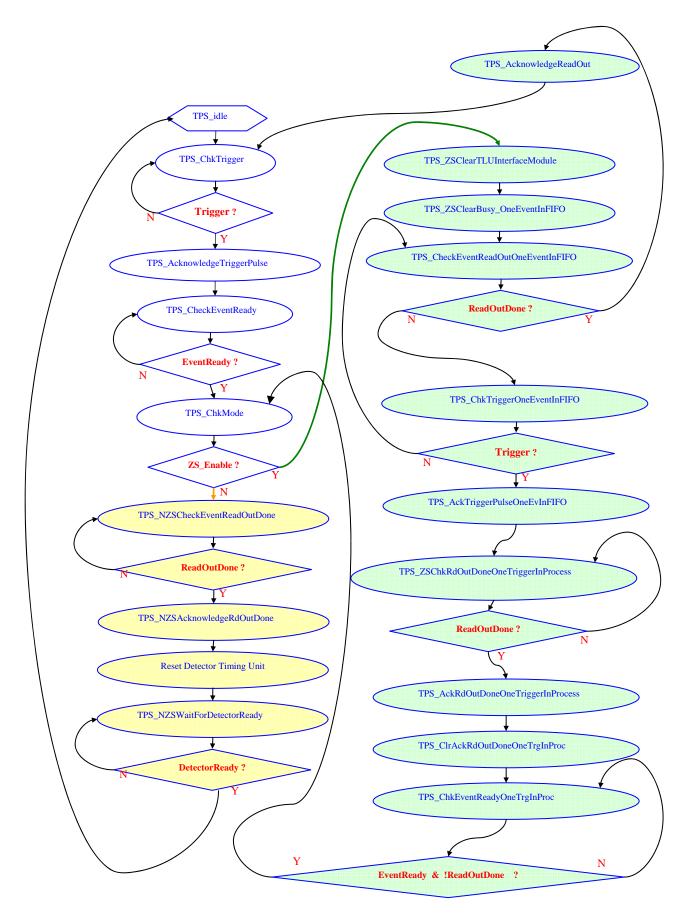

This block contains the VHDL description of the scheduler of all processes involved in the response of the EUDRB to triggers (real from EUDET-TLU or fake from the on-board NIOS-II). A flow diagram of the scheduler state machine is shown in **Fig. 4.3**.

The "MIMOxTrigProcSequencer" contains also one instance of the "MIMOx\_TLUInterFace" VHDL component, which describes the resources used in extracting the trigger information sent, according to a serial communication protocol, by the EUDET TLU. This module also controls the Busy line monitord by the TLU to determine when the EUDRB is ready for the next trigger. The EUDRB connected to the TLU through the front panel connector is the "TLU-Interface".

The status of the BUSY signal that the "TLU-Interface" returns to the TLU reflects the BUSY status of all the TLU in the crates; this information is obtained by means of an open collector signals distributed to all the EUDRBs in the crate via the user-defined lines of the VME bus.

## 4.2.3 The "MIMOx\_ZSEventBuilder" block (2.3)

This block performs, when scheduled by the "MIMOxTrigProcSequencer" module, the fetching of "hit" data in Zero-Suppressed mode without stopping detector scan and frame buffer update. Four "MIMOx\_CDS" submodules perform the "hit"extraction in parallel (CDS and comparison with threshold after perdestal subtraction), one for each submatrix, as already described in the EUDRB operation overview on page 8.

This processor controls local FIFOs to store hit information until the output FIFO is available for receiving a new event data packet. The event data packet contains "hit" signal amplitude and pixel address encompassed within a Header and a Trailer. the format is given in a later chapter.

## 4.2.4 The "MIMOx\_NZSEventBuilder" block (2.4)

This block performs, when scheduled by the "MIMOxTrigProcSequencer" module, the transfer of two voltage samples for each pixel, one BEFORE and one AFTER the trigger to the output FIFO as soon as this is available for receiving a new event data packet. The event data packet contains only the sample voltage amplitude. No need for addressing information is needed since the scan order is a priori defined. A Header and a Trailer are foreseen for flagging the begin and the end of the event data packet, as explained in detail in a later chapter. The sensor scan stops when the "MIMOx\_NZSEventBuilder" begins operation and restart automatically when the event packet produced by the trigger has been completely readout.

## 4.2.5 The "MIMOxIOController" block (2.5)

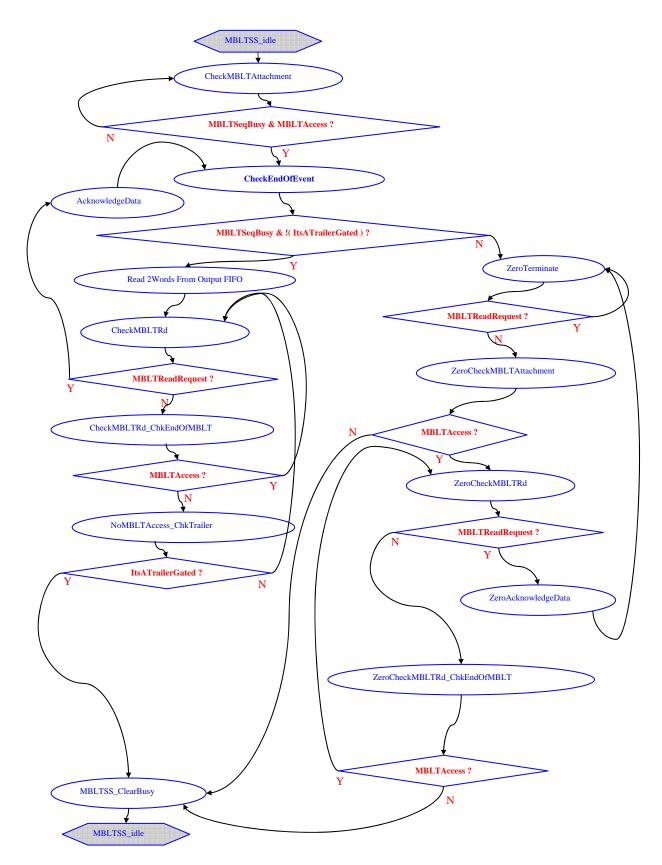

This block performs, when scheduled by the "MIMOxTrigProcSequencer" module, the transfer of the contents of the output FIFO to the VME CMU by responding to "Multiplexed Block Read Transfers" (MBLT for short) commanded by the CPU. The MIMOxIOController module actually demands this task to the "MIMOxMBLTSequencer" sub-unit.

**Fig. 4.4** shows the flow chart of the "MIMOxMBLTSequencer" supervising this process. The sequencer is complicated from the fact that the VME MBLT transfer of a large number of words is broken down by the VME CPU in a number of "atomic" block transfers of up to 2048 bytes, of length not fixed a priori.

**Fig. 4.5** shows two of such "atomic" MBLT tranfers scheduled by the VME CPU at the end of an MBLT transfer of 8208 bytes. The signals shown in the picture are internal FPGA signals captured thru its JTAG port by means of special dedicated resources. **Fig. 4.5** also shows how the transfer of data from the "MIMOx\_ZSEventBuilder" local FIFO buffers starts soon after completion of the readout of data from a previous trigger.

The "MIMOxIOController" also features a VME A32/D32 slave interface for all configuration and house-keeping tasks controlled by the VME\_CPU. It is worth noting here that the VME interface can map the frame buffers directly into the VME addressable space, in order to allow the user to directly write the pixel pedestal and threshold fields described above. The details of the resources mapped onto the VME bus are given in a later section of this note.

Fig,4.1 EUDRB\_MIMO's design "TopLevel\_MIMOx.bdf" schematic.

Block 1: MIMOx\_CoreModules. Block 2: NIOS-II microcontroller instance

**Fig,4.2 EUDRB\_MIMOx's design "MIMOx\_CoreModules.bdf" schematic.** Block 1: "MIMOxPixelsToSRAMs". Block 2: MIMOxTrigProcSequencer. Block 3: MIMOx\_ZSEventBuilder. Block 4: MIMOx\_NZSEventBuilder. Block 5: MIMOxIOController

Fig. 4.3 Flow chart of the "MIMOxTrigProcSequencer" finite state machine

Fig. 4.4 Flow chart of the "MIMOxIOController| MIMOxMBLTSequencer" finite state machine

| UN MIM     | DxTestBasicZS20080404.stp                                                                     |                           |                                                              |                         |            |                                       |                                      |            |                                        |                   |

|------------|-----------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------|-------------------------|------------|---------------------------------------|--------------------------------------|------------|----------------------------------------|-------------------|

|            | 🔖 🗉 🕅 Invalid JTAG configuration 🔹 🕽                                                          | 1 D 1                     | <u>}</u>                                                     |                         |            |                                       |                                      |            |                                        |                   |

| Instance M | lanager. 🍬 ې 🔳 🔝 Invalid JTAG configuration                                                   | 6                         | )                                                            |                         |            |                                       | X                                    | JTAG Chair | n Configuration: No device is selected | 2 >               |

| Instance   | Status Incremental Co                                                                         | mpilation I               | LEs: 5675   Memory: 532480   M512: NA   M4K: NA   MRAM: N    | A                       |            |                                       |                                      |            |                                        | -<br>             |

| 🚼 EUDRE    | MIMO Not running                                                                              | 1                         | 5675 cells 532480 bits NA NA N                               | IA.                     |            |                                       |                                      | Hardware:  | Disabled                               | Setup             |

|            |                                                                                               |                           |                                                              |                         |            |                                       |                                      | Device:    | None Detected                          | Scan Chain        |

|            |                                                                                               |                           |                                                              |                         |            |                                       |                                      | >> SOF     | Manager: 👗 🕕                           |                   |

|            |                                                                                               |                           |                                                              |                         |            |                                       |                                      |            |                                        |                   |

| log: 20(   |                                                                                               | <del>(</del> <del>,</del> |                                                              |                         | +21<br>    |                                       |                                      |            |                                        | ^                 |

| Type A     | lias Name                                                                                     | -102 <sub>Val</sub> -101  | -160 -152 -144 -136 -128 -120 -112 -10                       | 4 -96 -88               | -80 -7     | 2 -64 -56 -48                         | -40 -32 -24 -16                      | -8         | 0 8 16 24 32                           | 40 48             |

| 0          | ne:MIMOxRMW_Machine_instance/ADC_Data_strobe                                                  | 0                         |                                                              | μıı                     |            |                                       |                                      |            |                                        |                   |

| Ď          | ⊕- ADData_A                                                                                   | 817h                      | 818h/817h/818h/817h/ 818h /819h/ 818h / 817                  | h <u>(818h)(817h)</u> ( | 818h (817h | X 818h X 817h X81                     | 18h)(816h)(816h)                     | 18h        | (817h)(818h)(817h)(818                 | 3h ( 817h         |

| Ð          | GRAM_Data_A[05]                                                                               | 08h                       |                                                              |                         |            | 08h                                   |                                      |            |                                        |                   |

| ٥          |                                                                                               | 00h                       |                                                              |                         |            | OOh                                   |                                      |            | <br> <br>                              |                   |

| Ø          |                                                                                               | 817h 🔷                    | ) <u>817h) (818h) (() () () () () () () () () () () () (</u> | )()(_)()(_)(818h)(      | 817h 🐰     | )(817h)( 818h ))( 817                 | h                                    | 818h X X   | 818h XX 818h X817h 818h X              | X <u>818h</u>     |

| Ø          |                                                                                               | 818h                      | 817h X 818h (817h) X 818h 817h X (                           | 818h XX X               | 817h       | )                                     | <u>7h (818h) ()( ( 817h (818h))(</u> |            | ( <u>818h)(817h)(818h)(817h)(818h</u>  | ) <u>( ( 818h</u> |

| Ð          |                                                                                               | 818h                      | )818h /818h)(/818h)()(                                       | 818h X X                | 817h), X   | ) <u>     818h   )</u> <u>818h  )</u> | <u>) 818h () () () (817h (81</u>     | Bh) (      | <u>818h ( )( )( 817h))( )( )</u>       | <u>818h (</u>     |

| ۵          | RnW_Low_SRAM_A                                                                                | 1                         |                                                              |                         | $\Box$     |                                       |                                      | <u> </u>   |                                        |                   |

| 6          |                                                                                               | 3h                        |                                                              |                         |            | 3h                                    |                                      |            | I<br>I                                 |                   |

| 5          | - DataToOutFIFO                                                                               | 1400A01Fh                 |                                                              | 140                     | 0A01Fh     |                                       |                                      |            |                                        |                   |

| 0          | nWrEnOutFIFO                                                                                  | 1                         |                                                              |                         |            |                                       |                                      |            |                                        |                   |

|            | OFIFO_nEmpty                                                                                  | 1                         |                                                              |                         |            |                                       |                                      |            |                                        |                   |

| 0          | OFIFO_nRdEn                                                                                   | 1                         |                                                              |                         |            |                                       |                                      |            |                                        |                   |

|            | OFIFO_nFULL                                                                                   | 1                         |                                                              |                         | <u> </u>   |                                       |                                      |            |                                        |                   |

| 2          | DataFROMOutFIFO                                                                               | 5401B01Fh                 | 5401B01Fh                                                    | <b></b>                 | ╨          | F1000D0Eh                             |                                      |            | 05400804h                              |                   |

| 0          | DTACK_OUT                                                                                     | 1                         |                                                              |                         |            |                                       |                                      |            |                                        |                   |

|            | To_nFROM_VME_AD                                                                               | 0                         |                                                              |                         |            |                                       |                                      |            |                                        |                   |

| 0          | To_nFROM_VME_D                                                                                | 0                         |                                                              |                         |            |                                       |                                      |            |                                        |                   |

| D          | ocSequencer.inst35/2S_EventWordCount_active    ocSequencer.inst35/2S_EventWordCount_active    |                           |                                                              | 00804h                  |            | W                                     |                                      | )0002h     |                                        |                   |

| D          | . Group                                                                                       | 30401FF8h                 | FFFFFFEh 3040                                                |                         | )(A01Eh_)) | ( <u>)(30402000h)</u>                 | )( 9402C01Eh )))( ) ( )              |            | FFFFFFEh                               |                   |

| ð          | H- VME_D                                                                                      | 00000042h                 | FFFFFFhX                                                     | <u> </u>                | 401B01Fh_) |                                       | <u>XX F1000D0Eh XX X X X</u>         |            | FFFFFFh                                | _                 |

|            | cer:MMOxMBLTSequencer_inst(tts_A_Trailer_gated                                                | 0                         | , L                                                          |                         |            |                                       |                                      |            |                                        |                   |

| 0          | ZS_NZSPB_EventReady                                                                           | 1                         |                                                              |                         | -          |                                       |                                      | _          |                                        |                   |

| 0          | MIMOx_CoreModules:inst15[EventReadyToIOC                                                      | 1                         |                                                              |                         | <u> </u>   |                                       |                                      |            |                                        |                   |

| 0          | MIMOx_CoreModules:inst15[NZS_EventReady                                                       | 0                         |                                                              |                         |            |                                       |                                      | /          |                                        |                   |

| 0          | MIMOx_CoreModules:inst15[ZS_EventReady                                                        | 0                         |                                                              |                         |            |                                       |                                      |            |                                        |                   |

| 0          | ules.inst15/MIMOx_ZSEventBuilder.inst72/AllScanned                                            |                           |                                                              |                         | =          |                                       |                                      |            | 1                                      | _                 |

| 0          | sinst15/MMOx_NZSEventBuilderinst105/AllScanned                                                |                           |                                                              |                         |            |                                       |                                      |            | 1<br>1<br>1                            |                   |

| Ū          | NZSEventBuilder:inst105[UIntNoOfPixelScanned                                                  |                           |                                                              |                         |            | 00000h                                |                                      |            | I<br>I<br>I                            |                   |