### Deep N-well 130nm CMOS MAPS for the ILC vertex detector

Valerio Re

C. Andreoli, A. Bulgheroni, C. Cappellini, M. Caccia, L. Gaioni, M. Jastrzab, M. Manghisoni, E. Pozzati, L. Ratti, V. Re, F. Risigo, V. Speziali, G. Traversi

INFN Milano, Pavia, Roma III

University of Bergamo, University of Insubria, University of Pavia, Italy

ILC Vertex Workshop

April 21 - 24, 2008 - Villa Vigoni

### Why hybrid-pixel-like MAPS

- Modern VLSI CMOS processes (130 nm and below) could be exploited to increase the functionality in the elementary cell → sparsified readout of the pixel matrix.

- Data sparsification could be an important asset at future particle physics experiments (ILC, Super B-Factory) where detectors will have to manage a large data flow

- A readout architecture with data sparsification will be a new feature which could give some advantages with respect to existing MAPS implementations → flexibility in dealing with possible luminosity and background changes during the experiment lifespan, decouple modularity from readout speed

- An ambitious goal is to design a monolithic pixel sensor with similar readout functionalities as in hybrid pixels (sparsification, time stamping)

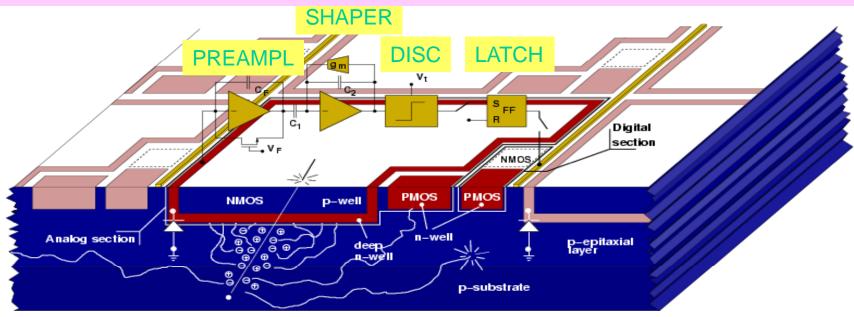

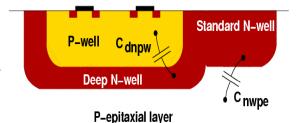

### Deep N-Well (DNW) sensor concept

New approach in CMOS MAPS design compatible with data sparsification architecture to improve the readout speed potential

Classical optimum signal processing chain for capacitive detector can be implemented at pixel level:

- Charge-to-Voltage conversion done by the charge preamplifier

- The collecting electrode (Deep N-Well) can be extended to obtain higher single pixel collected charge (the gain does NOT depend on the sensor capacitance), reducing charge loss to competitive N-wells where PMOSFETs are located

- Fill factor = DNW/total n-well area  $\sim$ 90% in the prototype test structures

- V. Re (INFN), 130 nm CMOS DNW MAPS

V. Re (INFN), 130 nm CMOS DNW MAPS

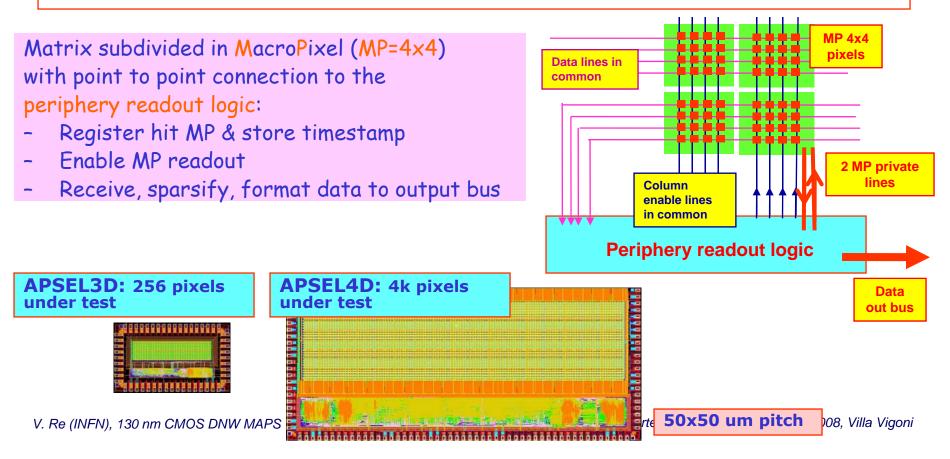

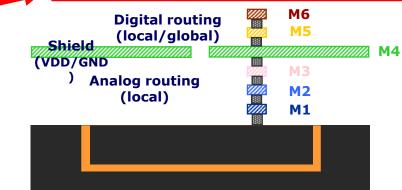

### **Fast Readout Architecture for MAPS**

- Data-driven readout architecture with sparsification and timestamp information under development.

- In the active sensor area we need to minimize:

- the logical blocks with PMOS to minimize the competitive nwell area and preserve the collection efficiency of the DNW sensor.

- digital lines for point to point connections to allow scalability of the architecture with matrix dimensions and to reduce cross talk with the sensor underneath.

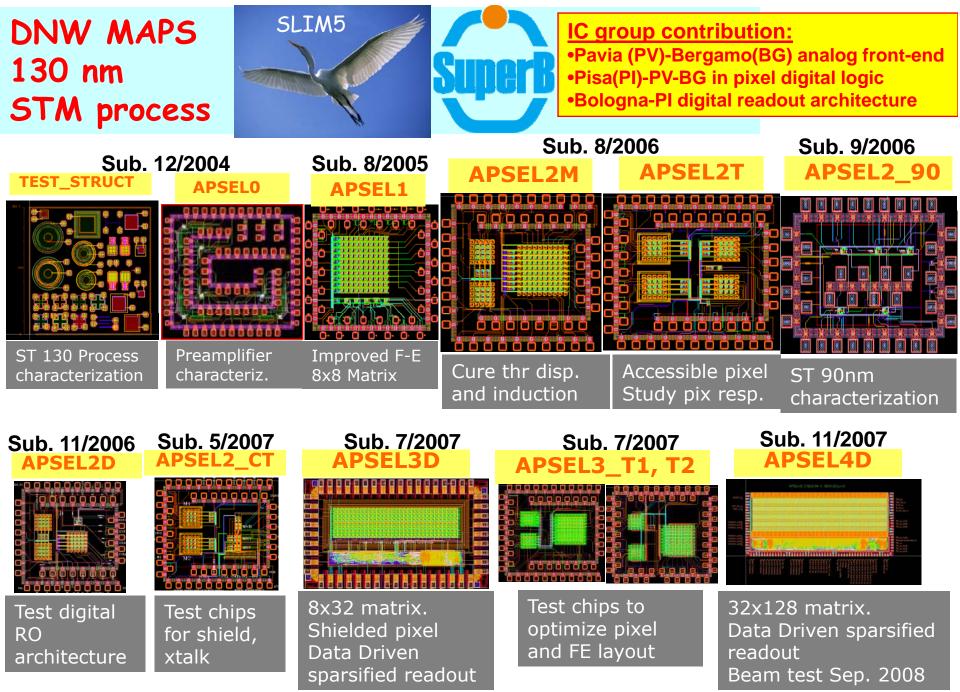

### From APSEL2 to APSEL3

#### **APSEL2** issues

- Requires aF level parasitic extraction to be modeled

- Relatively small S/N ratio (about 15)

- Especially important if pixel eff. not 100%

- Power dissipation 60 μW/pixel

- Creates significant system issues

#### APSEL3 Redesigned front-end/sensor

#### Optimize FE Noise/Power:

- Reduce sensor capacitance (from 500 fF to ~300 fF) keeping the same collecting electrode area

- reduce DNW sensor/analog FE area (DNW large C)

- Add standard NWELL area (lower C) to collecting electrode.

- New design of the analog part

- Optimize sensor geometry for charge collection efficiency using fast simulation developed:

- Locate low efficiency region inside pixel cell

- Add ad hoc "satellite" collecting electrodes

- APSEL3 Power=30 µW/pixel: <u>Perfomance</u>

**APSEL3D** Digital lines shielding

#### APSEL3 expected performance

| FE Version   | Geom | ENC<br>(PLS) | <b>ε(@5</b> σ) | S/N |

|--------------|------|--------------|----------------|-----|

| APSEL2 data  | Α    | 50 e-        | 88.7%          | 14  |

| APSEL3       | Α    | 41 e-        | 93.6%          | 16  |

| Transc.      | В    | 41 e-        | 99.4%          | 18  |

| APSEL3       | A    | 31 e-        | 98.6%          | 22  |

| Curr. Mirror | В    | 31 e-        | 99.9%          | 24  |

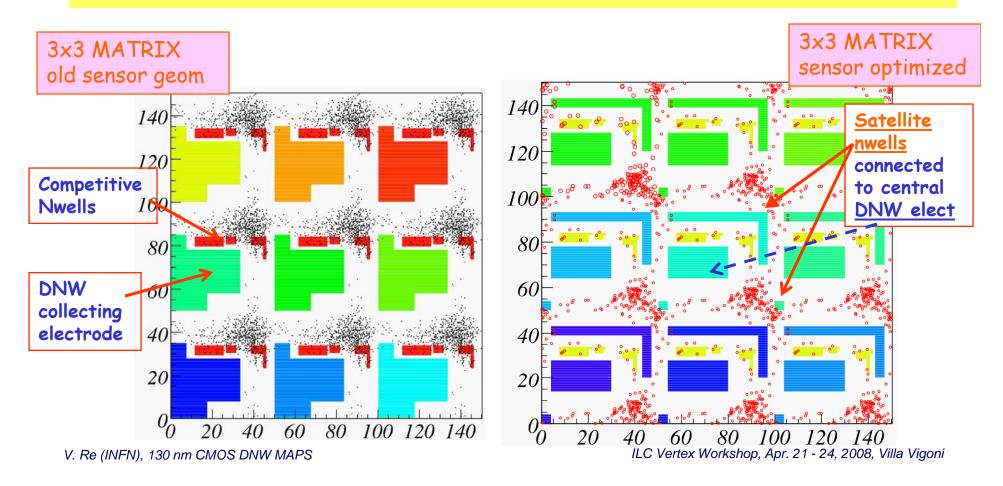

### An example of sensor optimization

- With old sensor geometry (left) Efficiency ~ 93.5% from simulation (pixel threshold @ 250 e- = 5xNoise)

- Inefficient regions shown with dots (pixel signal < 250 e-)

- Cell optimized with <u>satellite nwells</u> (right) Efficiency ~ 99.5%

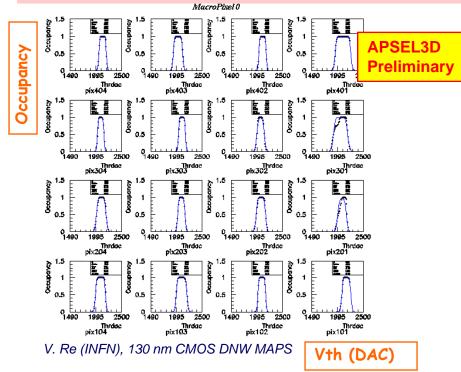

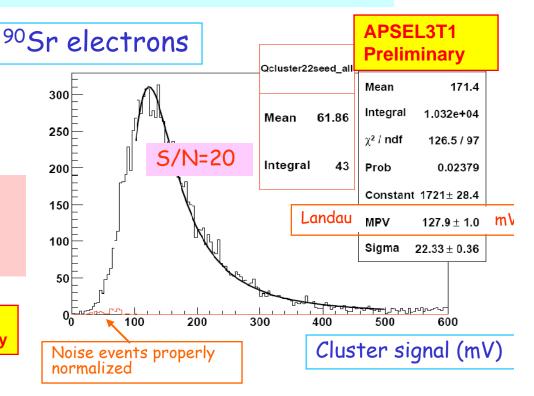

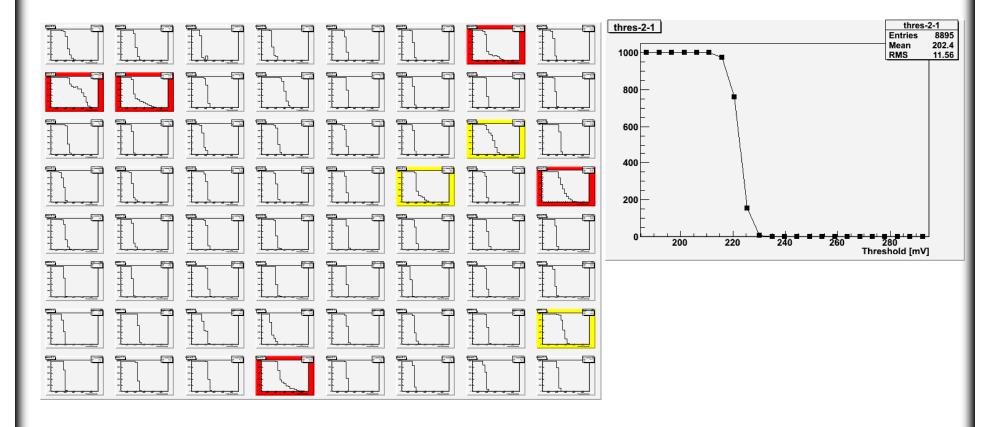

### APSEL3 chips now under test

Very preliminary!

•S/N = 20 for MIP from Sr90

•Absolute calibration of noise and gain still under way

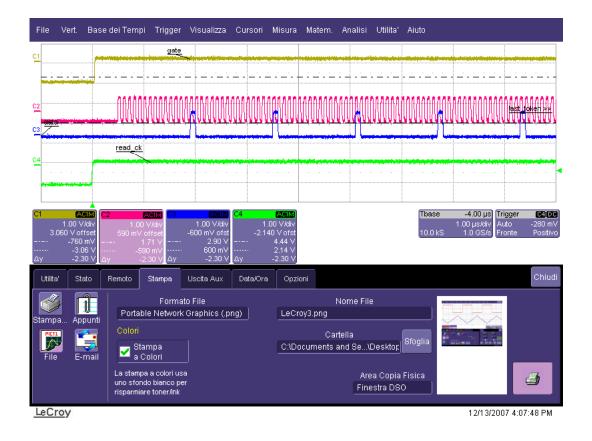

First test on APSEL3D (256 pixels): readout works as expected...with some bugs found!

Noise scan (hit rate vs discriminator threshold) to measure noise and threshold dispersion.

→Metal shield effective to reduce crosstalk effects due to digital lines crossing the pixel. This source is now at the level of the pixel noise...

→But some digital crosstalk still present in the APSEL3 series...different source? Power distribution problem?

### 130nm CMOS DNW MAPS for the ILC vertex detector

- INFN program started in 2006; design DNW MAPS according to ILC specifications

(INFN Milano, Pavia, Roma III; University of Bergamo, University of Insubria, University of Pavia)

- Same concept as in the APSEL chips, but reduced pixel pitch and power dissipation

- Digital readout architecture with in-pixel sparsification logic and time stamping, taking into account the beam structure of ILC

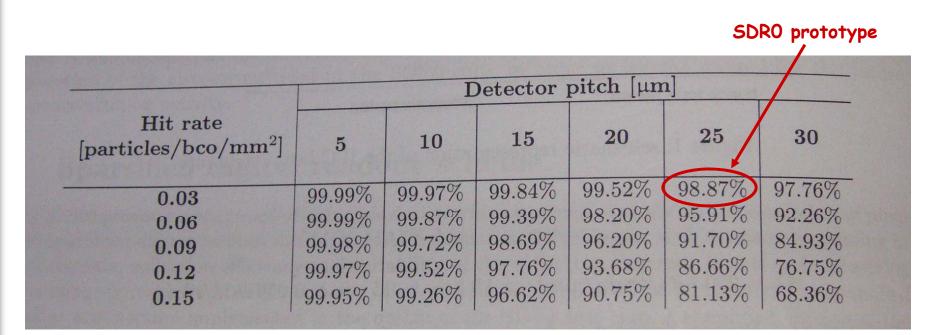

- A pipeline with a depth of one in each cell should be sufficient to record > 99% of events without ambiguity

- Data can be readout in the intertrain interval → system EMI insensitive

# Design specifications for the ILC vertex detector

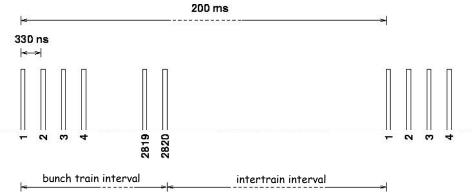

The beam structure of ILC will feature 2820 crossings in a 1 ms bunch train, with a duty-cycle of 0.5%

- assuming maximum hit occupancy 0.03 part./Xing/mm<sup>2</sup>

- if 3 pixels fire for every particle hitting  $\rightarrow$  hit rate  $\approx$  250 hits/train/mm<sup>2</sup>

- if a digital readout is adopted  $5\mu m$  resolution requires 17.3  $\mu m$  pixel pitch

- 15 µm pitch  $\rightarrow$  O<sub>c</sub>  $\approx$  0.056 hits/train  $\rightarrow$  0.0016 probability of a pixel being hit at least twice in a bunch train period

- A pipeline with a depth of one in each cell should be sufficient to record > 99% of events without ambiguity

- Data can be readout in the intertrain interval  $\rightarrow$  system EMI insensitive

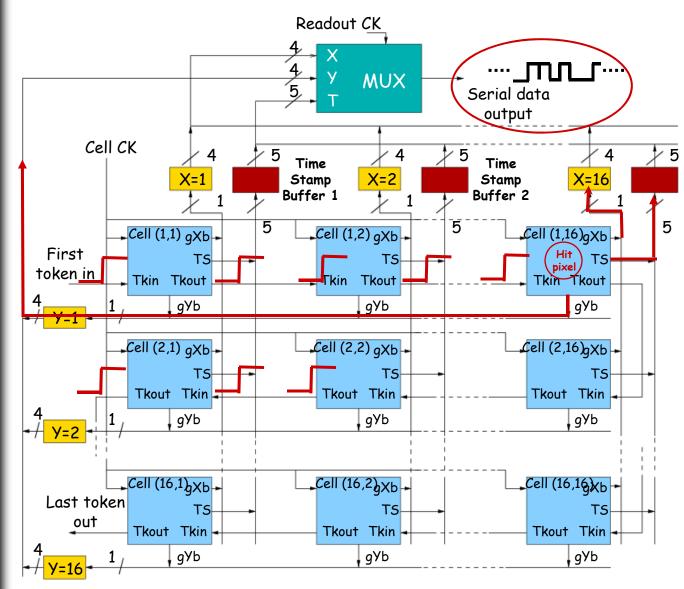

### Sparsified readout architecture

In DNW MAPS sensors for ILC, sparsification is based on a token passing readout scheme suggested by R. Yarema (FNAL)

(R. Yarema, "Fermilab Initiatives in 3D Integrated Circuits and SOI Design for HEP", *ILC VTX Workshop at Ringberg*, May 2006)

- This architecture was first implemented by Fermilab ASIC designers Jim Hoff, Tom Zimmerman and Gregory Deptuch in the VIP1 chip (3-D MIT LL technology, see Fermilab presentation on Wednesday)

- MAPS sensor operation is tailored on the structure of ILC beam

- Detection phase (corresponding to the bunch train interval)

- Readout phase (corresponding to the intertrain interval)

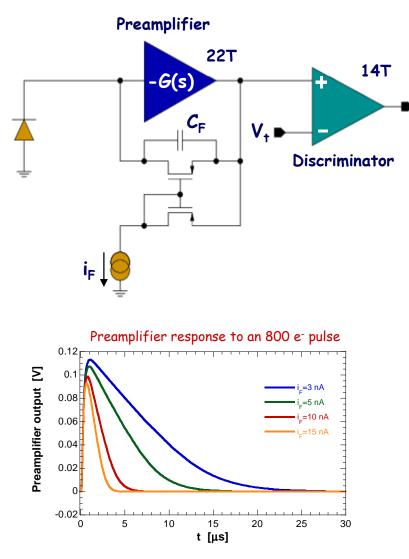

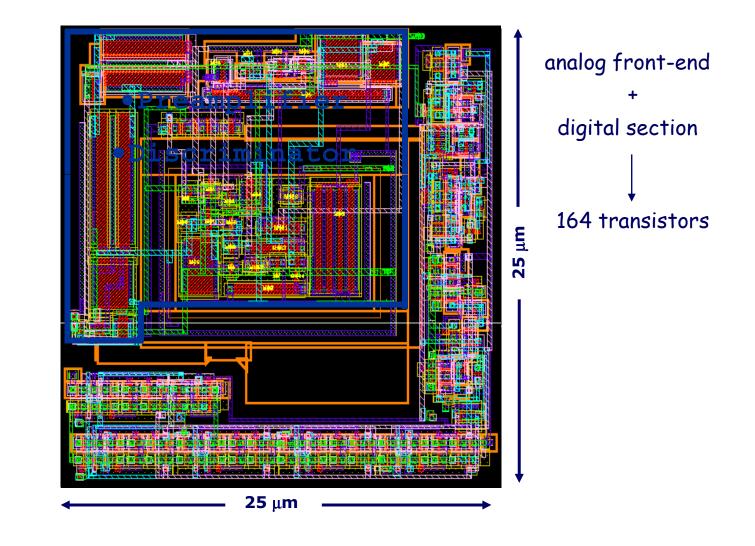

# Pixel level processor

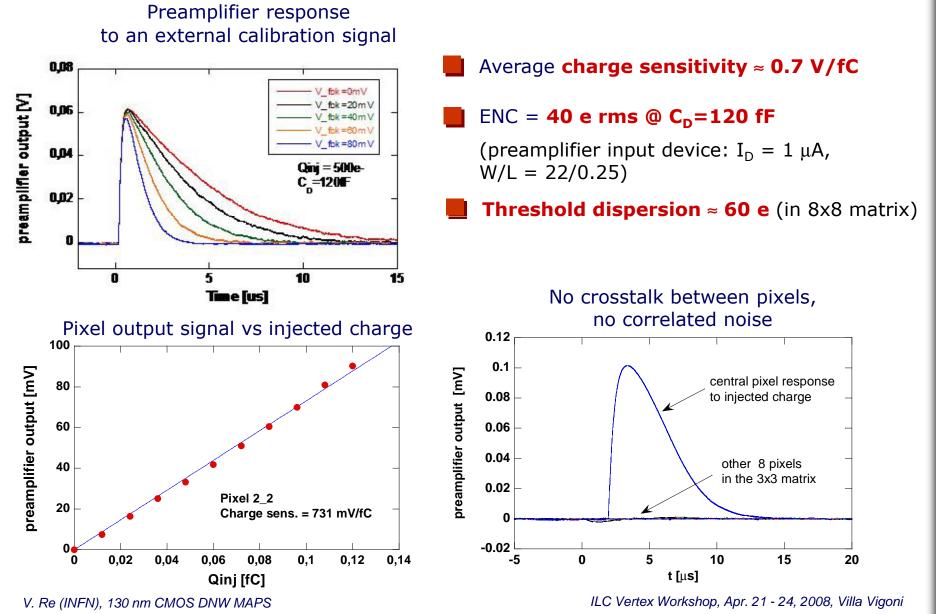

- C<sub>F</sub> obtained from the source-drain capacitance

- High frequency noise contribution has been reduced limiting the PA bandwidth

#### From simulations:

- ENC=25 e<sup>-</sup> rms@C<sub>D</sub>=100 fF

- Threshold dispersion ≈ **30 e<sup>-</sup> rms**

- Power consumption  $\approx$  **5**  $\mu$ **W**

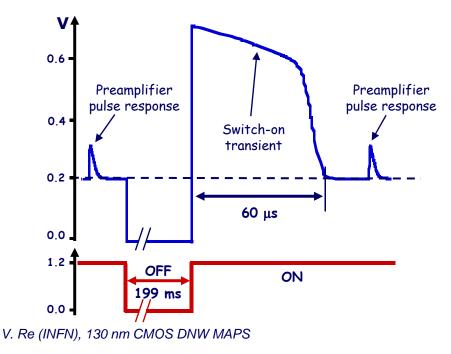

- Features power-down capabilities for power saving: the analog section cell can be switched off during the intertrain interval in order to save power (1% duty-cycle seems feasible)

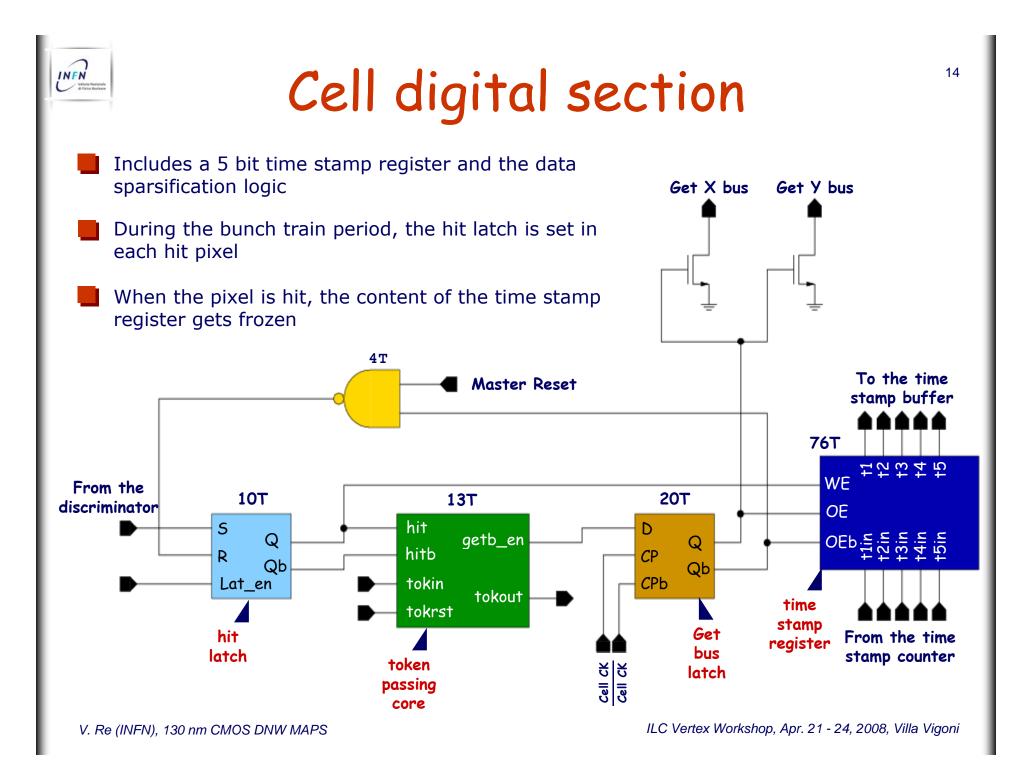

# ILC DNW elementary cell

# Digital readout scheme

Readout phase:

- token is sent

- token scans the matrix and

- gets caught by the first hit pixel

- the pixel points to the X and Y registers at the periphery and

- sends off the time stamp register content

- data are serialized and token scans ahead

The number of elements may be increased without changing the pixel logic (just larger X- and Yregisters and serializer will be required)

V. Re (INFN), 130 nm CMOS DNW MAPS

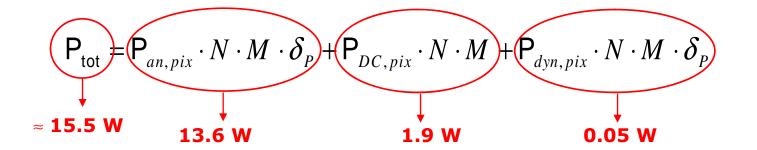

# Power dissipation analysis

- Because low material budget is necessary, there is little room for cooling system ——— very low power operation

- Analog power:  $P_{an,pix} \approx 5\mu W/pixel$  (dissipated in the analog PA)

Digital power: (power in the periphery neglected since it grows as the square root of the number of matrix cells)  $P_{DC,pix} \approx 7 \text{ nW/pixel}$  (leakage currents of the digital blocks)

$P_{dyn,pix} \approx 20 \text{ nW/pixel}$  (to charge the input capacitance of the time stamp register blocks during the detection phase)

#### Assuming:

- 170000mm<sup>2</sup> total vertex detector area (pixel pitch of 25 μm);

- 1 Mpixel chips;

- $\delta_{\text{P}}{=}0.01$  power supply duty cycle

N= number of cell per pixel M= number of chips composing the detector

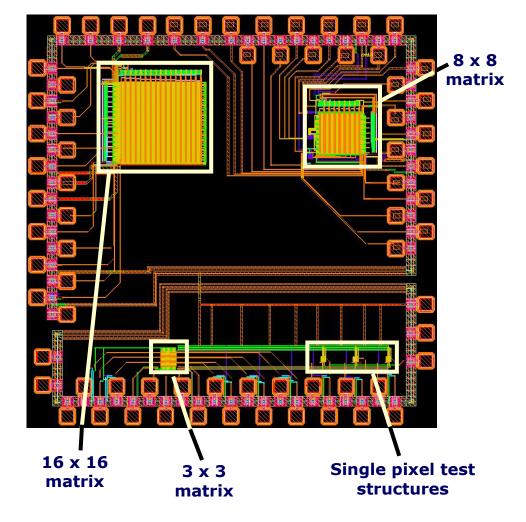

# The demonstrator chip (SDRO)

#### The chip includes:

- a 16 by 16 MAPS matrix (25 µm pitch) with digital sparsified readout

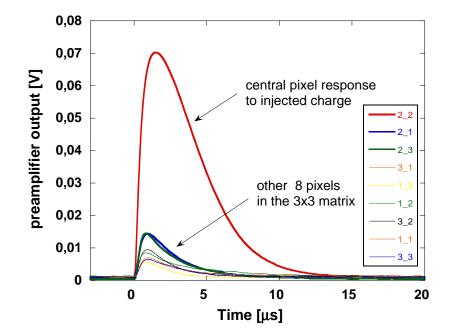

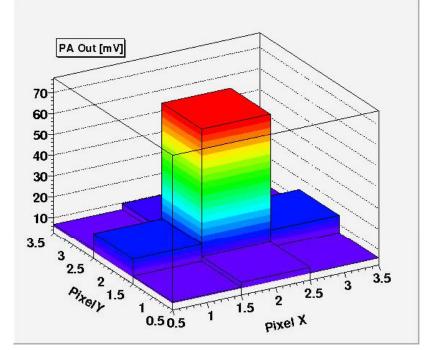

- an 8 by 8 MAPS matrix (25 µm pitch) with digital sparsified readout and selectable access to the output of the PA in each cell

- a 3 by 3 MAPS matrix (25 µm pitch) with all of the PA output accessible at the same time

- 3 standalone readout channels with different C<sub>D</sub> (detector simulating capacitance)

Delivered end of July 2007

18

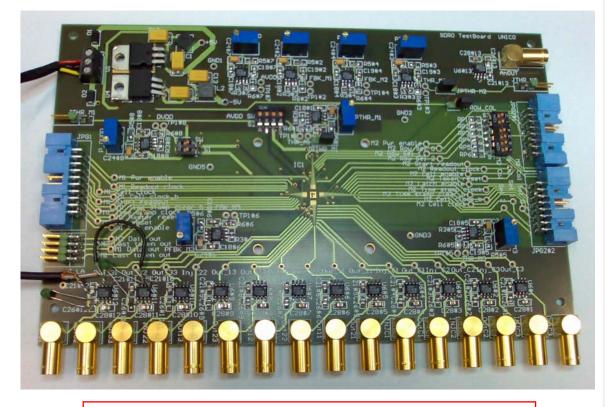

### SDRO chip and test board

#### Test board designed by Marcin Jastrzab

University of Science and Technology, Cracow (Poland) and University of Insubria, Como (Italy)

Credit: Fabio Risigo University of Insubria, Como (Italy)

19

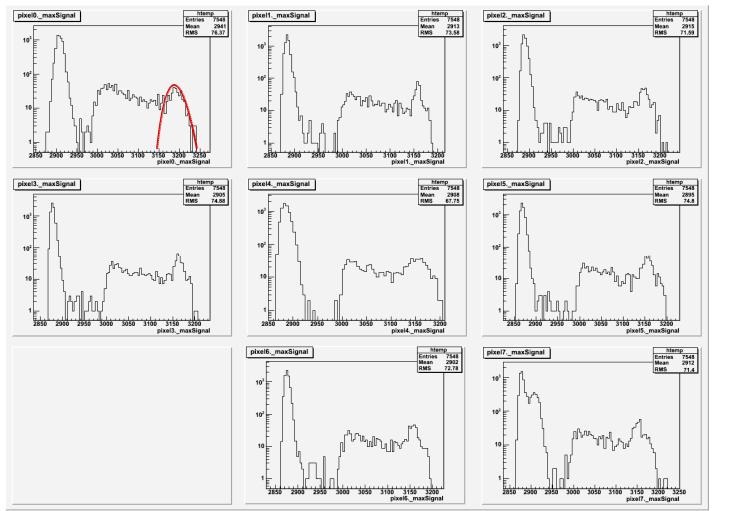

#### **3x3 matrix response to infrared laser**

#### 3x3 matrix response to 55Fe source

<sup>55</sup>Fe data confirm pixel gain calibration

V. Re (INFN), 130 nm CMOS DNW MAPS

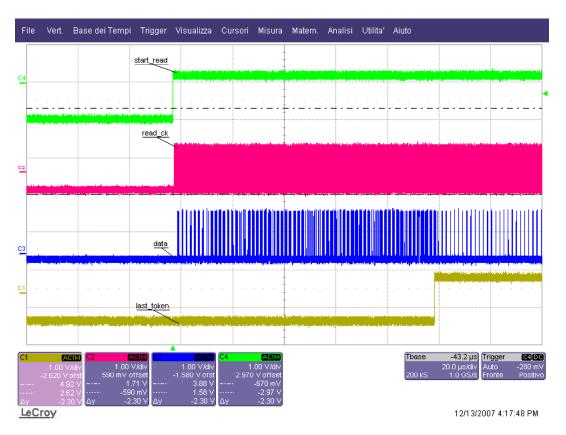

#### Digital readout: pixel address (8x8 matrix)

#### Digital readout: pixel address (8x8 matrix)

#### Digital readout: pixel address (8x8 matrix)

#### Digital readout: pixel address (8x8 matrix)

#### Digital readout: threshold scan (8x8 matrix)

#### **Digital readout: time stamp** (8x8 matrix)

|    | 🕺 No  | tepa              | d++      | - C:  | \Do    | cume    | ents      | and S  | Setti | ngs\ | Uter | nte\[      | )eskt  | op\s | ilim2 | 1 <b>5.</b> t | xt   |          |     |

|----|-------|-------------------|----------|-------|--------|---------|-----------|--------|-------|------|------|------------|--------|------|-------|---------------|------|----------|-----|

| F  | ile M | lodific           | a (      | Cerca | Vis    | ualizza | a Fo      | ormato | Lin   | guag | gio  | Config     | gurazi | one  | Macro | ) Es          | egui | Plug     | gin |

| £  | a 🚽   |                   |          | -     | 0      | K       | h         |        | Э     | C    | 箭    | <b>h</b> 2 |        | R    |       |               |      | <b>n</b> | 1   |

|    |       |                   |          | -     |        |         |           |        |       |      |      | -          |        |      |       | _             |      | ,        |     |

|    | e si  | im215             | .txt     | Dat   | a_l    | bit     |           |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  | 59    |                   | 0        |       | 0      | -       | sync      | chro   |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 93 <del>(</del> ) |          |       | 1      | -       | sync      | chro   |       |      |      |            |        |      |       |               |      |          |     |

| Ш  | 59    | 94                | 0        |       | 0      | -       | sync      | chro   |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 95                | 0        |       | 1      | 3       | x0        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 96                | 0        |       | 1      |         | x1        |        | x     | =7   |      |            |        |      |       |               |      |          |     |

| Ш  |       | 97                | 0        |       | 1      |         | х2        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 98                | 0        |       | 0      |         | х3        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 99                | 0        |       | 0      |         | γO        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 00                | 0        |       | 1      |         | y1        |        | ~     | =6   |      |            |        |      |       |               |      |          |     |

| Ш  |       | 01                | 0        |       | 1      |         | y2        |        |       | -0   |      |            |        |      |       |               |      |          |     |

| Ш  |       | )2                | 0        |       | 0      |         | γЗ        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 03                | 0        |       | 1      |         | ts0       |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       |                   | 0        |       | 1      |         | ts1       |        | _     |      |      |            |        |      |       |               |      |          |     |

| Ш  |       |                   | 0        |       | 0      |         | ts2       |        |       | S=2  |      |            |        |      |       |               |      |          |     |

| Ш  |       | )6                | 0        |       | 0      |         | ts3       |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | )7                | 0        | -     | 0      |         | ts4       |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 8                 | 0        |       | 0      |         | -         | chro   |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 09 🔿              |          |       | 1      |         | -         | chro   |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | LO                | 0        | _     | 0      |         | _         | chro   |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 11                | 0        |       | 1      |         | x0        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       |                   | 0        |       | 0      |         | x1        |        | )     | (=1  |      |            |        |      |       |               |      |          |     |

| Ш  |       |                   | þ        |       | 0      |         | x2        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 14                | 0        |       | 0      |         | х3        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 15                | 0        |       | 1      |         | γ0        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 16<br>17          | 0        |       | 1<br>1 |         | y1        |        | 1     | r=7  |      |            |        |      |       |               |      |          |     |

| Ш  |       | 18                | 0        |       | 0      |         | y2        |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 19                | 0        | - 2   | 0      |         | y3<br>ts0 |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 20                | 0        |       | 0      |         | ts1       |        |       |      |      |            |        |      |       |               |      |          |     |

| Ш  |       | 21                | 0        |       |        |         | ts2       |        | т     | S=0  |      |            |        |      |       |               |      |          |     |

| Ш  | 62    |                   | 0        |       | 0      |         | ts3       |        |       |      | ·    |            |        |      |       |               |      |          |     |

|    |       | 23                | 0        |       | 0      |         | ts4       |        |       |      |      |            |        |      |       |               |      |          |     |

|    |       | 24                | 0        |       | 0      |         |           | chro   |       |      |      |            |        |      |       |               |      |          |     |

|    |       | 25 🔿              |          |       | 1      |         | -         | chro   |       |      |      |            |        |      |       |               |      |          |     |

|    |       | 26<br>26          | 0        |       | 0      |         | _         | chro   |       |      |      |            |        |      |       |               |      |          |     |

|    |       | 27                | 0        |       | 0      |         | 2 y 110   |        |       |      |      |            |        |      |       |               |      |          |     |

|    |       | 28                | 0        |       | 1      |         |           |        |       |      |      |            |        |      |       |               |      |          |     |

| 12 | - 02  |                   | <u> </u> |       | -      |         |           |        |       |      |      |            |        |      |       |               |      |          |     |

| 194  |            |         |     |        |   |              | <i>a</i>    |          |     |        |        |     |       |    |      |          |     |    |

|------|------------|---------|-----|--------|---|--------------|-------------|----------|-----|--------|--------|-----|-------|----|------|----------|-----|----|

| _    |            |         |     |        |   | nts and      |             | <u> </u> |     |        |        |     |       |    |      |          |     |    |

| File | Mo         |         |     | Visu   |   | Formate      | o Lin       | iguag    | gio |        | gurazi | one | Macro | Es | egui | Plug     | ins | ?  |

| -    | Ð          |         | È 写 | 0      | K | ЪЪ.          | 9           | C.       | ñ   | ь<br>8 |        | R   |       |    |      | <b>¶</b> | 1   | 43 |

|      | l elim     | 215.txt |     |        |   |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 1          |         | Dat |        |   |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 640        |         |     | 0      |   | ynchro       |             |          |     |        |        |     |       |    |      |          |     |    |

|      |            | . 🔿 0   |     | 1      |   | ynchro       |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 642        |         | _   | 0      |   | ynchro<br>-  |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 643        |         |     | 1      | х | -            |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 644        |         |     | 1      | х |              | <b>х</b> =з |          |     |        |        |     |       |    |      |          |     |    |

|      | 645        | -       |     | 0      | x |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 646        |         |     | 0      | x |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 647        |         |     | 1      | У |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 648        |         |     | 1      | Y |              | Y=7         |          |     |        |        |     |       |    |      |          |     |    |

|      | 649        |         |     | 1      | Y |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 650        |         |     | 0      | Y |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 651        |         |     | 0      |   | з0           |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 652        |         |     | 0      |   | 31           | TC-         | ~        |     |        |        |     |       |    |      |          |     |    |

|      | 653        |         |     | 0      |   |              | TS=         | U        |     |        |        |     |       |    |      |          |     |    |

|      | 654        |         |     | 0      |   | <b>3</b> 3   |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 655        |         |     | 0      |   | s4           |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 656        |         |     | 0      |   | ynchro       |             |          |     |        |        |     |       |    |      |          |     |    |

|      |            | 00      |     | 1      |   | ynchro       |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 658        |         |     | 0      |   | ynchro       |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 659        |         |     | 0      | х |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 660        |         |     | 0      | х |              | <b>x</b> =  | 4        |     |        |        |     |       |    |      |          |     |    |

|      | 661        |         |     | 1      | x |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 662        |         |     | 0      | x |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 663        |         |     | 1      | У |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 664        |         |     | 1      | У |              | <b>Y</b> =  | 7        |     |        |        |     |       |    |      |          |     |    |

|      | 665        |         |     | 1      | Y |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 666        |         |     | 0      | У |              |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 667        |         |     | 1      |   | s0<br>-1     |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 668        |         |     | 0      |   | s1<br>- 2    | TS=         | .1.4     |     |        |        |     |       |    |      |          |     |    |

|      | 669        |         |     | 0      |   | s2<br>~ 2    | 15=         | 14       |     |        |        |     |       |    |      |          |     |    |

|      | 670        |         |     | 1<br>0 |   | s3<br>-4     |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 671<br>672 |         | L   | 0      |   | s4<br>vnchro |             |          |     |        |        |     |       |    |      |          |     |    |

|      |            |         |     | 1      |   | ynchro       |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 674        |         |     | 0      |   | ynchro       |             |          |     |        |        |     |       |    |      |          |     |    |

|      | 075        | . 0     |     | U      | 3 | ynchro       |             |          |     |        |        |     |       |    |      |          |     |    |

Normal text file

V. Re (INFN), 130 nm CMOS DNW MAPS

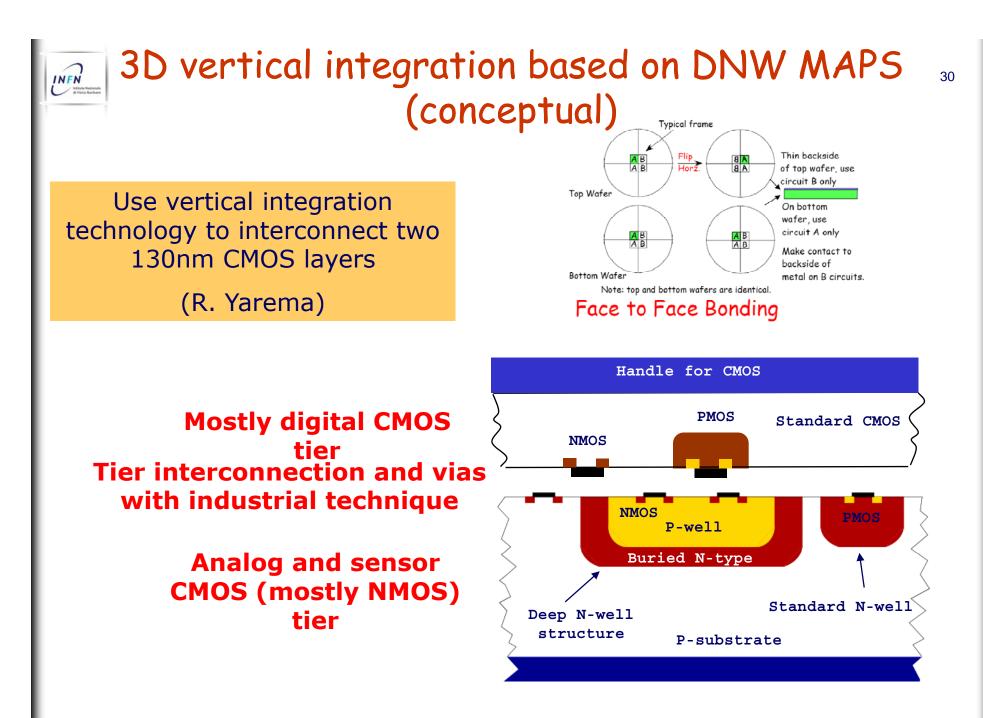

### Explore more advanced technological solutions: Vertical Integration

Vertical integration between two layers of 130nm CMOS chips.

The first layer may include a MAPS device with analog readout, and the second layer the digital readout circuits

(from an idea of Ray Yarema)

- Overcome limitations typically associated to "conventional" and DNW CMOS MAPS:

- Reduced pixel pitch

- 100 % fill factor (few or no PMOS in the sensor layer)

- Better S/N vs power dissipation performance (smaller sensor capacitance)

- Reduction of possible analog-to-digital interferences

- Increased pixel functionalities (multiple hit handling, analog information)

- INFN R&D program aims at developing 130nm CMOS MAPS with sparsified readout and time stamping for the ILC vertex detector

- DNW MAPS structures have been fabricated in a 130 nm, triple well CMOS technology; for the first time ever we have MAPS with pixel-level sparsification and time stamping

- Several issues have to be addressed to meet ILC specifications (pixel pitch, detection efficiency)

Binary readout: ILC VTX demands a pixel pitch < 20  $\mu$ m.

- Plans for the future:

- Tests of SDR0 structures with <sup>90</sup>Sr and in a beam

- Design of a 256 x 256 matrix for beam test (2008)

- Evaluation of microelectronic technologies with higher integration density (90 nm CMOS, 3D Vertical Integration)

### Acknowledgments

I want to thank the ILC pixel R&D group at Fermilab for the very useful discussions that helped us to choose the SDR0 chip architecture.

### Backup slides

### Design specifications for the ILC vertex detector

Detection efficiency for different sensor pitch and hit rate values

# Power cycling simulations

Power cycling can be used to reduce average dissipated power by switching the chip off when no events are expected

#### Example:

✓ILC bunch structure: ~330 ns spacing, ~3000 bunches, 5Hz pulse

The analog section in the elementary cell can be switched off during the intertrain interval in order to save power (analog power is supposed to be predominant over digital)

Based on circuit simulations, power cycling with at least 1% duty-cycle seems feasible