ILC Vertex Workshop 21-24 April 2008 Villa Vigoni

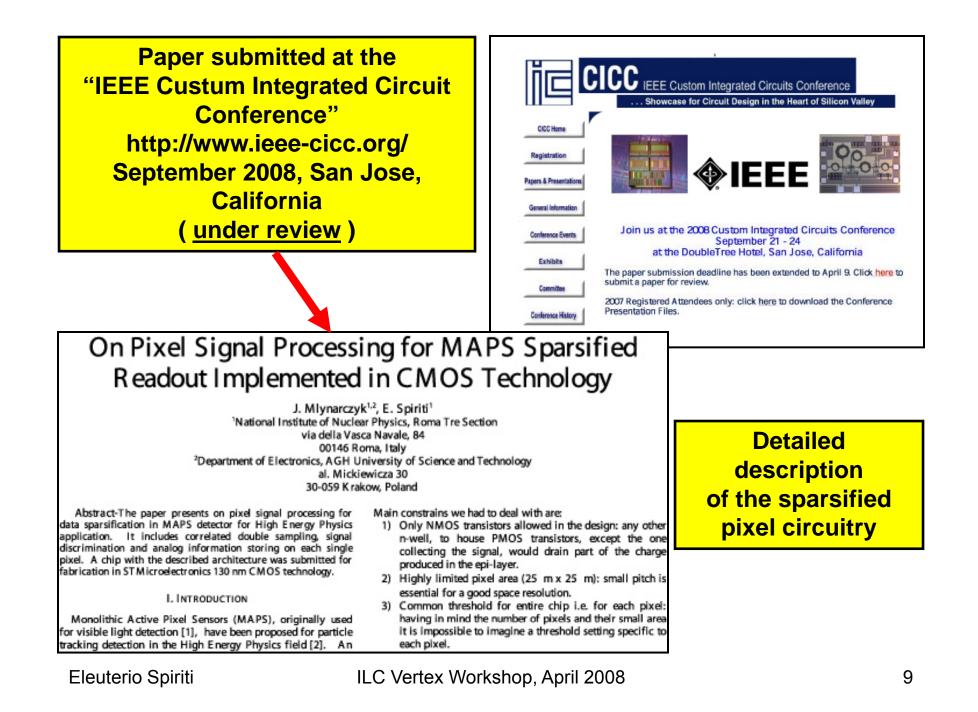

**On pixel sparsification architecture in 130nm STM technology**

Eleuterio Spiriti (INFN RomaTre)

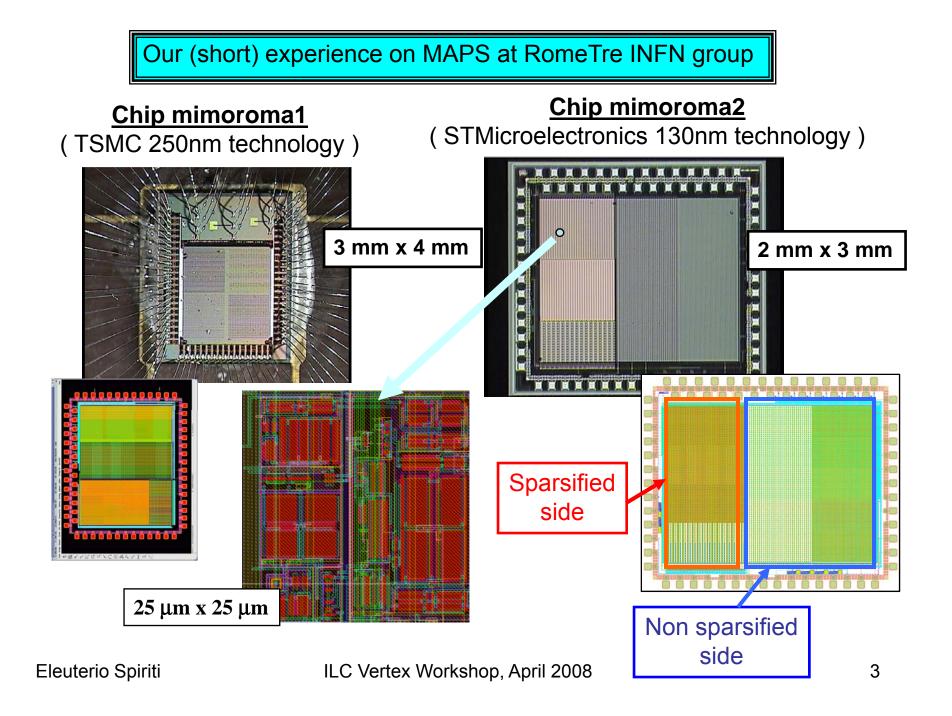

- 1. Our (RomeTre group) experience on MAPS

- Mimoroma1 chip: brief description and some results

- 2. The Mimoroma2 chip

- Main goals and constrains

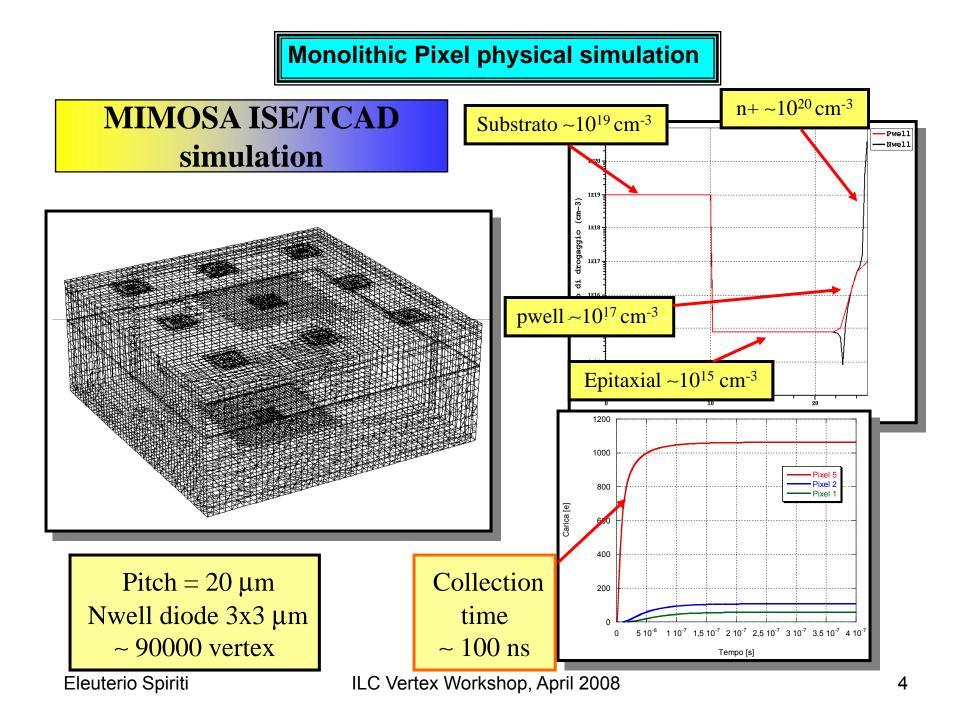

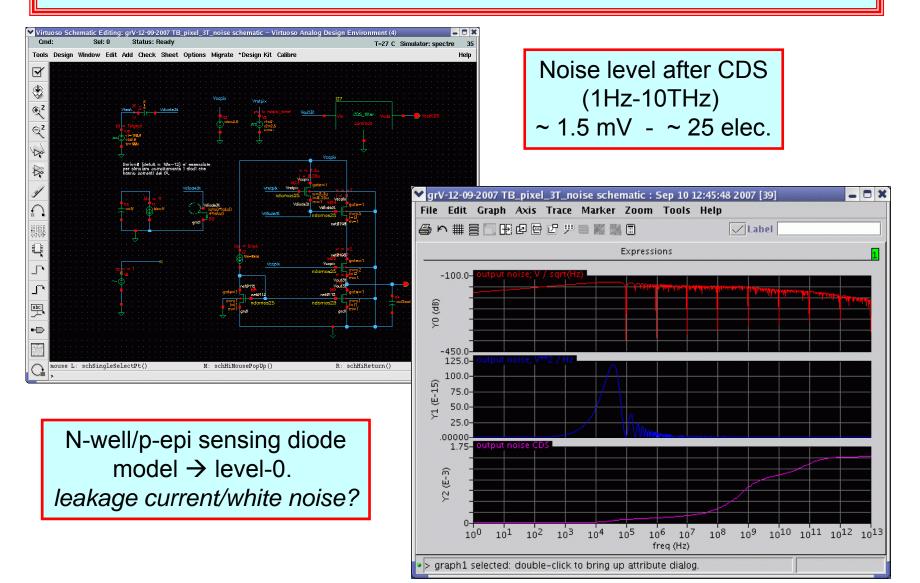

- Pixel noise simulation

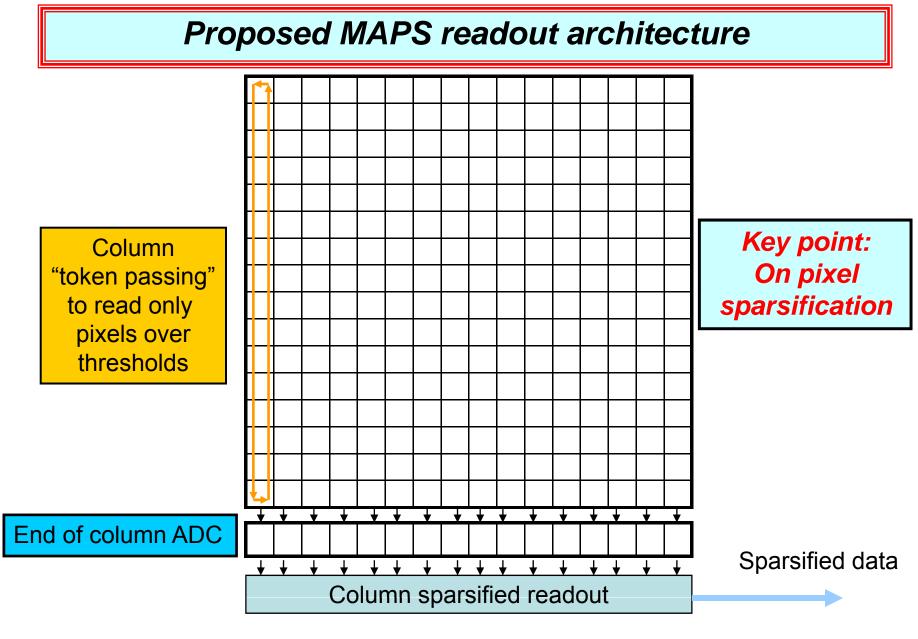

- Readout architecture

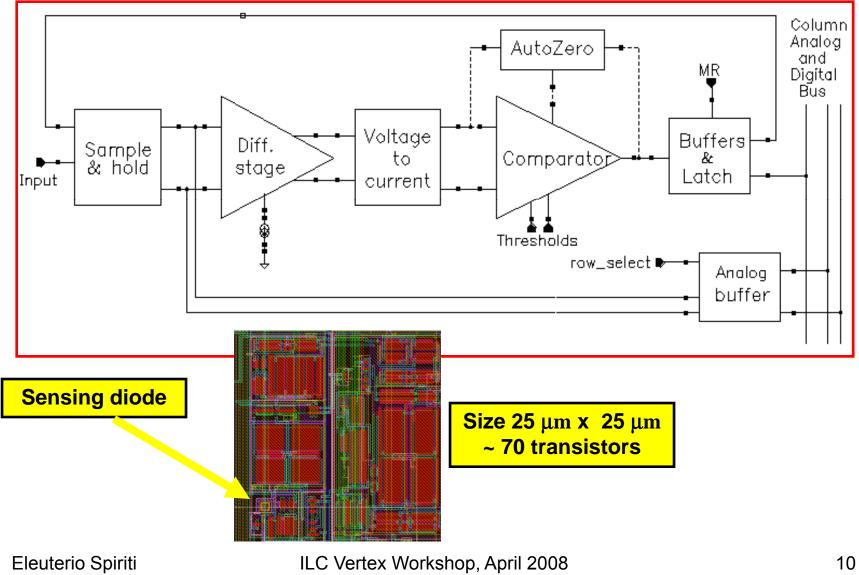

- Pixel architecture

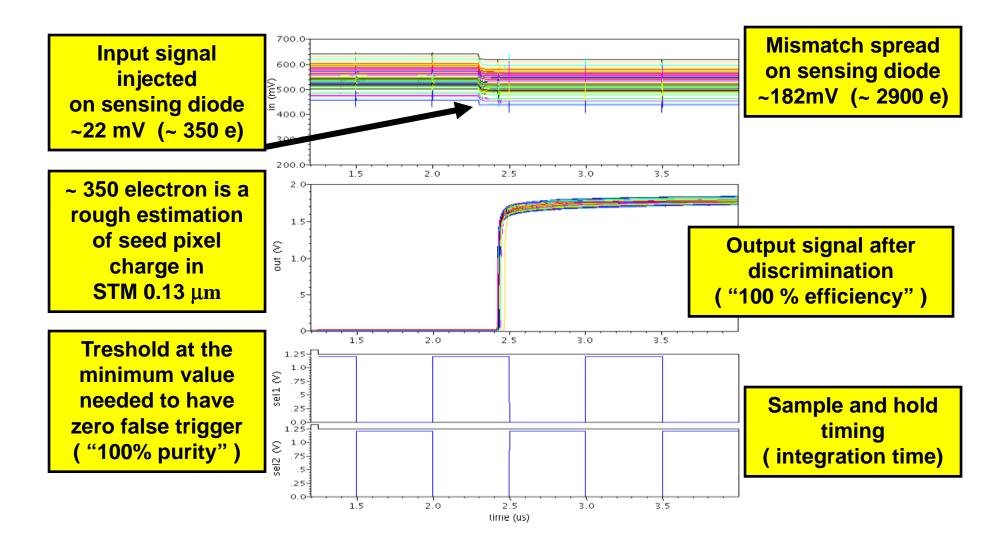

- Simulation of sparsified pixel

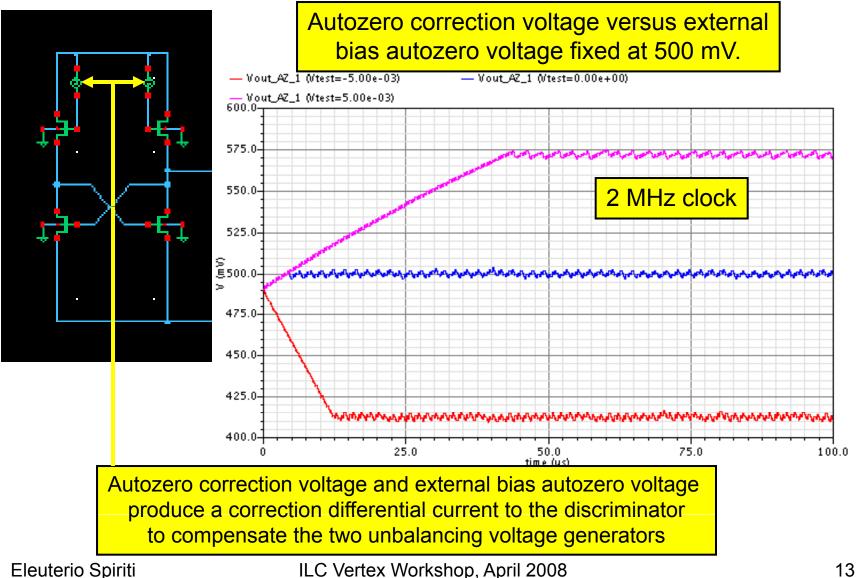

- Autozero simulation

- **3.** Conclusions

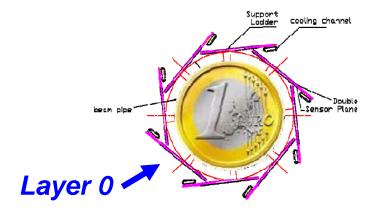

#### Monolithic pixels in vertex detector for future accelerator

|                        | Super-B                | ILC                   |

|------------------------|------------------------|-----------------------|

| Spatial resolution     | 10 µm                  | 2.5 µm                |

| Multiple<br>scattering | 0.05% * X <sub>0</sub> | 0.1% * X <sub>0</sub> |

| Duty cycle             | 100 %                  | 0.5 %                 |

| Occupancy              | ~1%                    | ~1%                   |

Eleuterio Spiriti

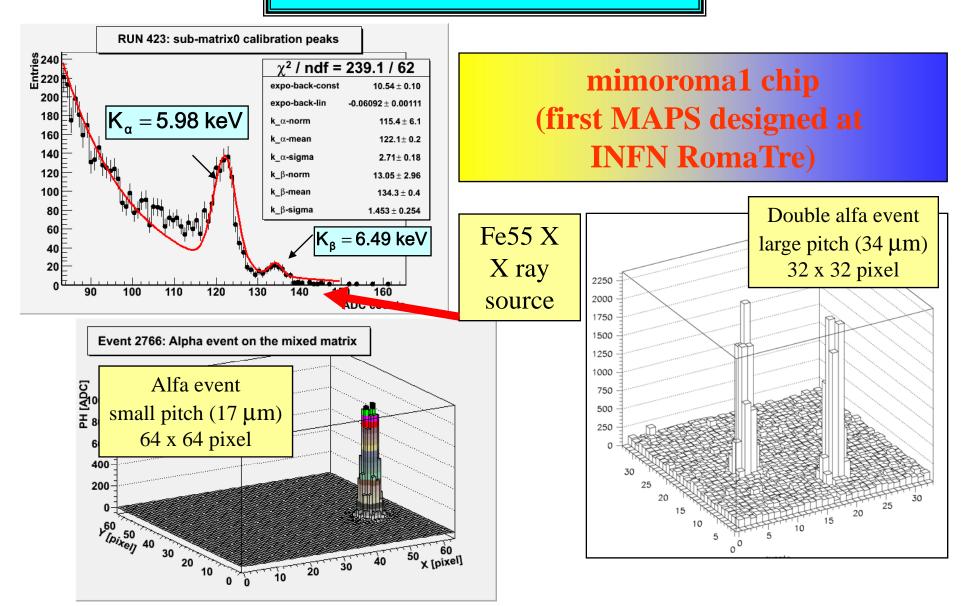

#### Mimoroma1 chip measurement results

Eleuterio Spiriti

### Mimoroma2 chip: main goals and constrains

- Characterization of the signal (epitaxial thickness and quality) level provided by the STM 0.13  $\mu m$  technology

- Implementation of an on-pixel sparsification architecture

- digital and analog output

- 1. Only NMOS transistors: no competing n-wells

- 2. Small available area (pitch 20-25  $\mu$ m)

- 3. Common threshold for all pixels in a chip

- 4. Threshold voltage and curren mismatch in submicron CMOS

- 5. Noise:

- **Temporal noise**

- **White and 1/f noise**

- **Charge injection**

- **Digital to analog cross-talk**

Technology characterization from the signal collection point of view Different parameters for the non sparsified part of the chip

Ten different matrix implemented

✓ Five 32x16 pixels arrays with 20x20 µm size

✓ Five 64x32 pixels arrays with 10x10 µm size

| Parameter          | Value 1     | Value 2         |

|--------------------|-------------|-----------------|

| Pixel structure    | 3T          | SB              |

| Pitch              | 20 µm       | 10 µm           |

| Diode dimension    | 1 μm x 1 μm | 1.5 μm x 1.5 μm |

| SF transistor size | Small gain  | Large gain      |

| Power supply       | 2.5 V       | 1.2 V           |

## **Pixel architecture**

## Pixel 3T noise simulation

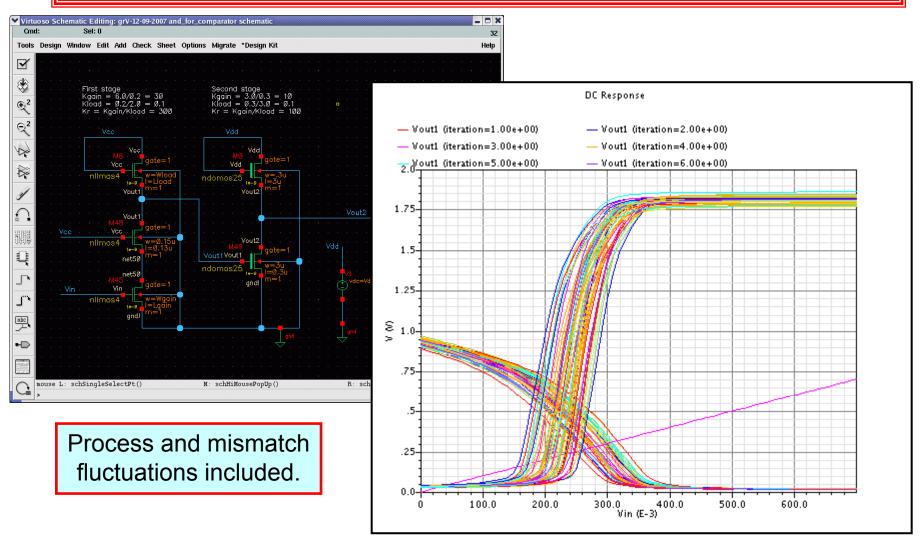

#### NAND logic Montecarlo simulation. ( used inside the Pixel )

Eleuterio Spiriti

#### Autozero correction voltage simulation.

#### Sparsification logic Montecarlo simulation (100 runs)

Eleuterio Spiriti

# Conclusions

- Design effort was driven by the highly demanding performances required by the vertex detectors for future colliders

- The proposed architecture for the on-line data sparsification was designed and simulated

- Simulation results of the on-pixel signal processing seems promising, considering that this will be the first run in ST 0.13um technology. We had many unknows and we tried to be prepared for the worst case

- Large room for improvements expected after feedback from measurements.

- > The autozero correction technique could be a key point.

- Chip submitted through CMP Service November 2007, testing will start next week