# **Tracking and Vertexing Summary**

#### Suyong Choi SKKU, Korea

# **Vertex Detector**

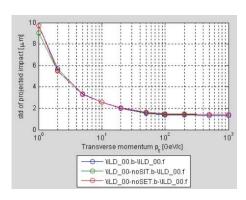

# Physics Requirements for LC Vertex Detector

10

$$\sigma_{IP} = a \oplus \frac{b}{p \sin^{3/2} \theta}$$

|         | a (μm) | b (μm GeV) |

|---------|--------|------------|

| LEP     | 25     | 70         |

| SLD     | 8      | 33         |

| LHC     | 12     | 70         |

| RHIC II | 14     | 12         |

| ILC     | 5      | 10         |

| CWS08 3 |        |            |

# Vertex Requirements for ILC

- Geometry

- Coverage  $|\cos \theta| < 0.96$

- Radii 1.5 cm ~ 6.0 cm

- Fine pixels

- 20  $\mu m$  x 20  $\mu m$

- Thin Detector

- 0.1%  $X_0$  per layer

- Sparsified readouts

- 1 Gpixels

- zero suppression and/or time stamping

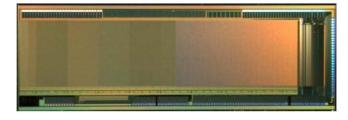

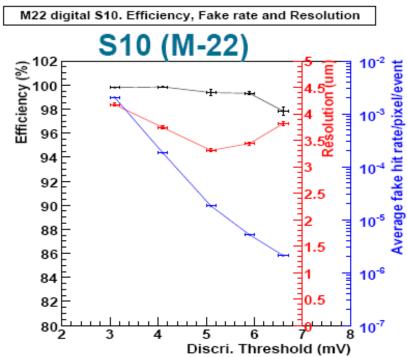

#### **MIMOSA**

M. Winter

- On pixel integrated CDS with discriminator

- CMOS

- Mimosa-22

- 128 col x 576 pixel, 18.4  $\mu$ m pitch

- 10 k/s readout

- 99.9% det. eff

- S/N: 16 ~ 20

- ENC: 11e ~ 14e

- 3.5  $\mu$ m pos. resolution

- Irradiation test

- 300kRad ENC:  $10e \rightarrow 15e$

- ➔ Performance requirements met

#### **MIMOSA**

- Add zero sup circuit for 2009 EUDET beam tests

1152 columns

- A variant will be used for STAR VXD

- Being fabricated

- Physics in 2010

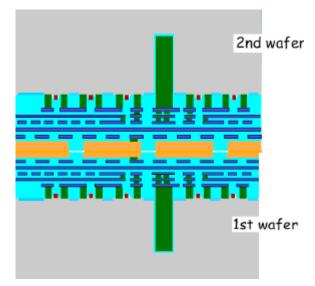

- 3-D in collaboration with INFN and FNAL

- 130 nm 2-Tiered Chartered-Tezzaron process

M. Winter

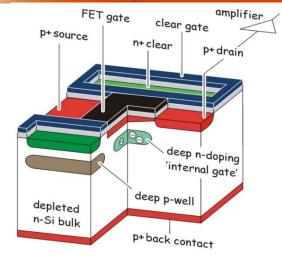

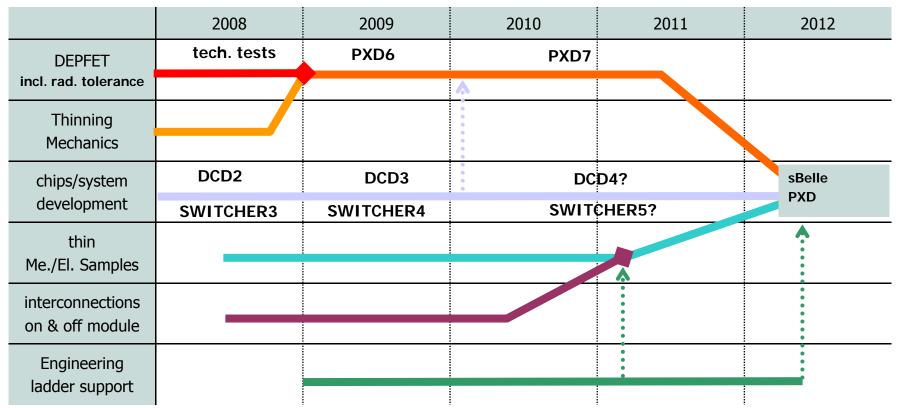

#### DEPFET

C. Pardo L. Andricek

- Charge drifts to FET gate  $\rightarrow$  current flow

- $\checkmark\,$  Prototype System with DEPFETs (450 $\mu m$ ), CURO and Switcher

- ✓ many test beams @ CERN and Desy:

- ✓ S/N≈140 @ 450  $\mu$ m ←→ goal S/N ≈ 20-40 @ 50  $\mu$ m

- ✓ sample-clear-sample 320 ns  $\leftarrow$  → goal 50 ns

- ✓ s.p. res. with 24 µm pixels: 1.3 µm @ 450 µm ←→ goal ≈ 3.4 µm @ 50 µm

- ✓ Thinning technology established, thickness can be adjusted to the needs of the experiment (~20  $\mu$ m ... ~100  $\mu$ m), design goal 0.11 % X<sub>0</sub>

- $\checkmark\,$  radiation tolerance tested with single pixel structures up to 1 Mrad and  ${\sim}10^{12}~n_{eq}/cm^2$

C. Pardo L. Andricek

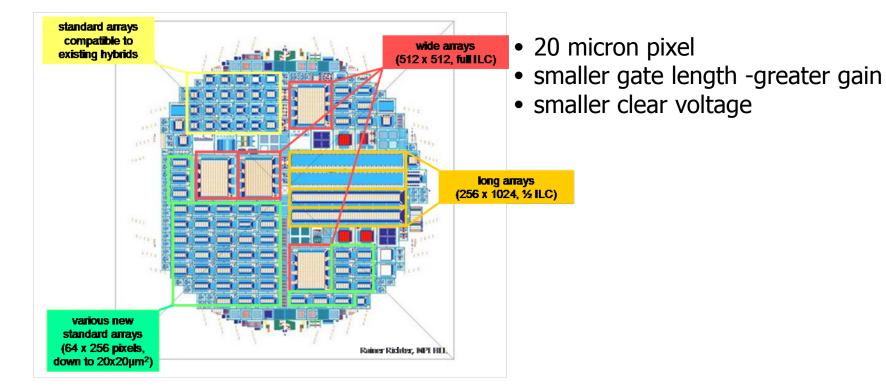

• New PXD5 DEPFET

New quieter readout – DCD2

– 100e- ENC

- PXD6 will be first thinned DEPFET

- Work on SuperBelle detector will be beneficial

C. Pardo

L. Andricek

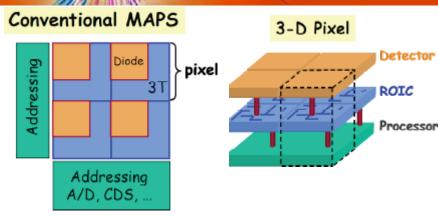

# **Monolithic Active Pixel Sensors – MAPS**

- On-chip sparsification and time stamping

- Deep N-Well MAPS

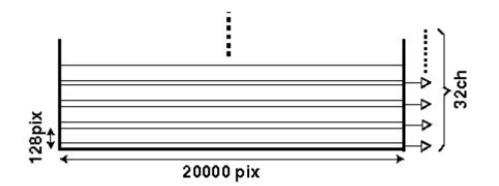

- APSEL4D -32x128

- 50  $\mu$ m pitch move to smaller process

- Beam test 90% efficiency change layout to improve efficiency

- should implement multiple pixel hit

- Mimoroma2

- Analog readout

- threshold scan works as simulation

- Going to 3D will help

| V. | Re |

|----|----|

| V. | Re |

|    |    |

E. Spiriti

# Continuous Acquisition Pixel Detectors (CAP)

- SuperBelle application

- MAPS with in-pixel signal storage

- after charge to V conv.

- CAP7

- 60k pixels 5 mm<sup>2</sup>

- pixel: 35 x 50  $\mu$ m<sup>2</sup>

- 0.2 micron OKI on SOI

- Chip expected this month

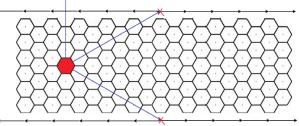

- New ideas for Hexagonal routing of signals

- Reduced fakes, improved resolution, faster transfers

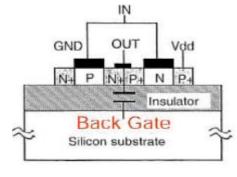

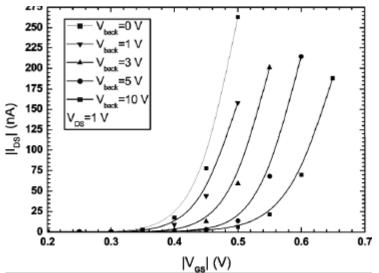

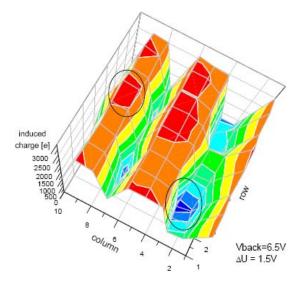

## **SOI – Silicon-on-Insulator**

M. Trimpl

- Backgate effect

- can be mitigated but not eliminated

- Cross talk

- No Cadence tools to analyze this

# **Chronopixel**

- Monolithic CMOS

- In-pixel sparsification

- Single bunch time stamp

- 4 hits/pixel/train

- 80 chips fabricated

- 80x80 pixel, 50 micron pitch

- Status

- Test equipment ready in Jan. 2009

- Simulation of expected performance

- Design deep p-well device (improves eff), looking for manufacturer

- move to 45 nm process

N. Sinev

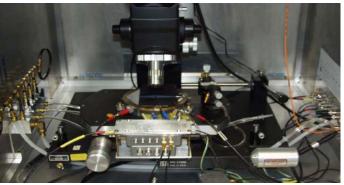

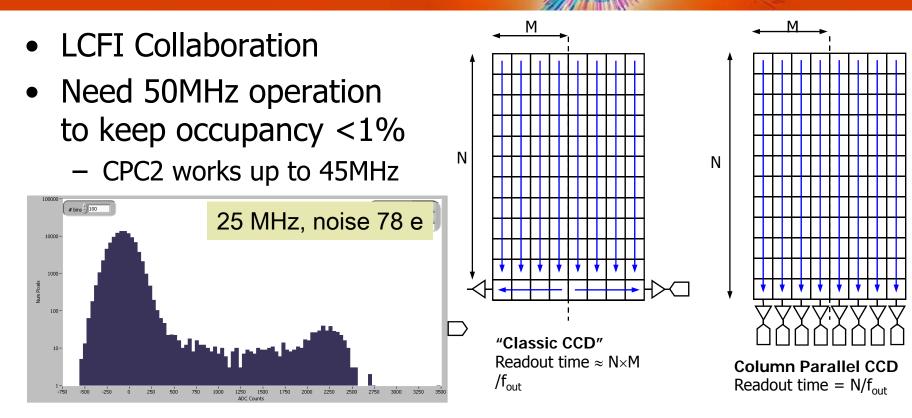

# **Column Parallel CCD (CPCCD)**

A. Nomerotski

• Lower capacitance variant successfully operating

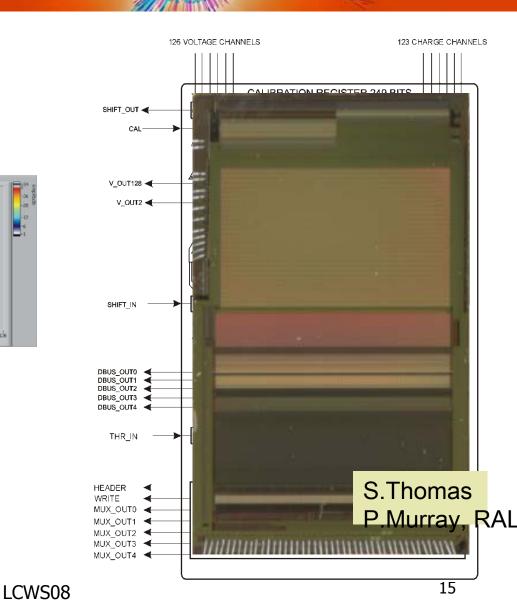

# **CPCCD Readout – CPR2A**

- Voltage and Charge

- 5 bit Flash ADC

- Cluster finding

- Sparsified readout

- Performs up to specs

🔜 A. Nomerotski

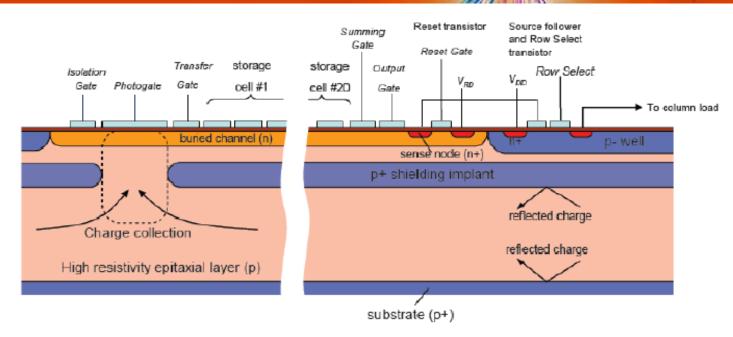

# In Situ Image Sensor (ISI

- Charge collected in "photogate"

- Charge transferred to 20 CCDs in the pixel

- Read out during 200ms quiet time

- 1MHz operation

- CMOS and CCD technology

A. Nomerotski

#### ISIS

#### 🚤 A. Nomerotski

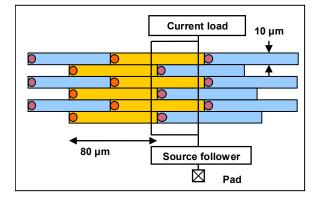

- ISIS2

- Pixels 80 x 10  $\mu m^2$

- Imaging pixels 40 x 20  $\mu m^2$

- Total area 1 cm<sup>2</sup>

- p-well

- just delivered

- Future of UK Silicon project

- New proposal SPIDER

(Silicon Pixel DEtector R&D)

- Continue ISIS program

- Develop MAPS based on 4T process

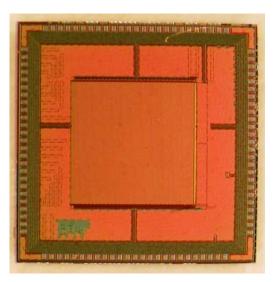

# Fine Pixel CCD (FPCCD)

- Integrate for 1 train, readout in the quiet time

- To keep the occupancy below %1 / train reduce pixel size

- goal: 5 micron pitch

- fully depleted epitaxial layer 15, 24 micron thickness

- moderate clock speed, small power dissipation

- goal: signal level <2000e, noise <50e

Y. Sugimoto

Y. Takubo

#### **FPCCD**

#### Y. Sugimoto Y. Takubo

- First prototype delivered by HPK

- 512 x 512, 12 micron pitch

- 50 micron wafer thickness, epitaxial layer: 15 and 24 micron

- 10 MHz readout

- 10 mW/channel

- gain 5~6  $\mu$ V/e

- Detailed testing in progress

- Readout chip

- ENC = 40 e- > 30 e- (target)

- production problem

- not yet in their target 10Mpix/s

- Small prototype in 2010 for beam tests

- construction-ready EDR by 2012 2013

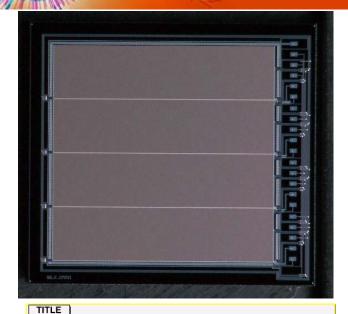

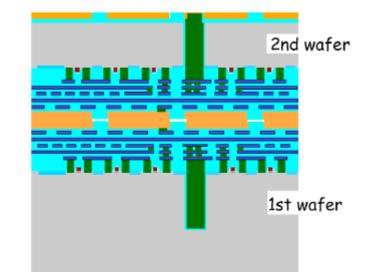

# **3-D Vertical Integration**

R. Lipton Z. Ye

- Vertical integration of electronics

- reduces interconnection lengths

- heterogenous device integration

- Tezzaron 3D process

LCWS08

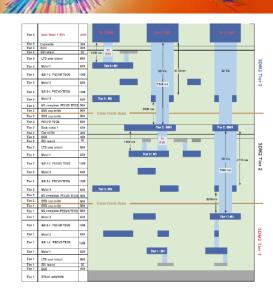

# **3-D Vertical Integration**

- Fermilab VIP chip

- 3 Tiers

- 22 micron thick

- Multiproject run being organized by Fermilab

- Cost sharing

- Synergy

- Special focus session on Tuesday

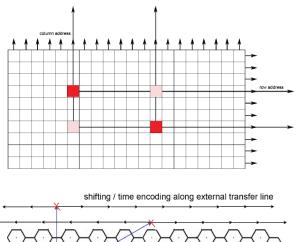

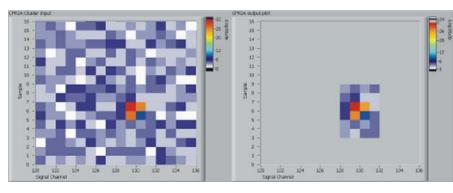

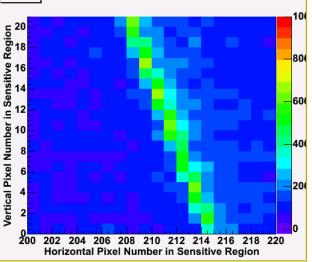

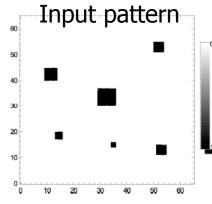

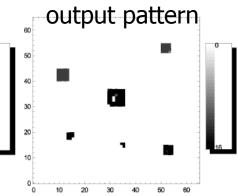

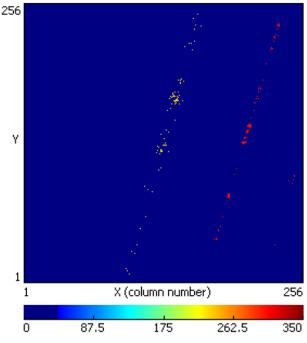

Preselected pattern of pixels for the injection of signal to the front-end amplifiers; pattern shifted into the matrix, than positive voltage step applied accross the injection capacitance; threshold levels for the discriminator adjusted according to the amplitude of the injected signal

LCWS08

Pattern of pixels from the preselected injection pattern that after injection of tests charge reported as hit (grey level represents number of repetition - 8 times injection)

R. Lipton Z. Ye

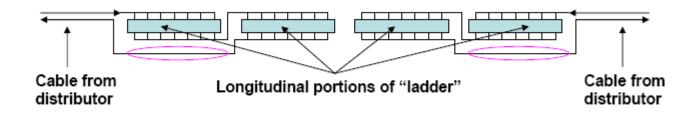

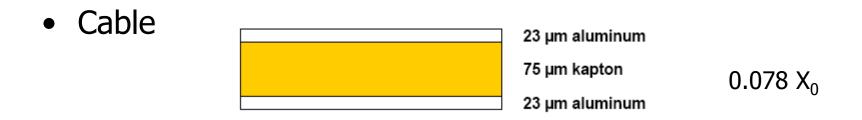

#### **Power Distribution to Vertex Detectors**

- Lorentz Forces: 0.72 N per cable

- Routing of cable has design implications

#### 23

M. Winter

P. Luzniak R. Walsh

. Maczewski

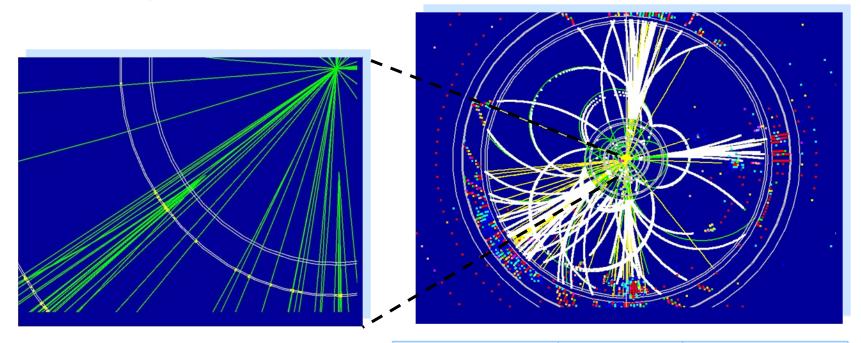

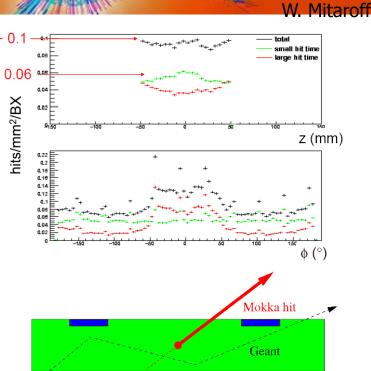

# Backgrounds and Simulation

- Background in the first layer

- large time hit

- sensitive vol. thickness 50  $\mu\text{m}$

- Low angle tracks in simulation was not adequate

- Option to store in new version

- Tagging studies for optimizations

- LiC Detector Toy

- allows quick study tracker perf.

LCWS08

# **Tracking Detector**

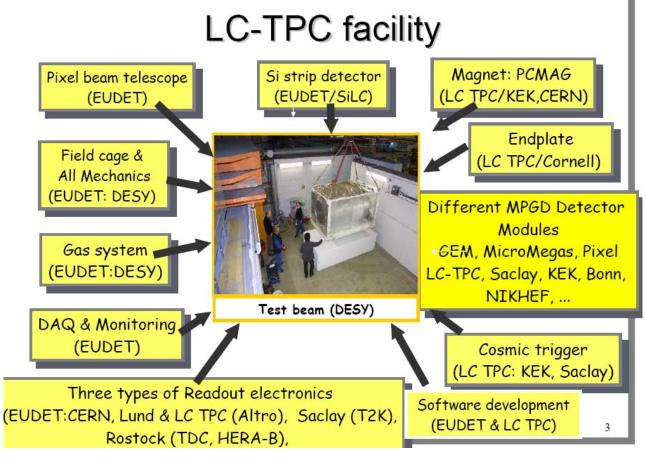

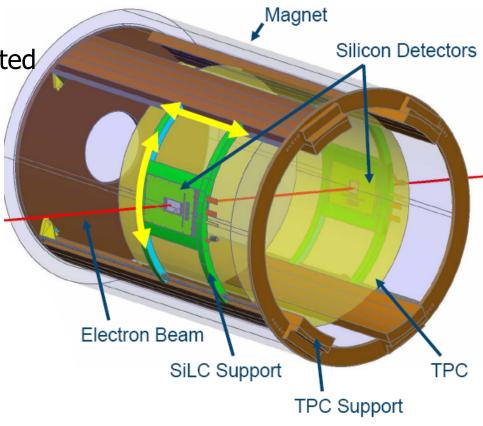

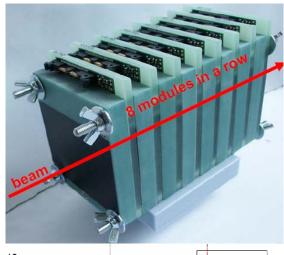

# LC TPC Large Prototype Test Beam

- Strong collaboration among many groups esp. EUDET

- Talk by I. Gregor

LCWS08

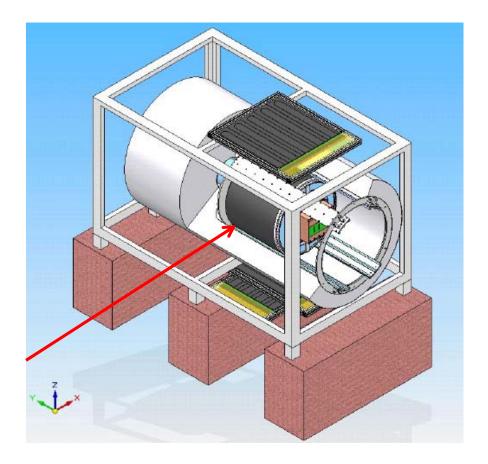

# LC TPC Large Prototype

- SilC strip detector outside to monitor beam position

- Overall beam infrastructure ready

- Movable stage expected early 2009

- Beam will be available for most of 2009, but DESY cryo upgrade

- First cosmics with B field next week with micromegas

T. Behnke

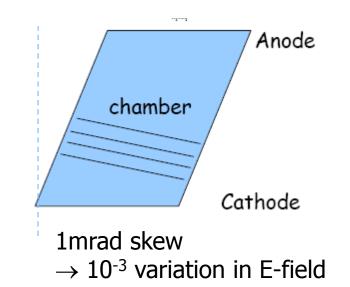

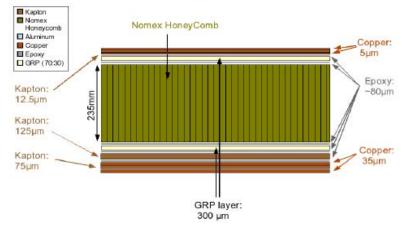

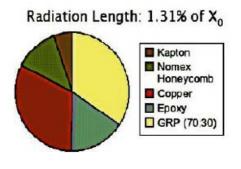

# LC TPC Large Prototype

Material budget per wall

**Ties Behnke**

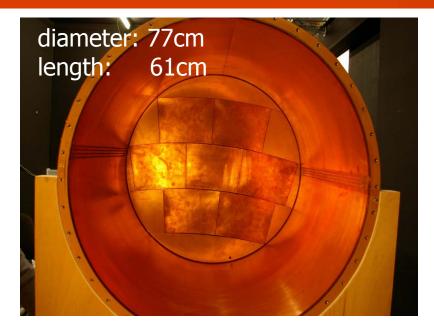

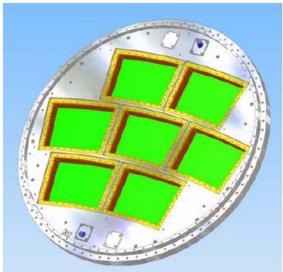

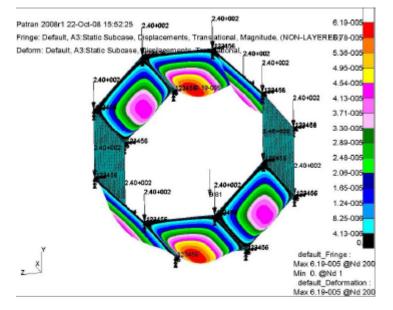

# LC TPC Endplate

provide framework to evaluate several readout technologies

LCWS08

- 7 modules common radius of curvature

- 25 micron tolerance

- made of aluminum

- 10/30/2008 endplate assembled with one micromegas module

D. Peterson

M. Dixit

# LCTPC Large Prototype

- Commissioning

- End plate and cathode mounted

- gas tightness confirmed

- HV test undergoing

- Demonstrate

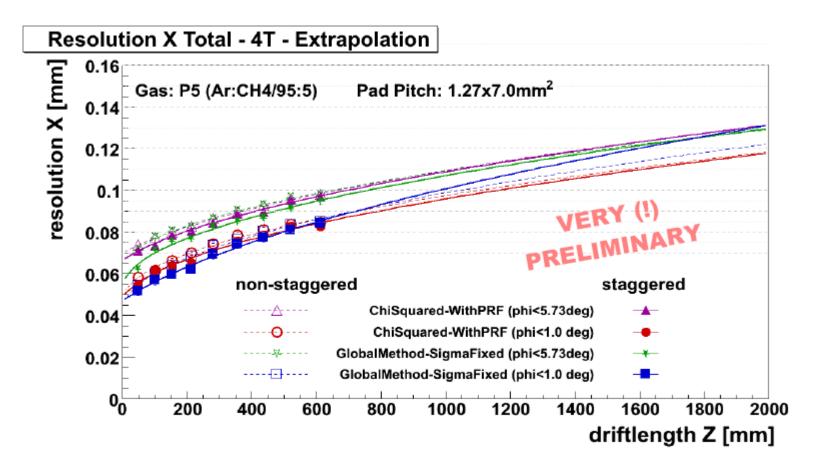

- full volume tracking in non uniform B field

- d(1/pt) ~ 10<sup>-4</sup> (GeV<sup>-1</sup>)

- 100 micron r- $\phi$  resolution 2-m drift

- dE/dx capabilities

Silicon detectors in Feb. 2009

Energy Resolution Photopeak [%]

LCWS08

. Hallermann

Angle Cut at  $|\phi| < 1.0^{\circ}$  and  $|\phi| < 0.1$ rad (5.73°)

LCWS08

R. Diener

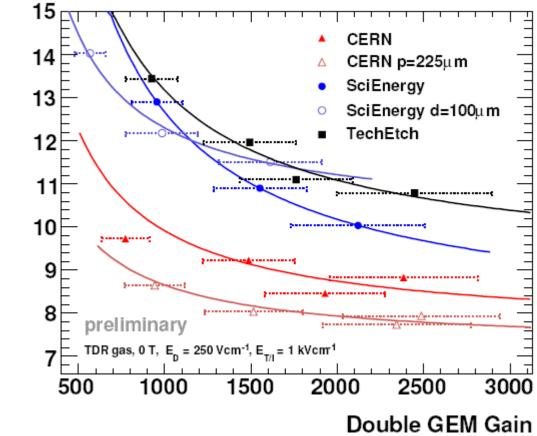

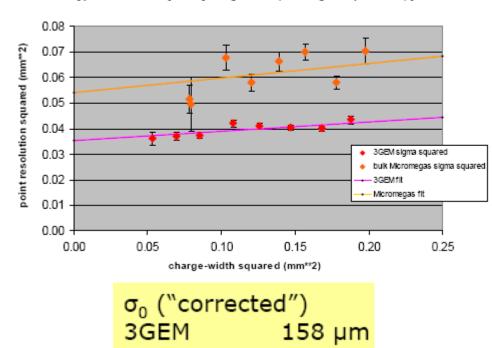

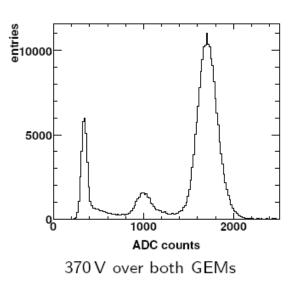

## GEM and Micromegas With Ar-CF<sub>4</sub>isobutane gas

small TPC prototype at Cornell in CLEO magnet

Micromegas 209 µm

- gain of micromegas half of 3GEM in this setup

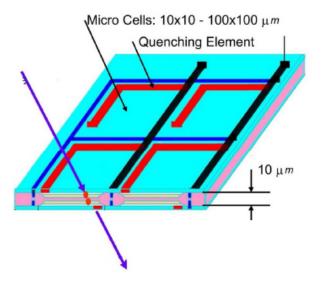

## Silicon Pixel Readout for TPC

LCWS08

J. Timmermans R. Uwe

- Timepix chip with 20 micron Amorphous silicon protection

- works stably even when discharge

- CERN beam test

- In progress

- Alternative grid structures: twin grid – separate high-gain region from anode

- Optimize protection / signal

- Scale up

- Studies of Triple GEM with timepix

## **GEM Support**

- Flatness affects gain variation

- 380  $\mu m$  variation in flatness  $\pm$  6% in gain

- GEM support

- Ceramic material

L. Hallermann

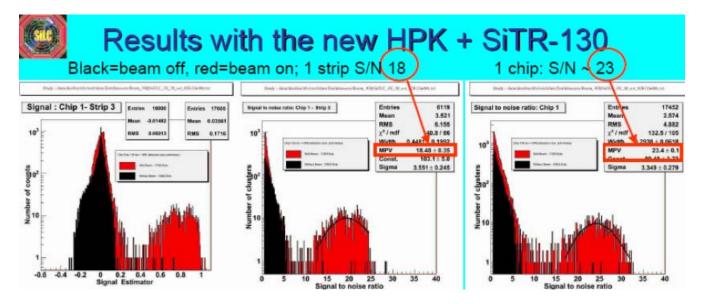

# SiLC Tracker

A. Navarro

- HPK 6" delivered end of 2007

- Short term

- single sided sensor

- edgeless detector from Canberra

- thin detector with HPK

- 3-D planar started testing

- Longer term pixel technology

- DEPFET

- Low material, high-gain 10<sup>6</sup>

- 3-D pixels and 3-D Vertical interconnect

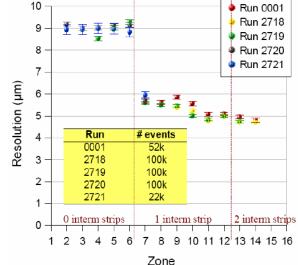

# SiLC Tracker

- Sensors

- HPK 1 intermediate strip improves resolution from 9  $\rightarrow$  5 micron

- new 3D pixel breakdown mode

- Electronics

- FEE: 130nm -> 90 nm

- FE chip direct connection to sensor by bump bonding

- 3D Vertical integration

#### SiLC Beam Test

#### SilC

- Mechanics

- Alignment using silicon trackers, single layer

- light support structure

- test beam 3-D table

- Integration

- ILD integration of SiLC tracker

- Driving schedule

- test beam

- LOI

- Driving parameters

- lightness and robustness

- simplicity for construction

A. Navarro

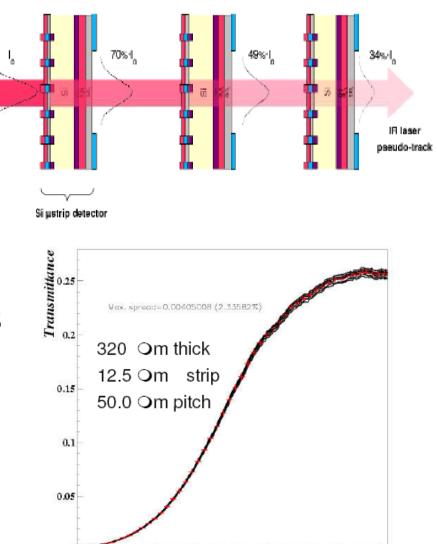

# SiLC Tracker Alignment

A. Jimeno

- Laser alignment

Used in AMS and CMS

- Problem is transmittance

- strip width reduction

- new transparent materials

- Accuracy currently 4 microns

Single layer

975

95.0

LCWS08

1000

1025

1050

1075

1100

1125

1150

λ (nm)

## SiLC Tracker Readout Chip

A. Navarro

- 88 channel fully programmable version in hand

- Next steps

- thin

- 90 nm process

- CLIC

- bump bonding to sensor

# Silicon Pixel Tracking

- 5 layers, 5% X<sub>0</sub>

- 50 micron pixels

- Occupancy: 10<sup>-4</sup>

- 50 Gpixels

- Integrate signals through 1 train or

- Time slicing integrate several bunches

- ISIS technology low power

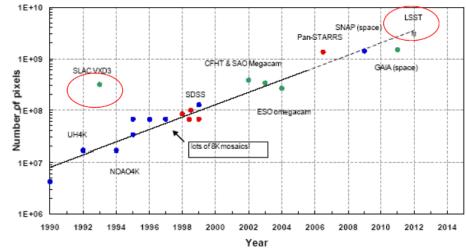

Illustration of focal plane sizes, from Luppino/Burke 'Moores' law

C. Damerell