# Development of Vertically Integrated Circuits for ILC Vertex Detectors

- This talk will be an overview of the work done over the past two years to investigate the application of vertically integrated electronics to HEP

- Contents

- Overview of 3D

- The VIP chip for ILC Vertex

- VIPII

- Sensor integration

- Conclusions

- Other talks today

- Direct oxide bonding Zhenyu Ye

- SOI R&D Marcel Trimpl

# 3D Technology

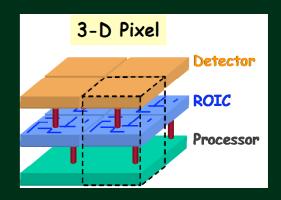

- 3DIC vertical integration of electronics

3D IC technology is likely to become an important component of future electronics

- Reduces length and R,C of interconnects

- Allows for heterogeneous device integration

- Improves processing density/pixel

- Increases circuit density without billions of investment in new fab facilities

- Multicore processors are at the memory access limit - more bandwith is crucial to continue Moore's Law performance

- This is a opportunity for HEP to build detectors with significantly improved performance

Conventional MAPS

IBM SOI on Glass Wafer

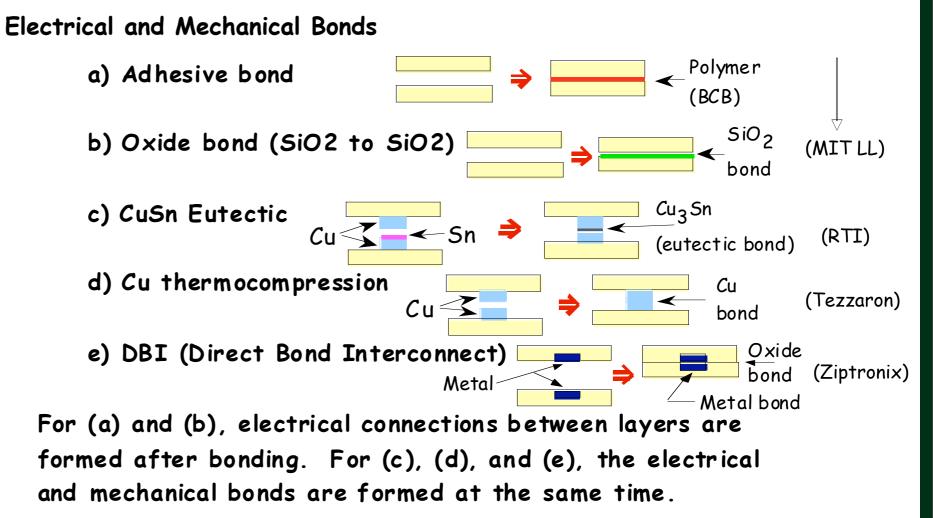

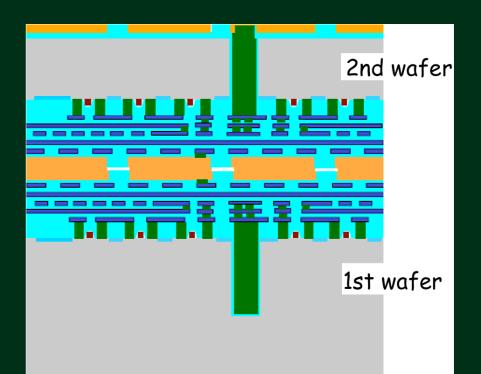

### Technology based on: 1) Bonding between layers

- Oxide to oxide fusion

- Copper/tin bonding

- Copper/copper

- Polymer/adhesive bonding

- 2) Wafer thinning

- Grinding, lapping, etching, CMP

- 3) Through wafer via formation and metalization

- With isolation

- Without isolation (SOI)

- 4) High precision alignment

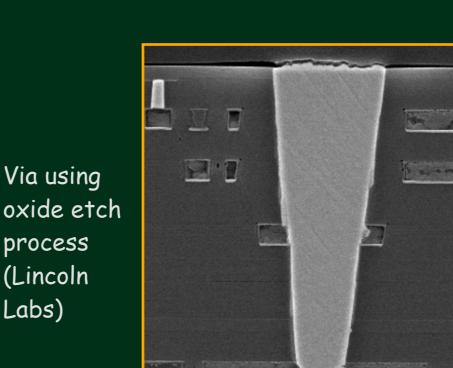

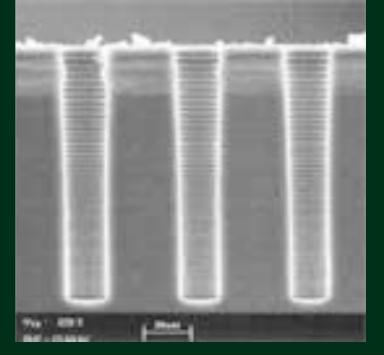

SEM of 3 vias using Bosch process

Labs)

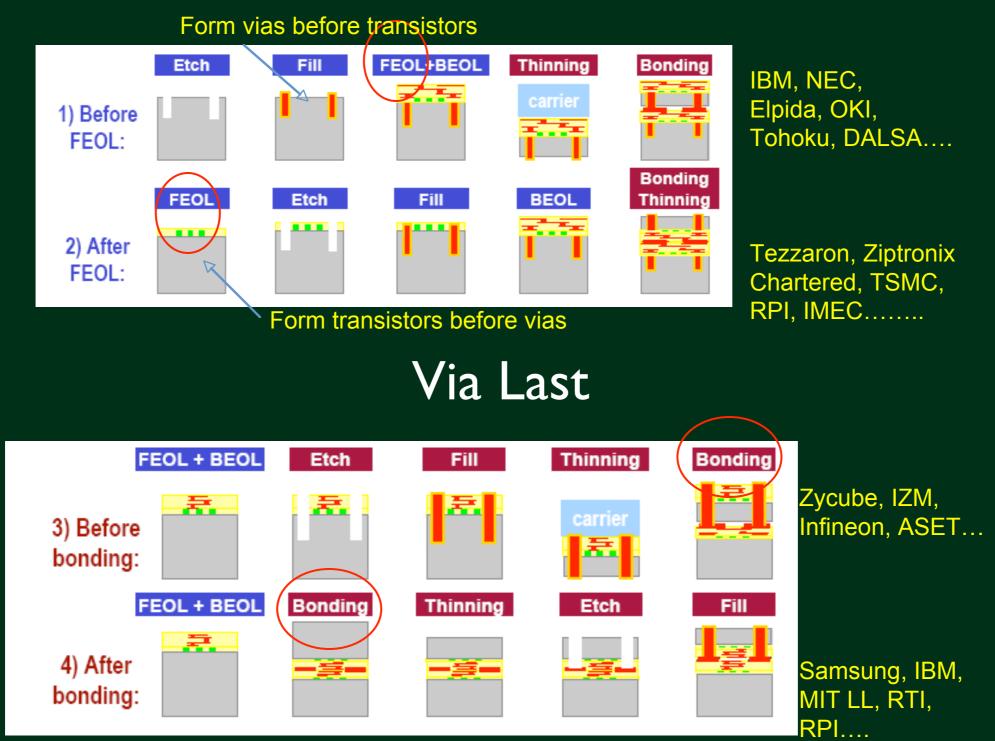

## Via Formation Strategies

# Via First

## **Bonding Technologies**

#### 1) Bonding between layers

- Oxide to oxide fusion

- Copper/tin bonding

- Polymer/adhesive bonding

- 2) Wafer thinning

- Grinding, lapping, etching, CMP

- 3) Through wafer via formation and metalization

- With isolation

- Without isolation

- 4) High precision alignment

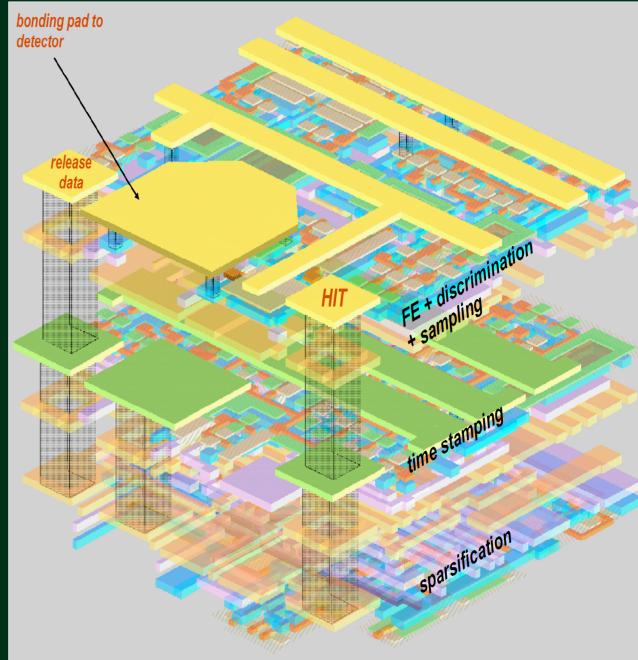

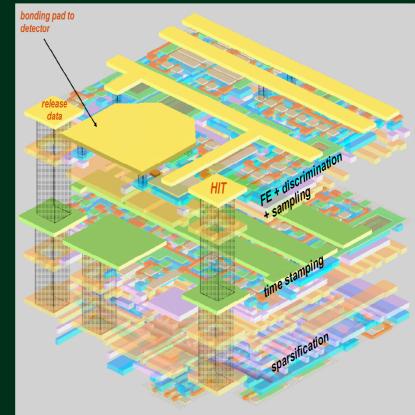

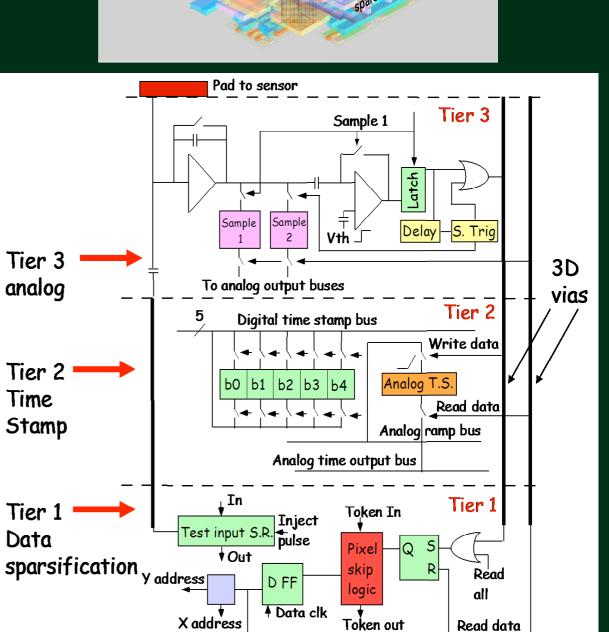

## **VIP** Chip

Goal - demonstrate ability to implement a complex 3D pixel design with all required ILC properties in a 20 micron square pixel

Previous technologies limited to simple circuitry or larger pixels - 3D density allows analog pulse height, sparse readout, high resolution time stamp in a 20 micron pitch pixel.

- Time stamping and sparse readout occur in the pixel, Hit address found on array perimeter.

- 64 x 64 pixel demonstrator version of 1k x 1K array.

- Submitted to 3 tier DARPA-sponsored ulletmulti project run. Sensor to be added later.

- Low power front end 1875 µW/mm2 x Duty Factor

Ronald Lipton, LCWS Nov 17 2008

Time

Tier 1

Data

6

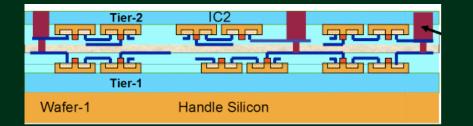

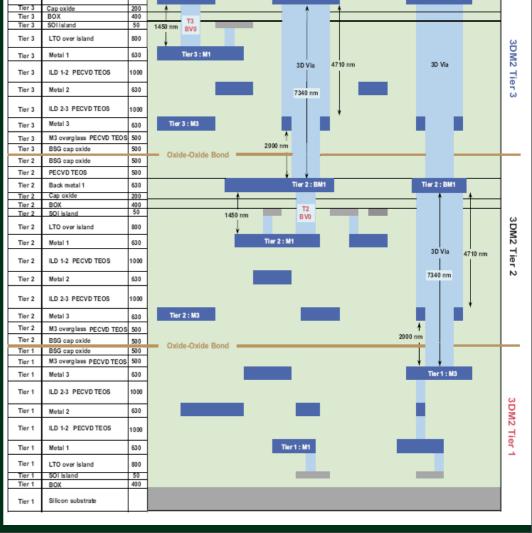

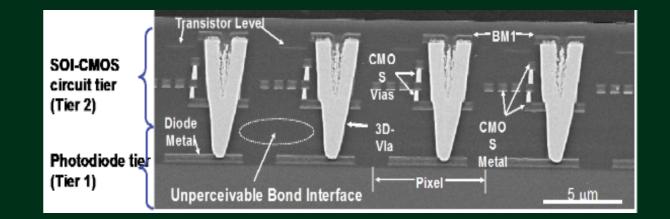

## **MIT-LL 3D Process**

#### 1) Fabricate individual tiers

|                   | Buried Oxide                   |   |

|-------------------|--------------------------------|---|

| Wafer-2           | Handle Silicon                 |   |

|                   |                                | _ |

|                   |                                |   |

| THE REAL PROPERTY |                                |   |

|                   | Buried Oxide                   |   |

| Wafer-1           | Buried Oxide<br>Handle Silicon |   |

4) Invert, align and bond wafer 3 to wafer 2/1 assembly, remove wafer 3 handle wafer, form 3D vias from tier 2 to tier 3

#### Three levels of transistors, 11 levels of metal in a total vertical height of only 22 um.

#### 2) Invert, align, and bond wafer 2 to wafer 1

| S-1∋teW | nooiliS əlbnsH | 3D. |    |

|---------|----------------|-----|----|

|         | Buried Oxide   | Via |    |

|         |                |     | 0  |

|         |                |     | bc |

|         |                |     |    |

| Wafer-1 |                |     |    |

3) Remove handle silicon from wafer 2, etch 3D Vias, deposit and CMP tungsten

Ronald Lipton, LCWS Nov 17 2008

xide ond

Back Metal 1 (RF)

Tier 3

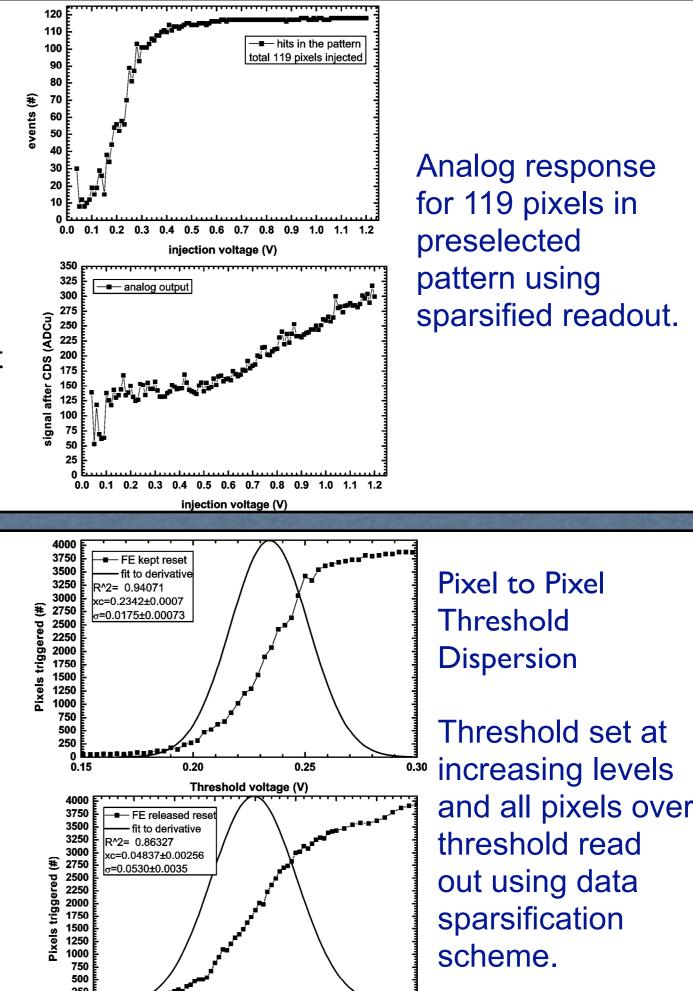

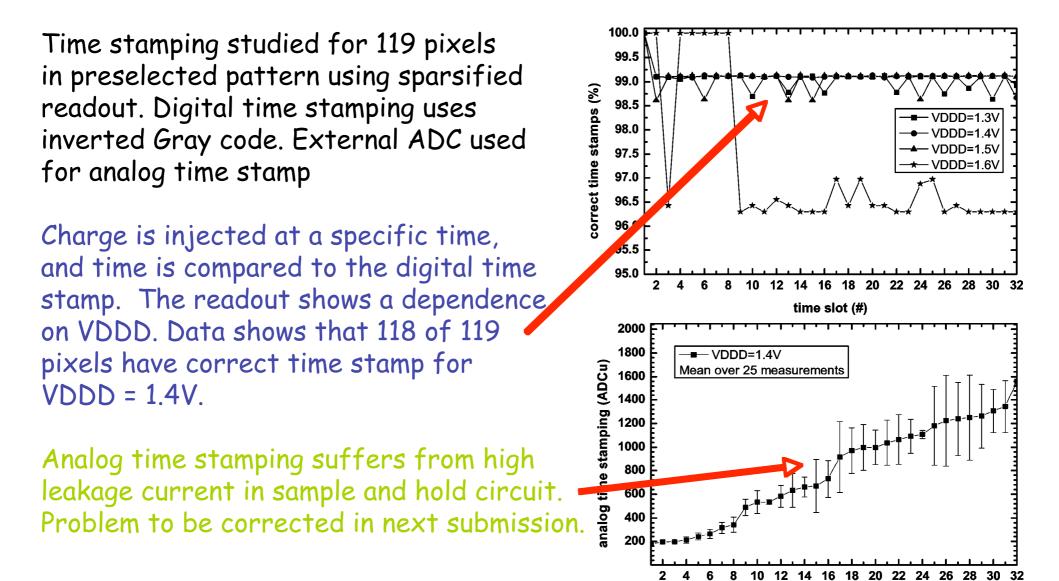

## **VIP** Test results

- Basic functionality of the chip has been demonstrated

- Propagation of readout token

- Threshold scan

- Input test charge scan

- Digital and analog time stamping

- Full sparsified data readout

- Fixed pattern and temporal noise measurements

No problems could be found associated with the 3D vias between tiers.

- Chip performance compromised by:

- Poor transistor models

- Large leakage currents in transistors and diodes

- Poor current mirror matching

- Vdd sensitivity

- low yield Ronald Lipton, LCWS Nov 17 2008

8

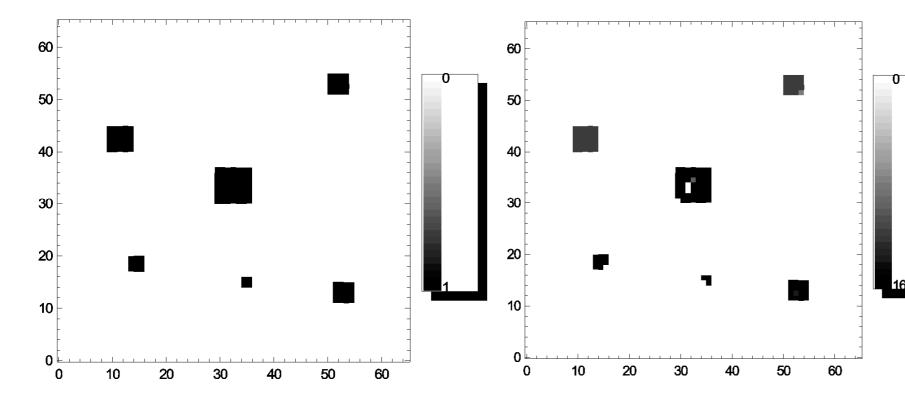

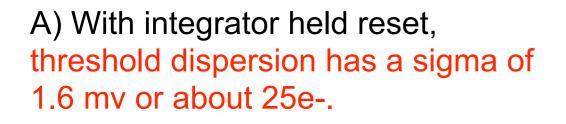

Injection of Test Charge into 119 Integrator Inputs of 64 x 64 Array

Preselected pattern of pixels for the injection of signal to the front-end amplifiers; pattern shifted into the matrix, than positive voltage step applied accross the injection capacitance; threshold levels for the discriminator adjusted according to the amplitude of the injected signal

Pattern of pixels from the preselected injection pattern that after injection of tests charge reported as hit (grey level represents number of repetition - 8 times injection)

#### Data readout out using data sparsification scheme.

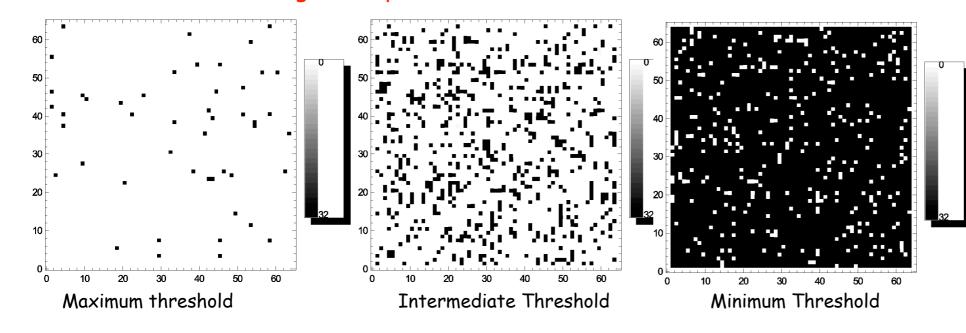

Hit Pixels in Full Array as a Function of Threshold As level of test charge through test capacitor (located between tier 2 and 3) is increased, more pixels exceed the threshold up to the maximum of 119 pixels

Mean analog signal level of pixels exceeding the threshold voltage. The red line is an indication of the linearity of the analog output signal (100 ADC units= 35 mv). charge injection capacitor = 0.2 fF

B) With integrator reset and released, discriminator reset (autozeroed), threshold dispersion has a sigma of 4.9 mv or about 75 e-.

-0.10 -0.05 0.00 0.05

-0.15

0.10

0.15

0.25

0.20

## Time Stamping Performance

time slot (#)

## **VIP Lessons Learned**

- Difficult to design complex devices in an R&D process

- Long turn-around

- Unreliable models

- low yields

- SOI has particular analog design issues

- Differential heating of "island" silicon and mobile contamination in oxide can cause mismatch of current mirrors

- MIT-LL had high leakage in protection diodes

- Short "hold" time in dynamic logic due to leakage

## VIPII

- An improved version of the VIP was submitted to MIT LL in October. The new chip is called VIP2

- Different power and grounding layout

- Larger transistor sizes  $(0.18 \rightarrow 0.5 \text{ micron})$

- Larger pixels (30 x 30 microns)

- Redundant vias and larger traces in critical paths

- On chip ADC

- More bits in digital time stamp (7 bits)

- Redesign of current mirrors

- Removal of dynamic logic due to leakage current problems

- Very useful interaction with MIT-LL on SOI should improve overall quality of the design

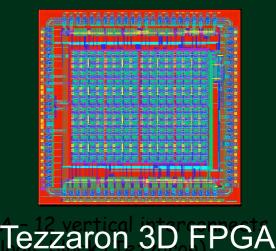

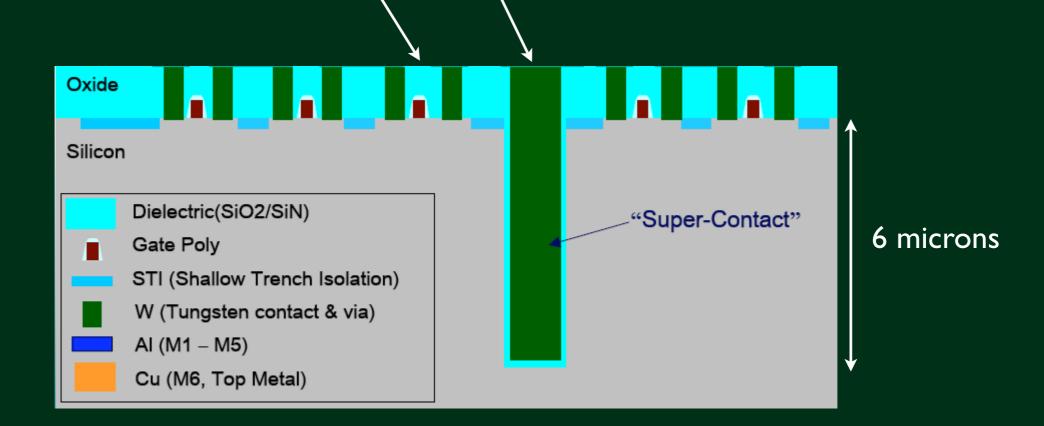

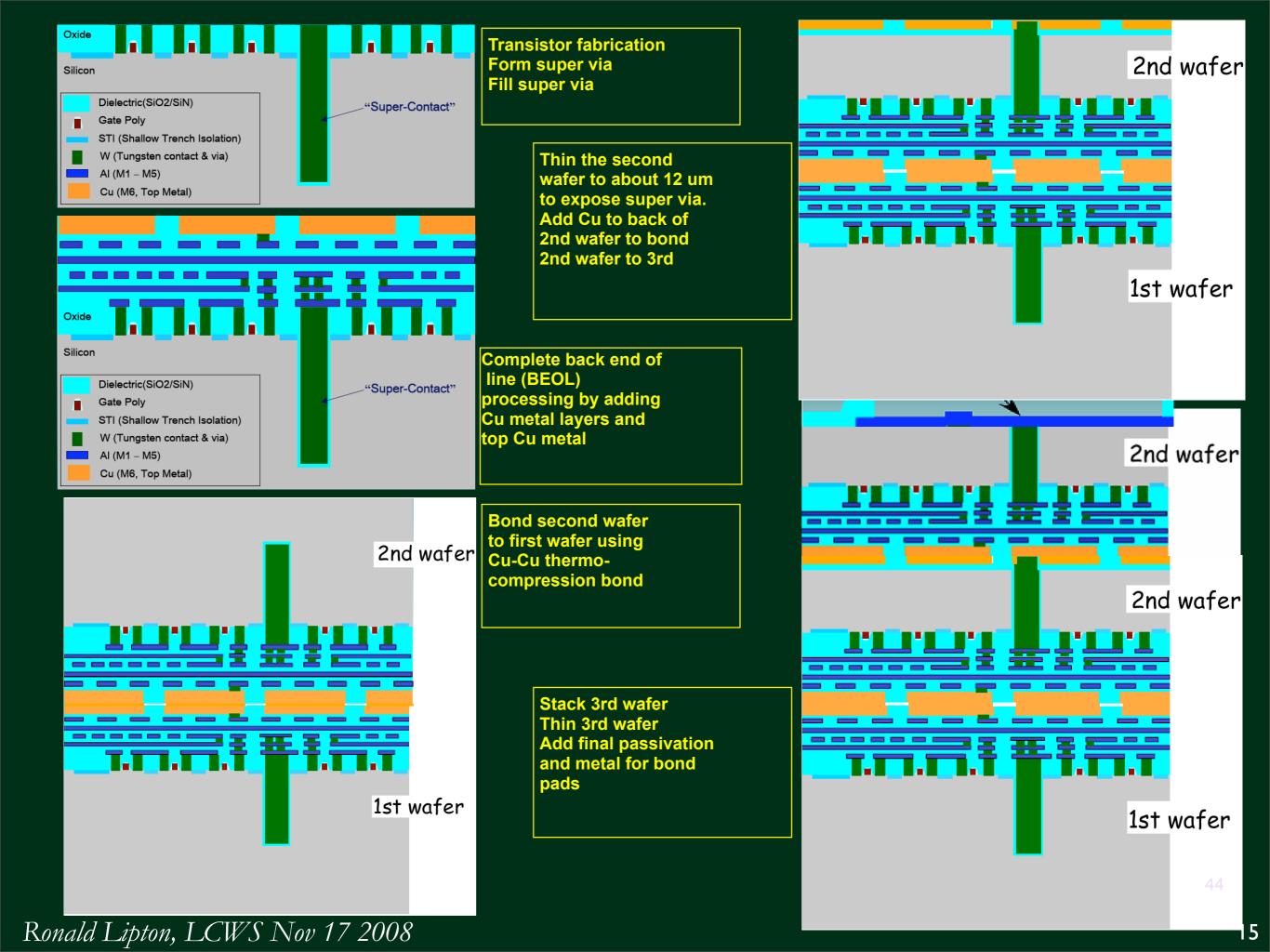

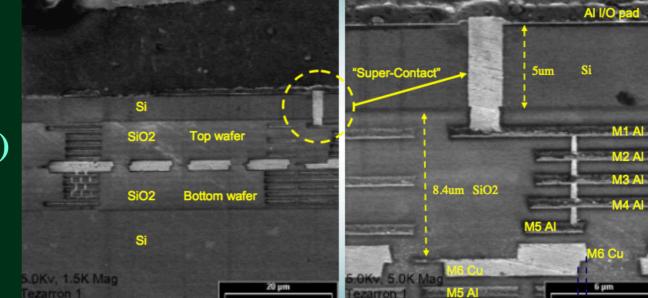

### **Tezzaron Process**

- Tezzaron (Naperville Ill) has developed a 3D technology implemented in the high volume 0.13 micron Chartered (singapore) process

- Through silicon vias are fabricated as a part of the foundry process. "Via first" approach.

- Complete FEOL (transistor fabrication) on all wafers to be stacked

- Form and passivate super via on all wafers to be stacked

- Fill super via at same time connections are made to transistors

## Tezzaron Multiproject run, VIPIIb

- Fermilab is organizing a multiproject run which will include a two tier version of the VIP

- Process can include MAPS option

- Submission this spring

- Labs with NDAs:

- Fermilab, Batavia

- University at Bergamo (3D MAPs)

- University at Pavia

- University at Perugia

- INFN Bologna

- INFN at Pisa

- INFN at Rome

- CPPM, Marseilles

- IPHC, Strasbourg

- IRFU Saclay

- LAL, Orsay

- LPNHE, Paris

- CMP, Grenoble

- VIP2b in *standard commercial CMOS*, more dependable models, better rad hardness, faster turn-around, availability of full wafers for sensor integration, less wasted area

- expect much better performance

## **Sensor Integration**

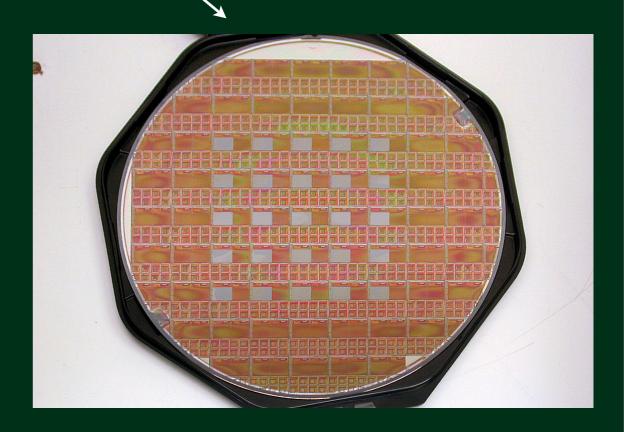

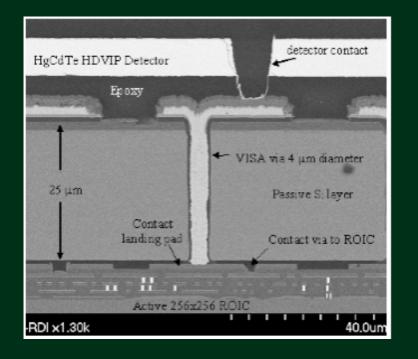

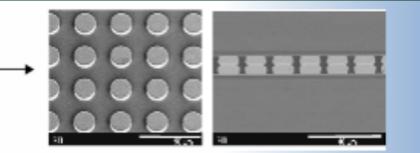

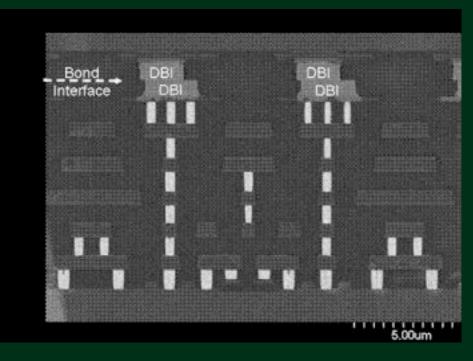

- 3D techniques can also be applied to sensor integration with readout

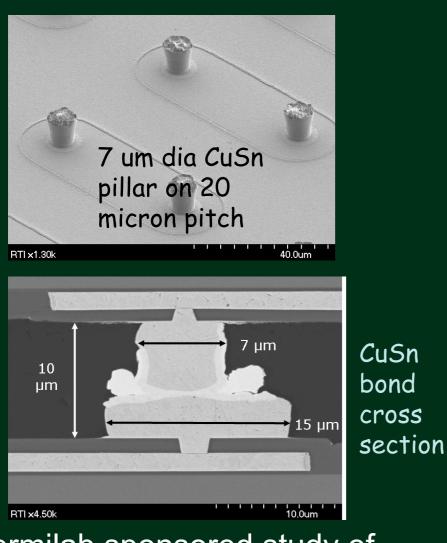

- We have tried two techniques: Cu-Sn and DBI oxide bonding

CuSn

bond

DBI provides a robust bond with low capacitance and very fine pitch - results of first tests in Zhenyu Ye talk

Fermilab sponsored study of sparse Cu-Sn bonding by RTI Ronald Lipton, LCWS Nov 17 2008

**MIT-LL BTeV sensors bonded to** FPIX2 wafer, tinned to 100 microns after bonding (would be better to bond ROIC to sensor)

## Examples of sensor Integration

Epoxy bonded 3D connected imager (RTI/DRS) with through silicon vias

Non-collapsible Cu-Sn bonds fabricated at RTI

8 micron pitch, 50 micron thick oxide bonded imager (Lincoln Labs)

8 micron pitch DBI (oxide-metal) bonded PIN imager (Ziptronix)

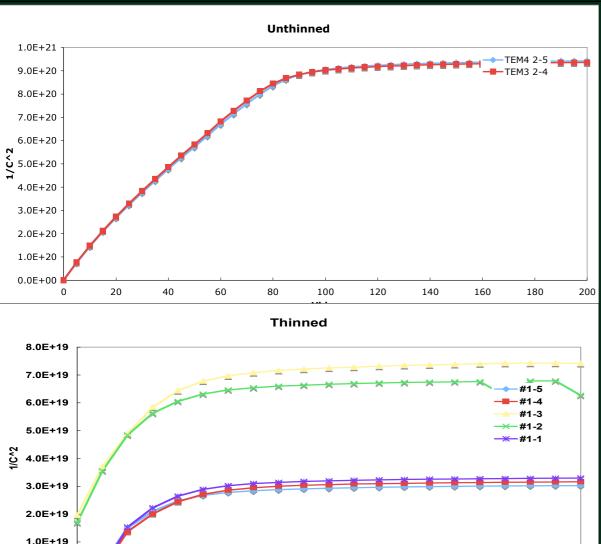

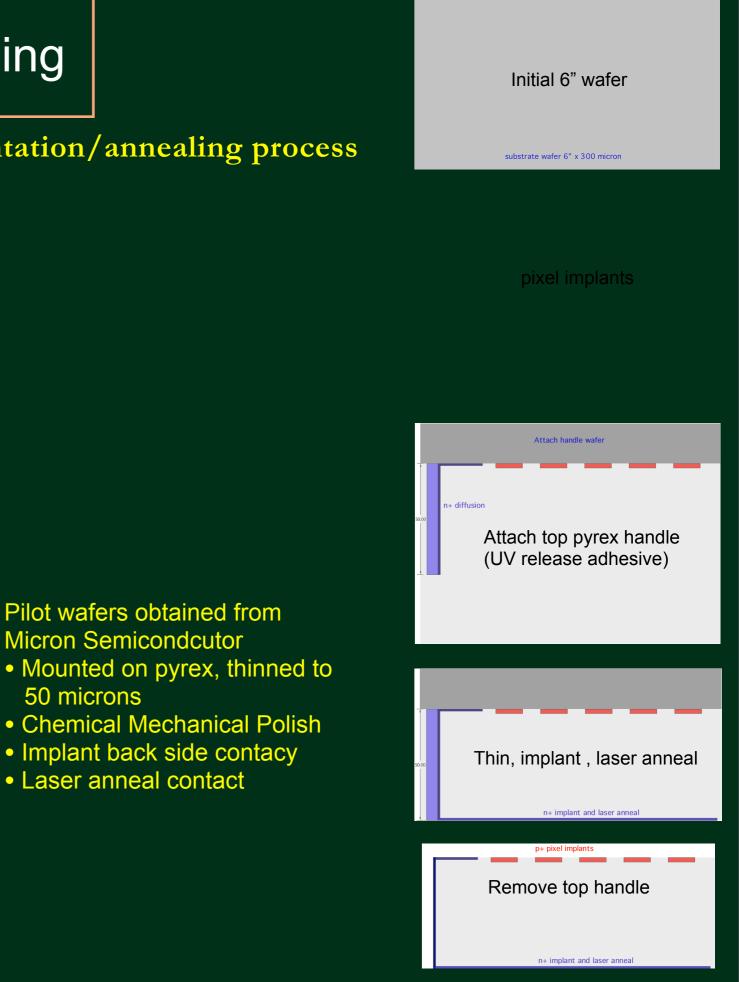

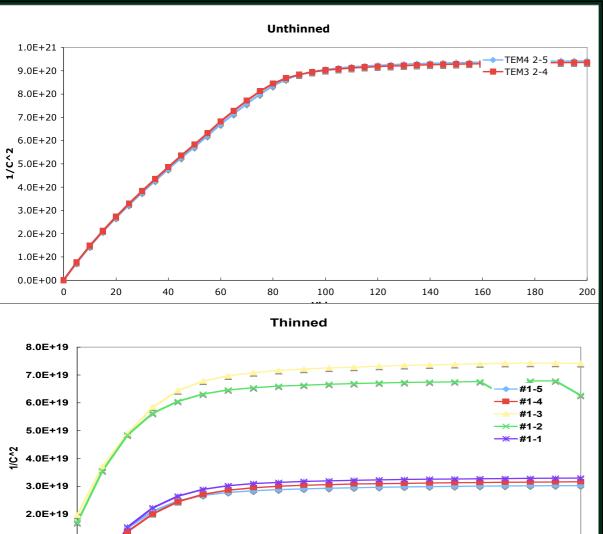

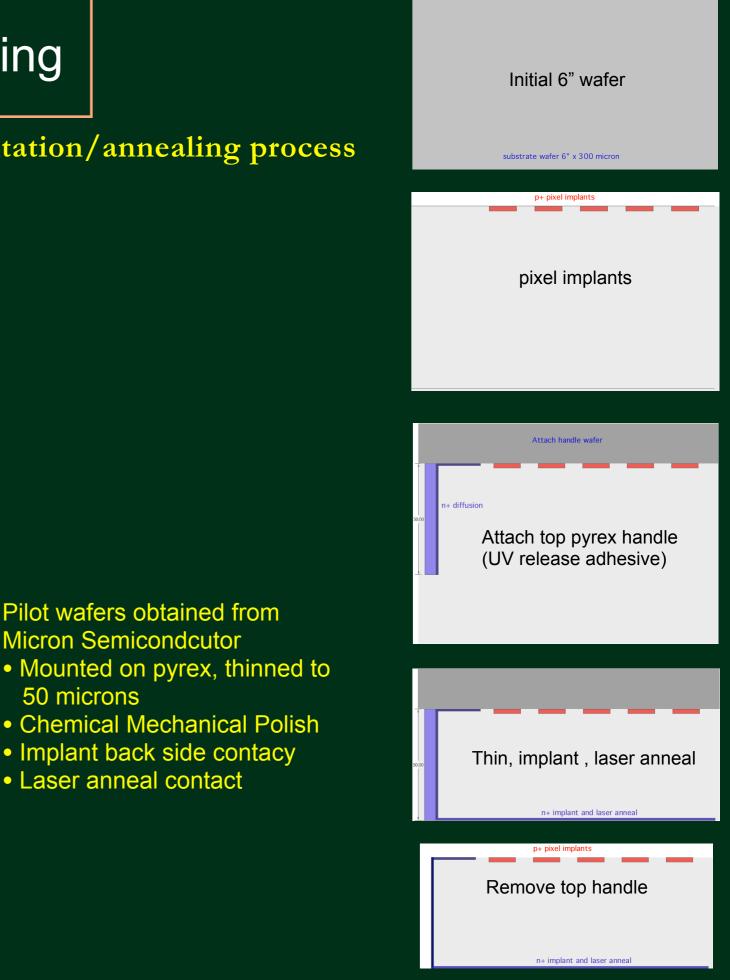

## Thinning and Laser Annealing

• We have developed a thinning/implantation/annealing process based on a 3M bonded pyrex carrier Bond to pyrex carrier lacksquareThin, chemical mechanical polish Implant Laser anneal Remove from carrier to dicing tape ۲ Unthinned 1.0E+21 TFM4 2-5 Attach handle wafe 9.0E+20 -TEM3 2-4 8.0E+20 7.0E+20 n+ diffusion 6.0E+20 **5**.0E+20 Attach top pyrex handle (UV release adhesive) 4.0E+20 3.0E+20 2.0E+20 Pilot wafers obtained from 1.0E+20 **Micron Semicondcutor** 0.0E+00 Mounted on pyrex, thinned to 20 40 60 80 100 160 180 200 0 120 140 50 microns Thinned Chemical Mechanical Polish 8.0E+19 Implant back side contacy 7.0E+19 Thin, implant, laser anneal Laser anneal contact 6.0E+19 #1-3 #1-2 5.0E+19 #1-1 ζ 2 4.0E+19 3.0E+19 2.0E+19 Remove top handle 1.0E+19 0.0E+00 n 1 2 2 4 5 6 9 10 n+ implant and laser anneal Vbias

### Thinning and Laser Annealing

- We have developed a thinning/implantation/annealing process based on a 3M bonded pyrex carrier

- Bond to pyrex carrier

- Thin, chemical mechanical polish

- Implant

0.0E+00

n

1

2

2

4

5

Vbias

6

7

9

10

- Laser anneal

- Remove from carrier to dicing tape

### Thinning and Laser Annealing

• We have developed a thinning/implantation/annealing process based on a 3M bonded pyrex carrier

Pilot wafers obtained from

Chemical Mechanical Polish

Implant back side contacy

**Micron Semicondcutor**

Laser anneal contact

50 microns

- Bond to pyrex carrier ightarrow

- Thin, chemical mechanical polish

- Implant

1.0E+19

0.0E+00

n

1

2

3

4

5

Vbias

6

9

10

- Laser anneal

- Remove from carrier to dicing tape ۲

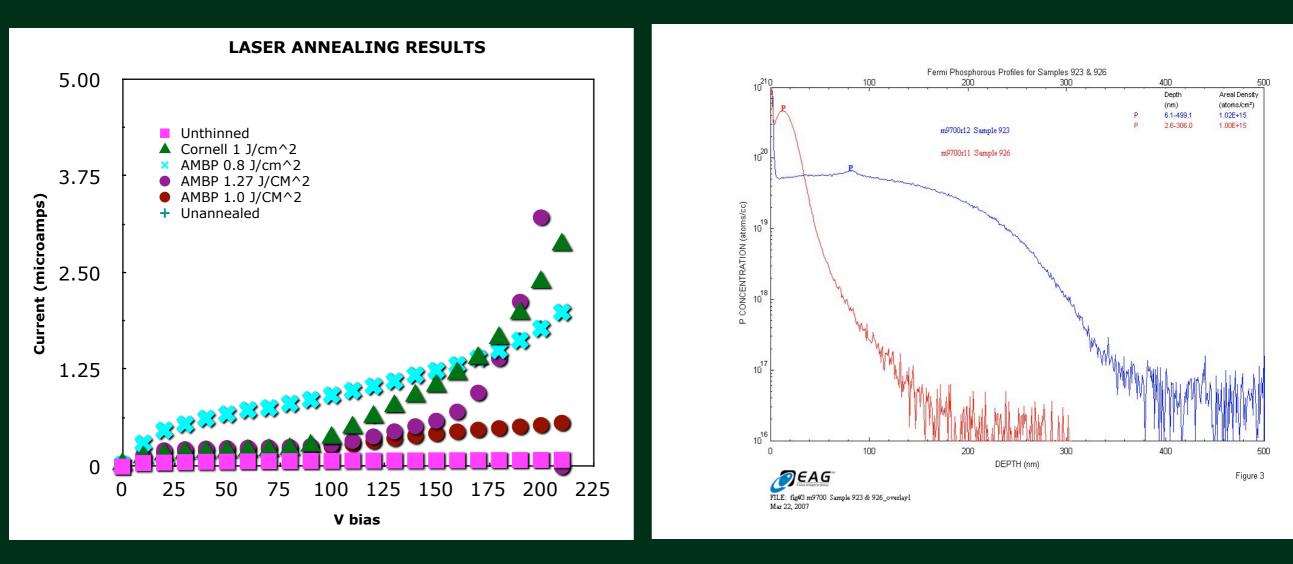

### Laser Annealing

- For some technologies sensors need to be thinned after the top side circuitry has been processed this limits the process temperature to <400 deg C. This makes backside ohmic contacts difficult to form. We are developing a laser annealing process which limits the frontside temperature

- Cornell group is continuing to optimize laser parameters.

- We will use the process to thin and anneal OKI SOI wafers.

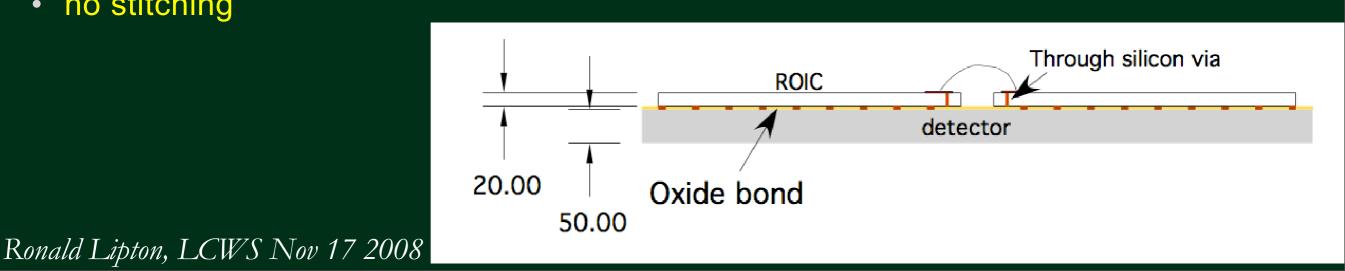

### Possible ILC Vertex Design

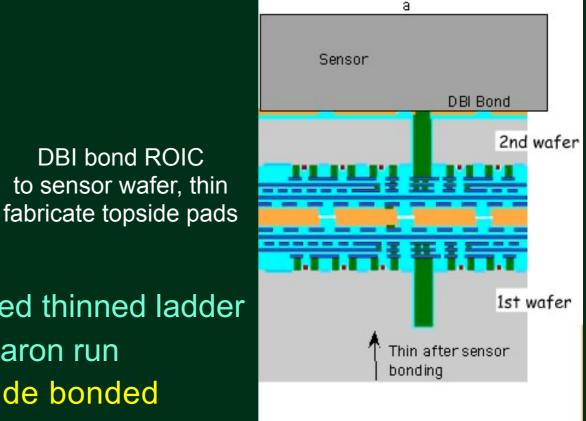

- A bonded Tezzaron wafer provides "supercontacts" above and below the substrate. The bottom contacts can be used to provide 4-side buttabiliy

- Produce sensor wafer thinned and bonded ٠ to silicon substrate

- DBI bond ROIC to sensor wafer using top ۲ supervias to contact sensor pixels to ROIC

- After bonding to sensor grind ROIC to ~ 24 microns to reveal top super vias ٠

- Contacts to readout are made by ٠ lithography to top pads

- Remove bottom side handle wafer to produced thinned ladder ٠

- This process will be tested in upcoming Tezzaron run

- Alternative could use cu-sn bonds and polyimide bonded wafers would allow all thinning on full wafers

- Use 6" sensor wafers full length ladders

- no stitching

**DBI bond ROIC**

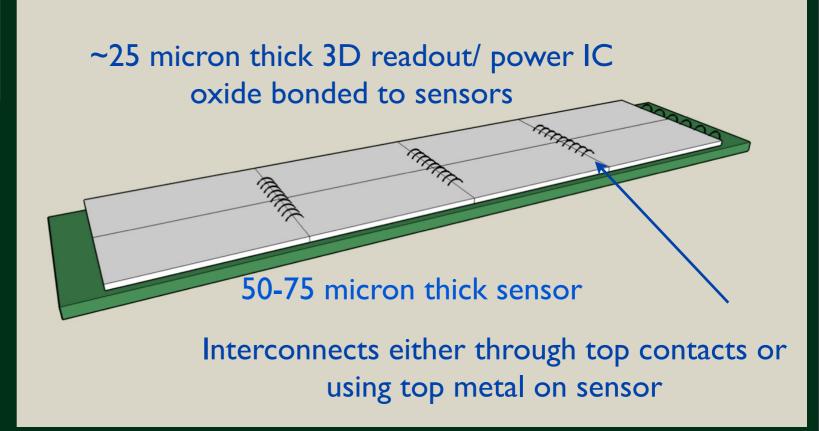

## 3D Based VXD

- Toy model of a 3D based vertex detector

- Normal p-on-n sensors with 20-25 micron pitch pixels

- Chip-on-wafer bond to readout ICs

- Thin ICs to 25 microns after bonding to expose through-silicon vias and pattern topside interconnects

- Thin base silicon if necessary

## Conclusions

- First 3D chip for HEP (VIP) produced and tested

- Functional, but low yield and high leakage currents

- Postponed detector integration efforts for VIP

- Second version has been submitted to MIT-LL

- Moving to commercial 3D technologies

- VIP in two-tier 0.13 micron CMOS

- Expect increasing commercial availability of other technologies. This is just the beginning.

- Developing sensor integration technologies

- Thinning and laser annealing techiques

- Received Direct bond Interconnect BTeV ICs bonded to thinned sensors

- Shown robust fine pitch cu-sn bonding

- Conceptual design for a 3D integrated ladder