#### Mimoroma2 MAPS chip: all NMOS on pixel sparsification architecture (LCWS08, November 2008)

### Eleuterio Spiriti (INFN RomaTre)

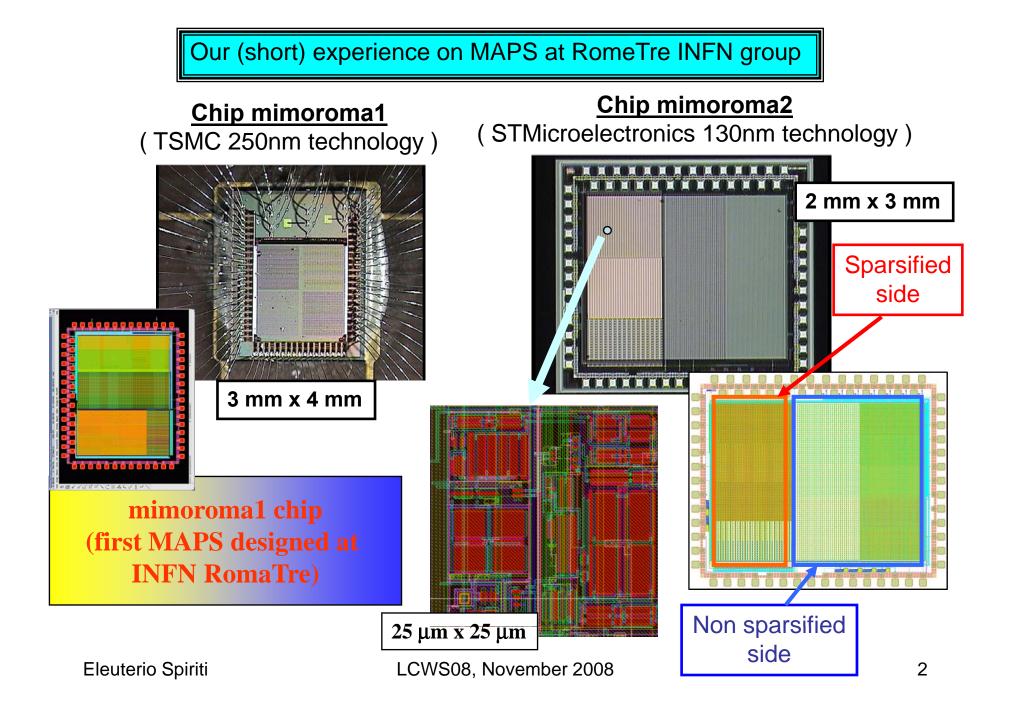

- 1. Our (RomeTre group) experience on MAPS

- Mimoroma1 chip: brief description

- 2. The Mimoroma2 sensor

- Main goals and constrains

- Proposed ladder readout and Pixel architecture

- Test set up

- Mimoroma2 sensor radioactive sources test results

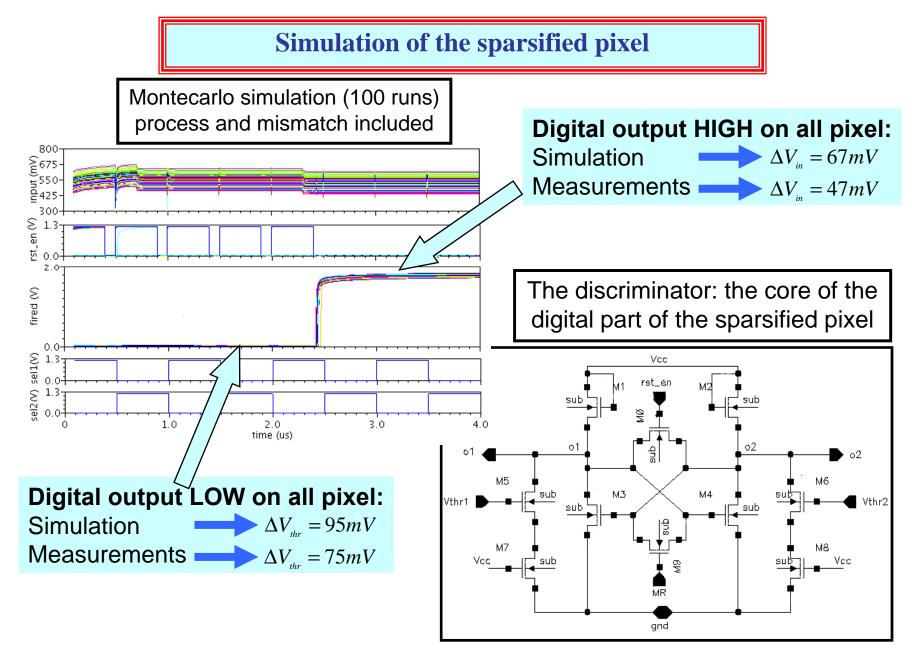

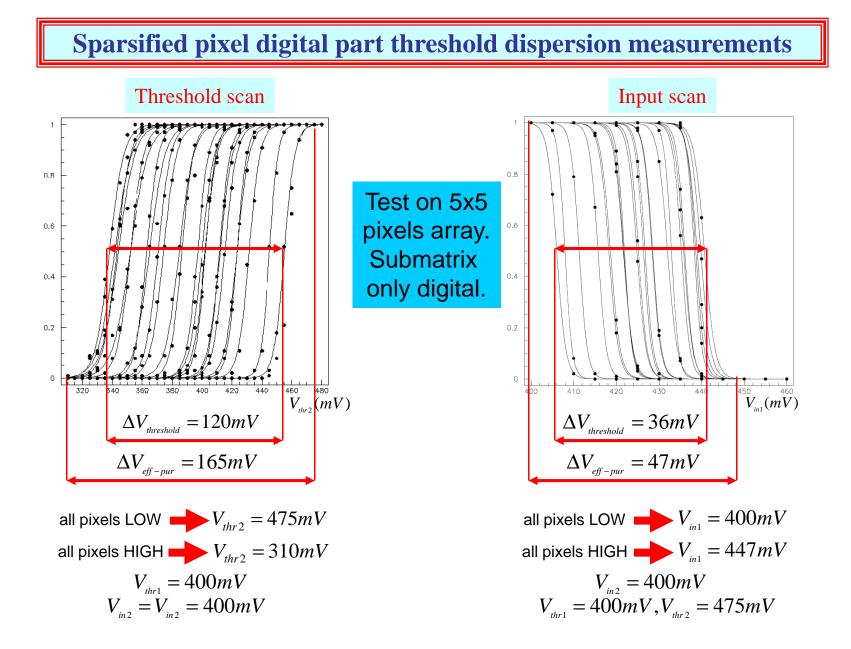

- Mimoroma2 sensor simulation and threshold spread measurements

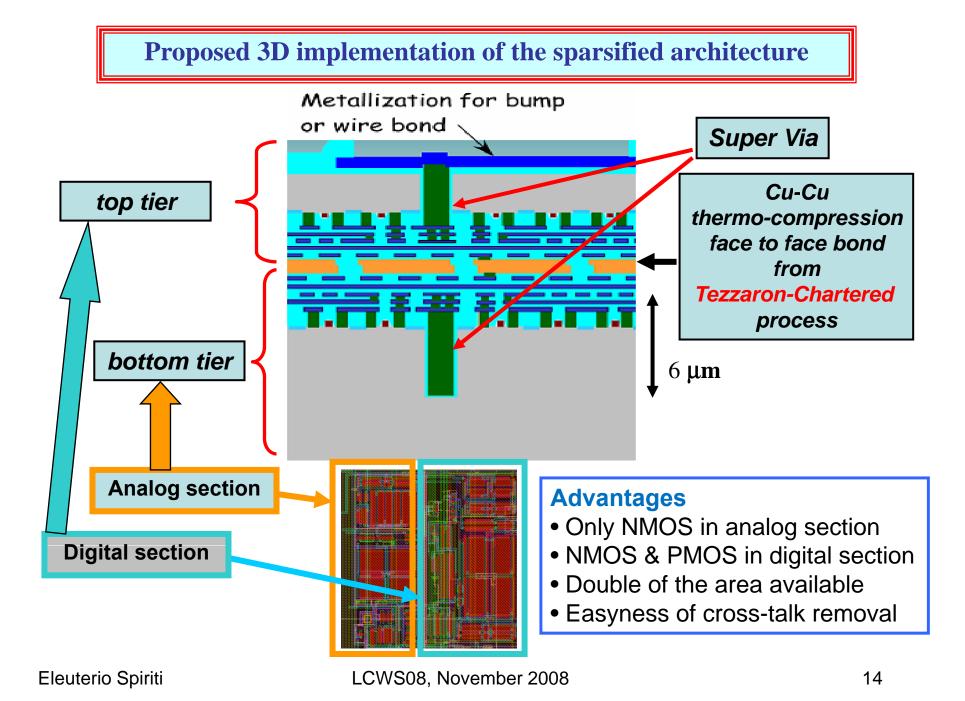

- 3. 3D implementation of the proposed sparsified architecture

- Tezzaron/Chartered 3D implementation, supported by the INFN P-ILC/VIPIX projects (FNAL-IN2P3-INFN collaboration)

- 4. Conclusions

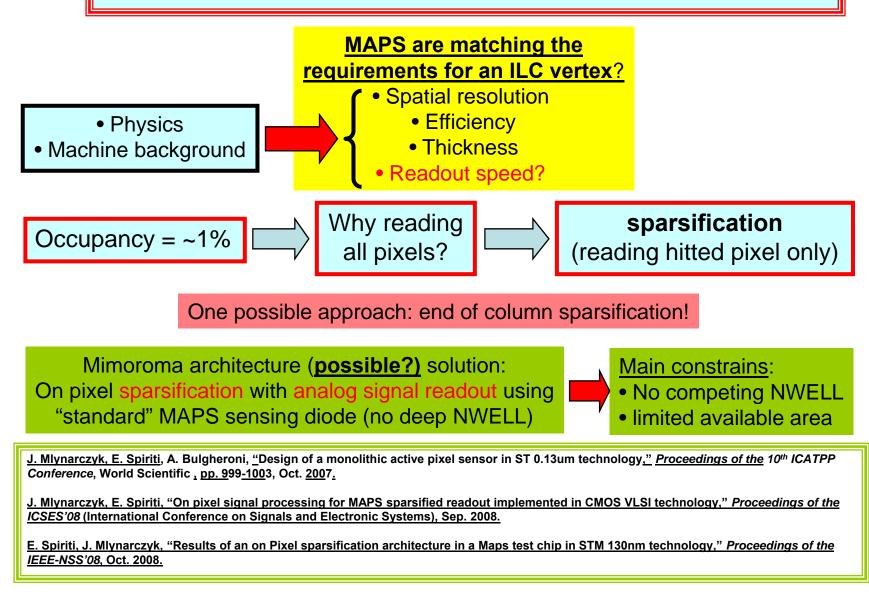

#### **Basic motivation for the proposed sparsified architecture**

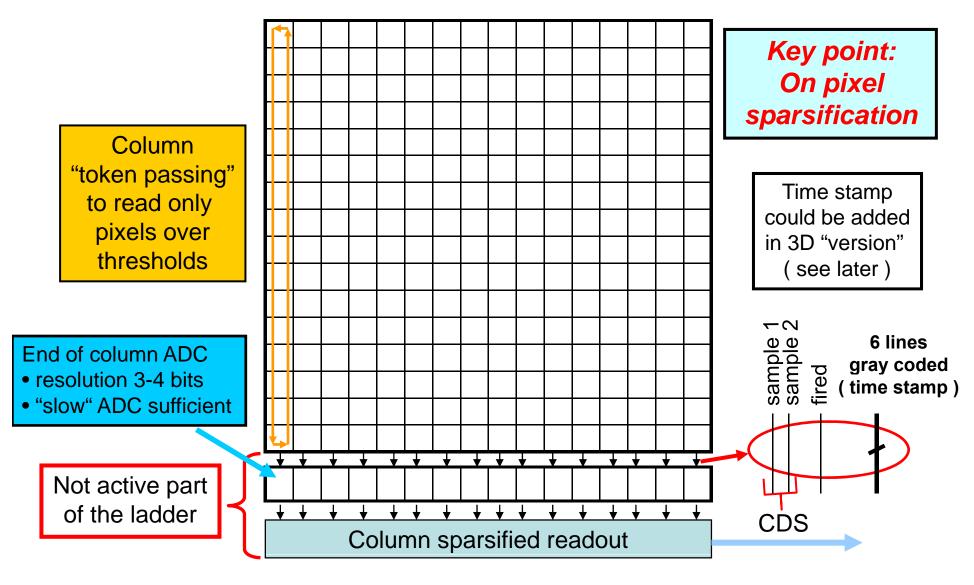

#### **Overall ladder possible readout architecture**

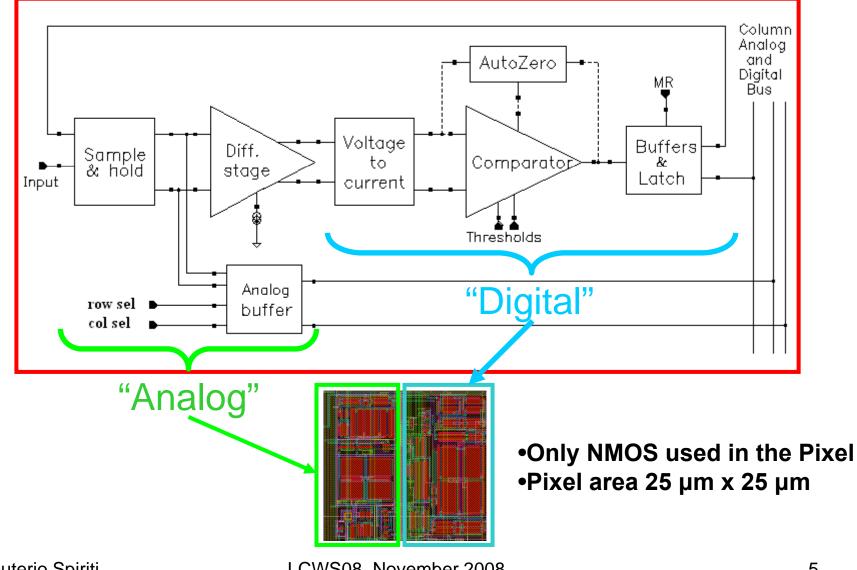

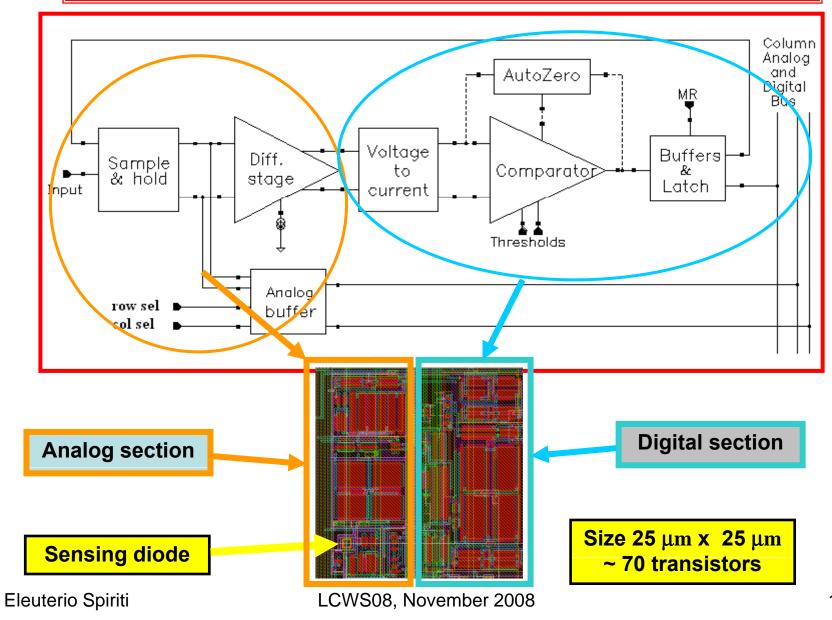

## Sparsified pixel architecture

## Mimoroma2 chip: main goals and constrains

- Characterization of the signal (epitaxial thickness and quality) level provided by the STM 0.13  $\mu m$  technology

- Implementation of an on-pixel sparsification architecture test structures (different sub-blocks)

- 1. Only NMOS transistors: no competing n-wells

- 2. Small available area (pitch 20-25  $\mu$ m)

- 3. Common threshold for all pixels in a chip

- 4. Threshold voltage and curren mismatch in submicron CMOS

- 5. Noise:

- **Temporal noise**

- □ White and 1/f noise

- **Charge injection**

- **Digital to analog cross-talk**

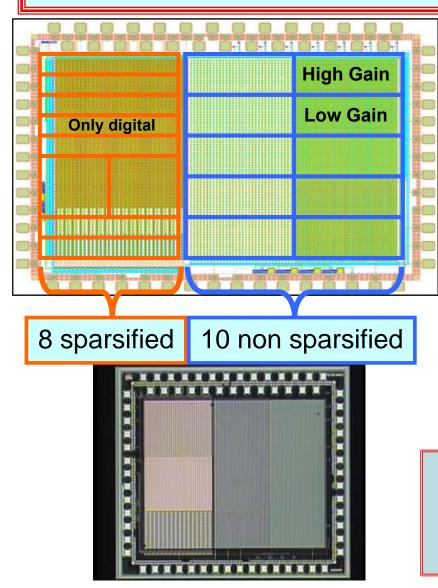

## Mimoroma2 chip layout

# Different parameters for the non sparsified part of the chip

- ✓ Five 32x16 pixels arrays with 20x20 µm size

- $\checkmark$   $\;$  Five 64x32 pixels arrays with 10x10  $\mu m$  size

| Parameter             | Value 1     | Value 2         |

|-----------------------|-------------|-----------------|

| Pixel structure       | ЗT          | SB              |

| Pitch                 | 20 µm       | 10 µm           |

| Diode<br>dimension    | 1 μm x 1 μm | 1.5 μm x 1.5 μm |

| SF transistor<br>size | Small gain  | Large gain      |

| Power supply          | 2.5 V       | 1.2 V           |

#### 8 sparsified pixel subarray

two 8x32 pixel arrays (1.2V,2.5V) only analog part two 16x16 pixel arrays (1.2V,2.5V) without autozero two 8x32 pixel arrays (1.2V,2.5V) only digital part one 8x32 pixel arrays only digital part with autozero one 8x32 pixel arrays complete pixel with autozero

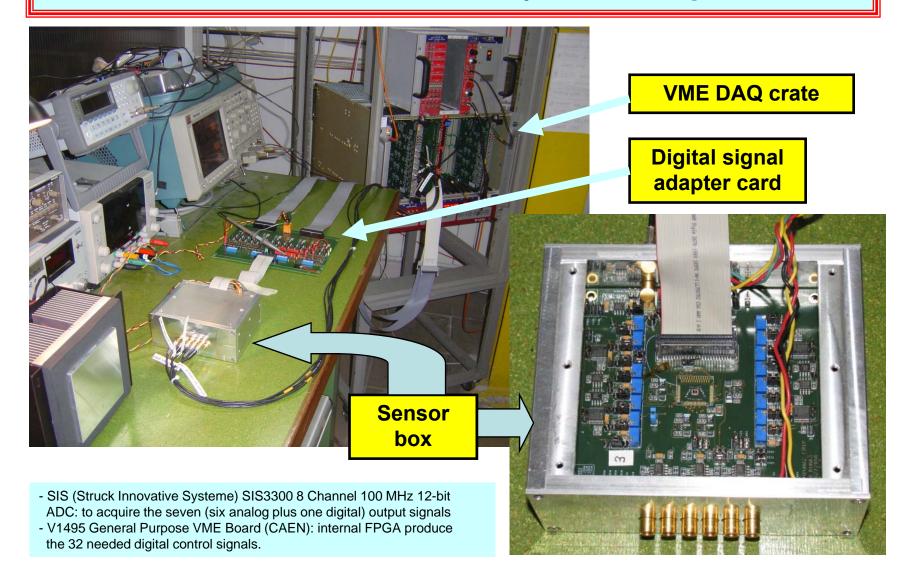

## Mimoroma2 laboratory test set-up

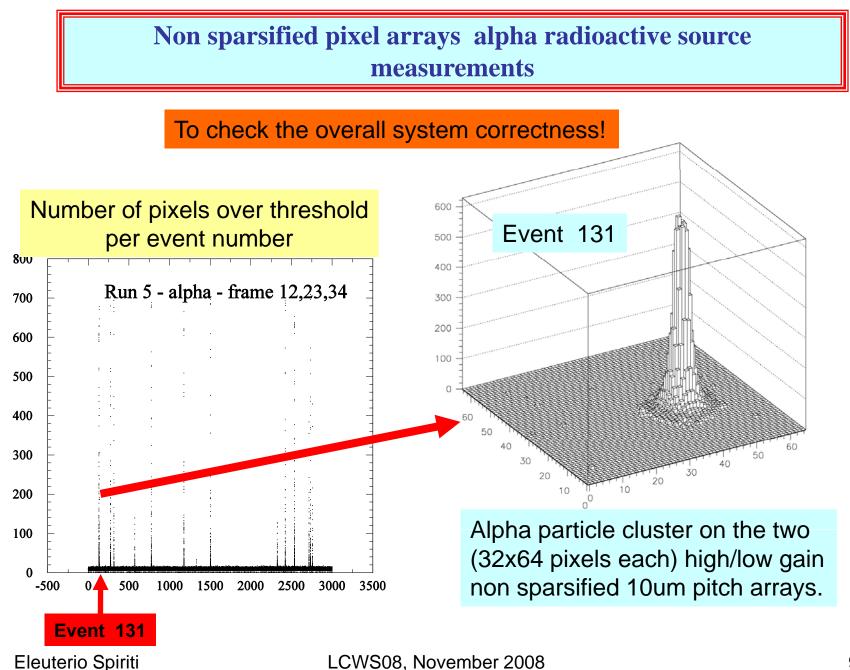

#### Non sparsified pixel arrays CCE (Charge Collection Efficiency) measurements

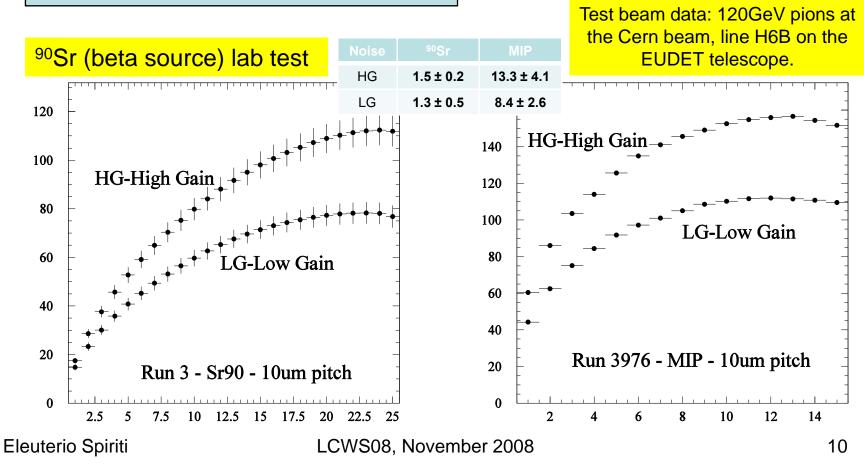

#### **Qualitative results for test beam!!!**

Based on a preliminary run (accelerator fault).

- noise ~ ten times the lab one

- missing synchronization with the telescope

Eleuterio Spiriti

LCWS08, November 2008

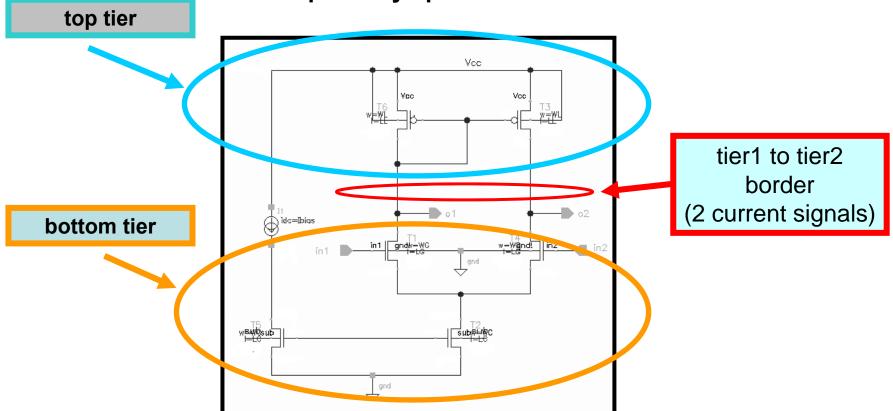

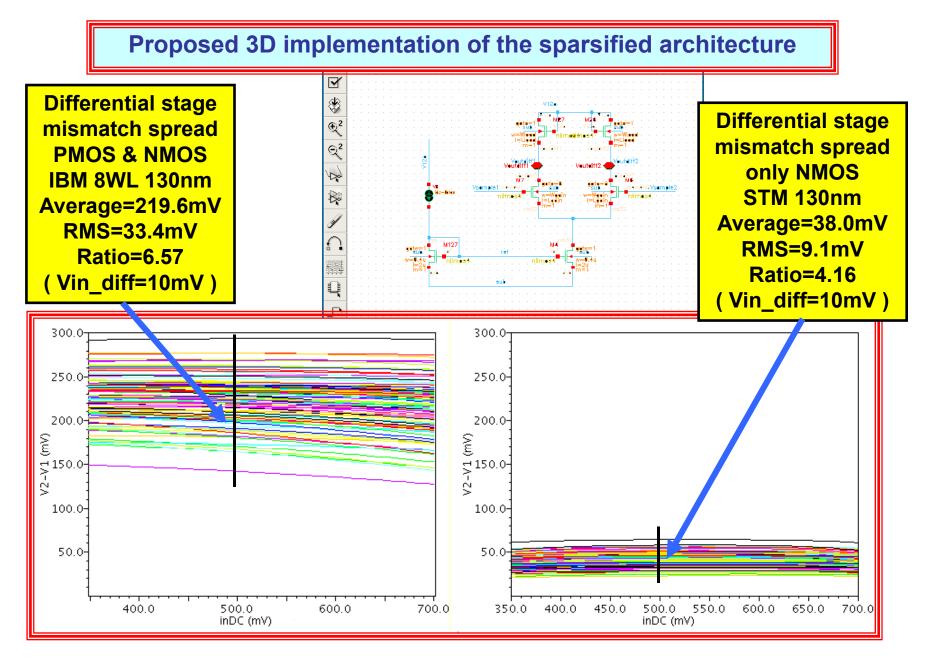

#### **Proposed 3D implementation of the sparsified architecture**

#### **Proposed 3D implementation of the sparsified architecture**

A differential stage is used to supply the signals from the sample & hold to the discriminator and the following digital circuitry. How to possibly split it in a 3D version!

Eleuterio Spiriti

LCWS08, November 2008

## Conclusions

- Mimoroma1 was a tremendously useful exercise in MAPS design and testing.

- Key point to use MAPS to built vertex detectors in new accelerators experiments could be on-pixel sparsification.

- First results of the Mimoroma2 on-pixel signal processing architecture are promising (even more than expected).

- The autozero correction technique could be of great help for threshold spread reduction.

- 3D solution could strongly improve the performances.

- Most of the tests still to be done (second test beam planned).