# SiD Tracker Readout: Context for Cable Design

Tim Nelson - SLAC

SiD Tracker Pigtail Cable Review

May 29, 2008

$\oplus$

# Outline

## SiD tracker hardware R&D

## The KPiX readout concept

## SiD barrel tracker sensor prototypes

## Design requirements for readout cable

## Key Hardware R&D Driver

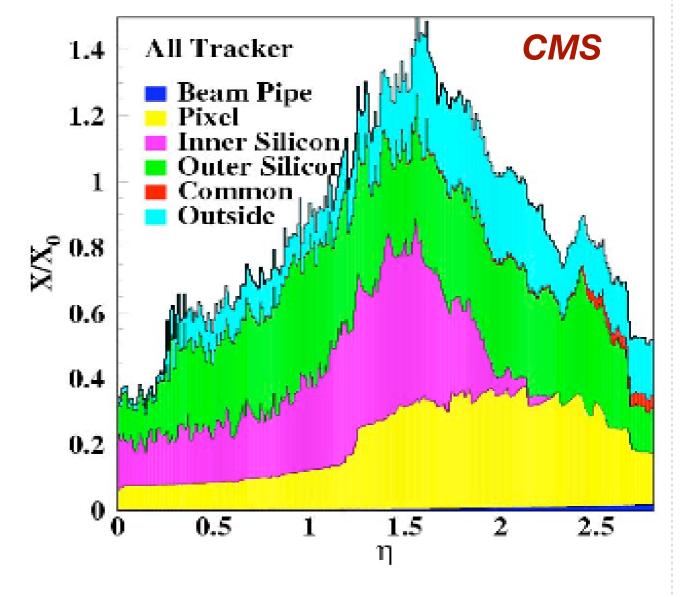

Large silicon trackers (ATLAS, CMS) have been too massive for the physics mission of the ILC

This issue drives nearly all hardware R&D for solid state tracking at the ILC

## **Reducing Material**

## Cooling: eliminate

- Readout / Power: reduce

- 🔒 Chips

- 🔒 Hybrids

- 🔒 Cables

- Support: minimize

Avoid unnecessary redundancy

### ATLAS SCT

# The Hows and Whys of ILC Readout Electronics

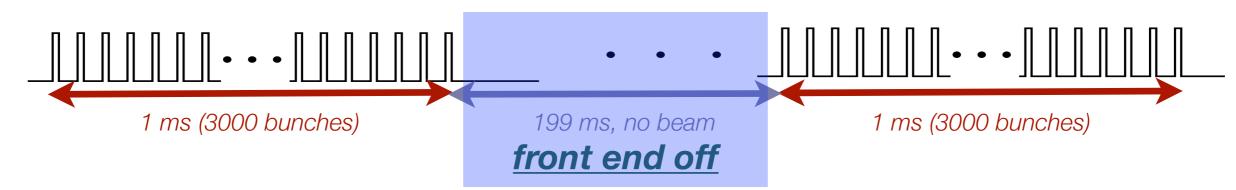

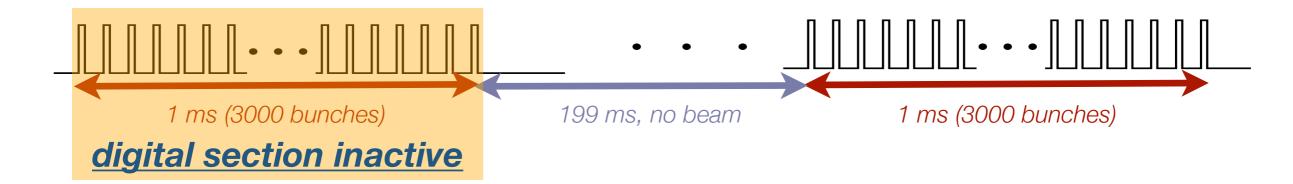

- Pulsed operation of front end results in ~100X reduction in dissipated power

- Minimizes services: cooling, cable plant

- Many ILC detector ideas don't work without pulsed power

- dense Si-W calorimetry

- Iow-mass tracking

- Pulsed power is a common element of many ILC readout efforts

- B The SiD realization of this an ASIC called **KPiX**: achieves  $20\mu$ W/channel avg.

- ~600W total for 30 million channels: tracker can be gas cooled

## What is Special About KPiX?

KPiX stores signals acquired during a bunch train in 4 analog buffers

- hits are time-stamped to individual bunch crossings, reducing background susceptibility

- digitization and readout occur between bunch trains, minimizing potential for pickup of digital activity on analog front end (only synchronous LVDS clock): allows chip to be more closely coupled to detector electrodes

- Along with an enormous repertoire of built-in capabilities and flexibility of configuration, KPiX may be bump-bonded directly to sensors

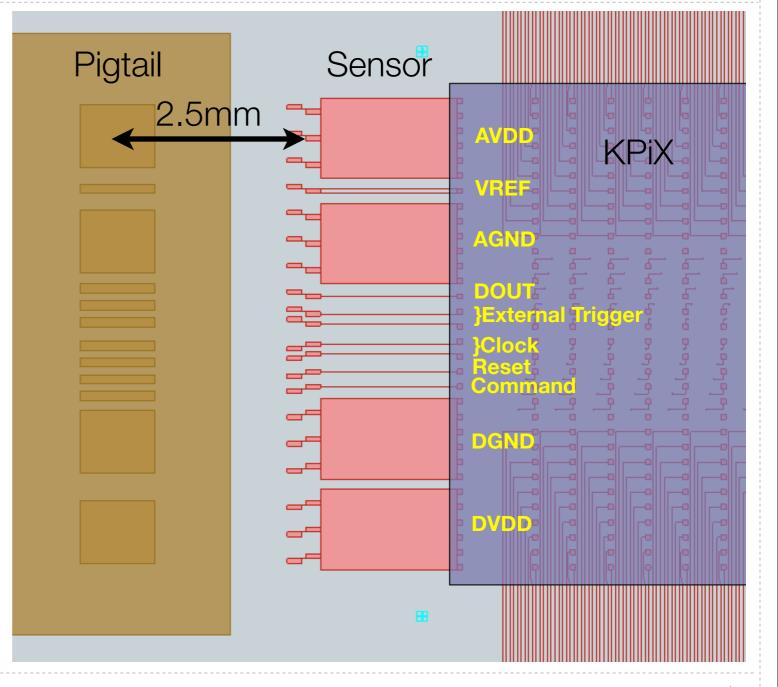

# SiD Tracker Module Design

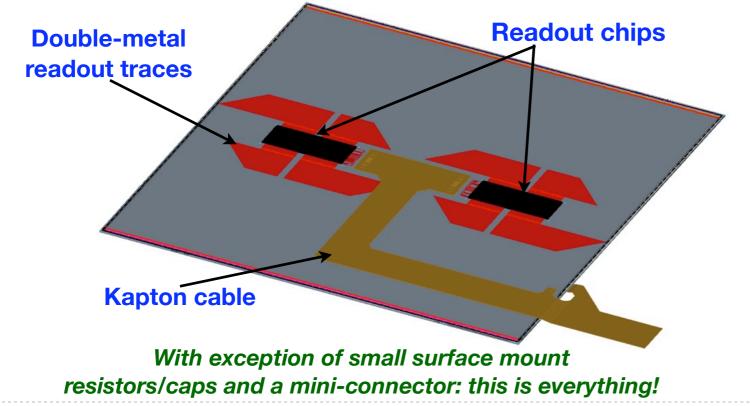

An aggressive approach to reduction of readout material:

- bump-bonded ASIC with double-metal readout: *no hybrid circuit board!*

- Short, single-sensor modules ensure low capacitance  $\Rightarrow$  high signal/noise

- negligible single-hit inefficiency reduces reliance upon redundancy in layout

- excellent single-hit resolution provides best possible momentum resolution

- per-sensor occupancy from physics+noise is small, simplifying pattern recognition

**Power and readout must** also be routed on double-metal!

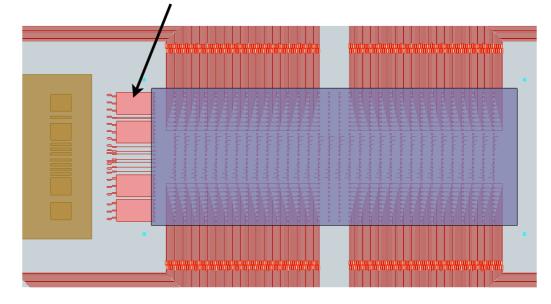

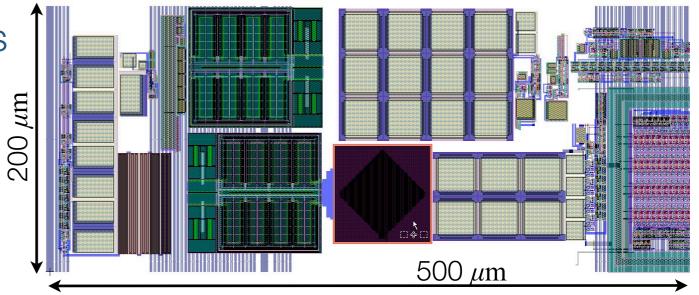

## KPiX SLAC, U. Oregon

- SMC 0.25μm CMOS

- 32×32 array = 1024 channels

- working with 2×32 prototypes

## First versions targeted only at ECal

- dynamic range switching for large charge depositions in ECal (0.05-2000 MIP range)

- bias current servo for DC coupled sensors

- lin calibration circuitry

### Other applications demand additions

- Nearest neighbor logic, high-gain feedback capacitor for tracker

- Polarity selection (GEM readout)

- External trigger for test beam

### All features tested and working

|   | -   | <br>141 |    | - | 1 |      | 61 | • | - | -  | 1 | - | - |   |   | - |       |   | - | - | ene<br>h |   | - | n i   | 1 | - |          | - |   |   | -        | 1 |   | ere<br>h | h | 1        | - |   |   | Ţ |   |   | ł          |

|---|-----|---------|----|---|---|------|----|---|---|----|---|---|---|---|---|---|-------|---|---|---|----------|---|---|-------|---|---|----------|---|---|---|----------|---|---|----------|---|----------|---|---|---|---|---|---|------------|

| ł |     |         |    |   |   | -    | 1  |   | - |    |   |   |   | - |   |   |       |   | 1 | ſ | Ŧ        |   |   |       |   |   |          | - | - |   |          |   |   |          |   |          |   | ſ | T | 1 |   |   | No. of Lot |

|   | 日月二 | -       |    |   |   |      |    |   |   | 11 | H |   |   | 1 |   |   | all n |   |   |   |          |   |   |       |   |   |          |   |   |   |          |   |   |          |   |          |   |   |   |   |   |   |            |

|   |     |         |    |   | - |      |    |   |   | -  |   | I | - |   | I | - |       | I | 1 |   | I        | 1 |   | I     | 1 |   | I        | 1 |   | 1 | I        | 1 |   | I        | 1 | 1        |   | I | I | 1 | 1 | I |            |

|   |     |         | M. |   |   | M. I | ā. |   |   | 1  |   |   |   |   |   | - |       |   |   |   | 2)<br>11 |   |   | 100 A |   |   | 플라<br>10 |   |   |   | 음!<br>10 |   | 비 |          |   | Ma<br>Ma |   |   |   |   |   |   | 1          |

KPiX64

### a single cell of KPiX

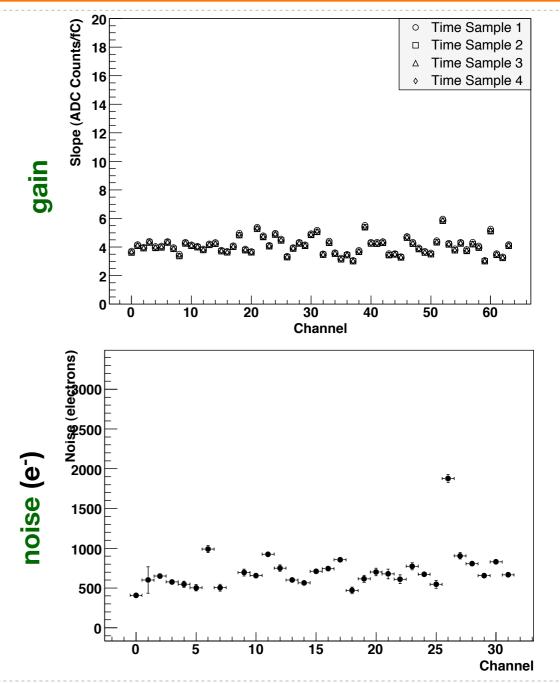

## KPiX Performance

- Each successive generation has added capabilities, improved greatly in performance.

- KPiX7 is current generation

- Good gain and threshold uniformity

- Expected noise achieved in both trigger branch <u>and</u> from ADC: ENC = 300+30\*C e<sup>-</sup>

- No major issues remain!

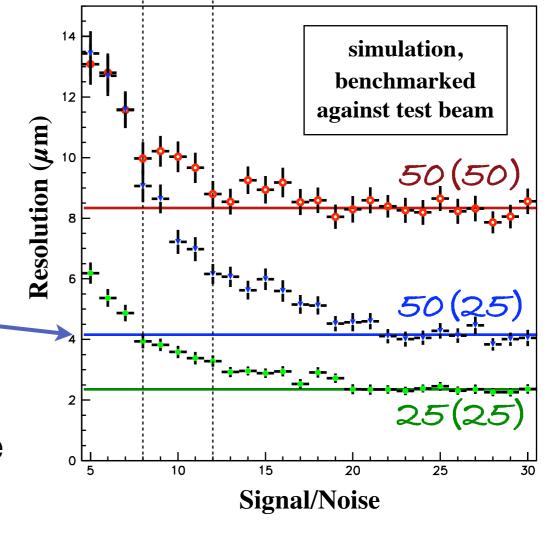

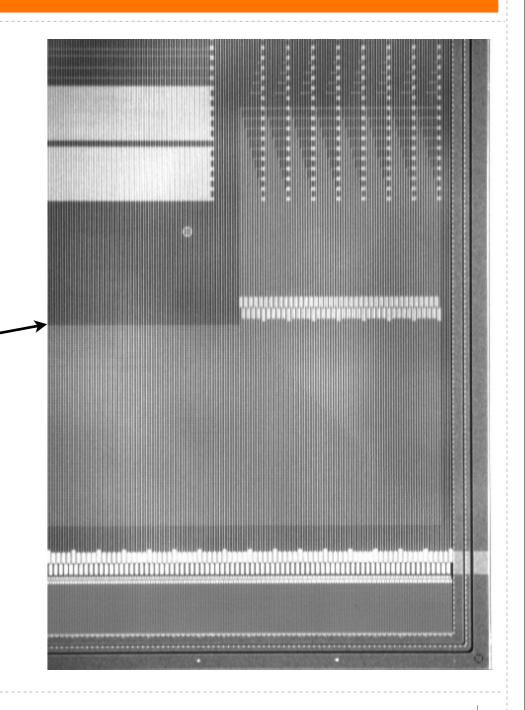

## Sensors SLAC, FNAL

Need ~30,000 sensors: keep it simple, cheap

- 👶 Single-sided p+-in-n silicon

- 👃 Largest square sensor from 6" wafer

- 🔒 Ensure high S/N

- 👶 Short strips with optimized double-metal

- Achieve best resolution for channel count

- 25 micron sense pitch, 50 micron readout: results in excellent resolution

- Minimize potential problems with double-metal power/readout scheme

- Lowest possible power/ground impedance

- Minimize coupling between LVDS clock traces and underlying strips

## readout(sense) pitch (µm)

## Double-metal Optimization

### Signal traces:

- HPK double-metal traces down to  $2\mu m$  width

- balance capacitance against series resistance, minimize variations among channels

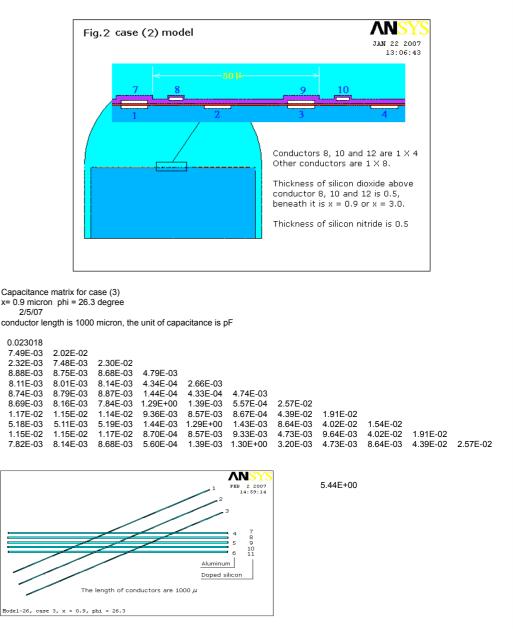

- Layout began with previously-learned lessons learned from others, proceeded through a great deal of ANSYS modeling

- 8(9)μm implant(sense strip) width,

4μm double-metal readout width:

- ♣ C=14-18 pF for 95% channels, 20 pF max

- $\clubsuit$  R < 350 Ω for all channels

- S/N = 20-25 with KPiX

The model for case 2 is plotted in Fig.2. There are 12 conductors. The capacitance matrices are listed on next page.

$\oplus$

# Double-metal Optimization

### **Power/readout traces:**

- Want shortest, widest traces for power, ground: 0.08 Ω/pair (round-trip spec is 1Ω max.)

- integration over odd number of clock edges will introduce ~3500 e- pedestal shift on channels underneath bond pads from capacitive coupling

- ➡ one clock per BX?

- clock rate faster than shaper response?

- somewhat smaller is shift due to voltage fluctuations on power and ground traces if assumed to be completely unbalanced

## Simulations cannot be trusted at this level: we need to try it!

| LVDS clo<br>4 micro<br>60 micro | ock pair{ |      |  |                  |                 |                 |                 |                |                                           |

|---------------------------------|-----------|------|--|------------------|-----------------|-----------------|-----------------|----------------|-------------------------------------------|

|                                 |           | DVDD |  |                  |                 |                 |                 |                |                                           |

|                                 |           |      |  | )100100<br>00000 | )00000<br>00000 | 100001<br>00000 | 100010<br>00000 | 10000<br>00000 | 1000000<br>000000000000000000000000000000 |

# HPK Prototype Sensors

## Received sensors from HPK on March 30.

- 20 full-sized tracking sensors for module prototypes with full-sized KPiX

- 40 smaller sensors for testing double-metal readout with smaller KPiX variants

- Quality excellent: bad channels <1/10000 (!!)</p>

- Appears that there were no yield problems

- Will be tested in the coming weeks

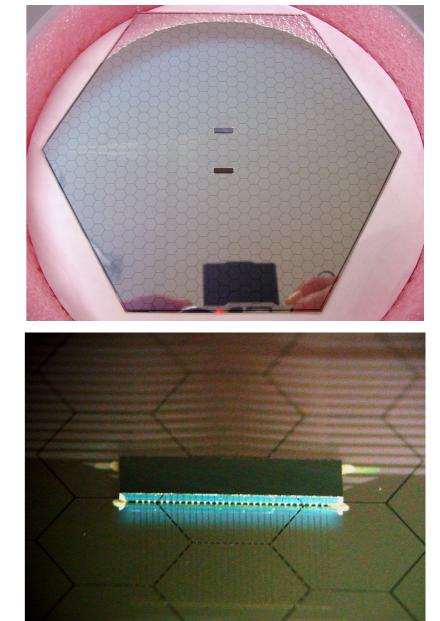

## KPiX Bump Bonding UC Davis

## Bump-bonding is a critical process for our designs

- At these pitches, gold-stud bumping becomes feasible, especially attractive for small-run R&D

- First attempts by Palomar Technologies on KPiX-5 and ECal prototype sensors somewhat successful

- Only 96% yield on first two test chips

- Corrosion problem between epoxy used for making final bond and Al pads: at worst we will have to add Ti-W as one would for indium bumping

Encouraging progress for an unfamiliar technique: anticipate using this process for prototype modules

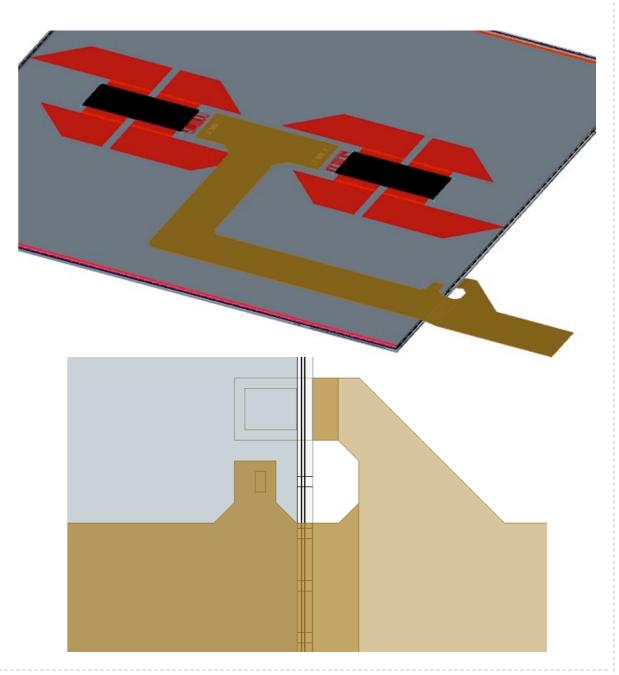

# Pigtail Cable UNM

- Pigtail glues to sensor, wirebonds to double-metal, bias tab at edge

- Connects to straight extension cable running to ends of cylinders (up to 1.7m)

- ¼-ounce copper on 50µm Kapton

- 2 power+ground pairs

- 8 narrow control/readout lines

- HV pair for sensor bias

- cable width 8mm

$\oplus$

# Pigtail Details

Large pads for wirebonding

- Important to consider details that minimize material

- 🔒 Meshed ground plane

- 🔒 Thinner Kapton?

- Important to design as robustly as possible

- 👶 Connectors

- Radiused inside corners?

$\ominus$

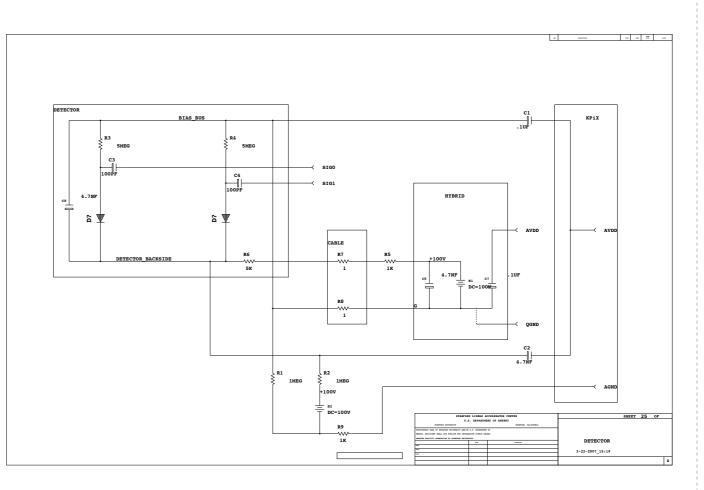

# Missing Details

- Critical to define surface mount components required for bypassing, termination

- Dieter Freytag drew up a "maximal" scheme: not clear that all of these components will be required

- At the prototyping stage, we want to have all options available for testing different configurations

- Provisions for these components are a key subject to be reviewed: input from Dieter is necessary

# Summary

- The pigtail is a rather simple item mechanically, only a few questions

Thickness

- 🔒 Nature of ground plane

- Robustness of connector and sharp inside corners

- The key details are electrical

- How are HVGND/AGND/DGND connected?

- How are signals terminated?

- How does bypassing work?

- These are prototypes intended for R&D on this readout scheme: we would prefer as much flexibility in configuration as we can have without creating fundamental problems.