IN 2 P 3

# HARDROC2

June 13rd, 2008

Orsay Micro Electronic Group Associated

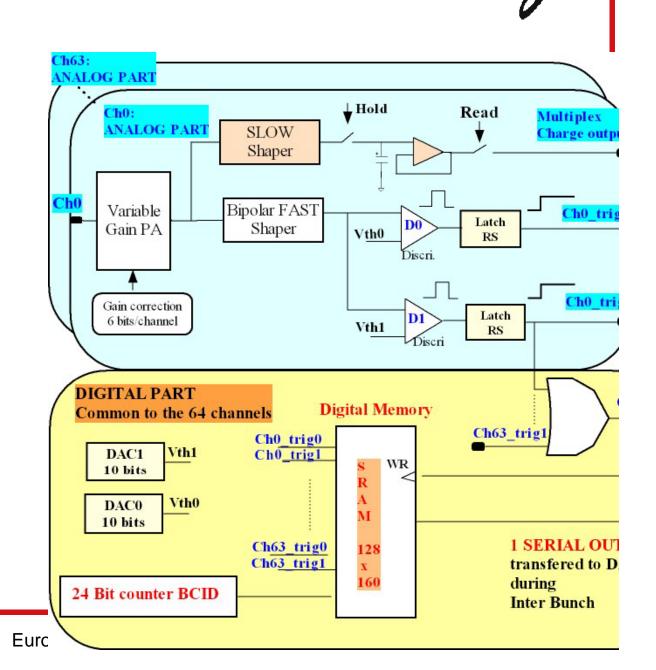

## HaRDROC1 architecture

- Variable gain (6bits) current preamps (500hm input)

- One multiplexed analog output (12bit)

- Auto-trigger on 1/2 MIP

- Store all channels and BCID for every hit.

Depth = 128 bits

- Data format : 128(depth)\*[2bit\*64ch +24bit(BCID)+8bit(He ader)] = 20kbits

- Power dissipation : 1.5 mW/ch (unpulsed) > 15µW with 1% cycle

- Large flexibility via >500 slow control settings

()mega

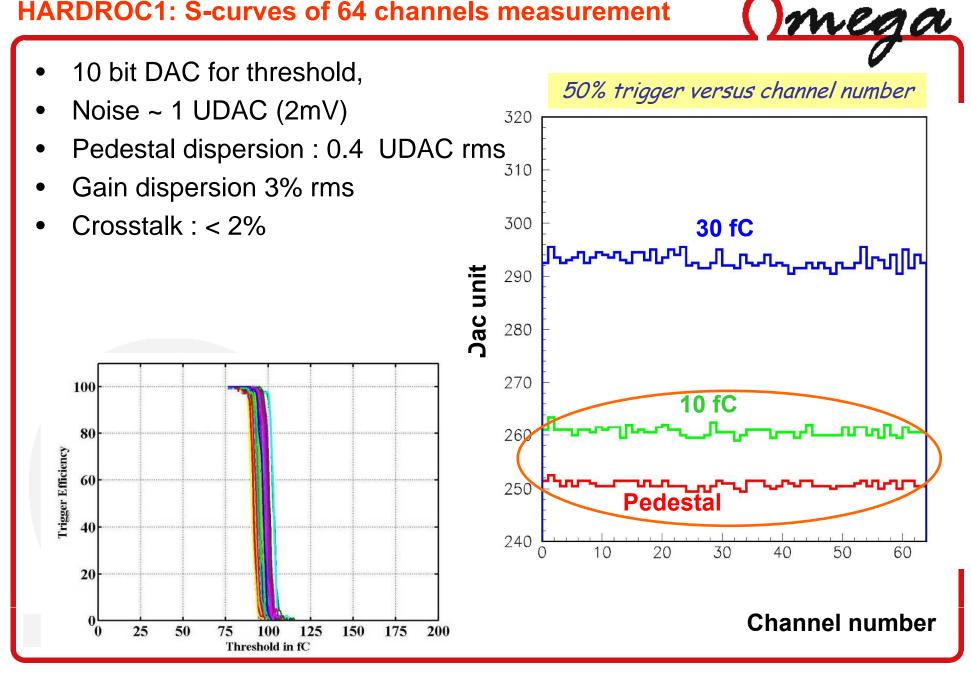

#### HARDROC1: S-curves of 64 channels measurement

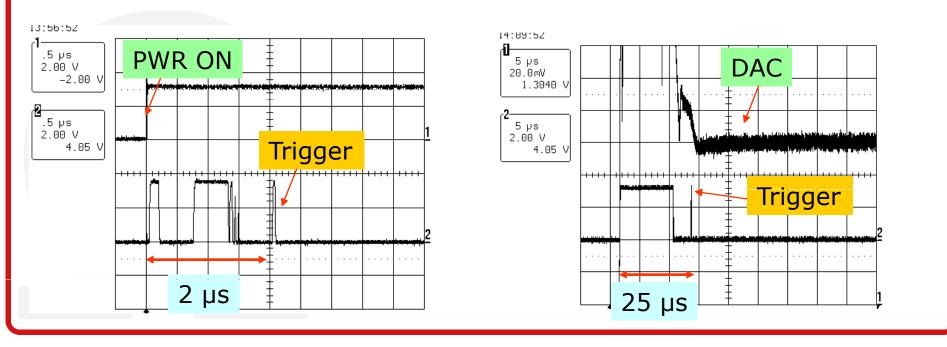

#### HARDROC1: Power pulsing measurement

- PWR ON: ILC like (1ms,199ms)

- All decoupling capacitors removed : difficult compromise between noise filtering and fast awake time

- Awake time :

- Analog part = 2 us

- DAC part = 25 us

- 0.5 % duty cycle achieved, now to be tested at system level

(<u>)mega</u>

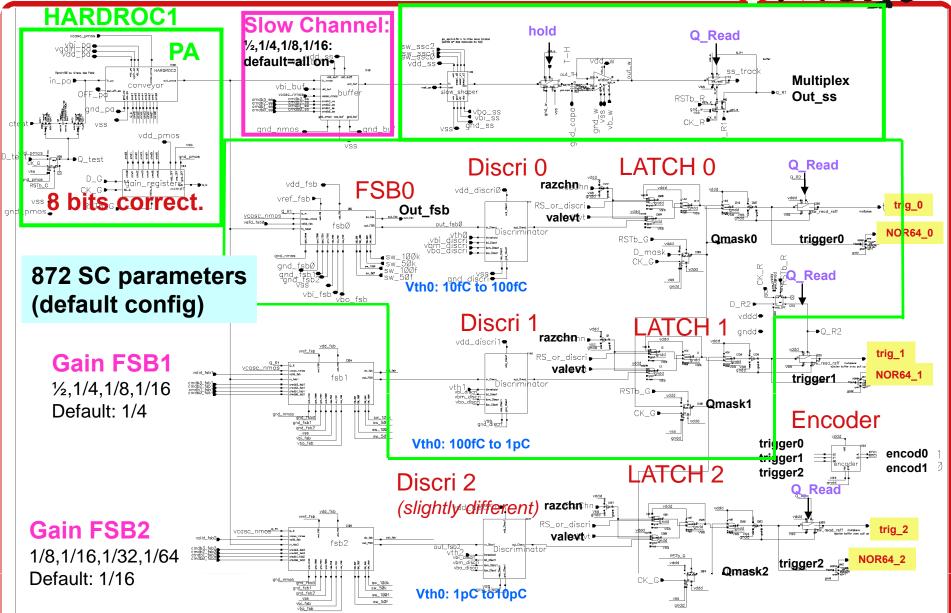

### **DESIGN of HARDROC2**

- Hardroc2 submitted: mid june 08

- ANALOG PART:

- Dynamic range extension

- Gain correction: 8 bits instead of 6

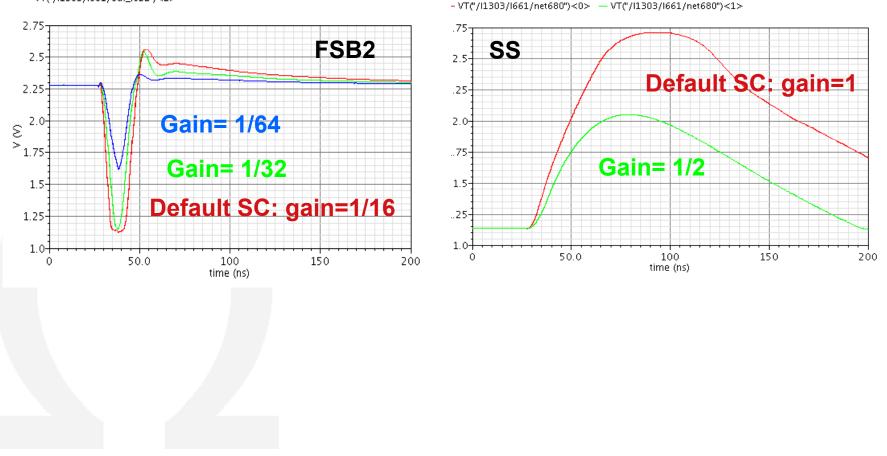

- 3 shapers and 3 thresholds (=> 3 DACs):

- 10 fC, 100fC, 1pC (megas)

- 100fC, 1pC, 10pC (GRPC)

- Encoder: trig0<i>, trig1<i>, trig2<i> outputs encoded to encod0<i> and encod1<i>

- Bandgap redesigned

#### • DIGITAL PART:

- Correction of the minor bugs of HR1:

- mask, memory pointer: dummy frame

- Shift registers improvements (multiplex, default, extra FF)

- Bypass on critical signals

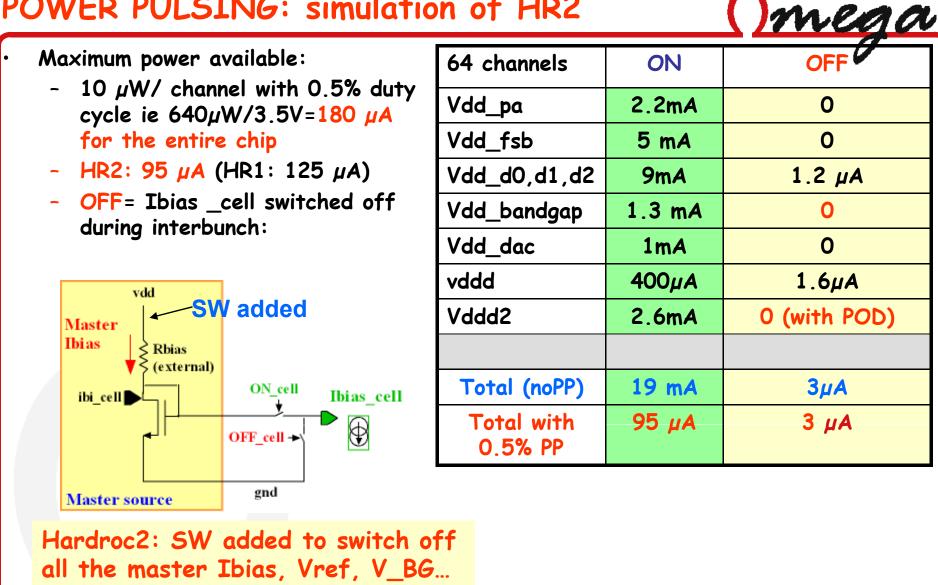

#### • Power consumption:

- Bandgap + ref Voltages + master I: power pulsed

- POD module (power budget)

- HARDROC2= HARDROC1 + modifs

⇒ HARDROC1= BACKUP

nega

Slow

Data

input

Select

control

Read

#### HARDROC2: analog part

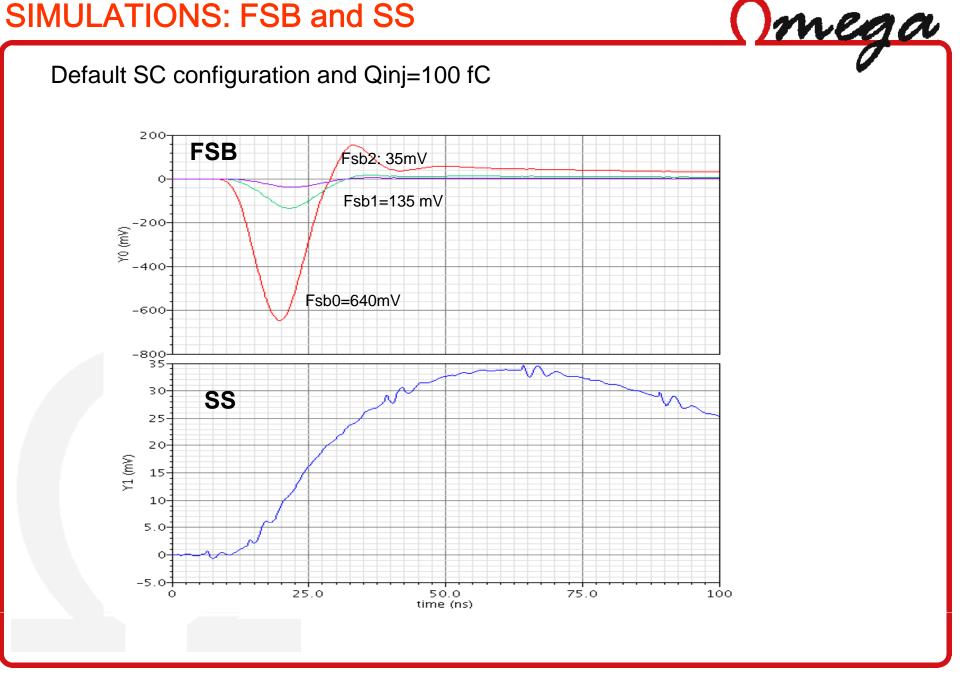

#### **SIMULATIONS: FSB and SS**

#### SIMULATIONS: FSB and SS

<u> Mega</u>

Transient Response

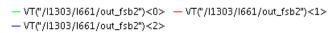

#### Different SC configurations (gain) FSB2 and SS Qinj=10 pC

Transient Response

June 13rd, 2008

European DHCAL meeting, NSM

# **POWER PULSING:** simulation of HR2

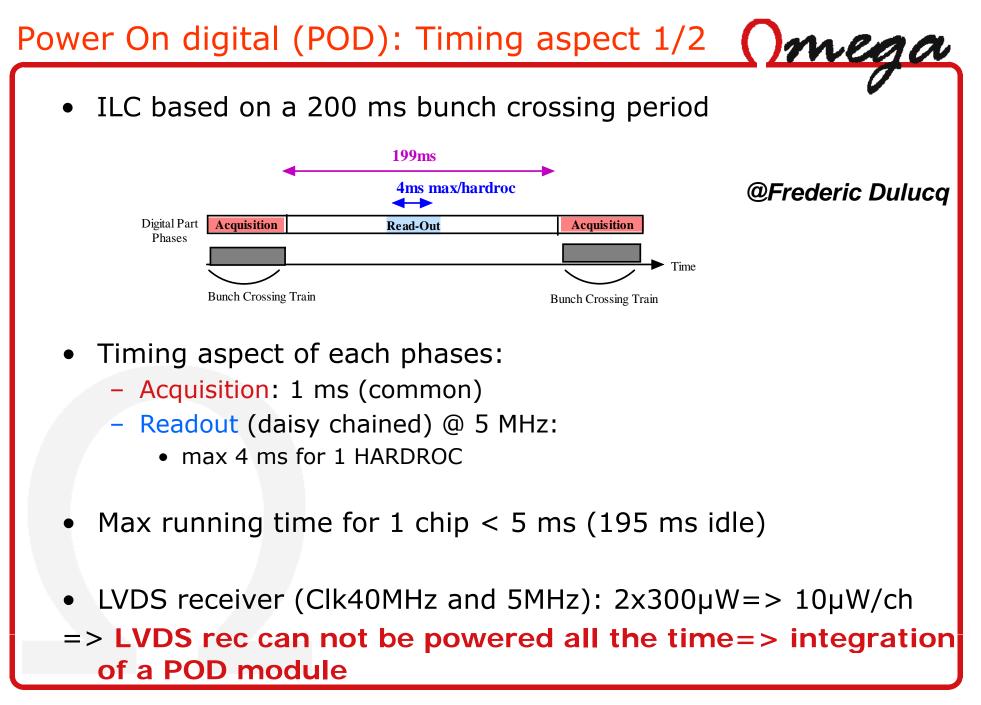

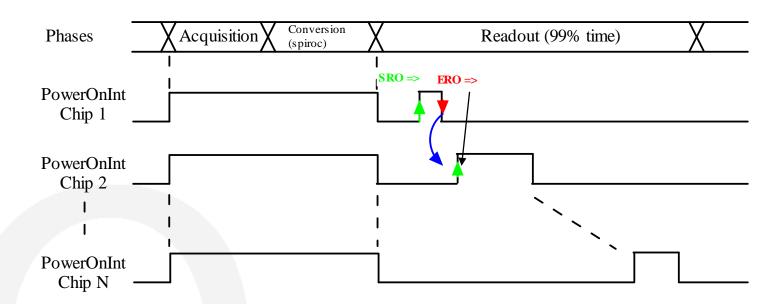

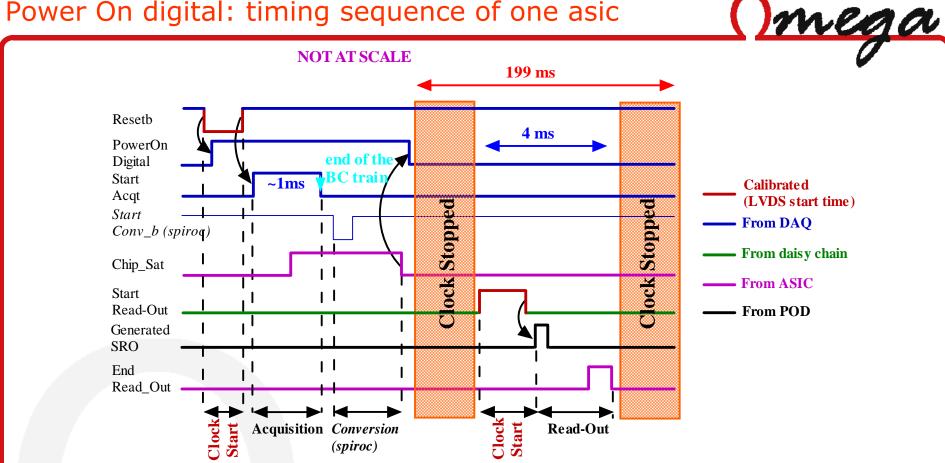

## Power On digital: Timing aspect 2/2

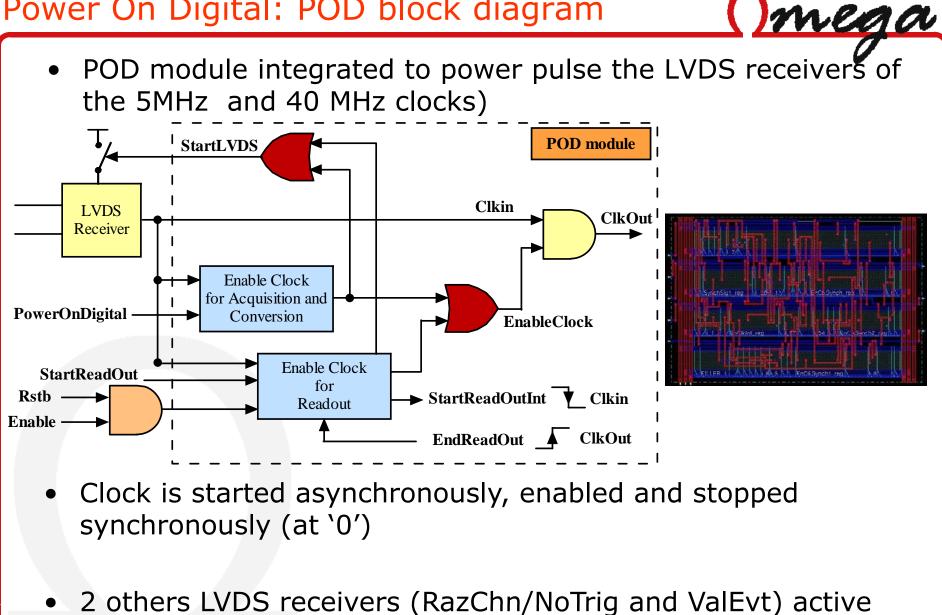

• clocks and LVDS receiver must be power pulsed to meet power budget.

- 2 operation modes :

- Acquisition, (Conversion) → common to all chips and managed by DAQ

- Readout → daisy chained managed by StartReadOut (sro) and EndReadOut (ero)

()mega

## Power On Digital: POD block diagram

during PowerOnAnalog (during bunch crossing)

#### Power On digital: timing sequence of one asic

- Some security added:

- − StartReadOut managed asynchronously → low pass filter added

- Possibility to use StartReadOut instead of the one generated by POD = POD can be bypassed by SC

- PowerOnDigital can be set to '1' by SC => can force the clock

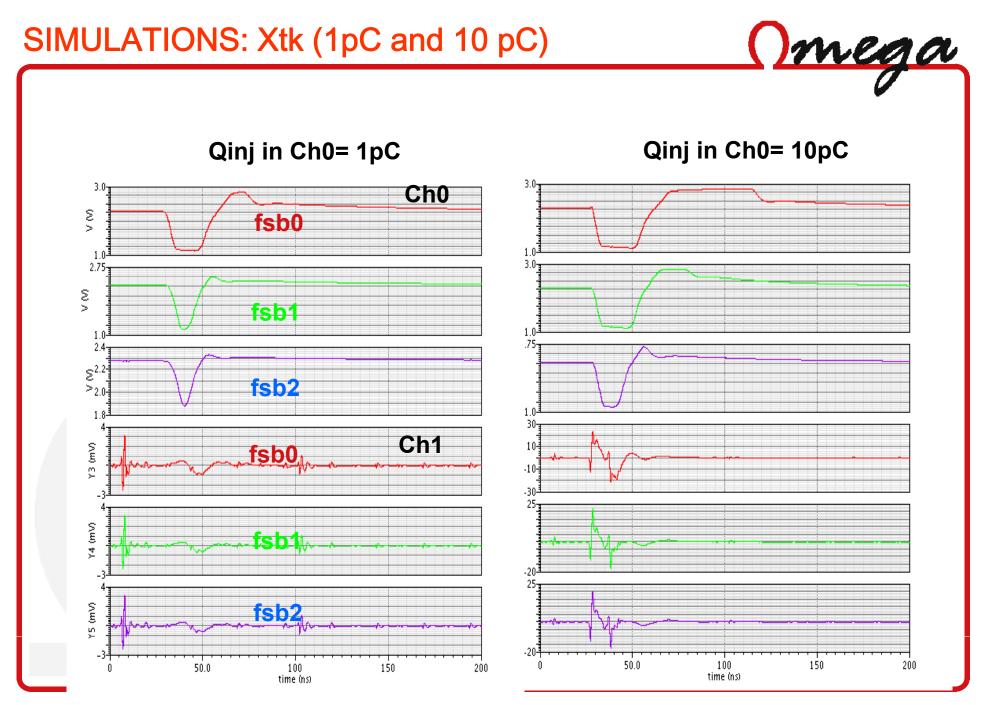

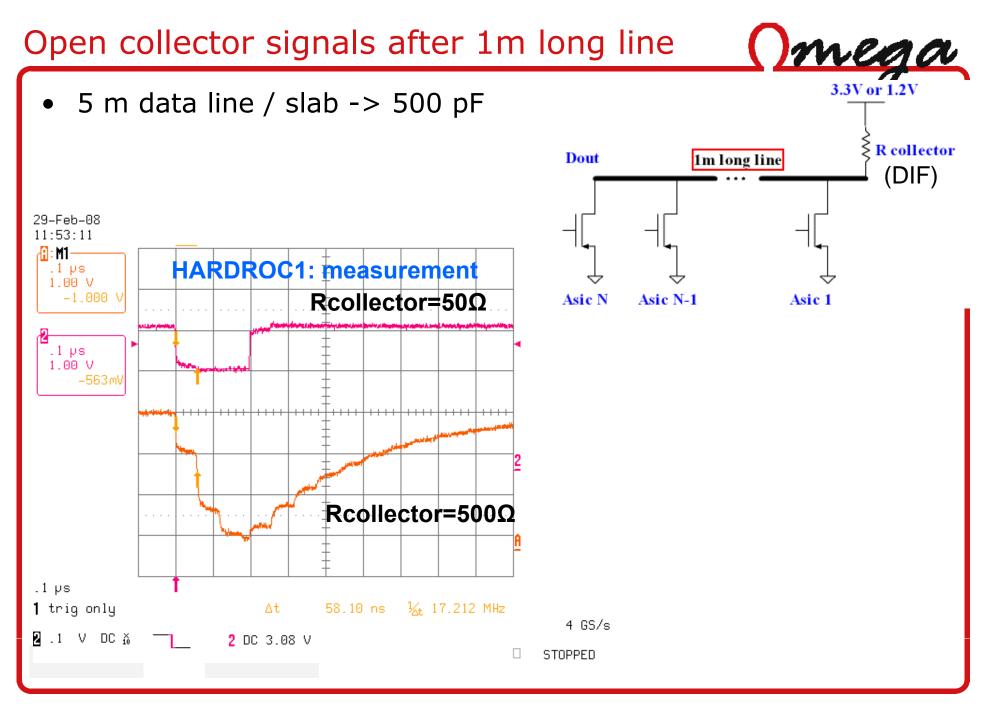

# SIMULATION of HR2 OC signals

()mega Hardroc2: change driver Transient Response transistor size in ASICs 4.0 In\_OC@5 MHz **POWER:** • 3.5  $- 40 \text{mVx} 1 \text{V} / 50 \Omega = 800 \mu \text{W}$ 3.04 ε<sup>2.5</sup>· ε<sub>2.0</sub>. - 800µWX4ms/200ms=16µW > 1.5- $- 16\mu W/64 = 0.25\mu W/ch$ 1.00.0 1.2 r=5Ø Out\_OC , 500 pF load 1.0-●out\_OC .8 ε 1000/0.35 EN OC in OCI 100 200 300 400 Jrtn  $=GN\Gamma$ time (ns) V=40 mV

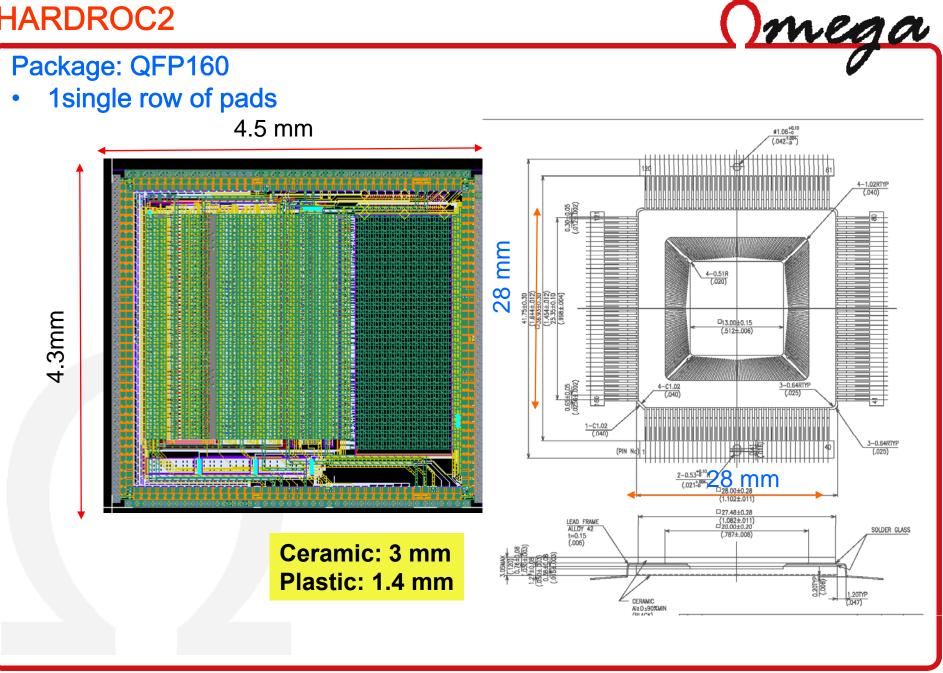

#### HARDROC2

#### **CONCLUSION**

- HaRDROC2 prototyped in june 08

- Keep HARDROC1 basic architecture and backward compatibility

- Have 3 very different thresholds

- Move bonding pads to single row (QFP160 package)

- + many small changes

(gain accuracy, power pulsing...)

- Integration of the « POD » module: possible bypass

- Area : 20 mm2

- HaRDROC2 dies expected mid september

mega