# A 130nm CMOS Digitizer Chip for Silicon Strips readout at the ILC

INSTITUT NATIONAL DE PHYSIQUE NUCLÉAIRE ET DE PHYSIQUE DES PARTICULES

#### **Thanh Hung Pham**

on behalf of

W. Da Silva<sup>1</sup>, J. David <sup>1</sup>, M. Dhellot<sup>1</sup>, D. Fougeron<sup>2</sup>, R. Hermel<sup>2</sup>, J-F. Huppert<sup>1</sup>, J-F. Genat<sup>1</sup> F. Kapusta<sup>1</sup>, H. Lebbolo<sup>1</sup>, F. Rossel<sup>1</sup>, A. Savoy-Navarro<sup>1</sup>, R. Sefri<sup>1</sup>, S. Vilalte<sup>2</sup>, A. Charpy<sup>1</sup>, C. Ciobanu<sup>1</sup>, A. Comerma<sup>3</sup>, D. Gascon<sup>3</sup>,

A.D Barrientos<sup>3</sup>

<sup>1</sup>LPNHE Paris, <sup>2</sup>LAPP Annecy, <sup>3</sup>University of Barcelona

Work in the framework of the SiLC (Silicon for the Linear Collider), R&D Collaboration and the EUDET I3-FP6 European Project

Eudet annual meeting JDET ANNUAL Q & Co 08th 2008, NIKHEF

**NIKHEF**

# Outline

- > The 4-channel evaluation chip in 130nm CMOS

- > The 88 channel chip

Conclusion

# Silicon strips detectors at the ILC

Envelope around the central tracking device

Assume:

- A few 10<sup>6</sup> Silicon strips

- 10 30 cm long,

- Thickness 200–300 μm

- Strip pitch 50 μm

- AC coupled (DC coupled if necessary)

→ Millions of channels Integration of k-scale channels readout chip

## Silicon strips data

- Pulse height: Cluster centroid to get a few µm position resolution

Detector pulse analog sampling

- Time: 150-300 ns for BC identification

Shaping time of the order of the microsecond depending upon strip length (capacitance)

$\succ$

# Outline

Silicon strips readout

> The 4-channel evaluation chip in 130nm CMOS

> The 88 channel chip

Conclusion

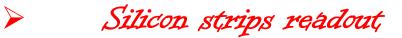

# Functionalities to be integrated

#### Full readout chain integration in a single chip

- Preamp-shaper

- Sparsification

- Sampling

- Analog event buffering:

- On-chip digitization

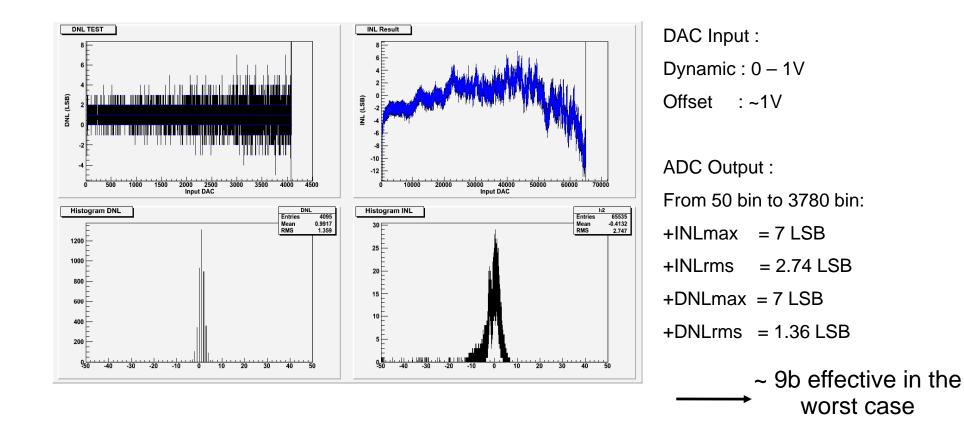

Trigger decision on analog sums 8-deep sampling analog pipe-line Occupancy: 8-16 deep event buffer 10-bit ADC

- Buffering and pre-processing:

- Centroids, least square fits, lossless compression and error codes

- Calibration and calibration management

- Power switching (ILC duty cycle)

# Front-End chip numbers

Goal: Integrate 512-1024 channels in 90nm CMOS:

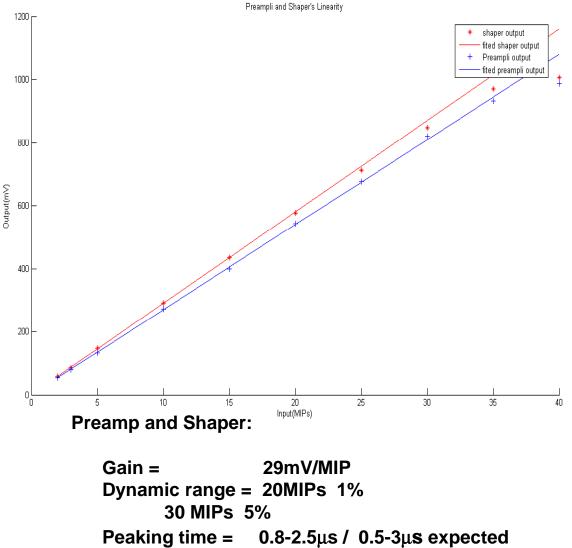

- Amplifiers: 30 mV/MIP over 30 MIP range

- > Shapers: ranges: 500ns-3 $\mu$ s

- Sparsifier: Threshold the sum of 3-5 adjacent channels

- Samplers: 8 samples at 80-640ns variable sampling clock period

- Event buffer 8-16 deep

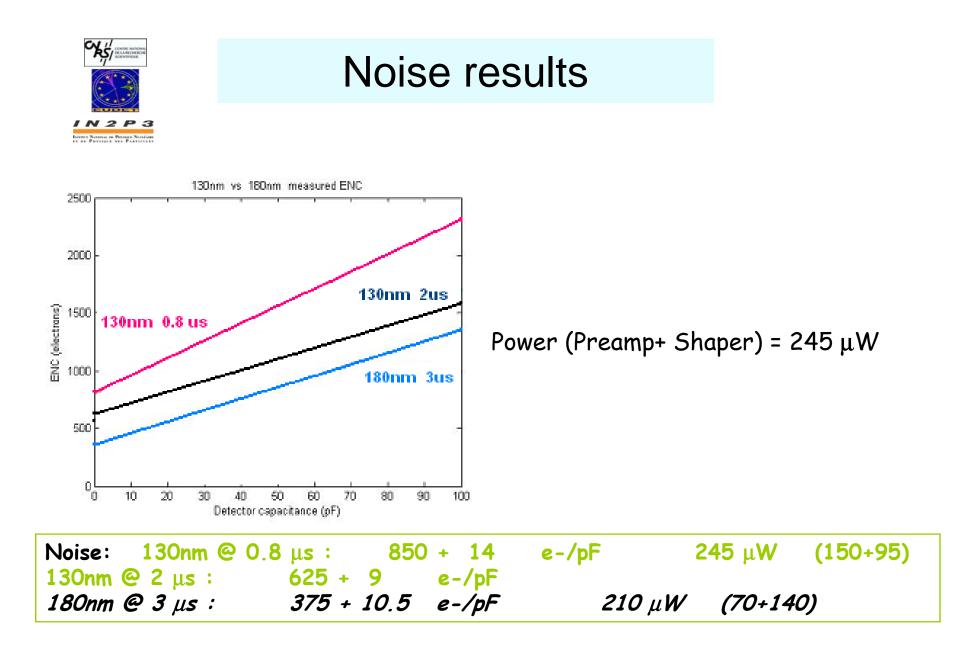

- Noise baseline: Measured with 180nm CMOS: 375 + 10.5 e-/pF @ 3 μs shaping, 210μW power S/N ~ 20

- ➢ ADC: 10 bits

- Buffering, digital pre-processing

- > Calibration

- Power switching can save a factor up to 200

- ILC timing: 1 ms: ~ 3000 trains @ 360ns / BC 199ms in between

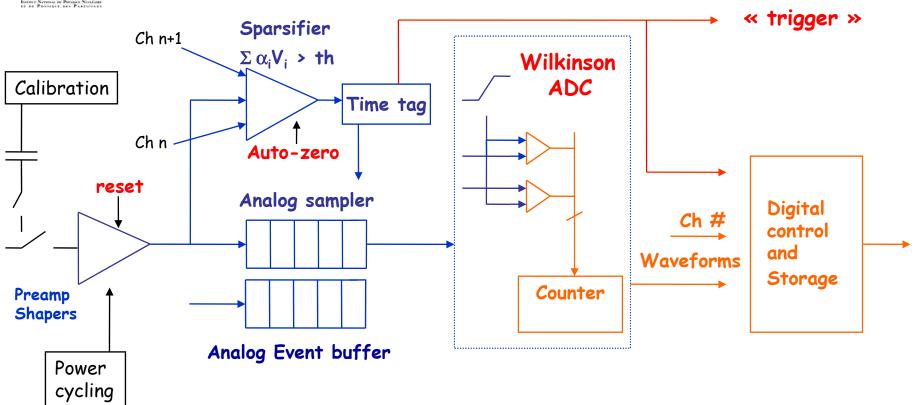

## Front-end architecture

Charge 1-30 MIP, Time resolution: BC tagging 150-300ns 80ns analog pulse sampling

Technology: Deep Sub-Micron CMOS 130-90nm

# Outline

Silicon strips readout

The 4-channel evaluation chip in 130nm CMOS

> The 88 channel chip

Conclusion

# Front-end in 130nm

Motivation for 130nm CMOS:

- Smaller

- Faster

- Less power

- Will be (is) dominant in industry

- (More radiation tolerant)

Drawbacks:

- Reduced voltage swing (Electric field constant)

- Noise slightly increased (1/f)

- Leaks (gate/subthreshold channel)

- Design rules more constraining

- Models more complex, not always up to date

# UMC CMOS Technology parameters

|                                                                                                                                | 180 nm                                             | 130nm                                                   |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------|

| <ul> <li>3.3V transistors</li> <li>Logic supply</li> <li>Metals layers</li> <li>MIM capacitors</li> <li>Transistors</li> </ul> | yes<br>1.8V<br>6 Al<br>1fF/μm²<br>Three Vt options | yes<br>1.2V<br>8 Cu<br>1.5 fF/μm²<br>Low leakage option |

Help from IMEC Europractice (Leuven, Belgium): Paul Malisse, Erwin Deumens

# 4-channel Chip

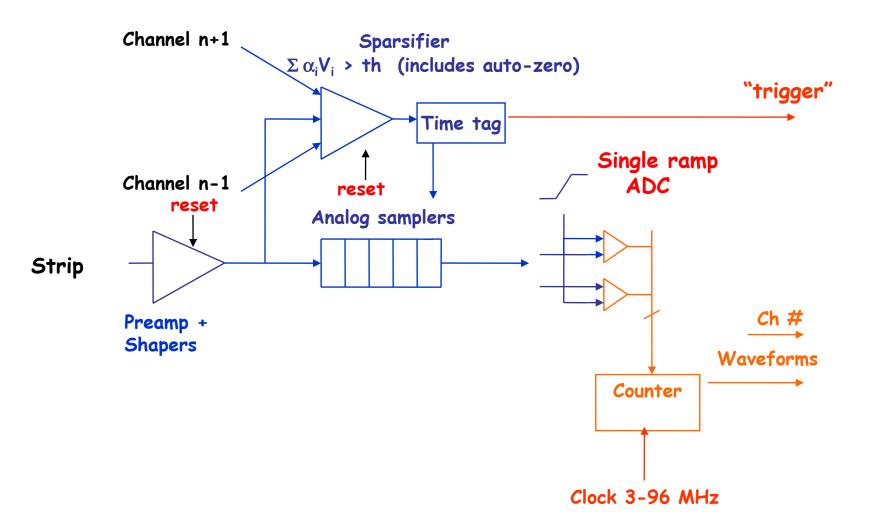

# 4-channel chip layout

Amplifier, Shaper, Sparsifier 90\*350  $\mu m^2$  Analog sampler 250\*100  $\mu m^2$

180nm 130nm

Layout of the 130nm chip including sampling and A/D conversion

# Preamp-shaper results

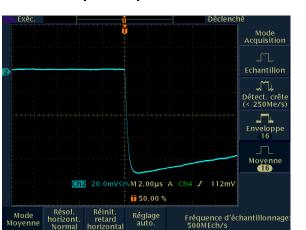

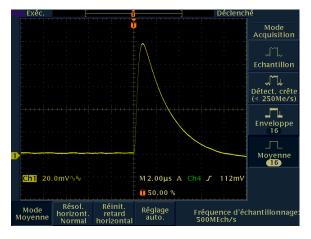

#### Preamp output

#### Shaper output

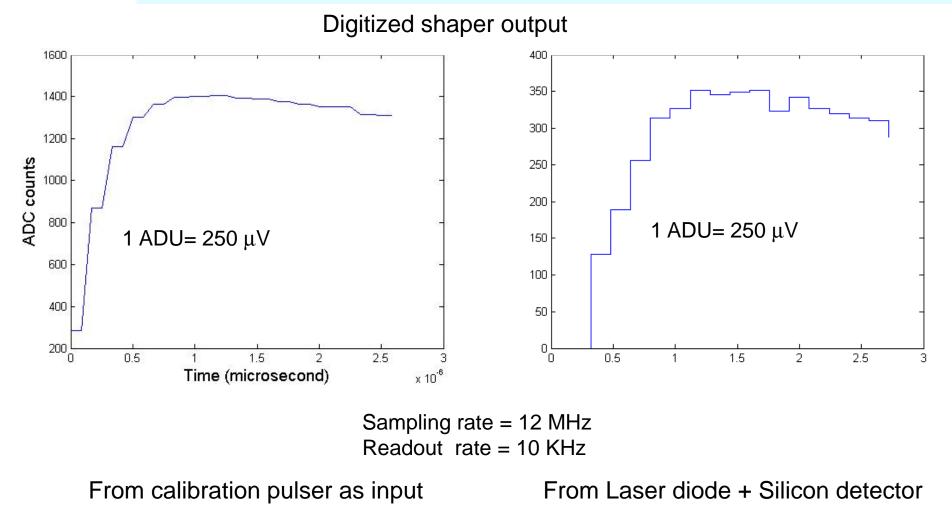

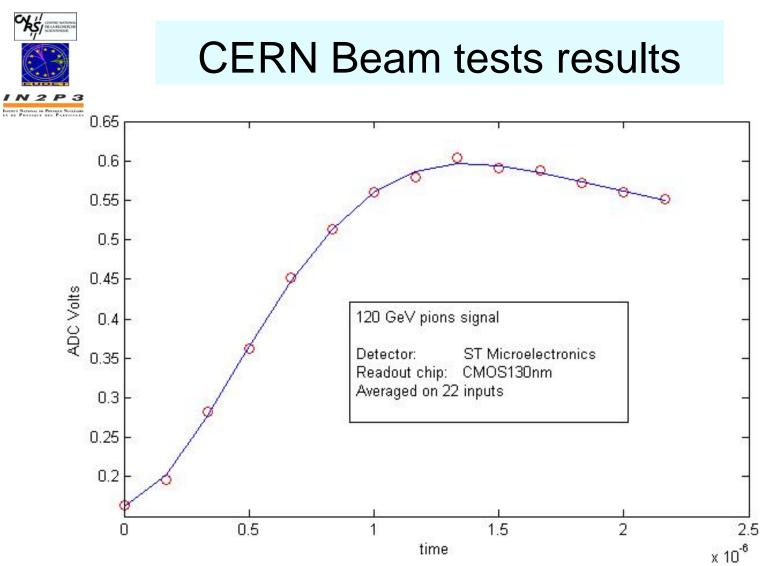

# Digitized analog pipeline output Laser response of detector + 130nm chip

### ADC TEST

- Averaged response of  $\,$  120 GeV pions through 500  $\mu m$  thick Silicon detector

- Pedestal subtracted off-line, then digitized shaper waveform OK.

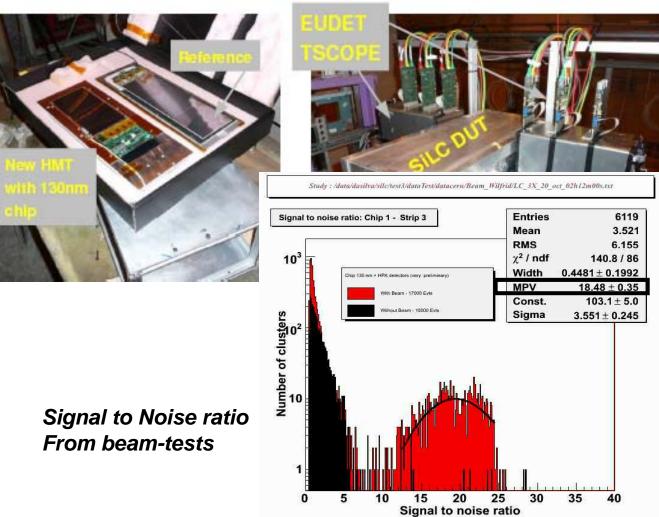

### 130nm chip test-beam response

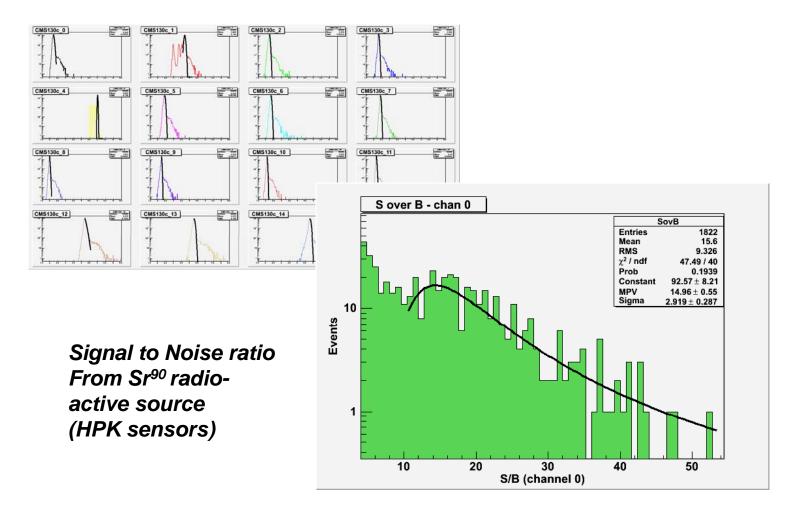

### 130nm Sr<sup>90</sup> radio active source

$\succ$

# Outline

Silicon strips readout

> The 4-channel evaluation chip in 130nm CMOS

Find the second stand the second seco

Conclusion

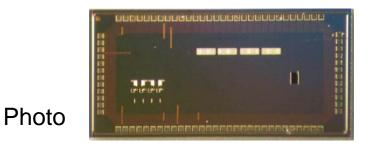

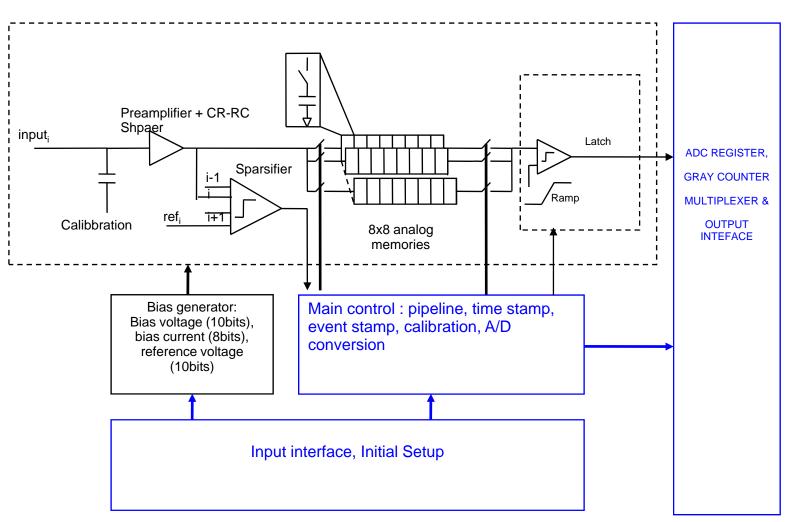

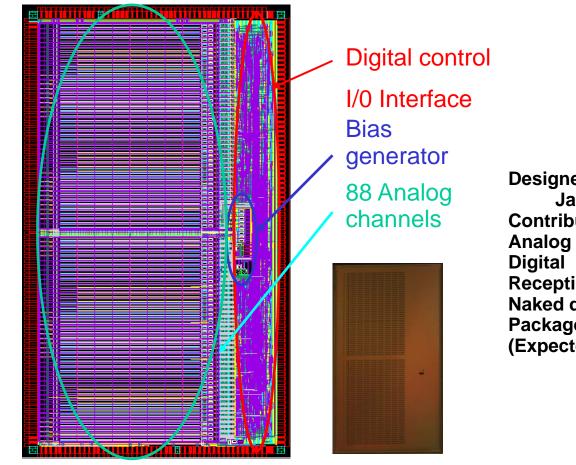

Block diagram

**Electrics**:

-Consumptions : ~ 1.1mW/channel

-LVTTL digital IN/OUT

Features:

- 88 channels in 130nm CMOS

(Preamplifier, Shaper, Sparsifier, 2D 8x8 analog memories, 12 bits ADC)

- Integrated calibration

- Power switching

- Digital controls

(Bias, threshold, sampling, zero suppression data out, time/event stamp, power switching control, serial in/out interface)

Two samples : 60 naked dies 20 packaged dies

Designed : Jan/08 – Juin/08 Contribution: Analog : LPNHE Digital : UB Reception: Naked die : Sep 12th 08 Packaged die : Mid Octorber/08 (Expected)

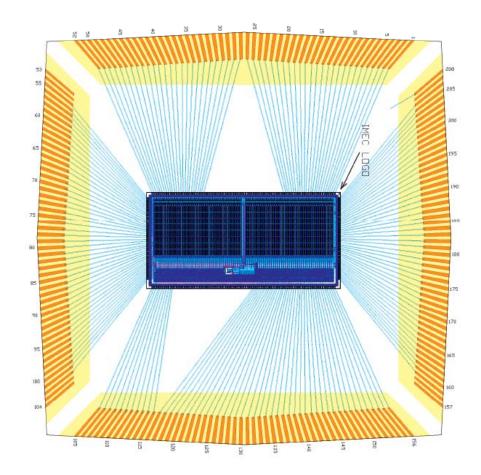

Layout of 88 channels readout circuit (5mmx10mm)

**CQFP 208**

- 50 analog input including 1 test channel

-> Functional test, productivity

#### Functional test with packaged chip

- Front-end board -> already designed (will be soon available)

- DAQ Software

- "simplified" version -> charged by University of Barcelone

- -> Initialization, probe digital signal

- -> Confirm the functionality of the chip

- -> Power test (bias voltage, current)

- -> Test channel : Preamplifier, Shaper ...

"developed" version -> under development, charged by LPNHE+UB

- -> ADC characterization

- -> Calibration scan

- -> Optimization ...

#### Beam/radio active source test (detector + naked die)

- Front-end board -> already designed (4 naked chips/module)

- DAQ Software

Previewed extension in actual acquisition system (FPGA board + soft) (see Alexandre's talk)

# Conclusion

The CMOS 130nm design and test results demonstrate the feasibility of a highly integrated front-end for Silicon strips (or large pixels).

The new 88 channels chip is available for the test. This chip will be able to equip the large silicon strip modules and confirm the strategy of the development

# The end...