## Summary:

•EUDRB developments in 2008

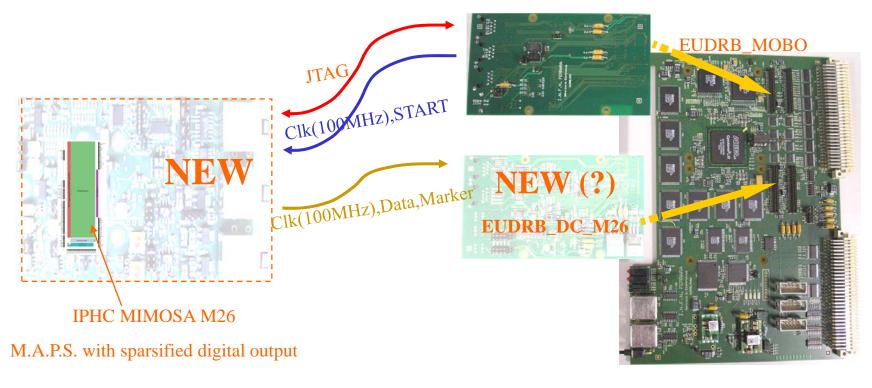

•Plans for interfacing the EUDRB to a new "proximity" card designed for the M26 sensor being developed at IPHC

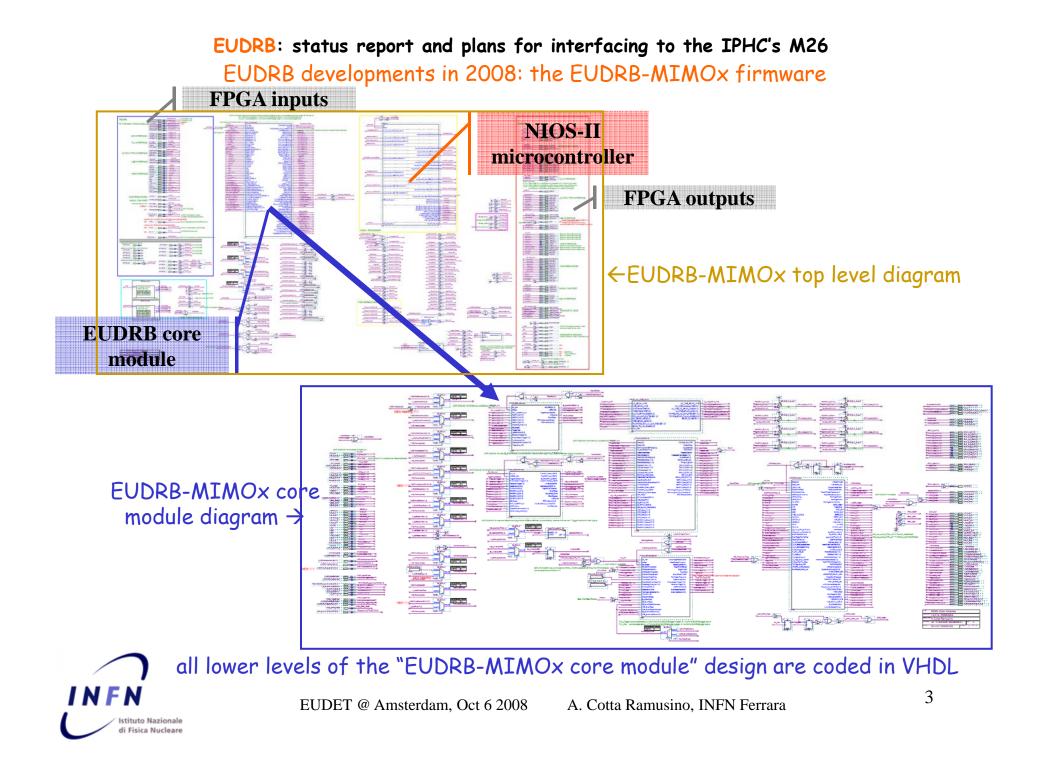

EUDRB: status report and plans for interfacing to the IPHC's M26 EUDRB developments in 2008: the EUDRB-MIMOx firmware

The "EUDRB-MIMOx" firmware was developed to:

- allow the EUDRB to read out the MIMOSA18 chip (256kpixels, high resolution sensor)

- allow full VME control of the parameters determining the sensor timing as well as the A/D converter timing and frame buffer size

- increase throughput by:

- allowing overlapped readout and trigger processing operation of the EUDRB ( capturing a new event can now start as soon as the previous event is stored in the output buffer )

- implement a "rolling two frames" raw data format, to reduce the size of the non zero-suppressed events with respect to the previous "static three frames"

- re-style the FPGA design (VHDL and block diagram entries) to make it easier to read and maintain (as much as possible)

EUDRB developments in 2008: the EUDRB-MIMOx firmware

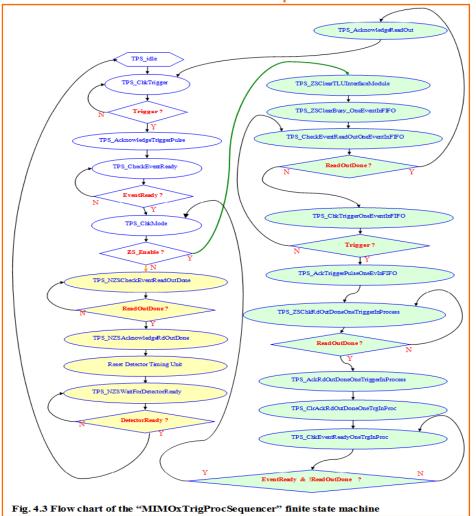

The "trigger processing sequencer" controls the overlapping of the sensor scan in response to a new trigger and the VME-MBLT readout of a previous event, both for Zero-Suppressed (green states) and Non Zero-Suppressed (yellow states) operation.

Decoupling the scan and the readout phase has allowed to achieve a trigger rate of about 100Hz in test beam operation with 6 boards in the crate.

While making the overlapped operation possible for EUDRB has improved things, the DAQ trigger rate is still below the goal ; the limitation is due to the idle time that the MVME6100 VME CPU spends while switching from MBLT to SINGLE CYCLE transfers (still under investigation)

EUDET @ Amsterdam, Oct 6 2008

Source: "The EUDET Data Reduction Board (EUDRB) (firmware version EUDRB\_MIMOx)" version 1.1 of Aug. 8th 2008, A. Cotta Ramusino INFN-FE

Plans for interfacing the EUDRB to the M26 sensor being developed at IPHC

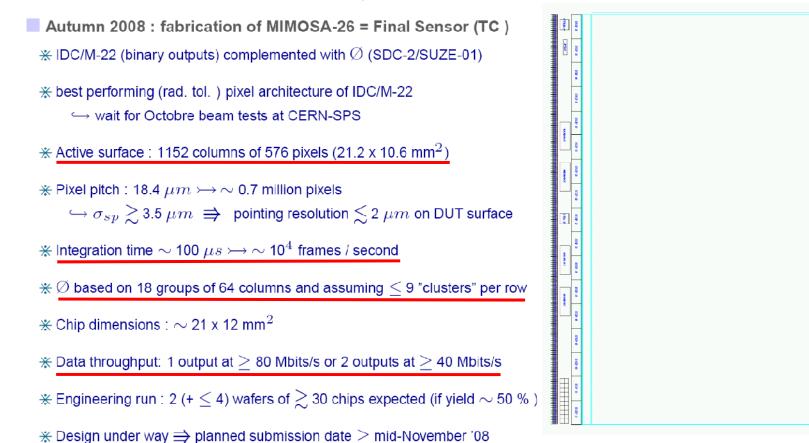

#### MIMOSA 26 characteristics: summary

Source: "Towards the Final Telescope Sensor: Status Report", Marc Winter IPHC-Strasbourg, EUDET - JRA-1 - Final Telescope Sensor Progress Report, 1 September 2008

Plans for interfacing the EUDRB to the M26 sensor being developed at IPHC

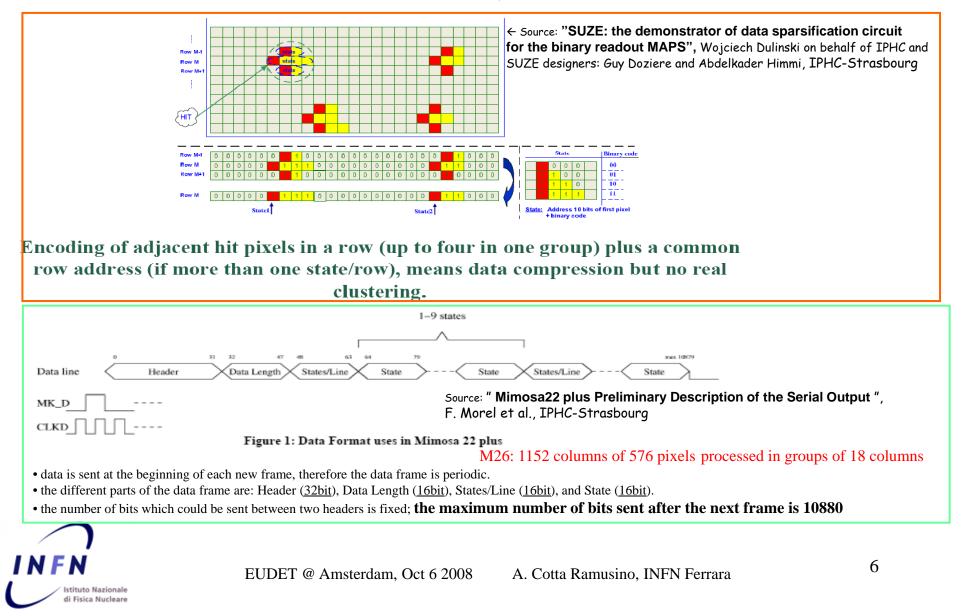

MIMOSA 26 characteristics: PRELIMINARY output data format

Plans for interfacing the EUDRB to the M26 sensor being developed at IPHC HARDWARE PLAN (A):

## • NO NEED TO BUILD A NEW DAUGHTER CARD:

! USE THE PRESENT J5 CONNECTOR ON THE EUDRB\_DCD CARD which provides 4 spare LVDS inputs

## **CAVEATS of this solution:**

• the outgoing LVDS signals <u>100MHz clock, and "Start"</u> will be generated as single ended signals from the main FPGA and will have to cross the board-to-board connector to be converted into LVDS on the EUDRB\_DCD digital daughter card

• the incoming LVDS signals <u>100MHz(50MHz) clock</u>, <u>1</u>(2) data and "NewFrame" marker will be converted to single ended signals on the EUDRB\_DCD card and will have to be transmitted as single ended signals to the main FPGA on the mother board: the reliability (concern with skewing) of this signal paths that cross the board-to-board connector between mother and daughter cards must be verified.

$\cdot$  only one MIMOSA26 sensor could be read by a EUDRB card

#### **ADVANTAGES of this solution:**

• cheaper (we have already enough EUDRBs to convert to MIMOSA26 readout and the conversion should involve only firmware changes)

• feasibility studies can start with the existent hardware

Plans for interfacing the EUDRB to the M26 sensor being developed at IPHC

## ALTERNATIVELY: HARDWARE PLAN (B):

EUDRB\_DC\_M26 daughter card: in order to interface the EUDRB to the MIMOSA26 sensor it would be necessary to build a new daughter card to replace the present EUDRB\_DCA analog daughter card.

The EUDRB\_DC\_M26 will feature (in addition to the resources now present on the EUDRB\_DCA to provide synchronous operation across the pool of EUDRBs in the DAQ system):

$\cdot LVDS$  receivers for the (100MHz / 50MHz) serial links (data lines and strobes) driven by the MIMOSA26

•a small, fast FPGA of the Cyclone III family, providing resources for:

•de-serialization of the input stream(s) and temporary storage of the frame data received from the sensor pending the transfer to the mother board

transferring the data collected for each new frame to the main memory on the mother board (EUDRB\_MOBO), using the parallel data path now used for the A/D converter data

diagnostics

# ADVANTAGES of this solution:

→ more sensors (possibly up to 3, due to space limitation at the front panel of EUDRB) could be read out by accessing a single EUDRB card. A patch card would be needed to fanout the signals 100MHz clk and "START" to three detectors unless such "fanout" is already provided by the sensor developers

$\rightarrow$  higher efficiency in the VME readout due to the limited need of switching between burst read accesses and single cycle transfers

Plans for interfacing the EUDRB to the M26 sensor being developed at IPHC

#### FIRMWARE UPGRADE PLAN:

The EUDRB\_MIMO× firmware will need upgrading to account for the different data handling needed when reading out a MIMOSA26 sensor.

The new EUDRB\_M26\_FW firmware will:

$\cdot$  de-serialize the input data in case of adoption of hardware plan (A)

• provide temporary storage (on FIFO memories embedded in the FPGA) for at least two frames, pending the trigger request

• Build, in response to a trigger request, an event data packet with header and trailer ( similar to the ones currently used)

- transfer the event in the output FIFO (external to the FPGA)

- control the transfer of the events buffered in the output FIFO over the VME backplane

Plans for interfacing the EUDRB to the M26 sensor being developed at IPHC MILESTONES AND COSTS FOR UPGRADING THE EUDRB to readout the MIMOSA26 sensor:

Setting milestones for the upgrade would require the final information on the characteristics of the sensor proximity cards which are expected soon from the sensor developers at IPHC.

Such information would have bearing on schedule and costs because it would determine:

• whether or not "patch cards" are needed to adapt to the final choice of connectors / pinouts

• whether each EUDRB would have to individually clock each sensor proximity card or a "timing signal fanout" will be made available by the sensor designers

#### Milestones and cost estimates (based on current informations):

Assuming some passive patch card is needed but hardware plan (A) is followed::

- end Oct. 2008: reliability of 100MHz link from EUDRB\_DCD (100Mhz clk+Start OUTPUT; 100MHz( 50MHz) Clk, 1 (2) data, "NewFrame" marker INPUT) assessed

- end Feb. 2009: new EUDRB\_M26\_FW ready for field tests

- cost ≈ 3K€ for patch cards

Assuming hardware plan (B) is followed:

- end of Jan 2009: EUDRB\_M26\_DC ready for testing

- end of Apr 2009: new EUDRB\_M26\_FW ready for field tests

- cost ≈ 3K€ for patch cards needed for clock fanout

cost ≈ 9K€ for EUDRB\_M26\_DC layout and production of 5 boards (capable of multiple sensor readout)