## The Silicon TPC System

EUDET Extended SC meeting

1 September 2008

Jan Timmermans

NIKHEF

## JRA2 activity/task

- Silicon TPC readout ("SITPC")

- development MediPix → TimePix chip

- development diagnostic endplate module incl. DAQ

Purpose: a SiTPC based monitoring system

#### Partners:

ALU Freiburg, Bonn, CEA Saclay, CERN, NIKHEF

#### **SITPC Tasks:**

- ✓ Develop the Timepix chip that allows to measure the 3<sup>rd</sup> coordinate (drift time)

- Implementation of Timepix together with GEM and Micromegas/Ingrid into diagnostic endplate system (in progress)

- ✓ Performance measurements in test infrastructure at DESY (in preparation)

- Develop simulation framework (in progress)

- Develop DAQ system and integrate in overall DAQ of EUDET infrastructure (in progress)

## Timepix

```

1st run 2006: 6 (Eudet) wafers

+14 ("private" + Medipix coll.)

All wafers probed; avg. yield ~73%

```

2<sup>nd</sup> run 2008: 38 (Eudet) wafers

+34 ("private" + Medipix coll.)

Sofar 2 wafers probed; similar yield

## Freiburg activities

# Measurements with laser @ Freiburg

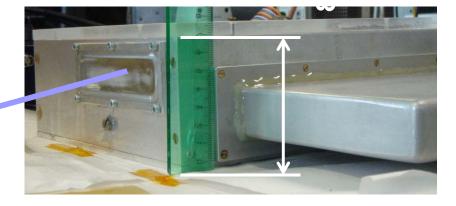

Installation of a laser test bench for measurements with single (primary) electrons. Detector with metallized drift cathode. From this laser releases single photoelectrons  $\Rightarrow$  creation of well defined and seperated clusters

- Measure detection efficiency for single electron clsuters

- Investigate influence from number of primary electrons on single point resolution.

- Possibly study ion backdrift proberties

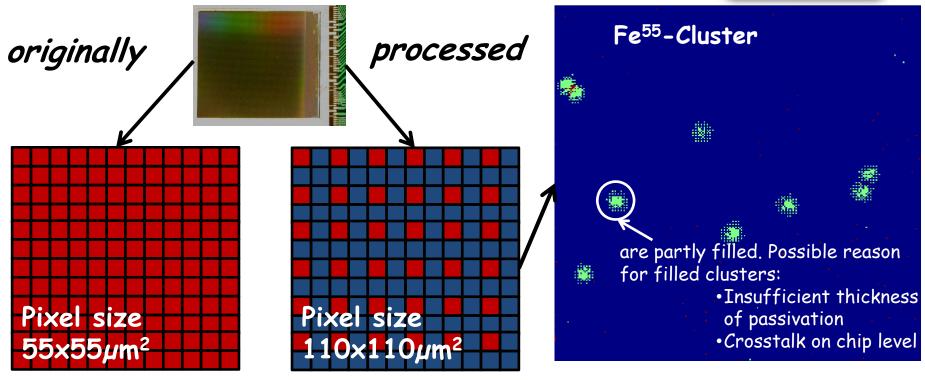

## Chip Post-Processing

- Pixel acitve

- Pixel passivated

- Work on technologies for post processing chips

- Optimization of readout granularity

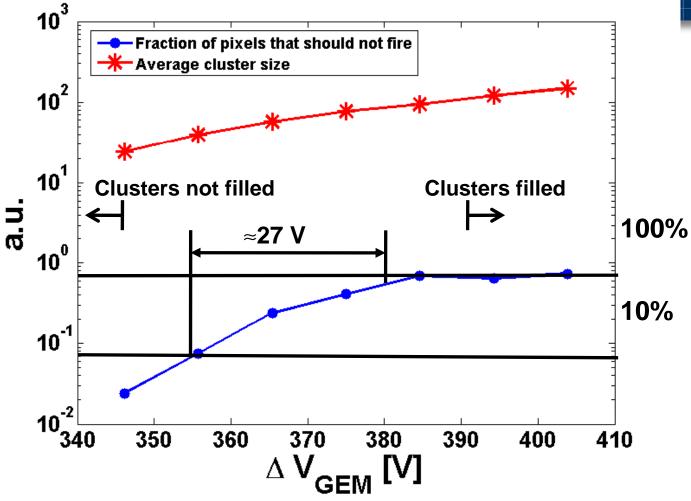

## First results with processed chip

≈27V correspond to a factor 5 in gain.

Ongoing investigation of the cross talk behavior

Next steps...

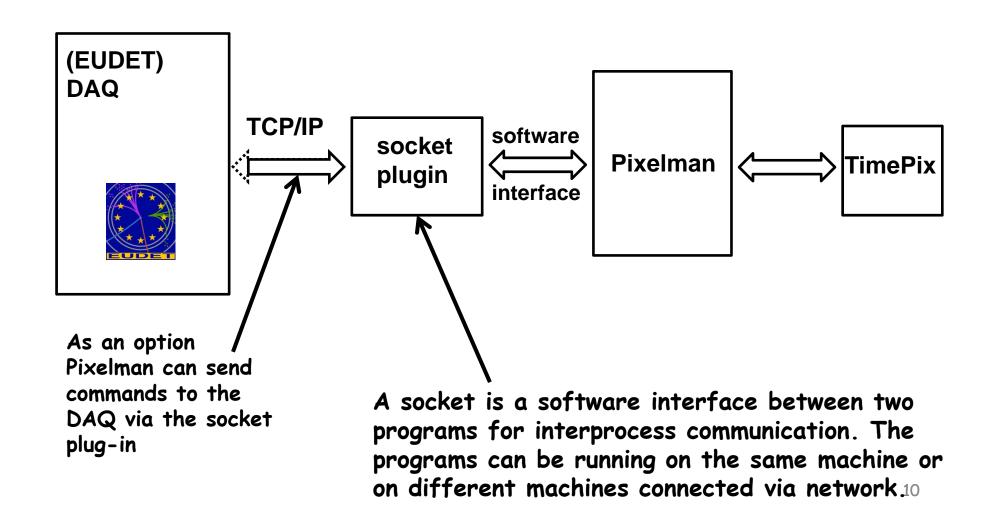

Produce Linux based DAQ steering (basic) Pixelman functions

Solution  $\rightarrow$  use network tools

Program a plug-in that uses standard network connections and TCP/IP, so that Pixelman software can be operated by a Linux DAQ-system, e.g. EUDAQ

## Next steps...

## Bonn activities

#### Reconstruction and Analysis: MarlinTPC

MarlinTPC is the TPC simulation, digitisation, reconstruction and analysis package for the Marlin framework

#### TimePix Reconstruction Chain

TimePix raw data TimePixCluster imePixReader ProjectionSeparator Processor TimePixSep TimePixRawData HitCandidates [imePixHighTO] mePixHitCente AnalyserPr. CalculatorPr TimePixRawData TimePixHits TrackFinder TimePixZero SuppressionPr. HoughTrafoPr TimePixZero TimePixTrack Supressed Candidates RawData: TimePixCluster LinearRegression FinderProcessor Processor TimePixHit TimePixTracks Candidates

Very modular with more than 50 processors, suited for all kinds of TPC readout (GEMs/Micromegas, ADCs, TDCs, TimePix)

- Reader for TimePix data from PixelMan

- Complete TimePix reconstruction chain

- Analysis processors (e. g. to determine spatial resolution)

- TimePix digitisation

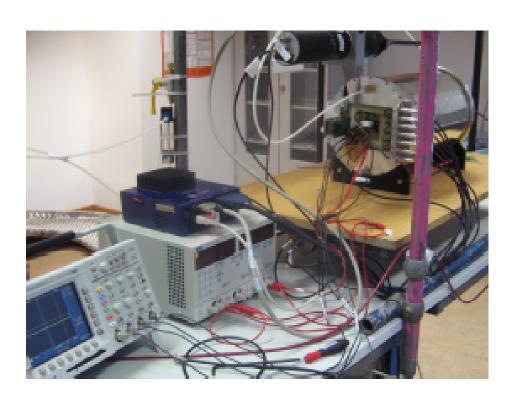

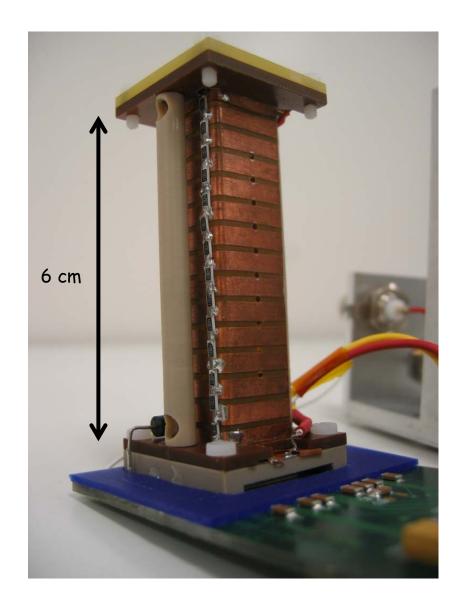

#### TPC Test Setup

- Field cage designed and produced in Aachen

- 26 cm diameter

- 26 cm drift distance

- Low material budget: 1 % X<sub>0</sub>

- Drift field up to 1 kV/cm

- Fits into 5 T magnet at DESY

- Trigger for cosmic muons:

Scintillators above and below the chamber

- Veto circuit: Only one shutter window per recorded frame

- TimePix readout with Muros and PixelMan

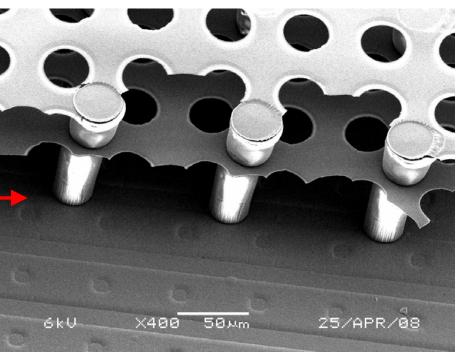

#### Post-Processing of TimePix

Freiburg group is testing MediPix chips with enlarged pixels (110×110 µm²), post-processed on per chip level by FMF (Freiburger Metallforschungszentrum)

Bonn has established first contact with IZM: Institut für Zuverlässigkeit und Mikrointegration, Berlin

Institut Zuverlässigkeit und Mikrointegration

Post-Processing of TimePix chips — on wafer level:

- Enlarging pixel size

by adding metal pads on a passivation

- Silicon through vias: replacing wire bonds by bump bonds

- InGrid plans to learn technology from Twente University

Contributions to the development of a TimePix successor chip.

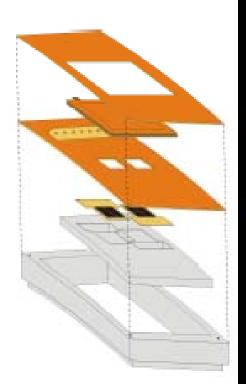

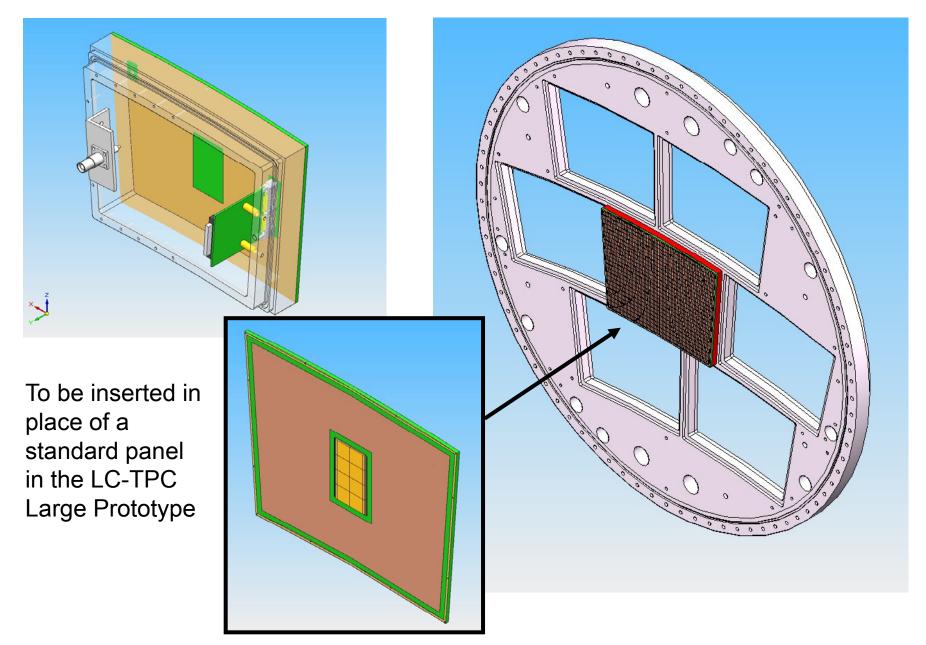

#### LP Module with 3GEM + TimePix

LOTPO-

- $\bullet$  3 standard GEMs 10 imes 10 cm<sup>2</sup>

- 1 mm transfer gaps and induction gap

- Two quad-boards (NIKHEF) with 4 TimePix chips each

anode plane

GEMs

readout plane

quad-boards

reinforcement of

anode plane

redframe

GEMs and QuadBoards have to be assembled

#### Status

#### **GEMs**

- GEMs are in house

- G10 frames have been delivered

#### QuadBoards

- One QuadBoard is fully equiped and bonded

- QuadBoard worked fine except for a broken bond (could not read DAC values from second chip)

- After fixing the bond the board does not answer any more

Problem not understood!

## Saclay activities

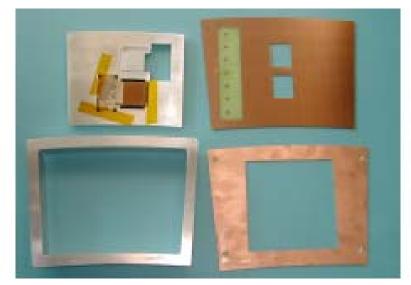

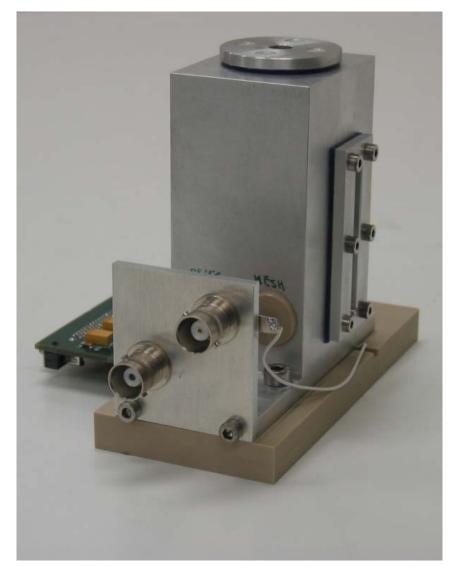

## Deliverable 1: single-chip diagnostic tool

- Must include a field cage

- Micromegas mesh with 55 micron pitch, to avoid Moiré effect

- Special frame to handle the mesh (in pick)

- 2 windows (beta on the side, gamma on the top). Also possible to shoot a photon beam for polarimetry applications.

- No magnetic component.

#### TimePix+Micromegas detector

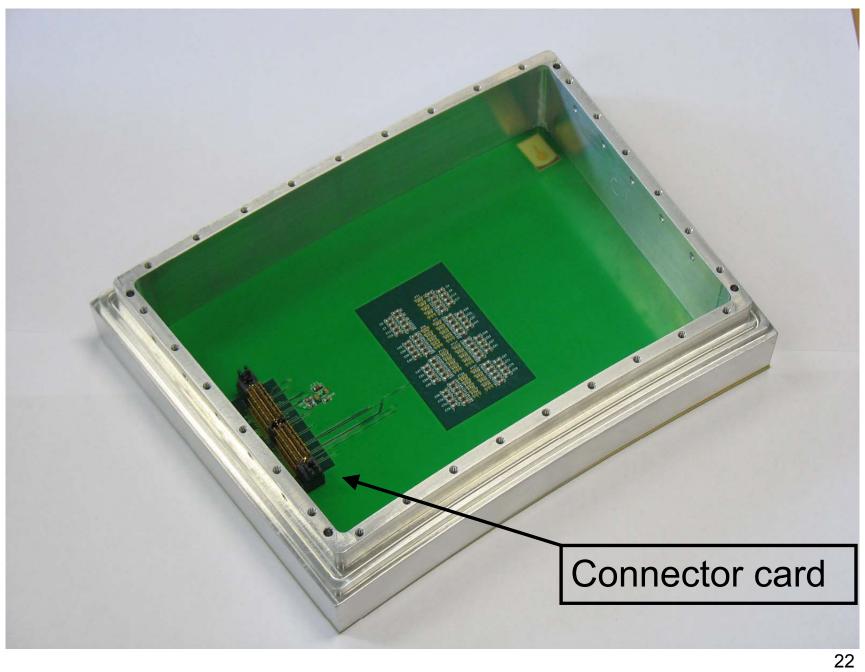

## Next Deliverable: 8-chip endplate panel infrastructure

- 8 chips is the maximum that can be handled by a MUROS readout card.

- The 8 chips must be power-supplied and the readout must be daisy-chained

- There must be a possibility to bypass any broken chip (but only one at a time)

- Chips must be equipped with an InGrid

## Recent developments and plans

- This infrastructure has been delivered in March 2008.

- Since then, it was equipped with 8 TimePix chips (600 wire bondings)

- Not enough power from MUROS: use external supply

- Mistake in the design found; solved by cutting some tracks on the PCB. Now a pure serial readout is used.

- Still not possible to read all 8 chips: wiring mistake will be corrected. This should solve the problem.

- After test with this PCB, will consider making a new PCB with 12 layers instead of 6; should contain all connections in a 30x60 mm rectangle.

- At the same time we can correct the present version for known mistakes.

### NIKHEF activities

- 1T magnet data and CERN PS data analysis

- Technology development:

- (together with Univ. Twente)

- Ingrid, "GEM"grid, Twingrid

- Protection layers: aSi:H, Si<sub>3</sub>N<sub>4</sub>

- Design larger chip-arrays

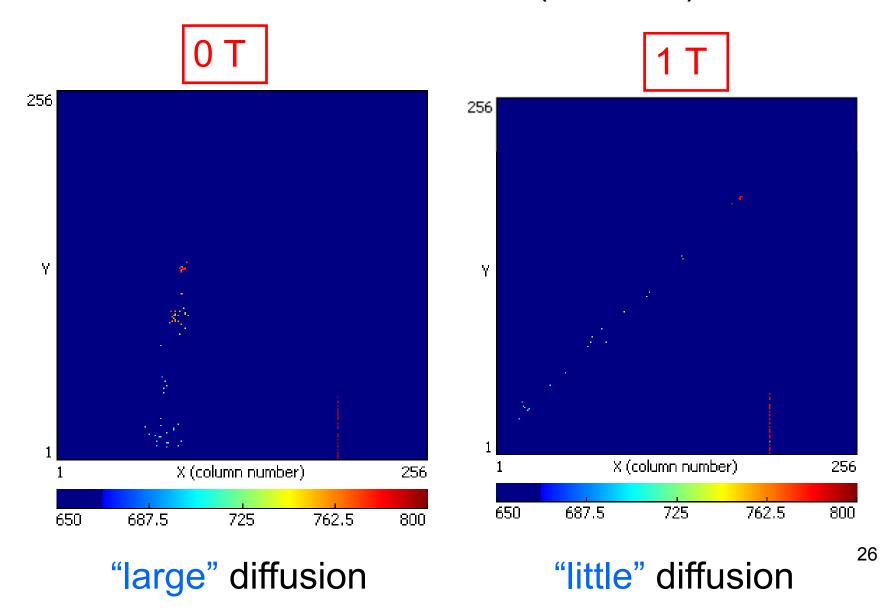

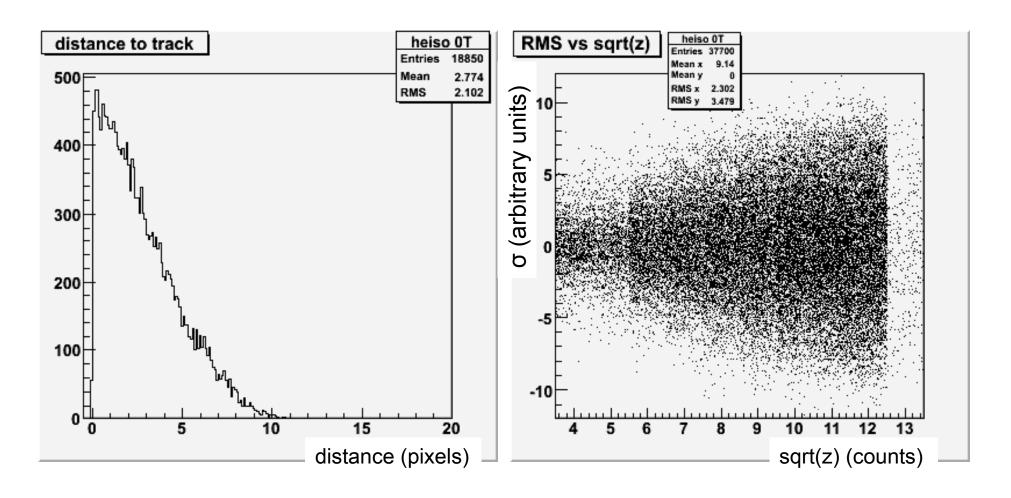

## Cosmic tracks traversing ~ 30 mm drift space in Ar-CF4-iC4H10 (95/3/2%)

### distance to track

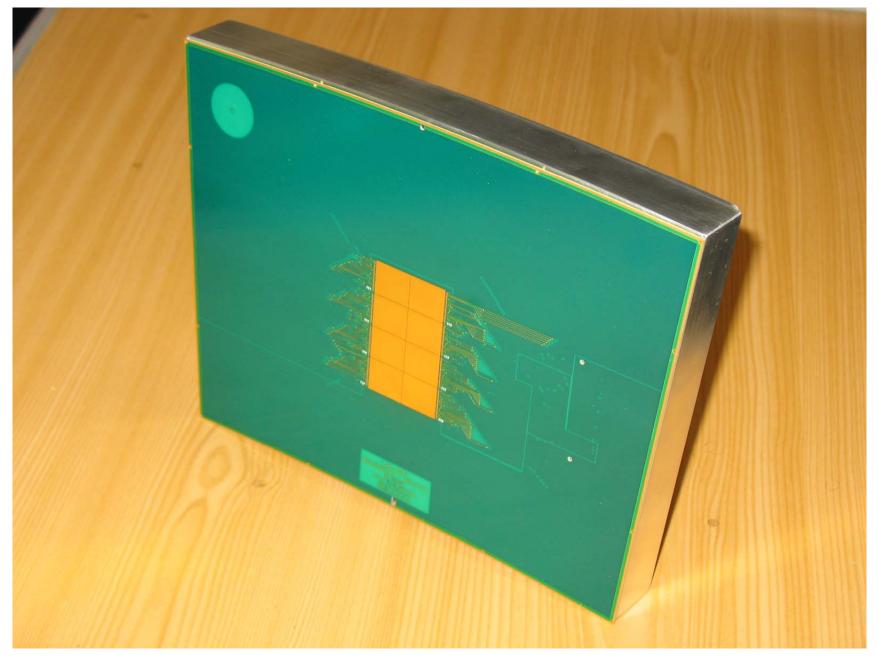

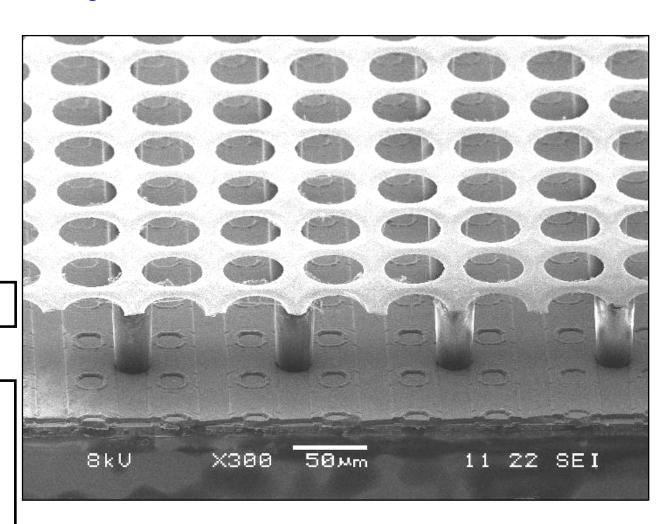

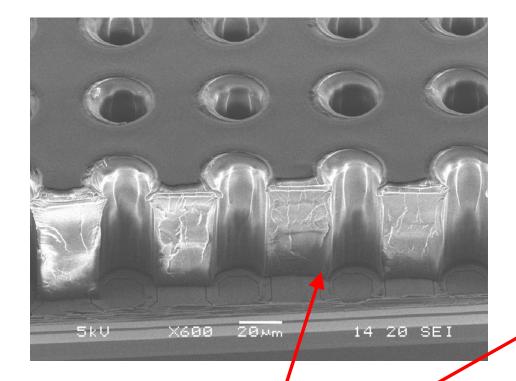

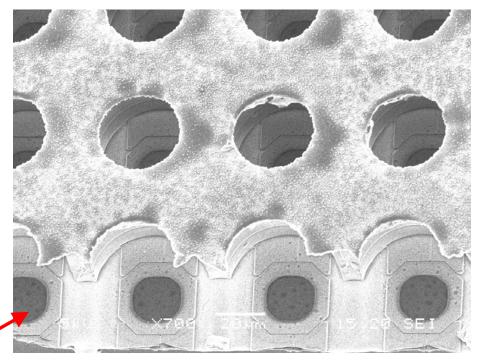

## Full post-processing of a TimePix

· Timepix chip + SiProt + Ingrid:

Timepix chip:

•256x256 pixels

•pixel: 55x55 µm<sup>2</sup>

•active surface:

14x14 mm<sup>2</sup>

MESA+: Ingrid

**IMT Neuchatel:**

15 or 20 µm highly resistive aSi:H protection layer

"GEM"grids

**Twingrid**

(under test)

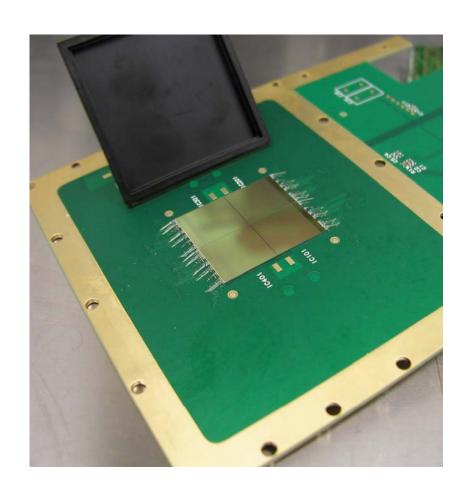

### Quad boards

- A square of 4 Timepix chips on a pcb.

- Solved some power problems.

- · Set up works.

- Awaiting chips with Si(N)Prot and InGrid from Twente

- Potential deliverable for EUDET.

## Work in progress

- (Post) processing in Twente.

- Both SiNProt and InGrid can be applied.

- Chip squares of 3X3

Timepix chips instead of individual chips.

- Search for high res InGrids. (Si<sub>3</sub>N<sub>4</sub>)

- Ageing test chips.

- Discharge test chips.

- Quad in testbeams.

- Design of an 8X8 array.

- Input from the RELAXED project.

- Composed of quads.

- Mechanics are being made right now.

- Readout electronics in prototype stage.

## SiTPC Summary-1

- Sofar mostly single-chip systems used

- Soon (Eudet deliverable) small multi-chip systems operational:

- Bonn: two 4-chip boards → on endplate module

- Saclay: one 8-chip board → on endplate module

- NIKHEF: 4-chip board, fitting single-chip detector mechanics and drifter (could become endplate module)

- Later (~3/2009): aim for a 64-chip system (bottleneck could be production of sufficient # Ingrids; IZM Berlin interested)

## SiTPC Summary-2

- A lot of progress made in last 'year'; not mentioned many details on track resolution studies and on signal development

- Part of the technology is ready:

- Very good energy resolution for Ingrid devices

- Ion backflow at the few per-mil level at high field ratio

- Discharge protection seems working for Ingrid (and Micromegas) devices under "normal" conditions

- Robust operation with GEM devices (without protection)

#### Next:

Build larger multi-chip detector systems with fast readout