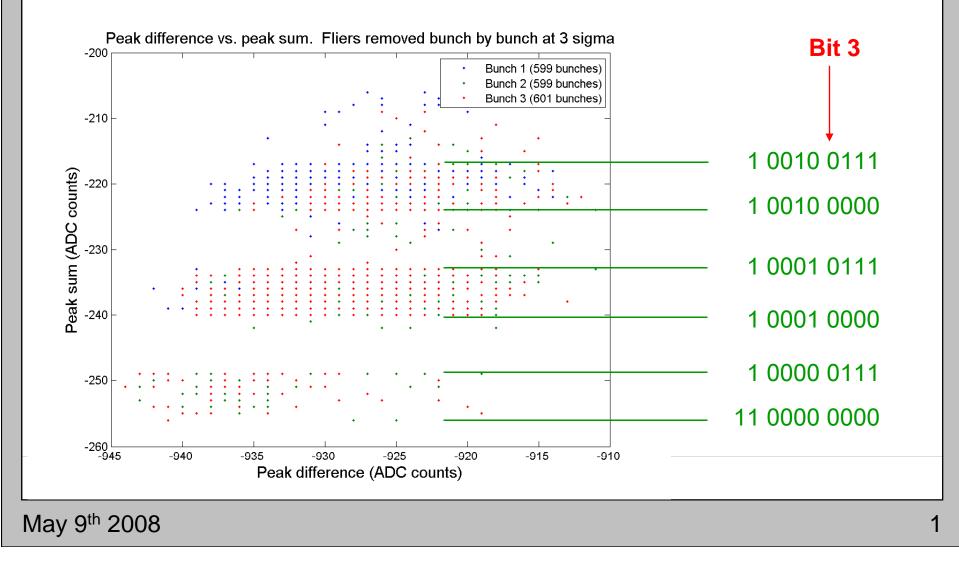

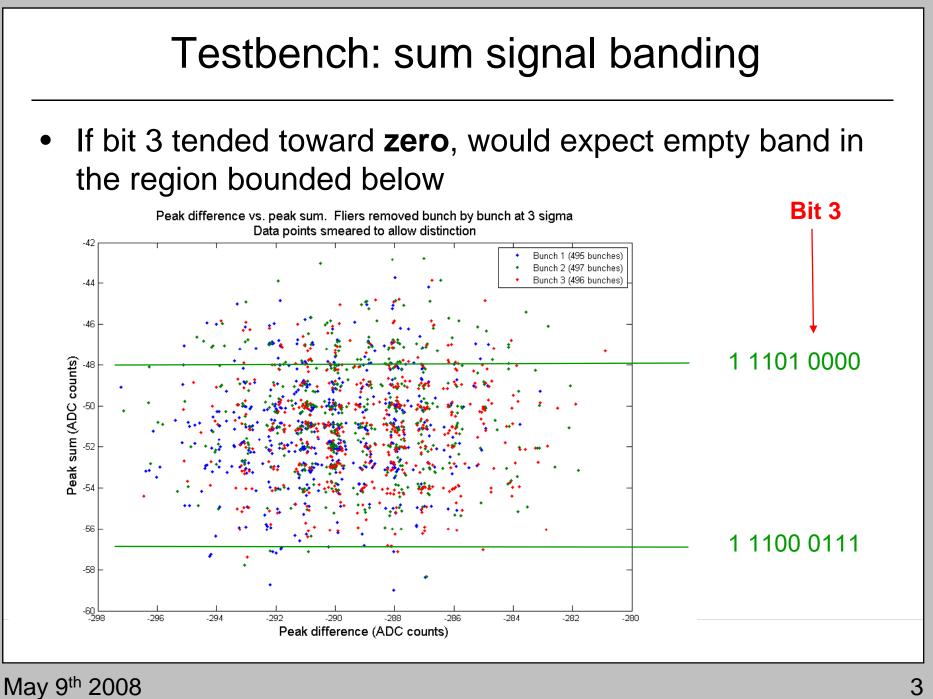

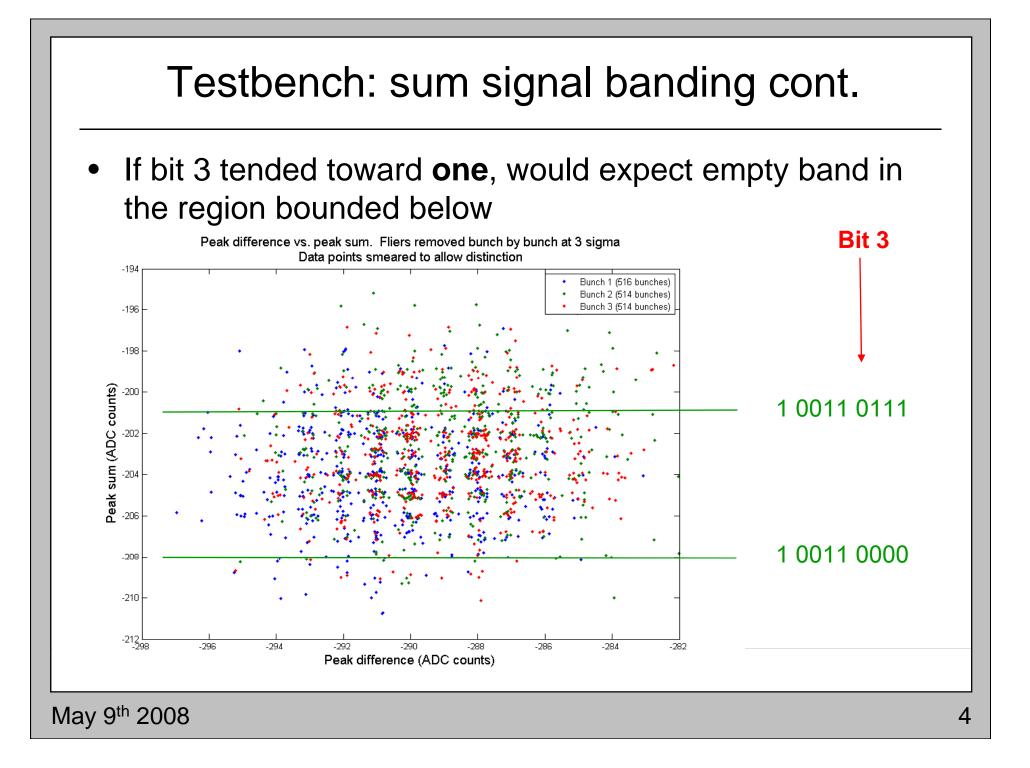

# Sum signal banding

#### • From last week:

### Modifications

#### **Testbench**

- Unsuitable splitters causing poor ring clock pulse

- Giving timing glitches on bunch output

- Now using two 2.16MHz signals from ATF racks

- Board 3 now outputs on ring clock cycle selected by trigger

### **FONT4 firmware**

- Tightened timing constraint on 357MHz by 40ps

- Enabled 'timing driven mapping'

- Ran high effort place and route

- Timing slack now 56ps

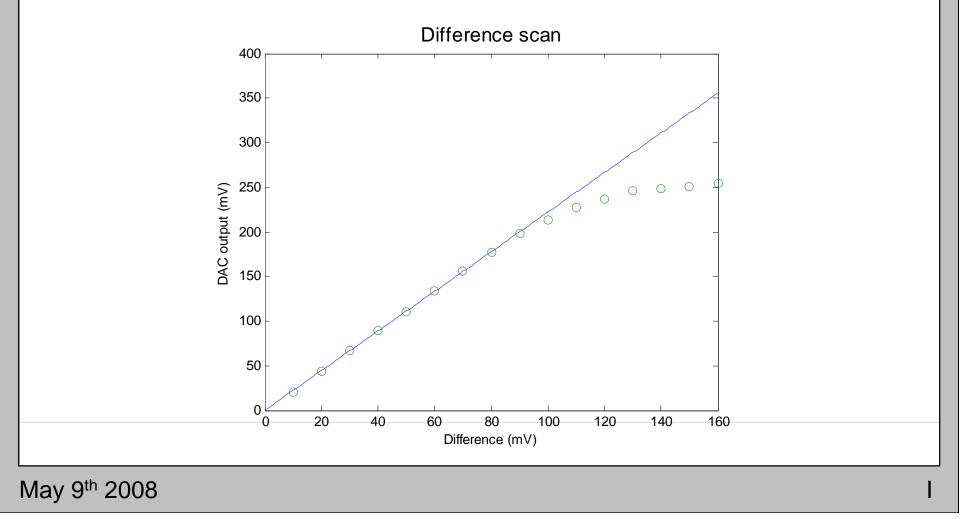

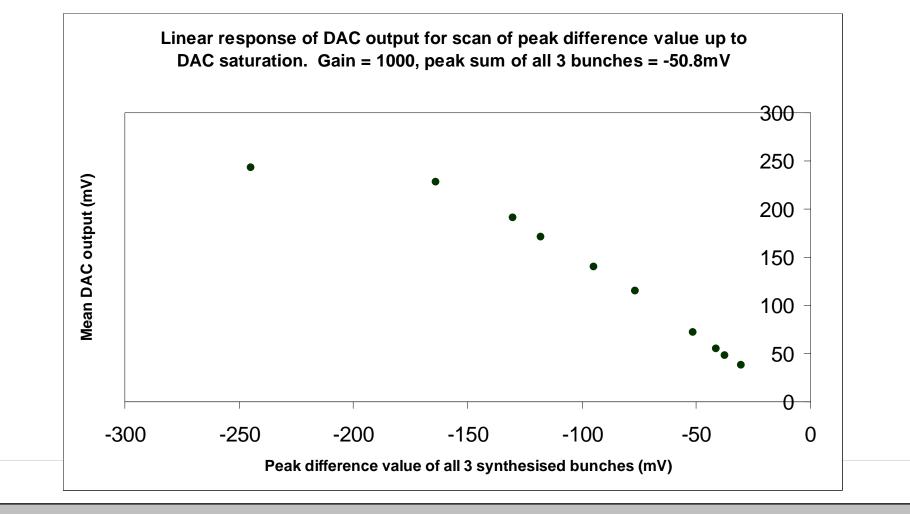

### DAC feedback signal response

- Varied sum and difference signals from testbench using combinations of attenuators

- Tested CN firmware with good timing slack

- Measured resulting peak sum/difference using scope

- Averaged DAC output using scope

- DAC output very stable

## Testbench: DAC response difference scan

• Feedback signal varies linearly with peak difference

May 9th 2008

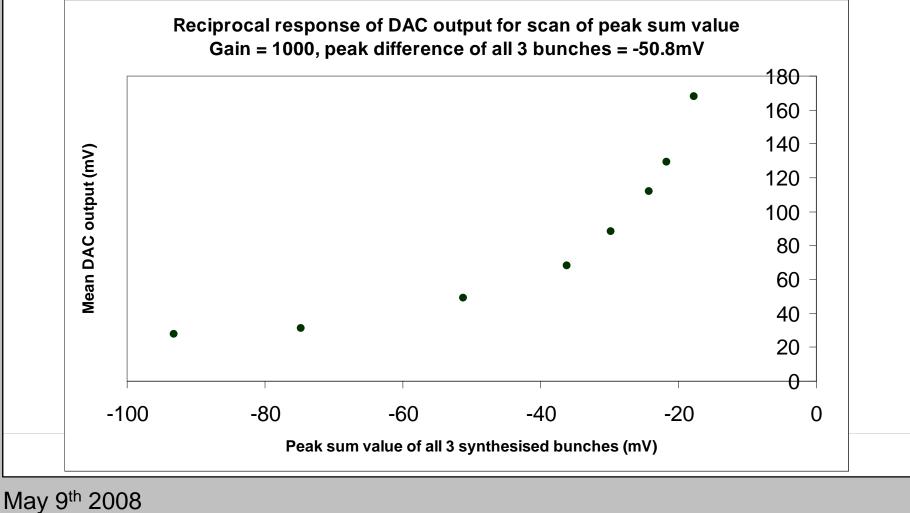

Feedback signal varies reciprocally with peak sum

### Additional: Oxford difference scan

• Scan over difference using square pulse also shows a drop off in DAC output before reaching full scale