### Alice TPC FEE - MWPC Readout

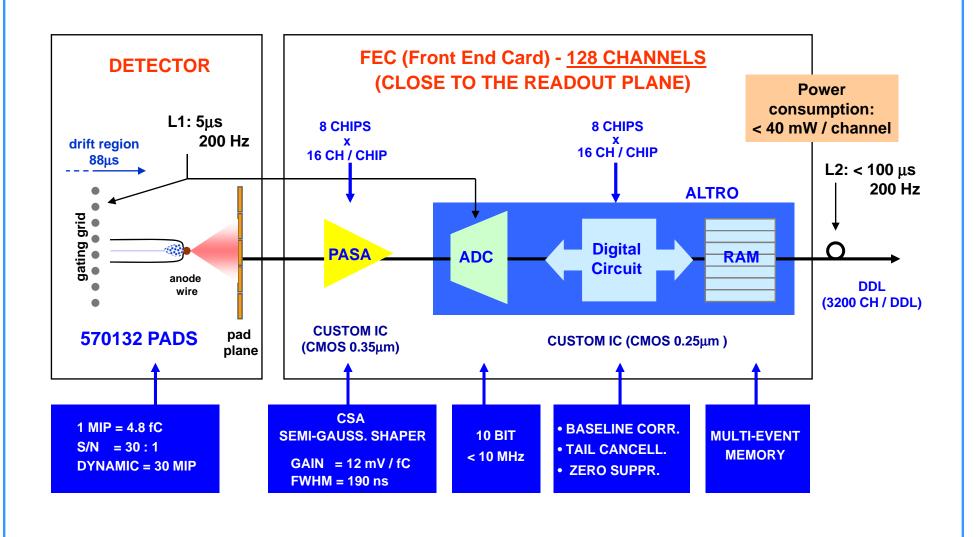

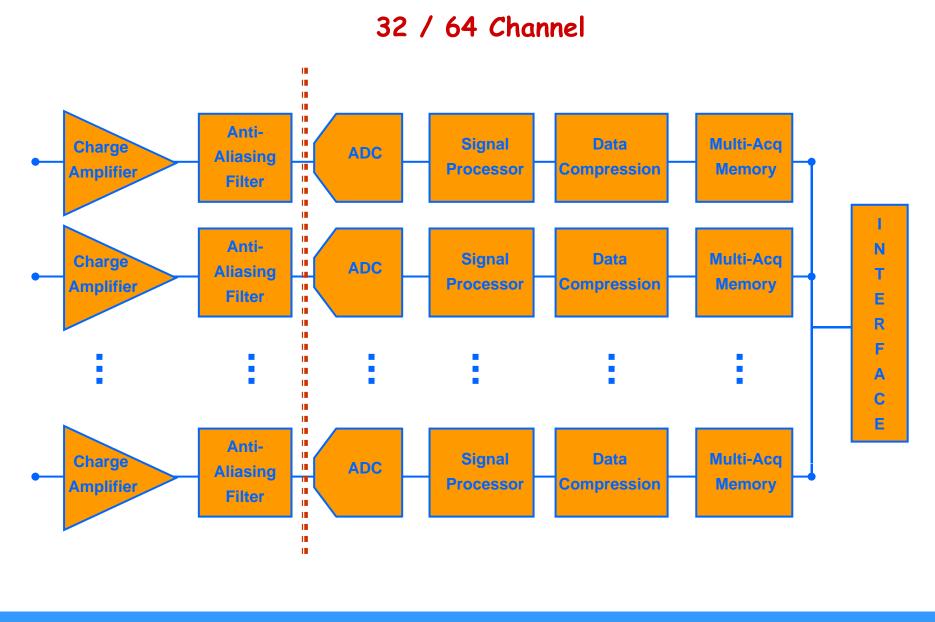

#### **Front End Electronics Architecture**

# Alice TPC FEE - MWPC Readout

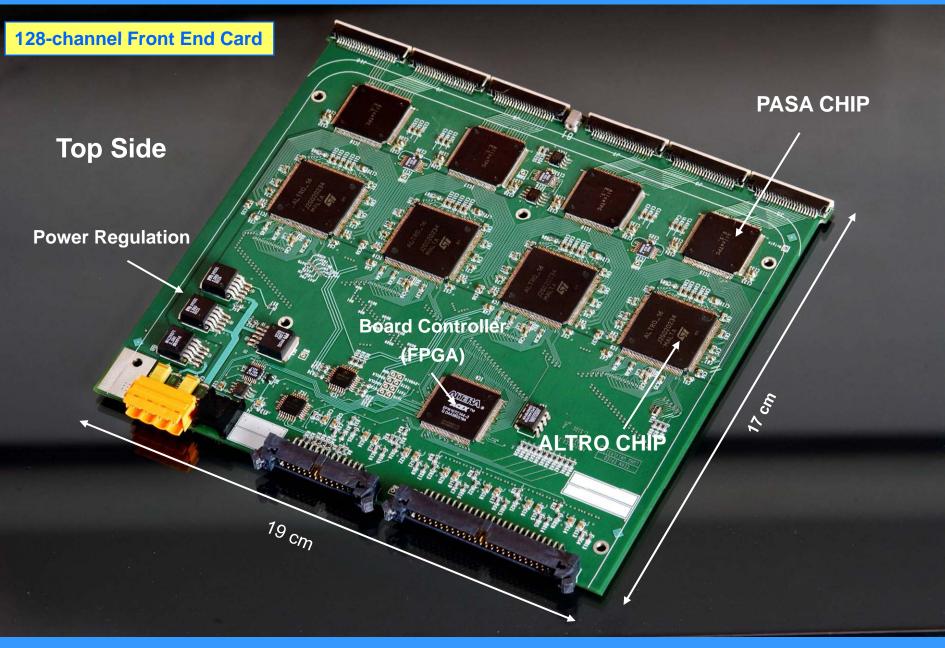

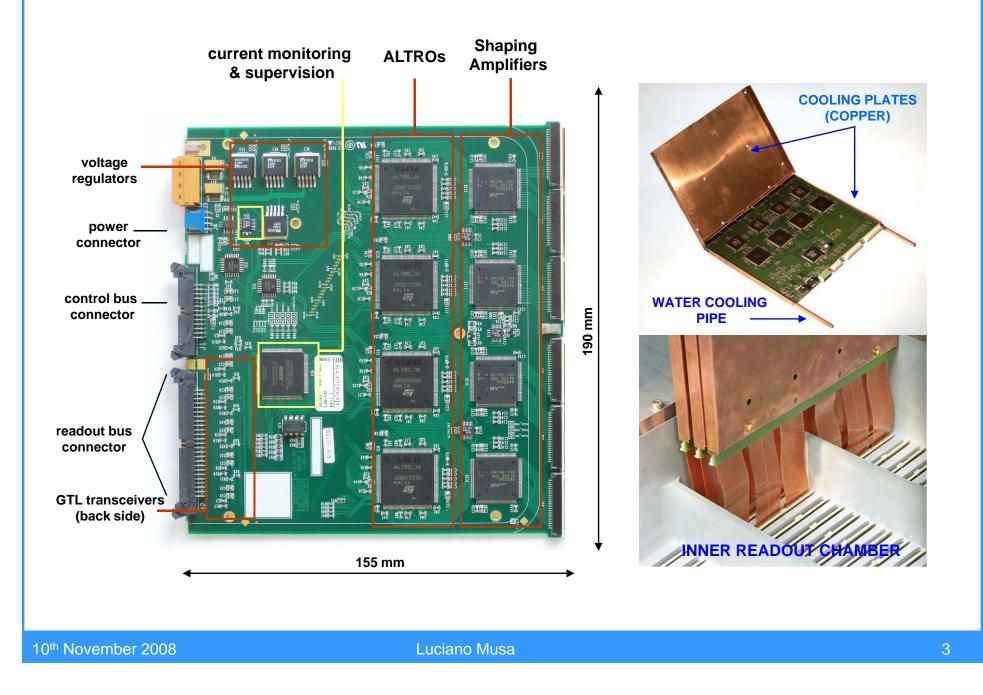

# ALICE TPC Front End Card: Layout, Cooling and Mounting

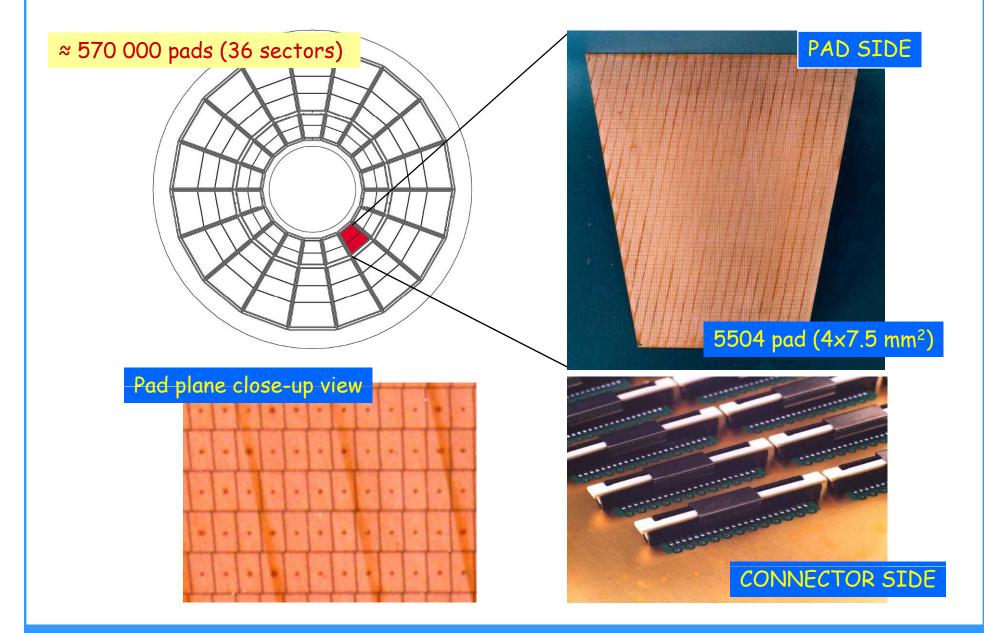

### ALICE TPC - Readout Chambers

# Installation of ALICE Front End Electronics (Feb-May '06)

10<sup>th</sup> November 2008

- ✓ number of channels: 32 or 64

- programmable charge amplifier

- sensitive to a charge in the range:  $\sim 10^2$   $\sim 10^6$  electrons

- Peaking time: 20ns 100ns

- high-speed high-resolution A/D converter

- sampling rate: 40MHz

- programmable digital filter for noise reduction and signal interpolation;

- a signal processor for the extraction and compression of the signal information (charge and time of occurrence).

- Two readout modes: external trigger or self-triggered

- Trigger can have any position wrt the acquisition window

- ✓ Standby mode

# Charge Readout Chip Block Diagram

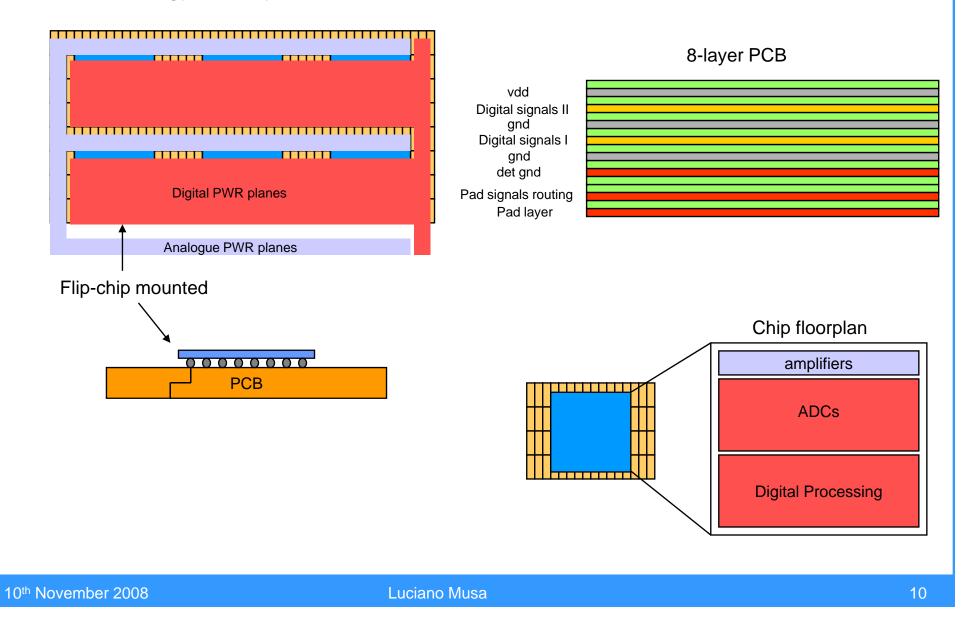

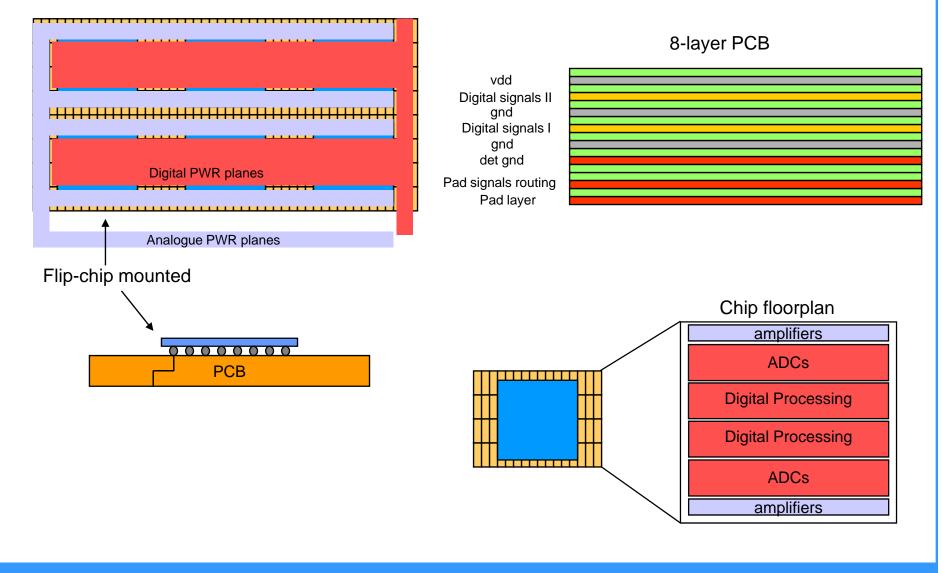

IC Area (die size)

- 1-2 mm<sup>2</sup> /channel

- Shaping amplifier 0.2 mm<sup>2</sup>

- ADC

0.7 mm<sup>2</sup> (prototype ⇒room for improvement)

- Digital processor 0.6 mm<sup>2</sup> (estimate)

- in the following we consider the case of 1.5mm<sup>2</sup> / channel

- 64 ch / chip ⇒ ~ 100 mm<sup>2</sup>

Area of the chip on the PCB:  $14 \times 14 \text{ mm}^2$  / chip  $\Rightarrow \sim 3 \text{ mm}^2$  / pad

PCB dimensions < 40 x 40 cm<sup>2</sup>  $\Rightarrow$  ~53000 pads, ~800 FE chips / board

#### PCB topology and layer stack-up

#### PCB topology and layer stack-up

#### Power consumption

- amplifier 8 mW / channel

- ADC 30 mW / channel

- Digital Proc 4 mW / channel

- Power regulation and links 10 mW / channel

- duty cycle: 1%

- average power / channel ~ 0.5 mW / channel

- average power / m<sup>2</sup> 167 W

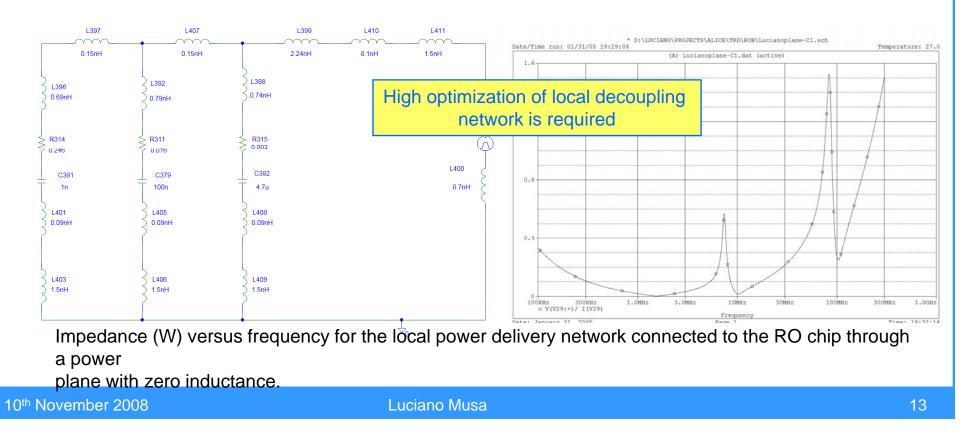

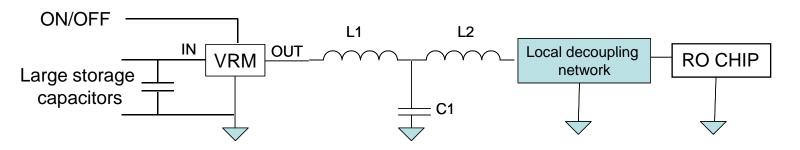

#### **Readout Board power delivery network**

Model used to evaluate the impedance of the local power delivery network