# Silicon tracking system for ILD: integration

A. Savoy-Navarro, LPNHE/CNRS-IN2P3

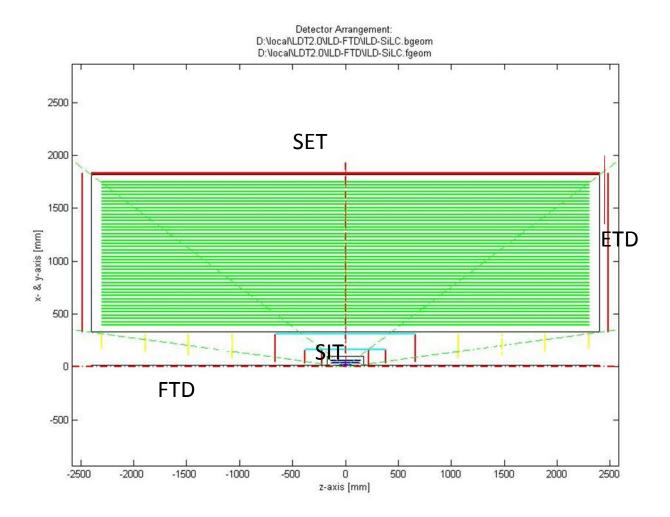

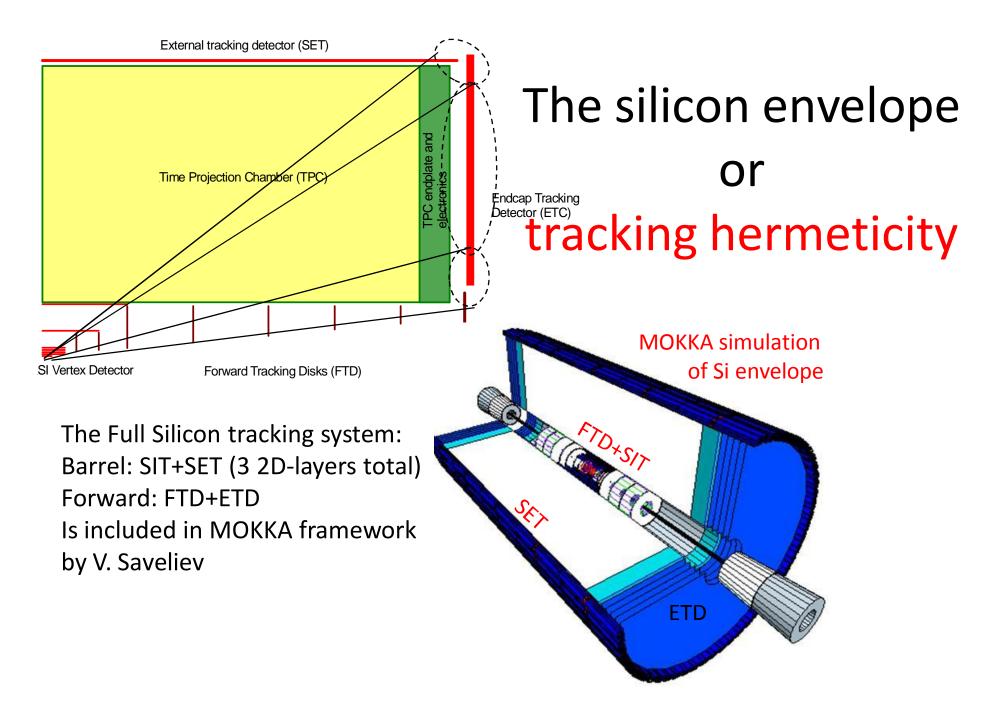

# The Silicon envelope (JE Augustin, M. Berggren, ASN)

(by M. Valentan, LicToy)

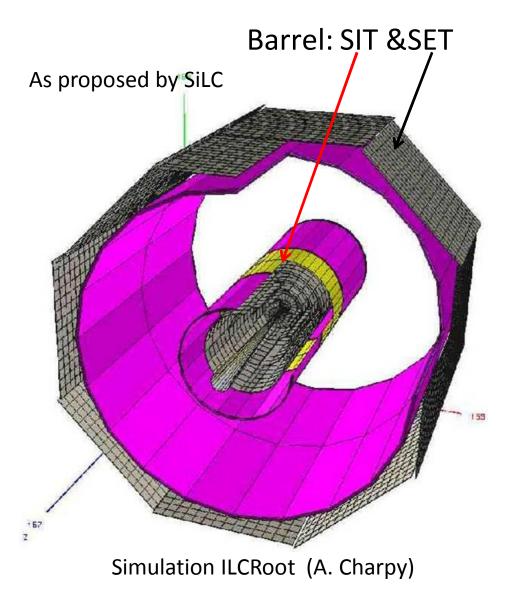

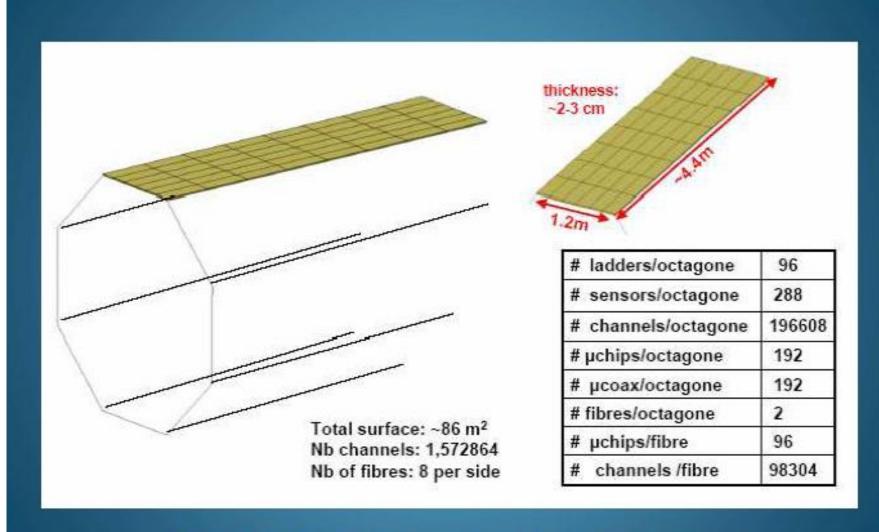

### **ILD Silicon tracking: the barrel components**

Calorimeter shape

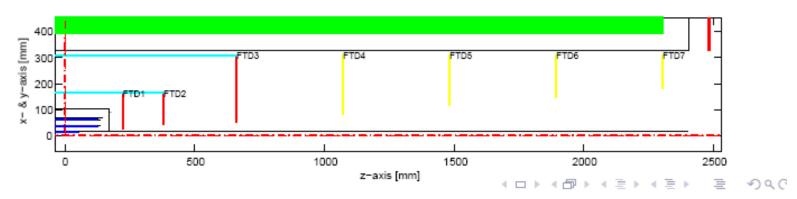

### ILD Silicon tracking: the forward components

#### Very preliminary mechanical design

# Main integration challenge

All-Silicon tracking system: fully integrated system => Much more easy to integrate.

Compared to an all Silicon tracking system (see SiD design for instance) The ILD Silicon tracking system is much more challenging in terms of integration as it is an hybrid system: gaseous + Silicon and each component is in a LINK region between 2 (at least) sub-detectors.

Thus the SiLC collaboration which is working on this system has to address each case separatly this work is undergoing ad we are briefly summarizing here the present status.

# Some important features:

- The FEE readout electronics prove to give: 1mWatt per channel and is power cycled (factor: 70:1) => NO COOLING

- The strips sensors will be edgeless technology, thus a "flat structure".

- The FEE readout will be on detector (bump bonding first then 3D vertical interconnect): high multiplexing in the FEE electronics architecture and NO FE-boards

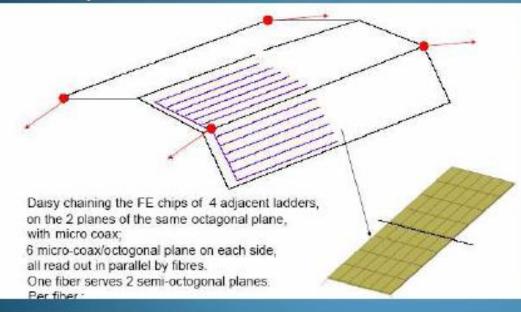

- The processed data are daisy chained (microcoax) on the detector and the sent outside with digital fibers to the outside of the detector (CR)

### Level 2: FE-on detector edges, interface detector with external world

#### Example

Cabling: Level 1 to Level 2: microcoax Level 2 to Level 3: digital fibers

Number of issues related to cabling: Follow industrial advances High rates and high speed, reliability, fault tolerance, robustness Common for all sub

Each red points = buffer + pre-processing 2 (re-order of the temperasing data), transceiver (digital fiber to external world = Control Room) Sends pre-digested data at CR and get slow control and distributes it on detector

### Just an example

Outer Silicon tracking layer : false double sided sensors

# The SET detector integratio

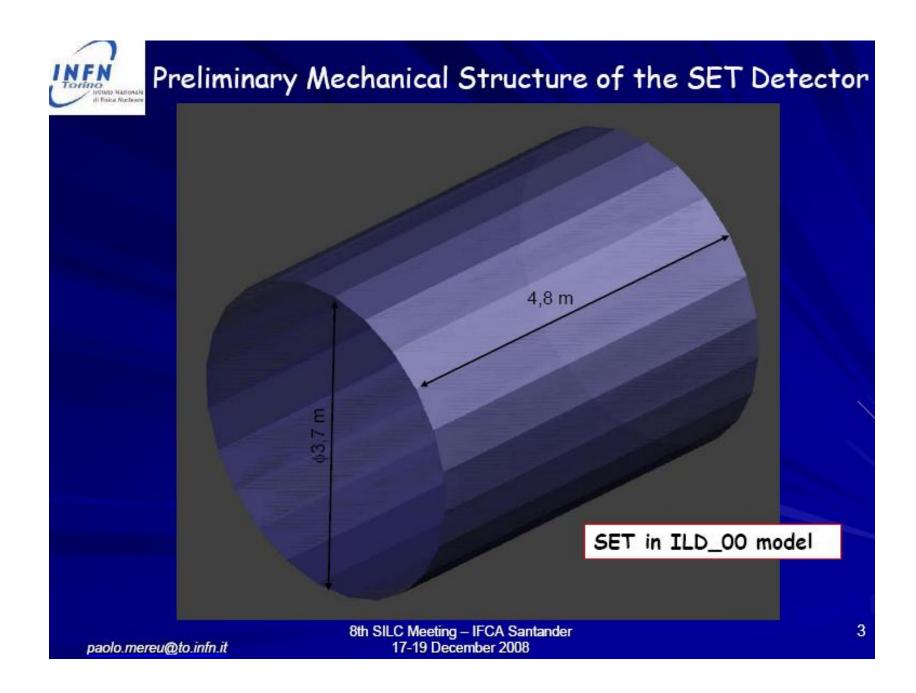

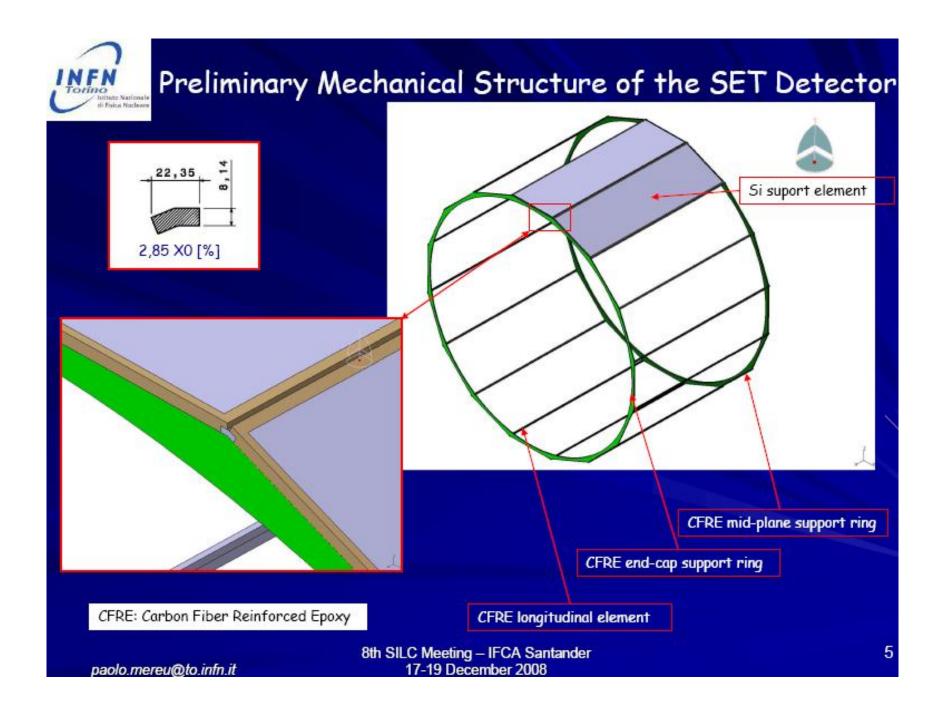

Preliminary Mechanical Structure of the SET Detector

- FEM studies of different lay-outs of SET mechanical structure;

- Production & Integration issues

- SET fixed on TPC

- Targets:

- Good rigidity of the support structure;

- Low X0 [%] for structural elements.

### Preliminary Mechanical Structure of the SET Detector

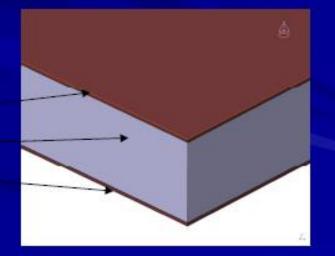

#### BASIC STRUCTURAL ELEMENT

sandwich panel

4 High Module UD Carbon-Epoxy 0,16 mm (0,64 mm) prepeg plies per side

15 mm Rohacell 31 core (PMI) polymethacrylimide rigid foam;

approx. 2,5 kg/m<sup>2</sup>

MATERIAL BUDGET

0,24 X0 [%] 4 UD C plies 0,135 X0 [%] 15 mm ROHACELL 0,24 X0 [%] 4 UD C plies

TOTAL 0,615 X0 [%]

paolo.mereu@to.infn.it

2

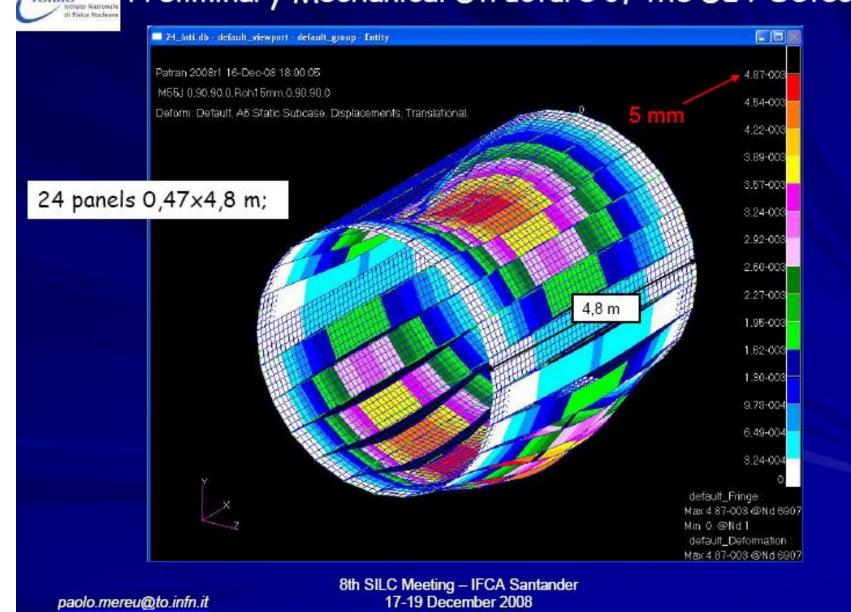

#### Preliminary Mechanical Structure of the SET Detector

orino

#### Preliminary Mechanical Structure of the SET Detector

#### Flat panel solution

- min deformation 0,4 mm;

- 2,4 meter-long sandwich panels;

- modularity: very good for production, Si positioning, assembly and maintenance;

- three fixation discs on TPC needed;

- more panels, better solution...

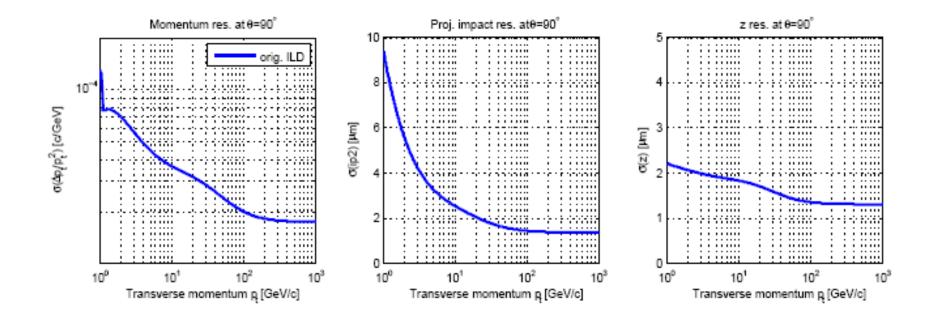

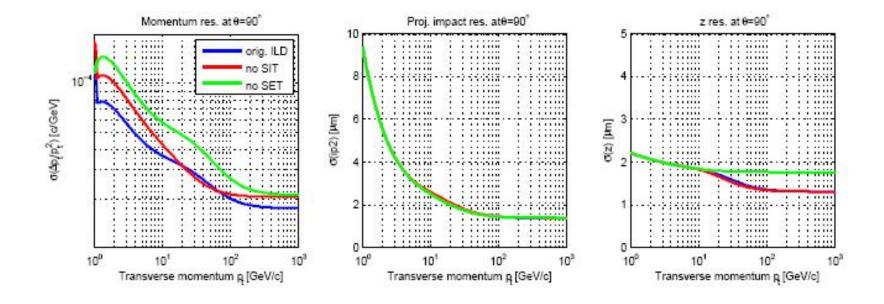

8th SILC Meeting – IFCA Santander 17-19 December 2008 ILD's tracking performance (in the barrel region)

and the effect of the silicon enevelope

Tracking performance in the barrel region of the present ILD setup, in terms of

• Momentum resolution  $\sigma\left(\frac{\Delta p_{\rm T}}{p_{\rm T}^2}\right)$

Projected impact parameter resolution  $\sigma(ip2)$

- **z** resolution  $\sigma(z)$

- evaluated at the inner side of the beamtube

- with LiC Detector Toy 2.0

### Tracking performance as function of $p_{\rm T}$ , at $\vartheta = 90^{\circ}$

(Evaluation at the inner side of the beamtube)

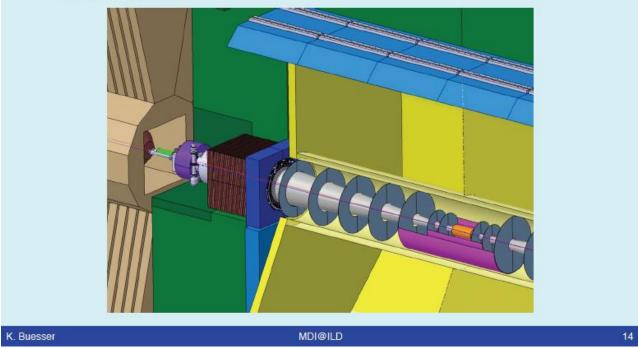

# The FTD integration case

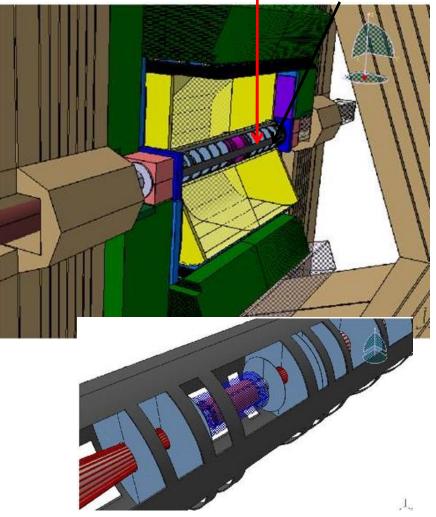

#### Inner Detector Support

- No study of the inner detector support yet

- Important to understand the support of the beam pipe, stability, vibrations, etc.

Preliminary idea: the FTD small disks 7x2 and the 2 DS SIT layers will be included in a single envelope made of rohacel I foam included into 2 foils of C-fiber

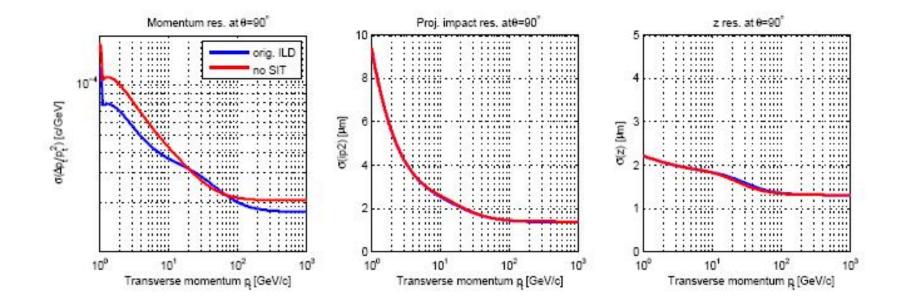

### Tracking performance as function of $p_{\rm T}$ , at $\vartheta = 90^{\circ}$

(Evaluation at the inner side of the beamtube)

### Tracking performance as function of $p_{\rm T}$ , at $\vartheta = 90^{\circ}$

(Evaluation at the inner side of the beamtube)

The SET provides a precise z measurement at large lever arm!

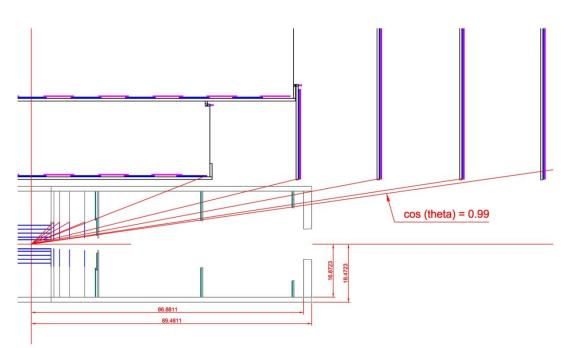

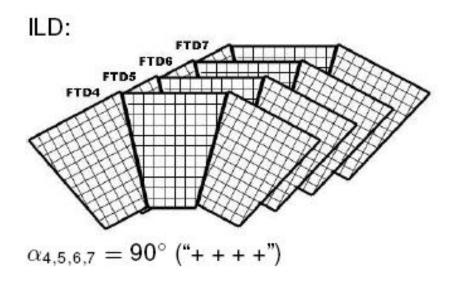

### Optimization of ILD's forward tracker

Up to now:

- 3 pixel disks FTD1-FTD3 near the vertex detector

- 4 microstrip disks *FTD*4-*FTD*7 with equal resolution in R and  $R\Phi$  (stereo angle  $\alpha = 90^{\circ}$ )

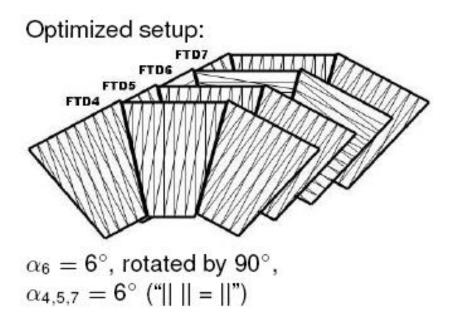

Optimized setup:

- Pixel disks untouched

- use sensors with stereo angle  $\alpha = 6^{\circ}$  (like in CMS)

- FTD4, FTD5, FTD7: one radial strip direction, the other one inclined by 6° (measures RΦ very precisely)

FTD6: module rotated by 90°, measures R very precisely

### Optimization of ILD's forward tracker

# FTD disks

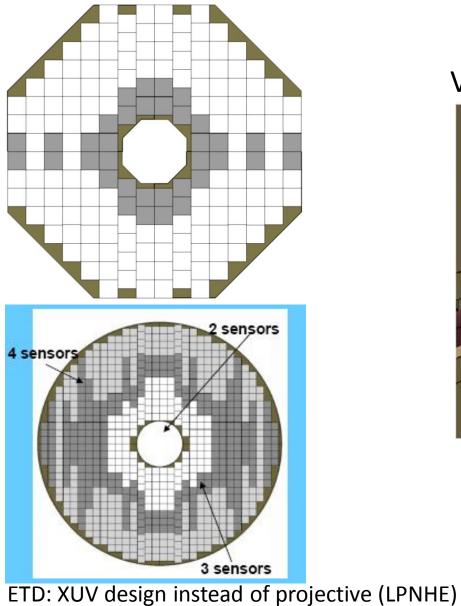

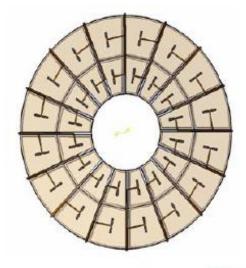

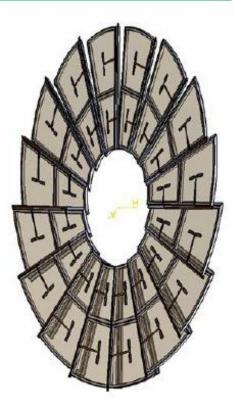

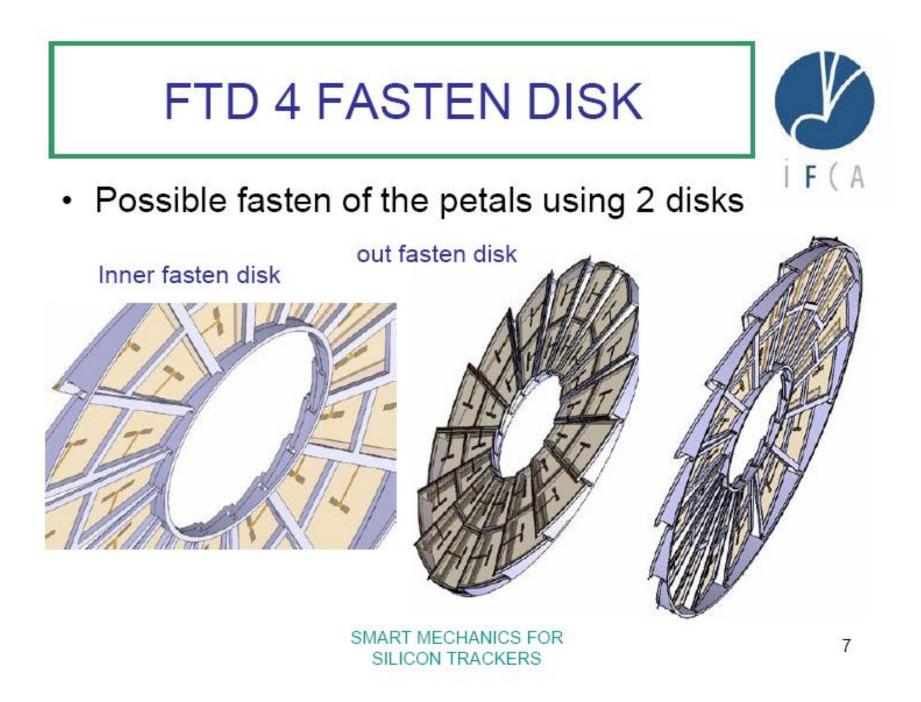

## 4th FTD DESIGN

- Applying the design to all the petals of the FTD

- In the right picture we can see the rotation of the petal respect to the bean pipe axis

- In the bottom picture we can see the 4th FTD perpendicular projection to the beam pipe.

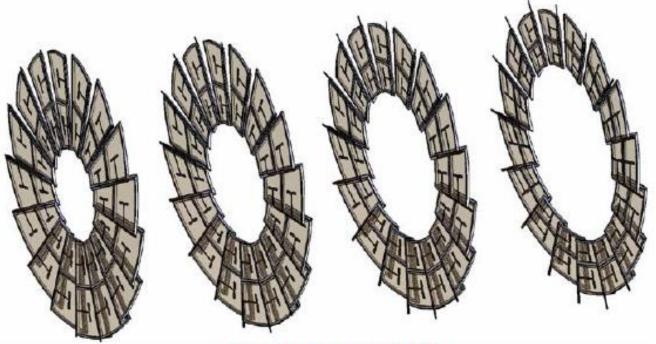

# DISK 5,6, and 7 DESING

Once the FTD 4 geometry and design is defined, we apply this to the 5,6 and 7 forward tracking disk.

# Alignment is going to be worked out by the IFCA team especially (more soon)

# **Concluding remarks**

- Works on integration of the Si components is udertaken by SiLC collaboration

- No show-stoppers

- But need to have collaborative effort with other subdetectors and MDI team to achieve a first reliable integration schema for all the components.