Jaap Velthuis, University of Bristol

Imperial College London

## SPIDER

# VK Collaboration working on Silicon Pixel R&D for future colliders.

- Demonstrate a new improved technique for calorimetry

- Develop a MAPS sensor with in-pixel data processing for tracking applications

- In principle funded until end of 2012

## FORTIS

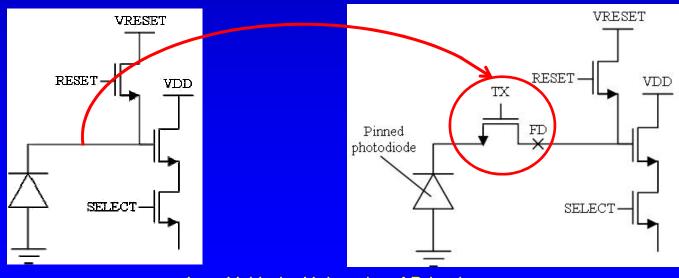

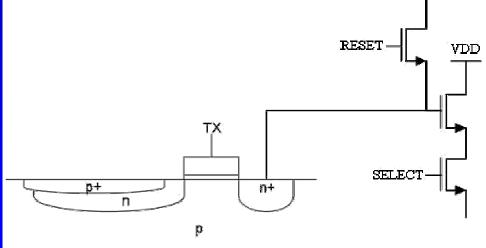

# ◇ FORTIS is the first 4T MAPS for Particle Physics

- 3T CMOS

- Simple architecture

- Readout and charge collection area are the same

- 4T CMOS

- ♦ Three additional elements

- Readout and charge collection area are at different points

VRESET

# 4T Pixel Advantages

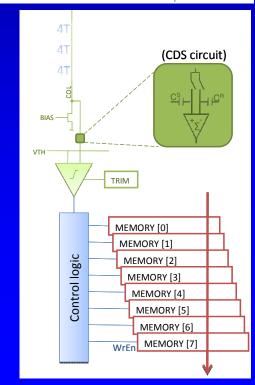

#### ♦ Low Noise

- readout node separated from charge collection area

- The reset noise and fixed pattern noise (FPN) can be removed by in-pixel correlated double sampling (CDS)

- ♦ High Conversion Gain

- Charge is collected on large diode then transferred to the floating diffusion

- Large C gives fast and complete charge collection

- Small C yields large gain

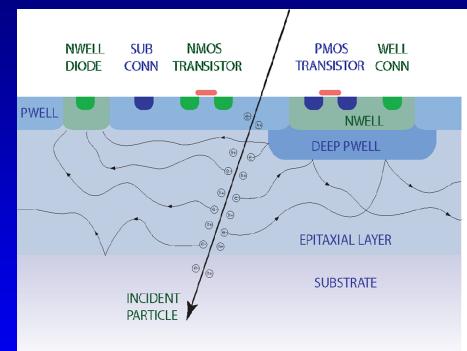

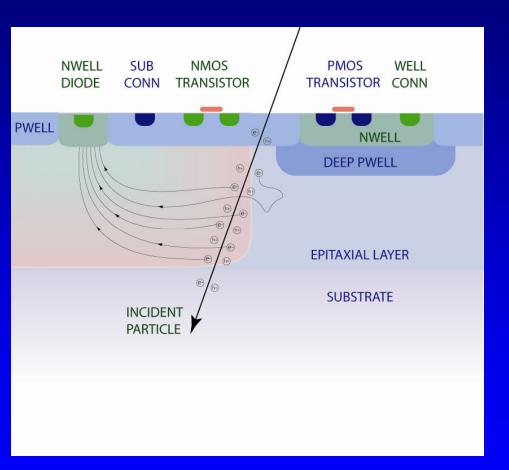

#### Problem in MAPS:

- PMOS electronics need Nwell

- Nwell acts as charge collection diode

- So can't make PMOS without losing huge amount of Q

- ♦ New development: make deep pwell with Nwell inside

→ can do CMOS

- Road to data processing in pixel

- Some FORTIS have empty deep pwell to test effect of Q collection

# Substrate Resistivity

- High resistivity (intrinsic) silicon enlarges the depletion region to fully occupy the pixel

- Majority of deposited charge now falls in a depletion region and is collected by electric field

**SPiDe**

- Improved charge collection efficiency

- Faster charge collection (drift vs diffusion)

- Some FORTIS have high res

## FORTIS Results

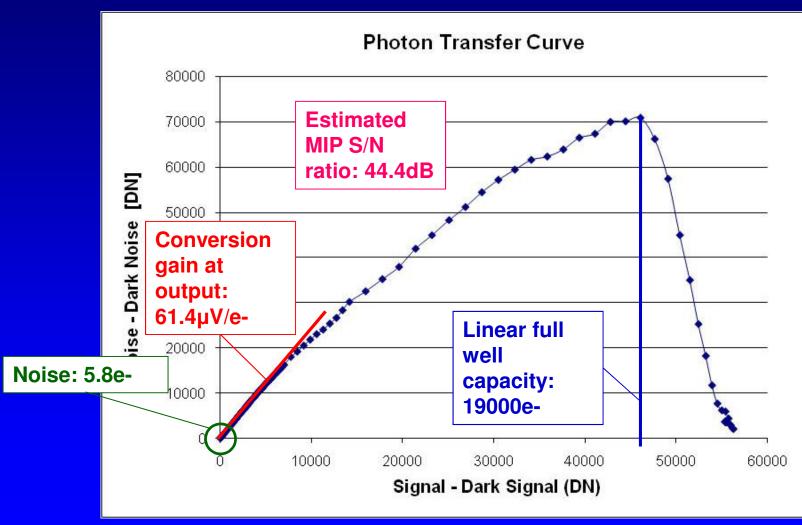

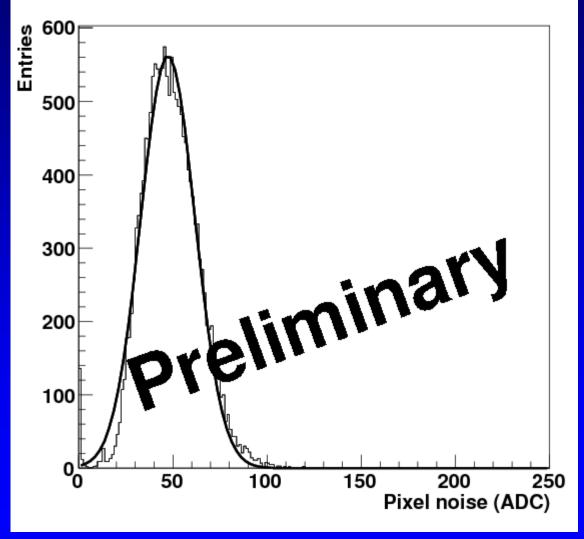

#### FORTIS results

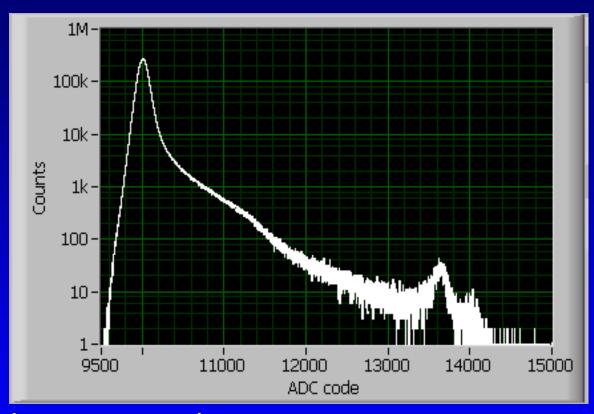

◆ <sup>55</sup>Fe Photons (preliminary)

- Conversion gain = 56  $\mu$  V/e<sup>-</sup>

- Noise (from dark fwhm) =  $7.7e^{-1}$

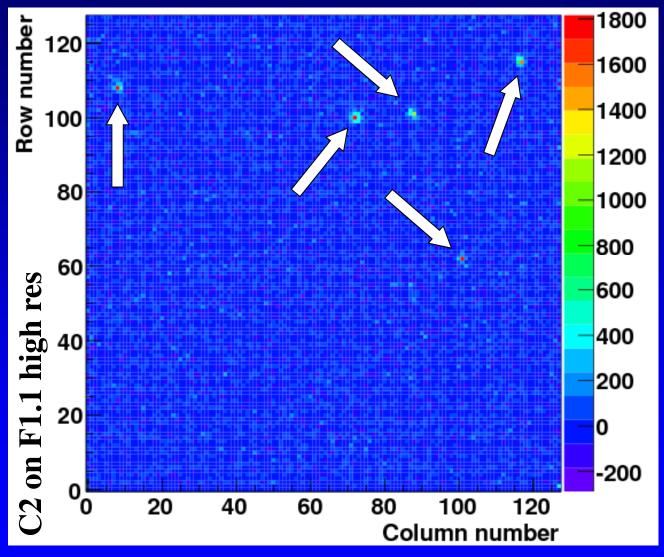

# Some test beam pictures

We see hits...

Jaap Velthuis, University of Bristol

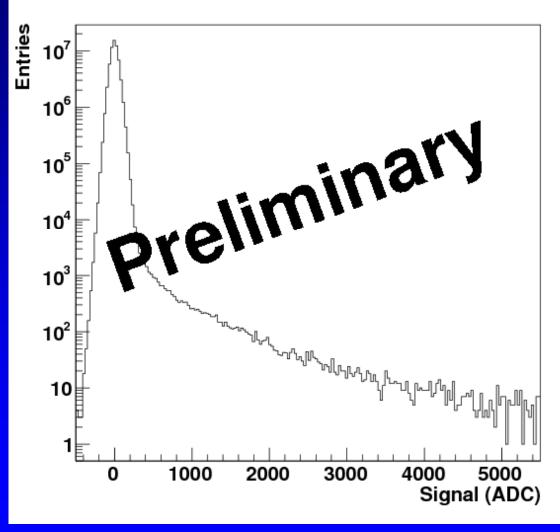

# Raw S/N for each pixel

Jaap Velthuis, University of Bristol

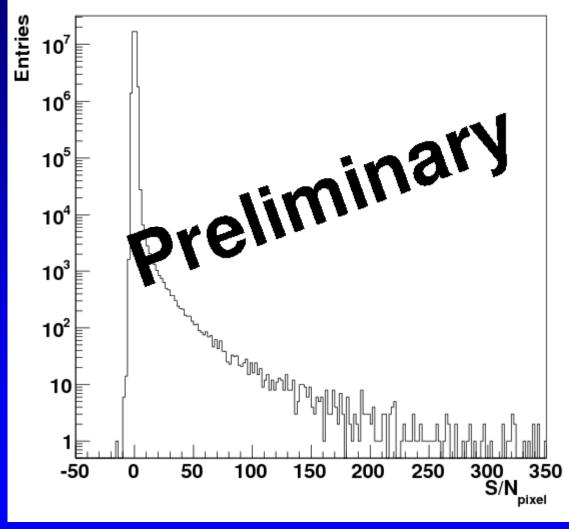

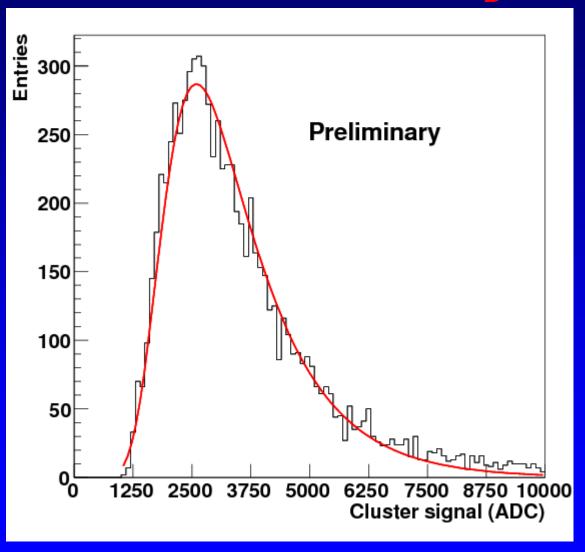

# Cluster signal

SPiDeR

♦ Corresponds to

S/N~50

Data analysis just started

Still need to match up with telescope

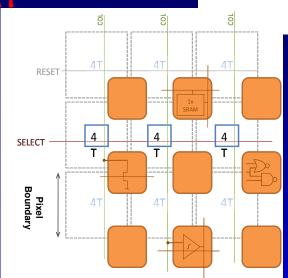

# The future: Cherwell

- within a pixel

- Investigation of data reduction/clustering

- Low noise using transfer gate, CDS and in-pixel amplification

- Low power using rolling shutter readout

- Combine 128 pixels in 1 strixel

- Cherwell1 will be submitted in spring

- Tests using sources & laser; no beam test

- Cherwell2 will be submitted beginning 2012

- Cherwell2 will be extensively tested

- 3 week beam test at CERN with high momentum pions

# Our needs/wishes

- ♦ Beam time!

- Need telescope

- Really like EUDET concept:

- ♦ Know the TLU; no big interfacing problems to be solved onsite

- Tracking and alignment software provided

- ♦ Essentially get the tracks

- Would like patch panels (bnc and fiber optic) between hut and area

- Cabling is pain

- ♦ Would like large XY-stage

- ♦ Would like cooling option

- ◇ If possible could arrange many user beam tests

- Remote shifts; saves lots of travel money

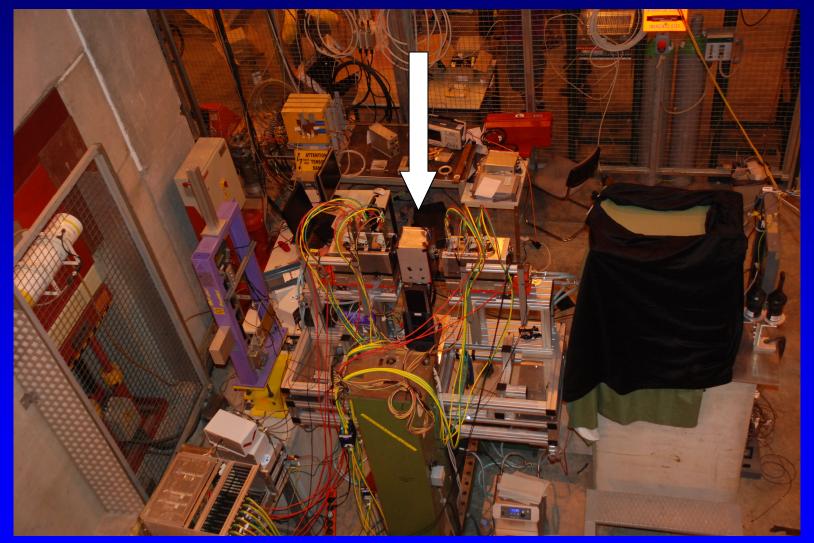

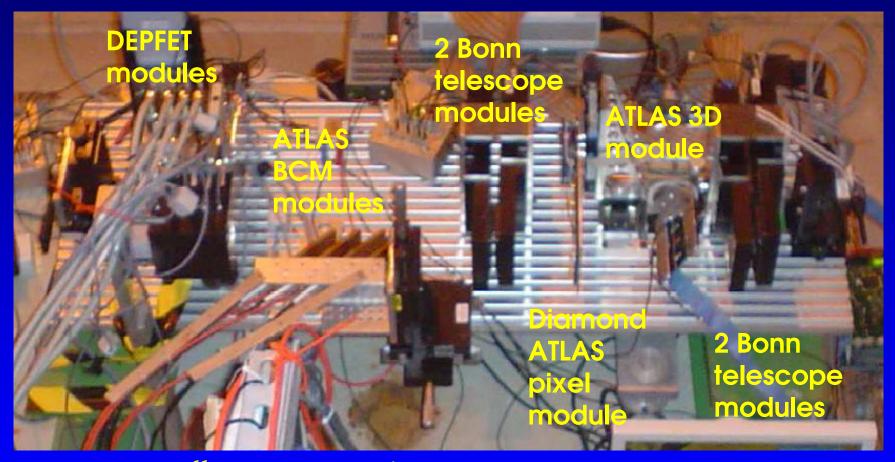

## Nice example

Tested 4 different devices at the same time

Currently only possible because 1 institute + friendly colleagues

## Summary

- SPIDER is developing a novel tracking device based on MAPS with in-pixel data processing

- Two iterations. Final chip will be delivered in summer 2012.

- Would be great to have common infrastructure: patch panels, large XY stage, cooling & TLU

- Very interested in collaborating with many other users