# CALICE SiW Ecal

- Results and Plans -

Roman Pöschl LAL Orsay

## EUDET Annual Meeting Geneva/Switzerland and CERN October 2009

EUDET Annual Meeting 2009

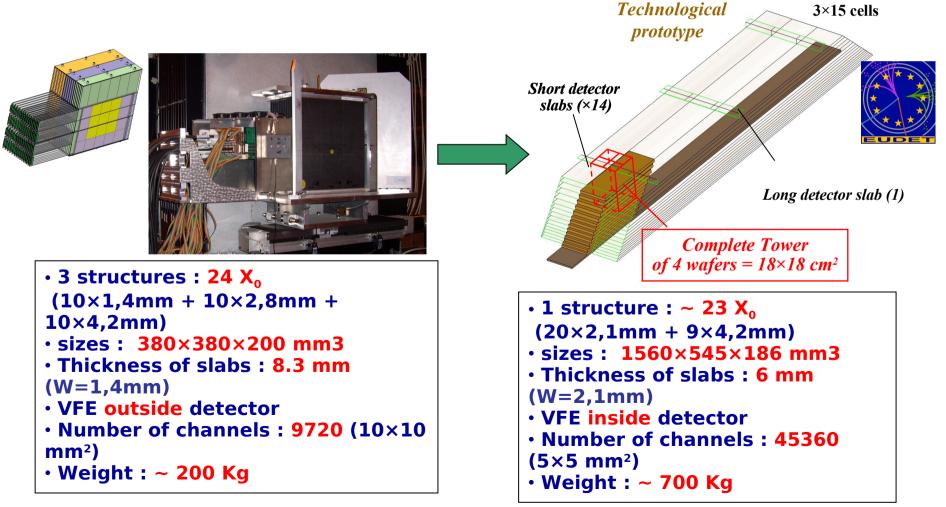

# **EUDET Prototype**

- Logical continuation to the physical prototype study which validated the main concepts : alveolar structure , slabs, gluing of wafers, integration

- Techno. Proto : study and validation of most of technological solutions wich could be used for the final detector (moulding process, cooling system, wide size structures,...)

- Taking into account industrialization aspect of process

- First cost estimation of one module

2

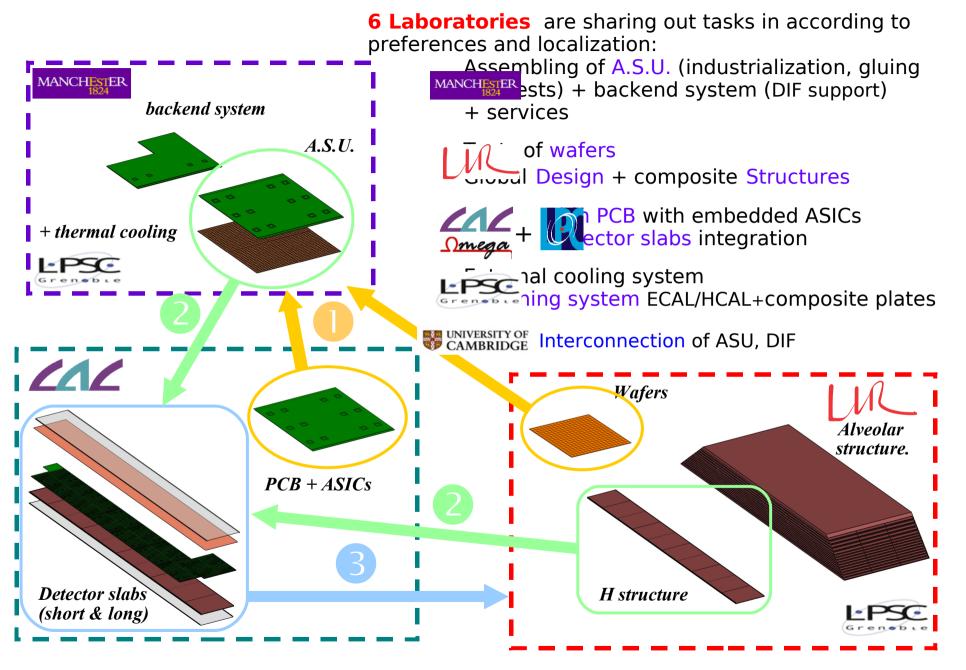

### The groups working on the EUDET Electromagnetic Calorimeter

- What we call "EUDET Module" is in fact the next SiW Ecal CALICE Prototype

- Financial support by EU

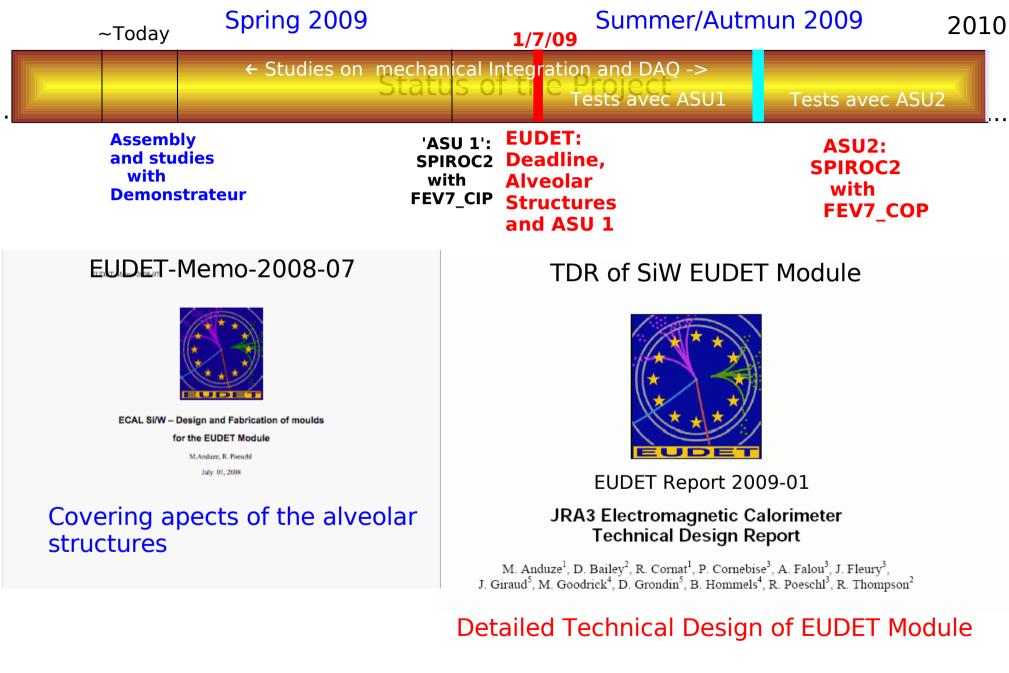

# Time Scale of Project

### **Parties Involved**

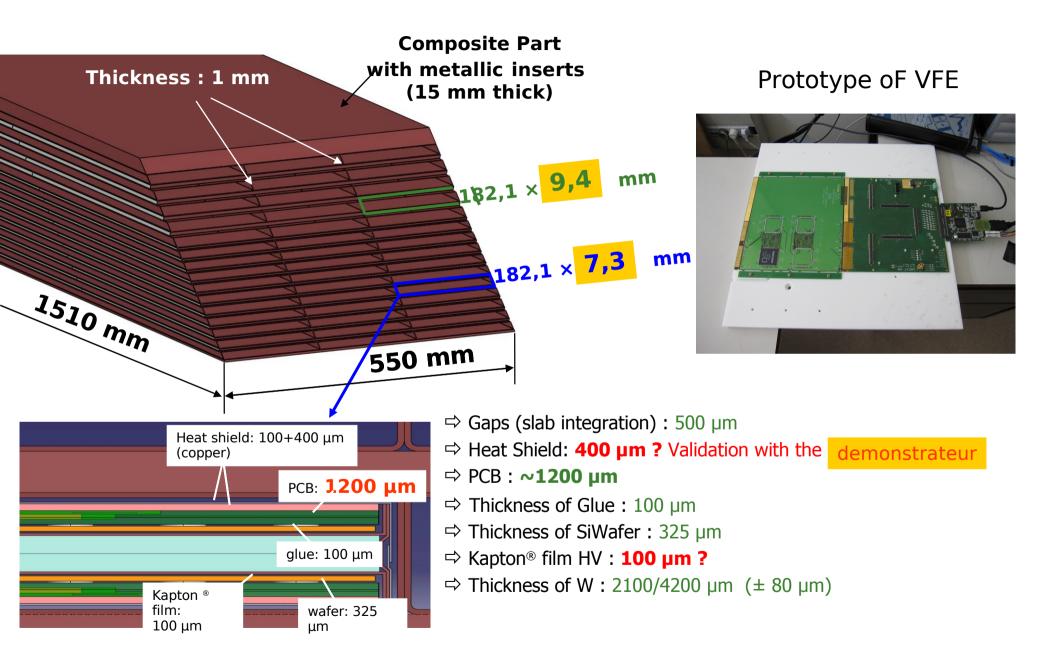

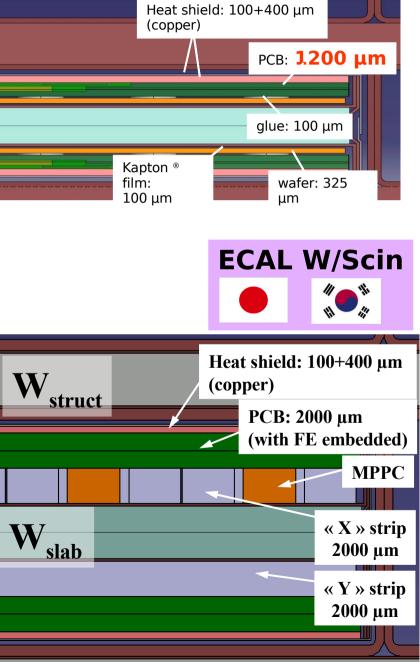

# Module EUDET – Current Design (final – developped 2008)

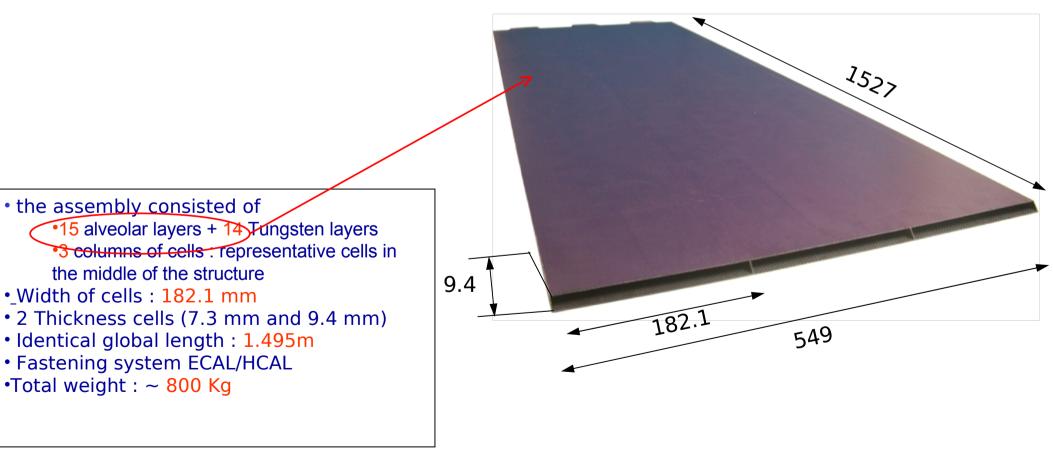

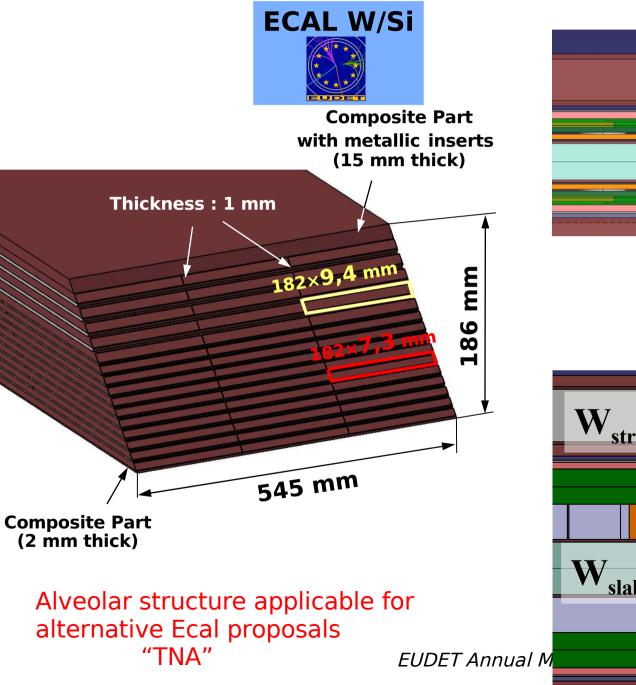

#### **Alveolar Structures with (~) ILC Dimensions**

# EUDET design

### New layer built for the EUDET Module

- Cells width is based on 182.1 mm

- Used for BEAMTESTS.

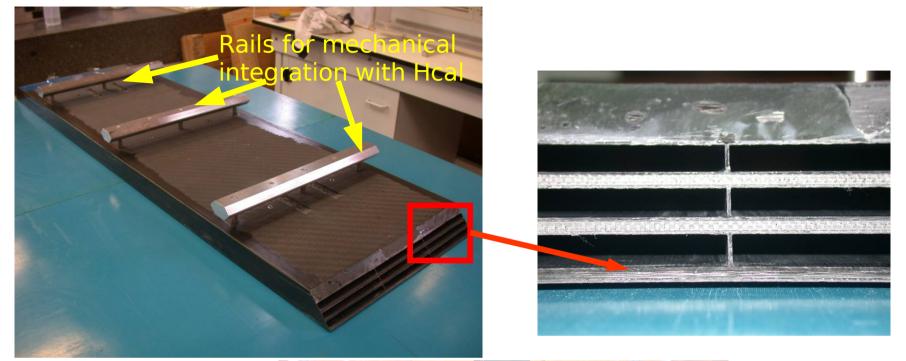

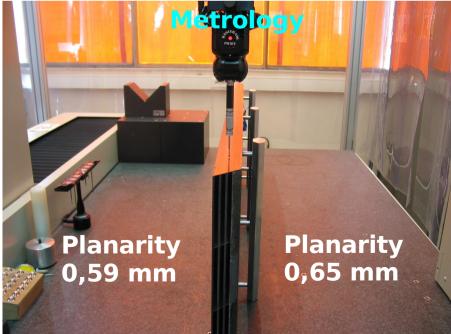

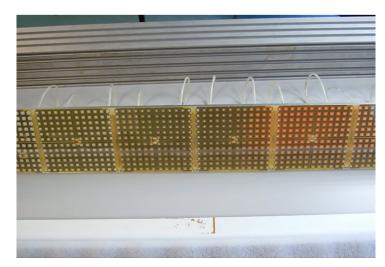

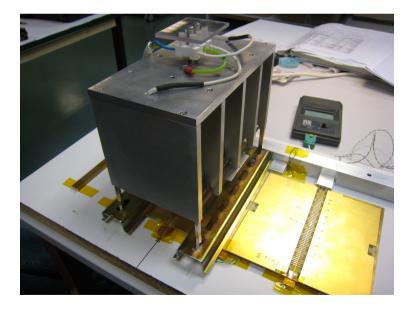

First EUDET layer alveolar structure

## Alveolar structure (based on EUDET)

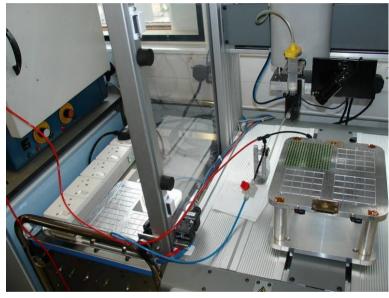

### Gluing of ASUS

- Controlled glue dot deposition on the PCB

- The (four) Si Wafers are picked up, aligned and placed on the PCB

- Accurate thickness and planarity control via vacuum jigs

- The assembled ASU is allowed to cure

Test board with Dispenser Robot

"Gluing" rate 0.4 Hz

#### **BGA Workstation for Wafer Placement**

Precise Wafer Placement by Split Field Optics

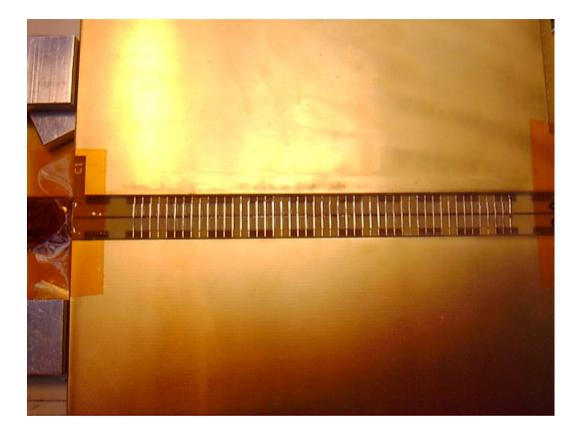

#### The joint between two boards

- Joint by halogen lamp heating up tin-bismuth soldering paste (Method developed by U. Cambridge)

- Heating Temperature ~200° C

Delicate Process for Demonstrator – Easier for EUDET Module EUDET Annual Meeting 2009 Thermal Layer – Developping the Techniques for Layer Construction

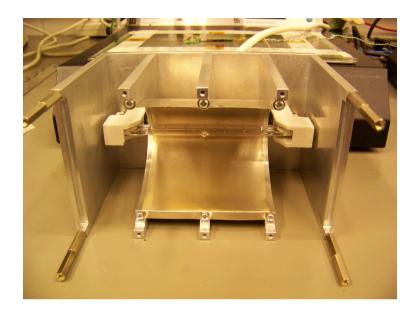

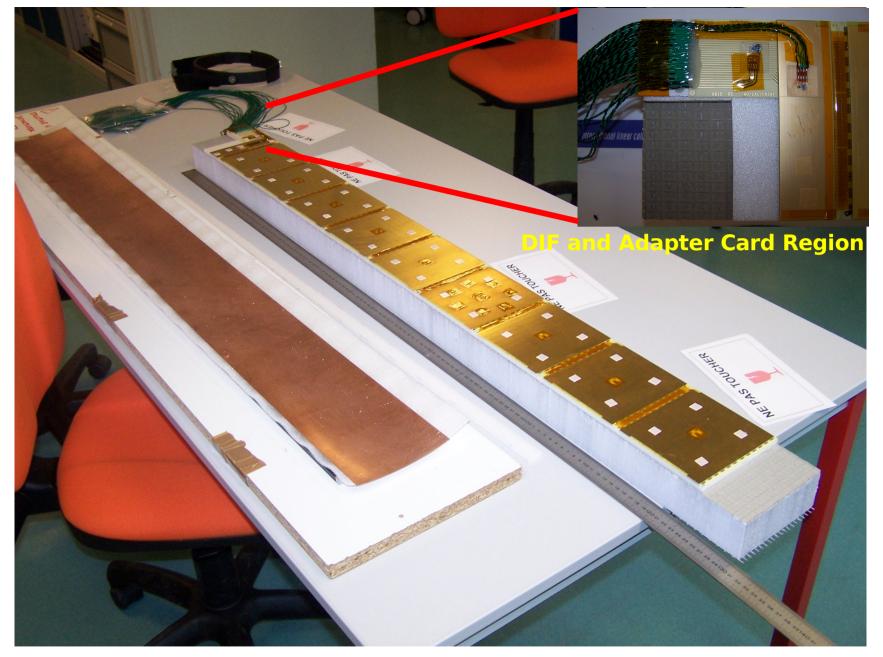

Proof-of-principle to build long layers EUDET Annual Meeting 2009 Assembly Tools – Handling of fragile layers

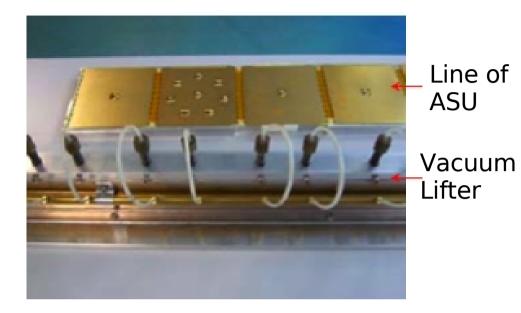

Handling by vacuum lifter

Positioning of Vacuum Lifter on ASU Line

Vacuum Lifter Line of ASU

### (Careful) handling of ASU Line established

- Detector Assembly needs more tools and an assembly hall

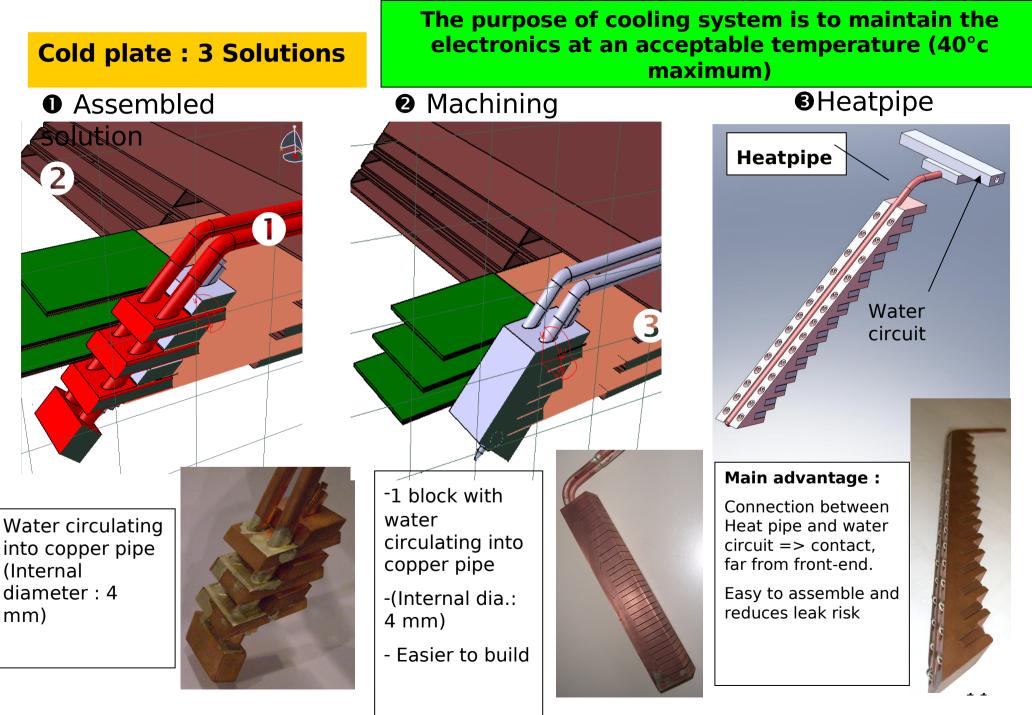

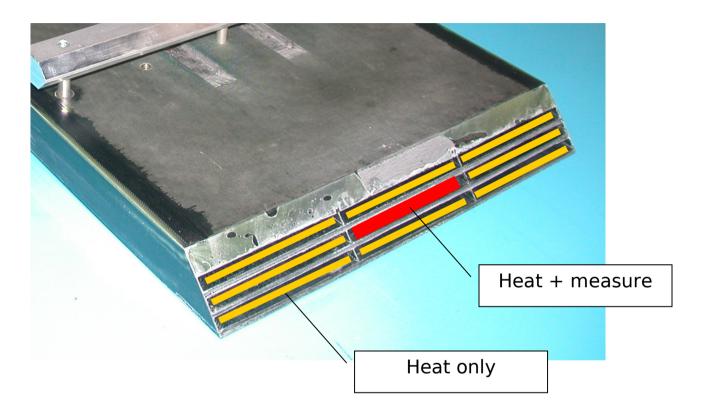

## EUDET COOLING

Reminder on demonstrator – Nex step

- Insertion of wrapped thermal slab into alveolar structure Important step towards EUDET (and ILC!!!)

Continuation of thermal tests with inserted thermal slab

Construction of heating mock-ups to establish realistic conditions

Time scale ~ September 2009

Pieces for 'read' EUDET Module will be ordered in autumn 2009 Funding assured!!!

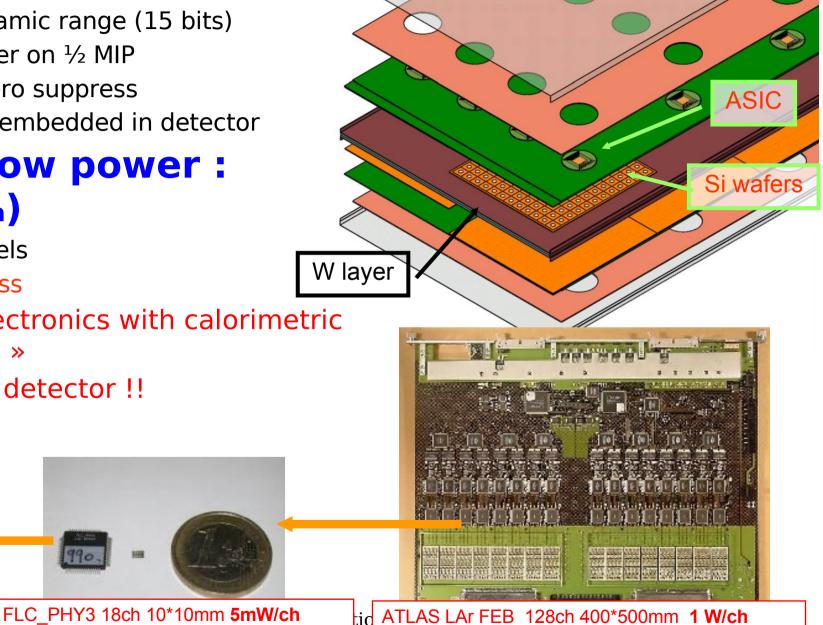

ILC : 25µW/ch

# ILC Challenges for electronics

- **Requirements for electronics**

- Large dynamic range (15 bits)

- Auto-trigger on  $\frac{1}{2}$  MIP

- On chip zero suppress

- Front-end embedded in detector

# - Ultra-low power : («25µW/ch)

- 10<sup>8</sup> channels

- Compactness

- « Tracker electronics with calorimetric performance »

- No chip = no detector !!

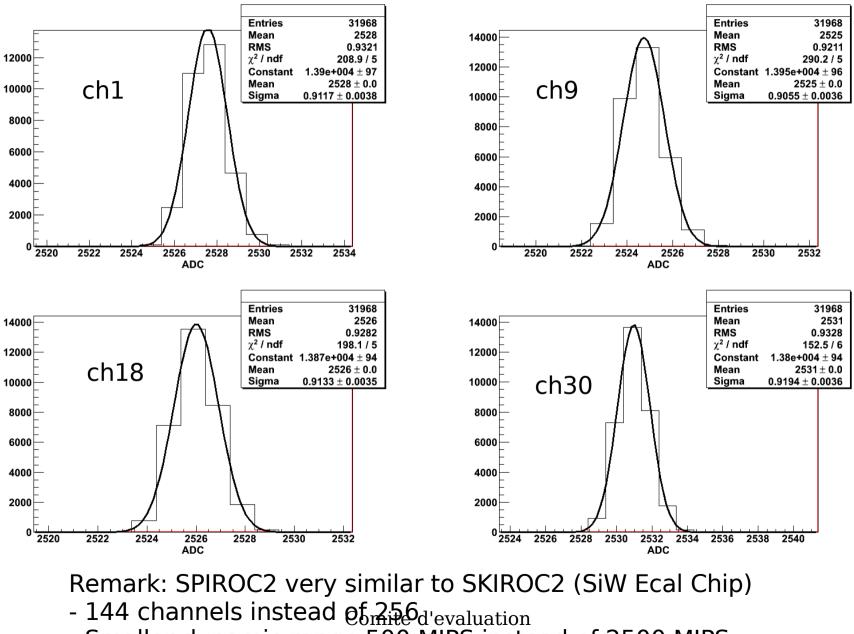

### Characterisation of SPIROC2 Chip – Used for first Ecal Prototype Gaussiennes – 2 Volt

- Smaller dynamic range 500 MIPS instead of 2500 MIPS

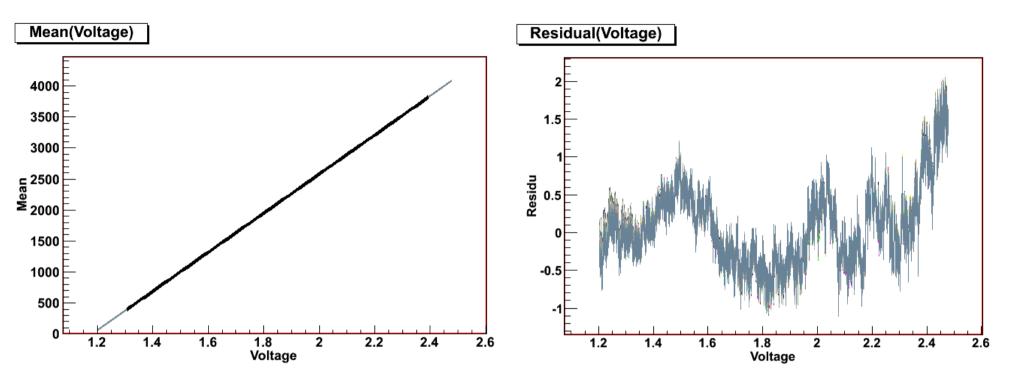

# Linearity of ADC - Chip n°2

- Linearity measured in 250 muV steps between 1.2V and 2.5V input Voltage

- ADC of Chips linear in dynamic range

- On going Study of signal propagation through Chip (Pre-Amp, Shaper ...) Already promising results

### **Chip ready to be used in SiW Ecal Prototype**

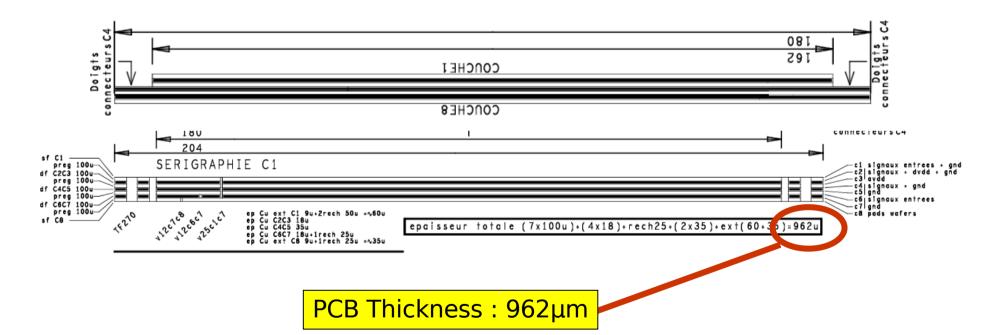

## PCB for first SiW Ecal Prototype

| Pile-up<br>TOP<br>C2<br>GND | GND + Input chip signal<br>horizontal routing + DVDD + |  |

|-----------------------------|--------------------------------------------------------|--|

| C3                          | AVDD                                                   |  |

| C4                          | GND + vertical routing                                 |  |

| C5                          | GND (pads signal shielding)                            |  |

| C6                          | pads routing                                           |  |

| C7                          | GND (pads shielding)                                   |  |

| BOT                         | PADS                                                   |  |

#### <u> 4 drilling sequences</u> :

- Laser C7-C8 120µ filled

- Laser C6-C7 120µ Mochanical C1 C7

- Mechanical C1-C7

- Mechanical C1-C8 (for PCB fastening)

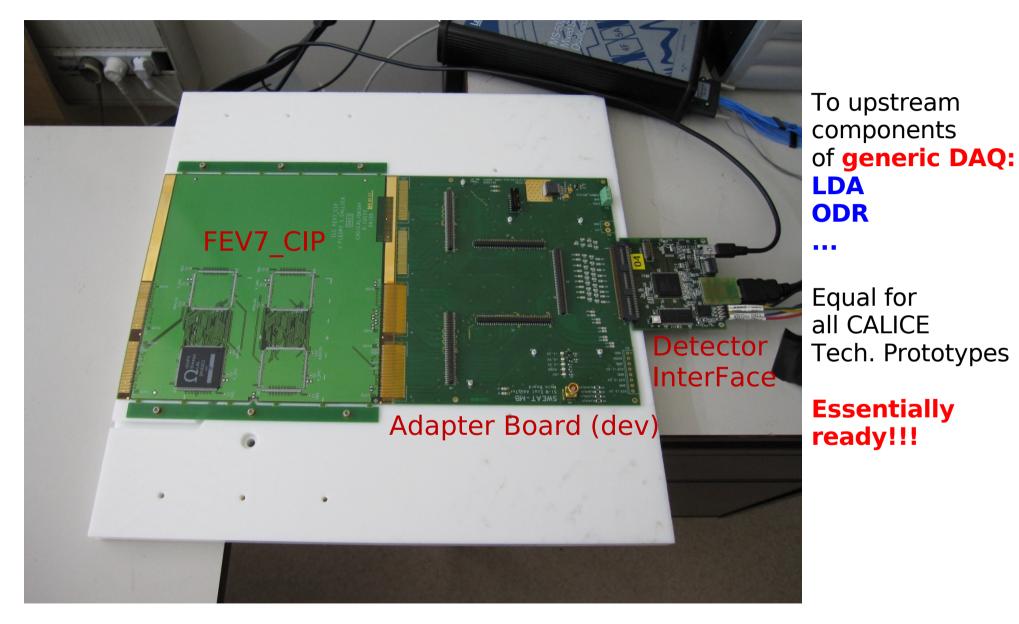

FEV7\_CIP (Chip in Package):Predecessor for final board with all functionalities Next Step FEV7\_COB (Chip on Board) Final Aim FEV8

# First SLAB prototype

EUDET Annual Meeting 2009

# **PIN Diodes Silicon Sensors**

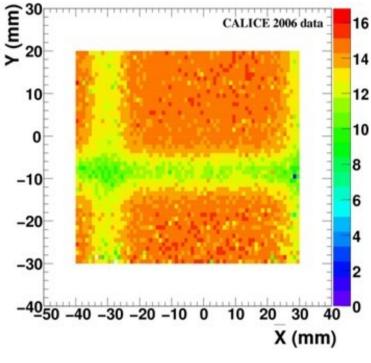

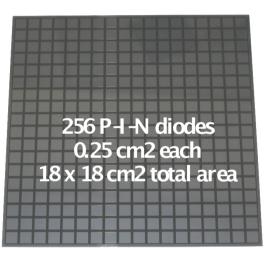

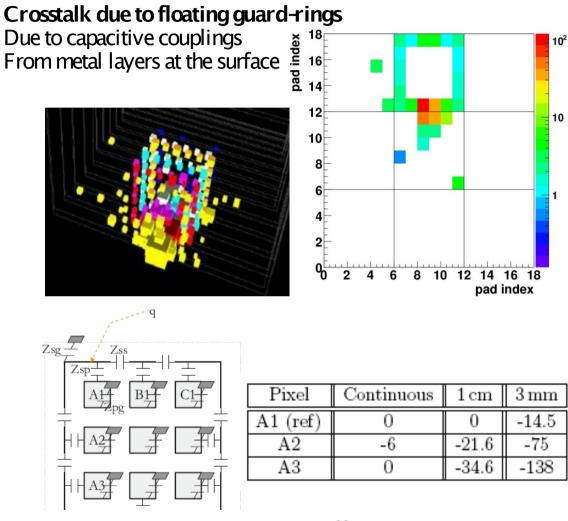

Designed for ILC : Low cost, 3000 m2 Minimized number of manufacturing steps Target is 2 EUR/cm2 Now : 15 EUR/cm2 Use of floating guard-rings Dead space optimization

Guard-rings do not collect charges Dead space to be reduced

Hit map from physics prototype

#### **EUDET** layout

Prototype from Hamamatsu 40 Wafers at Hand out of 180 needed!!!

### R&D on Crosstalk Segmented Guard Rings layout Simulation models at Silicon or Electrical Level

$T = T_{elec} \times T_{pix} \times (T_{seg} \times T_{ss})^{N_{seg}} \times T_{seg} \times T_{inj}$

# I(V) and C(V) characterization

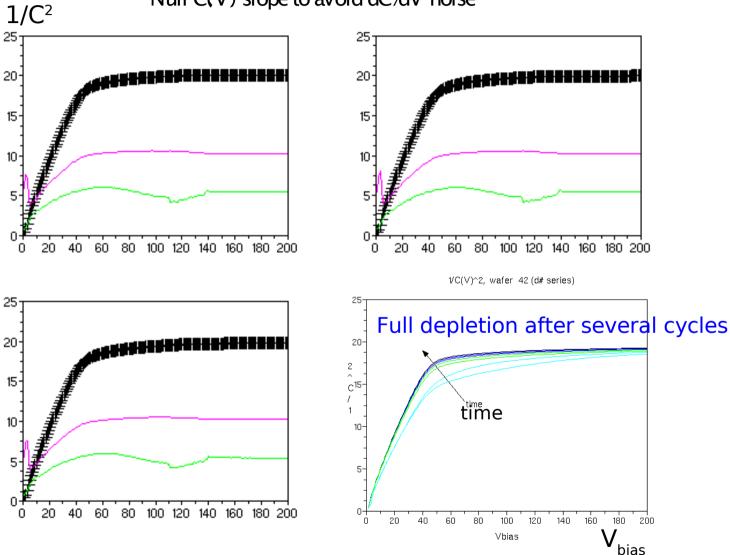

B reakdown voltage > 500V Current leakage < 4 nA/pixel (chip is DC coupled) Full depletion at 150 V Null C(V) slope to avoid dC/dV noise

### - Working set of Wafers is Milestone for EUDET $\checkmark$

- Finding a way to produce cost saving SiW is a very critical item for the completing the EUDET module and also for the ILC

Will be one of the top priorities in the coming year

Clearly, a nice opportunity for TNA Testing new wafers on working electronics bench

- EUDET funding exhausted by set of 'Hamamatsu SiW'

Funding for entire module might need to be stretched over several years!!!!

**Conclusion and Outlook**

- Technical Design finished in Oct. 2008 Preparation of Demonstrator Tests since then

- Since February studies with the demonstrator

- Measurement for thermal analysis

- Assembly of alveolar structure finished

- Integration tools for long slab very well advanced

#### **Demonstrator studies**

#### cover most if not all aspects described in EUDET proposal

The collaboration is a real pleasure, thanks to everbody involved!!!

Conclusion and Outlook cont'd

- Towards the EUDET Module

- Focus of getting the VFE accomplished during 2010

- Meeting EUDET Timeline with "intermediate" solution for VFE SPIROC in SKIROC on a FEV7 variant

- "Shipping" signals out Interface to the DAQ is addressed

- Results with first ASU expected during this winter

Electronics testbench setup In Debugging Phase

- Construction of Alveolar Structure for 'real' EUDET Module has started Completion during first half of 2010

Once first cosmics on electronics testbench seen we can say

# SiW Ecal protoype is ready

Funding for full blown detector is however on critical path in several fields

Expect Assembly to start towards the beginning of 2011

First (beam)tests with small units maybe still during 2010

Testbeams with EUDET Module towards middle/end 2011