# DAQ system hardware status

David Ward (Cambridge)

for UK DAQ groups: Cambridge, Manchester, RHUL and UCL

### **Outline**

- System overview and recent progress

- Status of the individual (hardware) components

- System tests

- Numbers of each component and availability

- Summary and issues

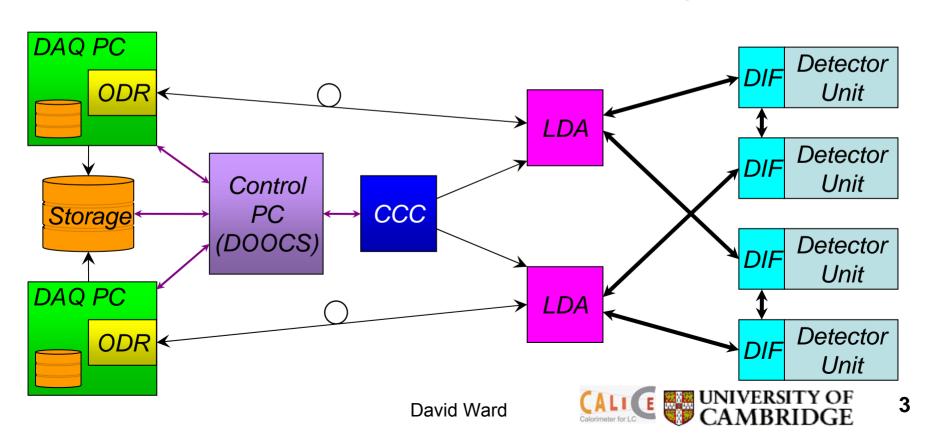

## DAQ system overview

(Detector Unit: ASICs)

**DIF**: Detector InterFace connects generic

DAQ and services

**LDA**: Link/Data Aggregator fansout/in DIFs

and drives links to ODR

**ODR**: Off-Detector Receiver is PC

interface

**CCC**: Clock and Control Card fans out to

ODRs (or LDAs)

**Control PC**: Using DOOCS

## Overall status—progress in last year

- Final hardware tweaks and production versions of relevant components.

- Hardware orders so as to have enough systems available for lab and beam tests.

- Firmware improvements and finalisation.

- Delivered a full set of components to LLR for use and testing.

- System tests getting DAQ chain running are ongoing.

### **ECAL DIF**

- ❖ The ECAL DIF developed by the Cambridge group; HCAL DIFs developed by other groups, but all within the DIF task force.

- ❖ Produced a prototype board which worked well, in use at LLR. Have reduced number of components, whilst maintaining functionality (e.g. FPGA).

- ❖ Two DIFs have been produced and being used in system tests. Will now produce full run of 40 ECAL DIFs—all PCBs and components in-house.

- Not time critical but will start soon.

- Firmware being debugged in DAQ system tests.

## C&C card

- Incorporates all needs and connectors requested by calorimeter groups.

- ❖ Full complement of 10 boards with power supplies tested (one of which in LLR).

- CCC link to LDA still needs to be done: simple PCB attached to LDA.

- ❖[Functionality

- CLOCK : machine

- FAST\_OUT : transfer asynchronous triggers

- ❖ FAST\_IN : used by DIFs to "stop acquisition"

- TRAINSYNC\_OUT : synchronisation of all front-end slow clocks]

#### LDA

- ❖ The LDA (from Enterpoint) consists of: a Mulldonoch2 baseboard; an add-on HDMI board to connect to 10 DIFs; and an add-on ethernet board to connect to an ODR.

- Have 20 baseboards in-house.

- Have 5 ethernet boards in-house, 20 being manufactured.

- Have 5 HDMI boards in-house, 20 being manufactured.

- Firmware development ongoing :

- get DIF <=> LDA link running

- general improvements (different compilers)

- new code posted

- ❖ Hardware problems have been fixed by Enterpoint and new add-on boards should be delivered in two weeks (hopefully).

- Slightly complicated by Marc Kelly's departure.

So this is an example of commercially-available, off-the-shelf equipment ... all of which needed some corrections / additions / modifications from ourselves...

## ODR and DAQ PC

System has generally been stable for a while:

- Firmware written.

- Control software.

- Linked to LDAem, LDA, etc...

- Performance optimised.

- Working on documentation and code repository in SVN.

- Interfaced with DAQ software.

- Customised DAQ PCs.

- Have 8 ODRs in house along with 6 DAQ PCs, one of each is at LLR.

## **DAQ Software**

- Started development using DOOCS software mainly by V.Bartsch and T.Wu.

- They have both left and David Decotigny (LLR) has taken over.

- Discussions ongoing also within context of FP7 bid for ideas as to the best way to go.

- ❖ We (UK) will be able to provide some additional effort for next ~6 months to help.

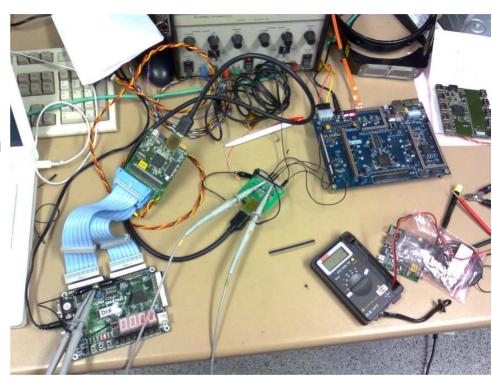

# System tests

- ❖ Have a system set-up in UCL :

DAQ PC with ODR <=> LDA <=> DIF :

- using network analyser and 'scope to check signals

- using both prototype and production DIF

- this highlighted bugs and improvements...

- ❖ have sent commands ODR => LDA and received data back LDA => ODR

- ❖ have sent commands all the way up to the DIF, ODR => LDA => DIF

- link DIF => LDA has not yet been established—firmware updated and being debugged

- hopefully just a matter of a weeks until working.

### Hardware numbers needed

- ❖Detectors' requirements :

- ◆ ECAL: 30 layers → 30 DIFs, 3 LDAs, 1 ODR and DAQ PC, 1 CCC

- ❖ AHCAL: 48 layers → (48 DIFs), 5 LDAs, 2 ODRs and 1 DAQ PC, 1 CCC

- ◆ DHCAL: 40 layers → (120 DIFs, 14 DCCs), 2 LDAs, 1 ODR and DAQ PC, 1 CCC

- In general UK DAQ groups have to provide :

- ❖ 30 ECAL DIFs, 10 LDAs, 4 ODRs, 3 DAQ PCs, 3 CCCs;

- sufficient spares for test-beam running;

- additional systems for tests in labs.

- ❖Our procurement schedule is :

- ❖ 40 ECAL DIFs (have 2, components for 40)

- ❖ 20 LDAs (baseboards in-house, add-on boards expected in couple of weeks)

- \* 8 ODRs and 8 DAQ PCs (have 8+6)

- 10 CCCs (have 10)

# Summary

- Progress made (firmware, purchasing, developing) for all components and system as a whole.

- We are gradually building up a stock of components which should be sufficient for lab and beam tests. Complete very soon.

- Completion of EUDET milestone, "DAQ system available" satisfied by having production versions of hardware and a system at another institute.

- ❖ We need to have a debugged system within the next few weeks, then make sure the system at LLR is also running and stable and then provide systems to other groups.

- By the end of the year, UK effort will decrease rapidly.

- Work is and will be thoroughly documented on the wiki and archived in a code repository