# Readout electronics for LumiCal detector

#### M. Idzik for FCAL Collaboration

Department of Physics and Applied Computer Science AGH University of Science and Technology, Krakow

#### EUDET meeting 19-21 October 2009

イロト イポト イヨト イヨト

#### Front-end electronics development

2 Development of 10 bit pipeline ADC

Peripheral circuits (DAC, Bandgap, LVDS)

< 🗇 🕨

→ Ξ → < Ξ →</p>

ъ

Front-End

ADC 00000000 Peripheral circuits (DAC, Bandgap, LVDS)

Summary

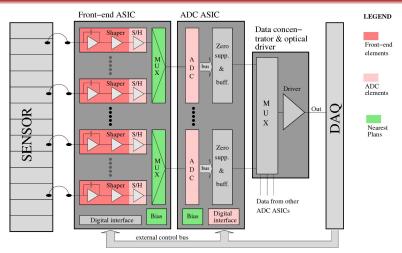

## LumiCal Readout System

Present developments done in 0.35  $\mu m$  CMOS technology, not necessarily final choice...

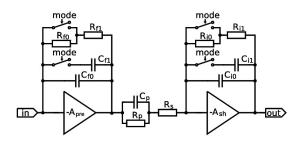

# Front-end requirements (old)

#### Components

- Charge amplifier

- Pole zero cancellation

- 1<sup>st</sup> order shaper

- $C_{det} = 10 \div 100 \text{ pF} \rightarrow \text{charge sensitive amplifier}$

- $\Delta t_{bunch} \simeq 300 \ {

m ns}

ightarrow {

m $T_{peak}$} \simeq 60 \ {

m ns}$

- Two independent modes: physics and calibration (MIP)

- $\rightarrow$  switched gain in preamplifier and shaper

- Physics mode:  $Q_{max} \approx 10 \text{ pC} \rightarrow C_f \approx 10 \text{ pF}$

- Calibration mode: S/N > 10 for MIP requested

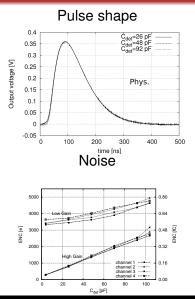

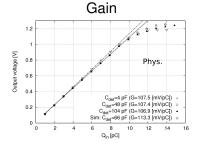

### Front-end measurements

- Prototype 8 channels ASIC produced

- 4 channels with resistive (R<sub>f</sub>) and 4 with MOS feedback in preamplifier

- Both versions fully functional

- Front-end linear up to about 10 pC, works with C<sub>det</sub> up to about 1000 pF

イロト イポト イヨト イヨト

3

| ront-Er<br>⊙●                | าd                     | ADC<br>00000000 | Peripheral circu   | its (DAC, Bandgap, | LVDS)         | Sumn             | hary |  |  |  |  |

|------------------------------|------------------------|-----------------|--------------------|--------------------|---------------|------------------|------|--|--|--|--|

| Front-end parameters summary |                        |                 |                    |                    |               |                  |      |  |  |  |  |

| -                            | Mode                   | Gain<br>[mV/fC] | Noise@50pF<br>[fC] | Linearity<br>[pC]  | Rate<br>[MHz] | Crosstalk<br>[%] |      |  |  |  |  |

| -                            | Physics<br>Calibration | 0.107<br>≈20    | 0.62<br>0.28       | 10<br>0.035        | 3<br>3        | ≈1<br>≈0.1       |      |  |  |  |  |

- Similar results for both R<sub>F</sub> and MOS configurations (MOS slightly better)

- Crosstalk needs to be measured with sensor fanout

- Power consumption per channel is 8.9 mW

- Noise in details:

- Noise<sub>phys</sub>[el] =  $3300 + 13 \cdot C_{in}[pF]$

- Noise<sub>cal</sub>[el] =  $170 + 26 \cdot C_{in}[pF]$

M. Idzik, Sz. Kulis, D. Przyborowski, "Development of front-end electronics for the luminoisty detector at ILC" Nucl. Instr. and Meth. A 608 (2009) pp. 169-174,

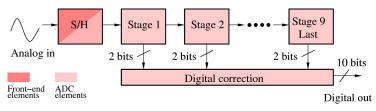

# ADC Requirements and archirecture

- 10 bit resolution

- Sampling frequency 3-30 MHz (depending on number of FE channels per ADC)

- With and without S/H (S/H can be a part of front-end)

- Power efficient, power and clock ON/OFF

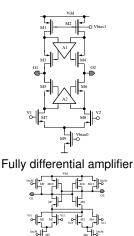

- Fully differential pipeline architecture

< 🗇 🕨

(4) (2) (4) (3) (4)

Peripheral circuits (DAC, Bandgap, LVDS)

Summary

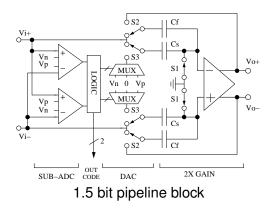

#### **Pipeline ADC - Design**

Dynamic latch comparator

э

э

|          | Cotup |  |

|----------|-------|--|

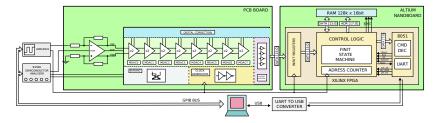

| ADC Test | Setun |  |

- Signal from AWG2021 generator

- External single-ended to differential converter

- FPGA based (Altium nanoboard with Xilinx Spartan2E) DAQ

イロト イポト イヨト イヨト

3

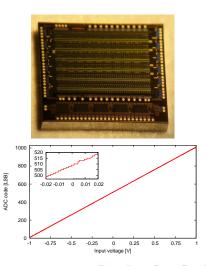

# ADC - prototypes and measurements

- 1<sup>st</sup> prototype: only 8 pipeline stages

- 2<sup>nd</sup> prototype: 9 stages + S/H + digital correction + clock and power switching

- No reference voltages yet applied externally

- Both prototypes fully functional

- Both prototypes work up to about 30 MHz

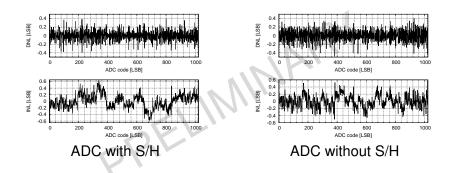

# ADC - Linearity

Both ADC versions show good differential (DNL<0.5 LSB) and integral linearity (INL<1 LSB)

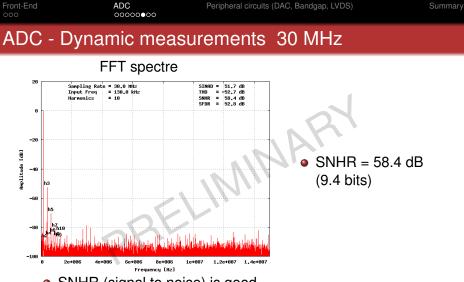

- SNHR (signal to noise) is good

- To measure harmonic distortions the setup needs to be improved (in progress)...

< 🗇 ▶

.⊒...>

Peripheral circuits (DAC, Bandgap, LVDS)

Summary

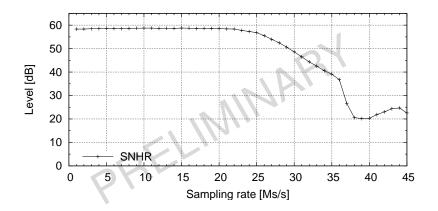

# ADC - Dynamic measurements

- Good SNHR up to about 25 MHz

- The scan versus input signal frequency f<sub>in</sub> also needs to be done...

Peripheral circuits (DAC, Bandgap, LVDS)

Summary

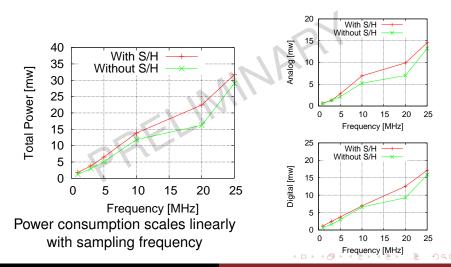

### ADC - Power scaling

M. Idzik for FCAL Collaboration Readout electronics for LumiCal detector

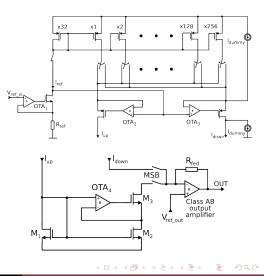

# Design of low power 10 bit general purpose DAC

- Current steering architecture

- High-swing voltage output

- Power cons. < 0.6 mW</p>

- Core area 0.18 mm<sup>2</sup>

#### Peripheral circuits (DAC, Bandgap, LVDS)

# **DAC** measurements

- DAC fully functional

- Power cons. below 0.6 mW

- max INL < 0.42 LSB</p>

- max DNL < 0.42 LSB</p>

- Efective number of bits ENOB=9.85

- Update rate up to few hundred kHz

# Other peripherals

- Bandgap reference voltage and temperature sensor circuit designed, fabricated and just bonded, to be tested...

- Fast (>500 MHz) LVDS transmitter and receiver designed, fabricated and just bonded, to be tested...

・聞き ・ヨキ ・ヨキ

#### Summary - present status

- Front-end ASICs designed, fabricated and matching the specifications

- Front-end 8 channels prototypes ready for tests with sensors, fanout and hopefully for test beam

- New 10-bit piepline ADC prototypes fully functional and preliminary results confirm expectations

- More ADC tests needed (power switching, harmonics, power scaling)

- Very low power 10 bit DAC designed, fabricated and matching the specifications, ready to be used

- Bandgap reference designed and fabricated, to be tested

- Fast LVDS pads designed and fabricated, to be tested

イロト 不同 とくほ とくほ とう

## Summary - future plans

- Proceed with tests (ADC, LVDS, bandgap), in progress...

- Tests of the readout chain comprising of sensor, fanout and front-end, in progress...

- Prepare the setup for test beam (as soon as the readout chain will be tested)

- Design and submission of complete multichannel (>=8) ADC, in progress, submission soon...

#### Digital processing & data concentrator

- Waiting for better detector specification  $\rightarrow$  data flux

- Pure digital design so can be done fast in comparison to front-end and ADC

- Will first be designed and tested with FPGA

- After FPGA tests ASIC implementation should be fast (mounth or two)

・ 同 ト ・ ヨ ト ・ ヨ ト ・

## Test setup (beam) preparation

- Silicon sensors from Hammamatsu ready and preliminary I-V and C-V measurements performed

- First fanout structures designed and fabricated

- Prototype front-end (8 channels) ASICs will be used

- External ADC will be used since the prototype ADC ASIC is not yet multichannel

- PCB board for test setup designed and produced

・ 同 ト ・ ヨ ト ・ ヨ ト