## S-ALTRO

#### integration and system level studies

### Outline

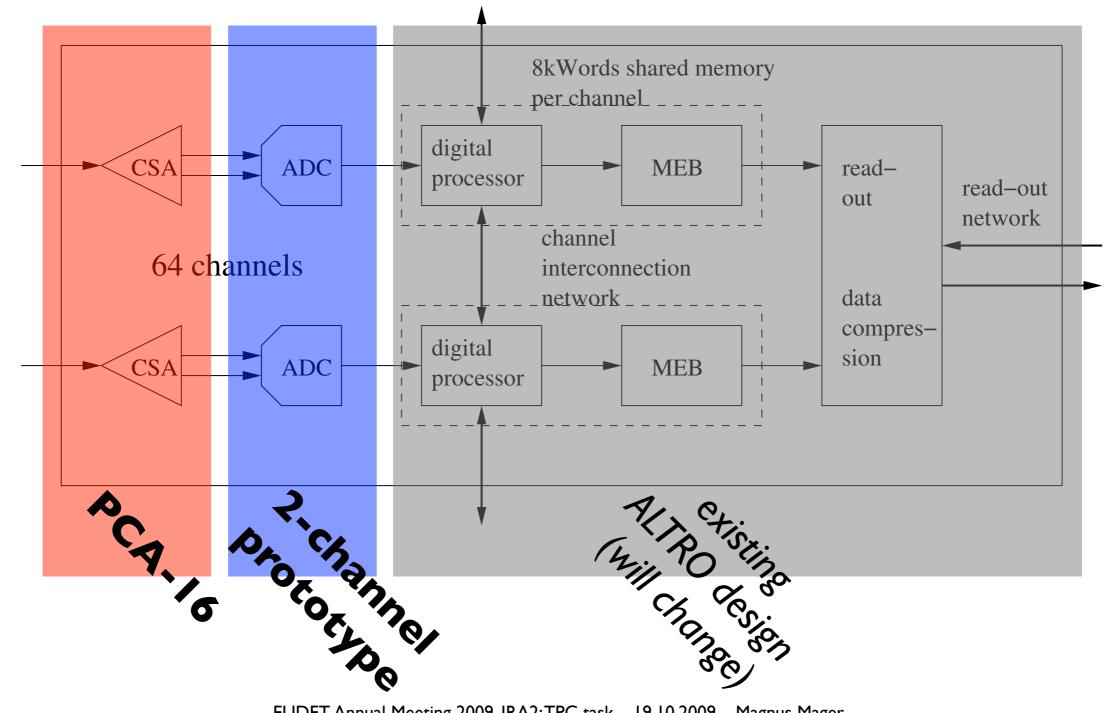

- status of S-ALTRO development short summary (see Paul's talk in "Special session on microelectronics developments within EUDET (NA2)" for details)

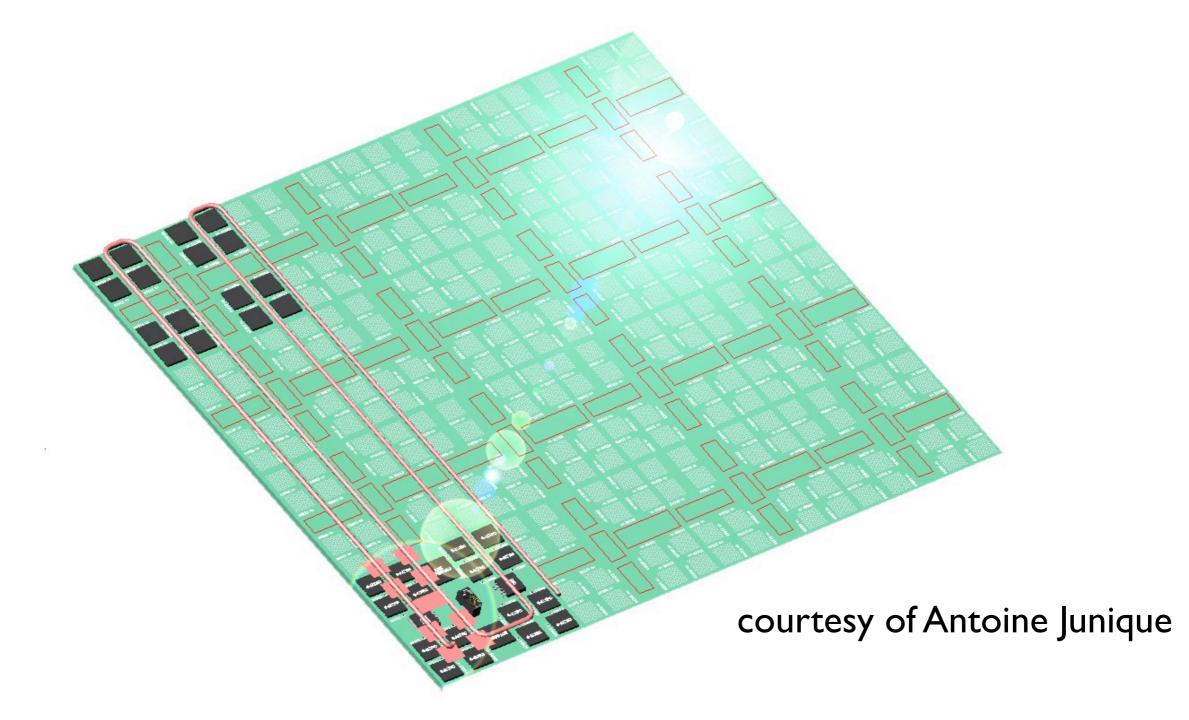

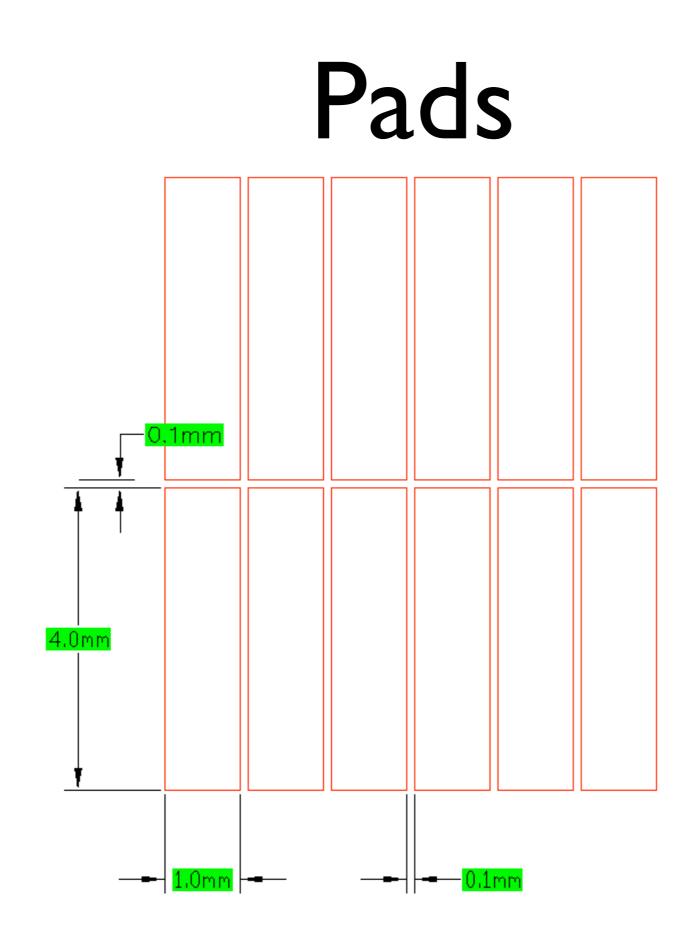

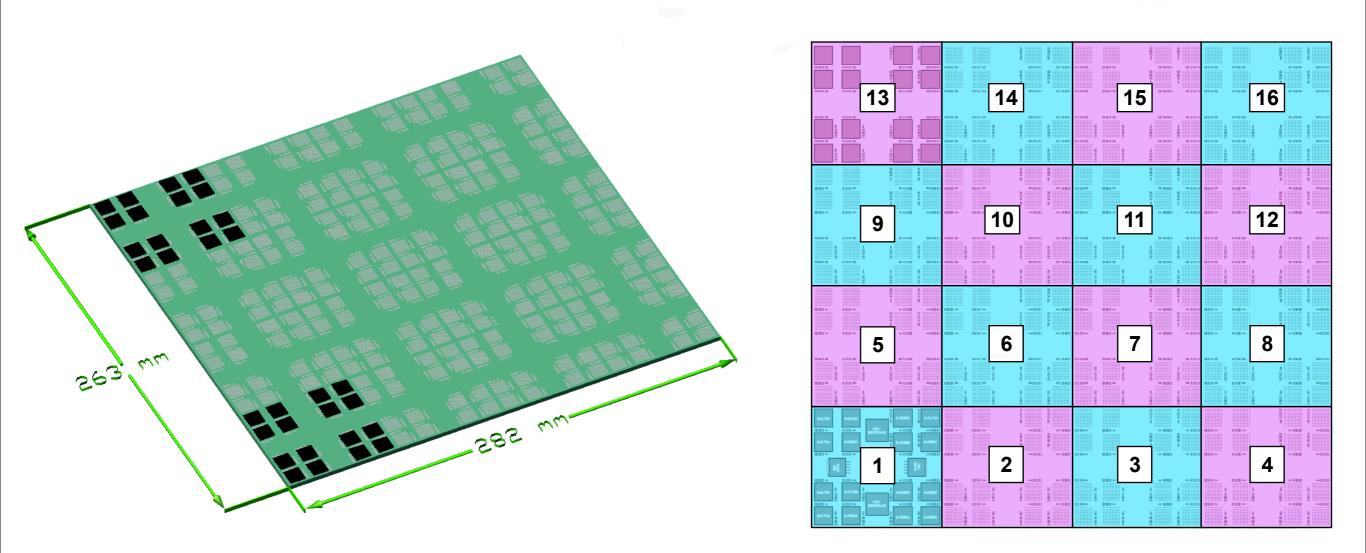

- Read-out backplane studies

- Plans/Outlook

# S-ALTRO design – current status

## PCA-16

- CMOS I 30 nm

- 0.2 mm<sup>2</sup>/channel

- < 8 mW/channel</p>

- <ImW in standby

- works according specifications

- is already in use (e.g. at DESY)

channel

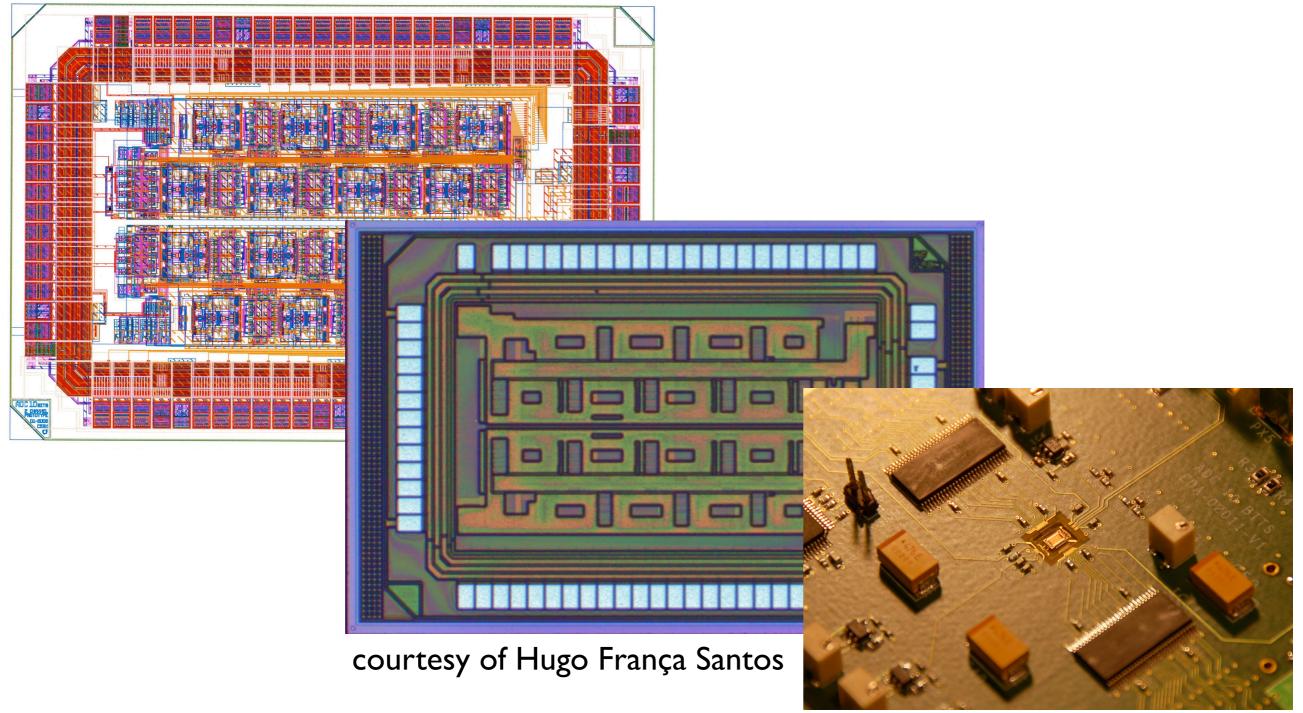

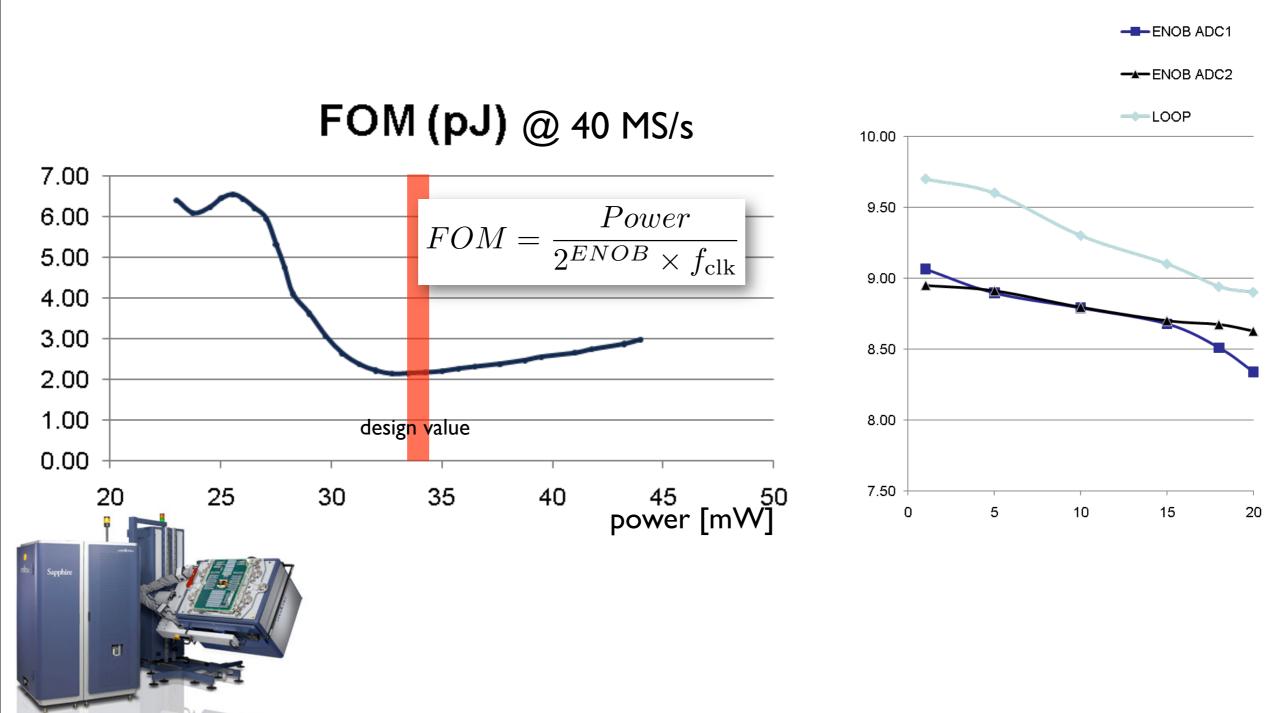

## ADC prototype

Single ADC area: 1.57 X 0.45 = 0.7 mm<sup>2</sup>

Prototype area: 2.35 X 1.6 = 3.76 mm<sup>2</sup>

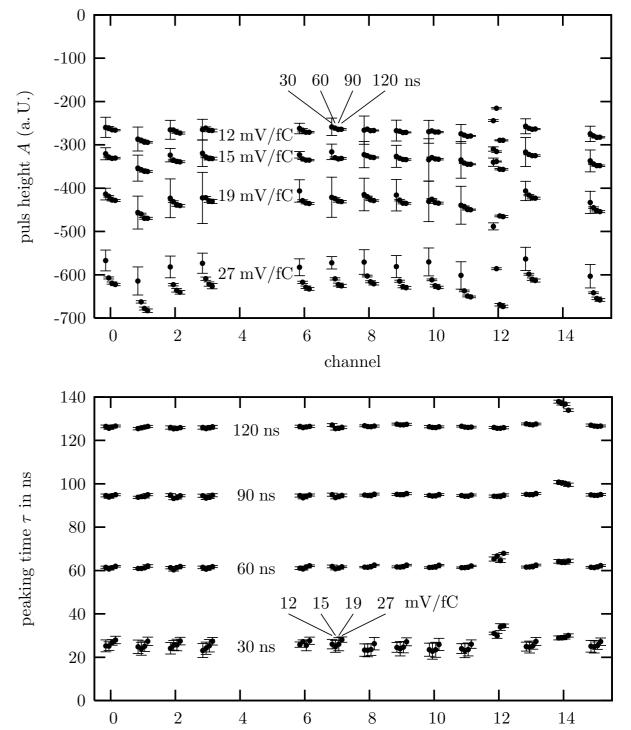

## ADC prototype – test

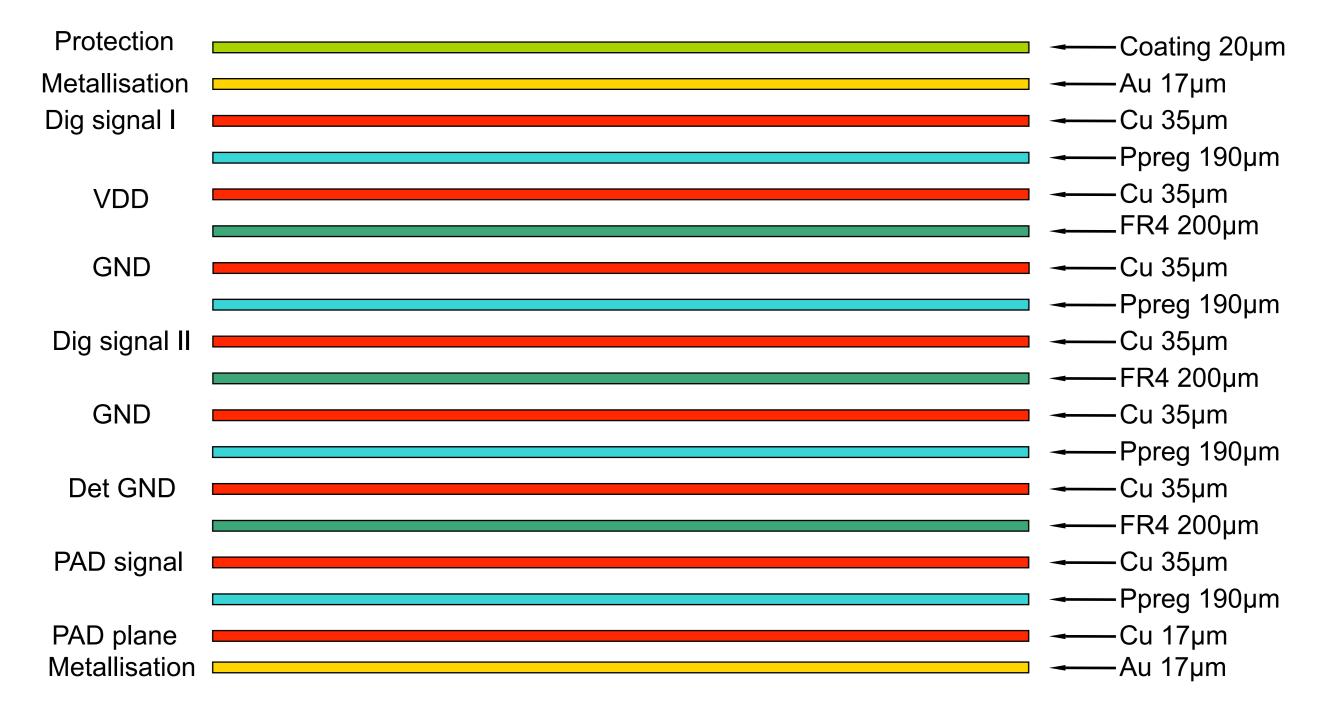

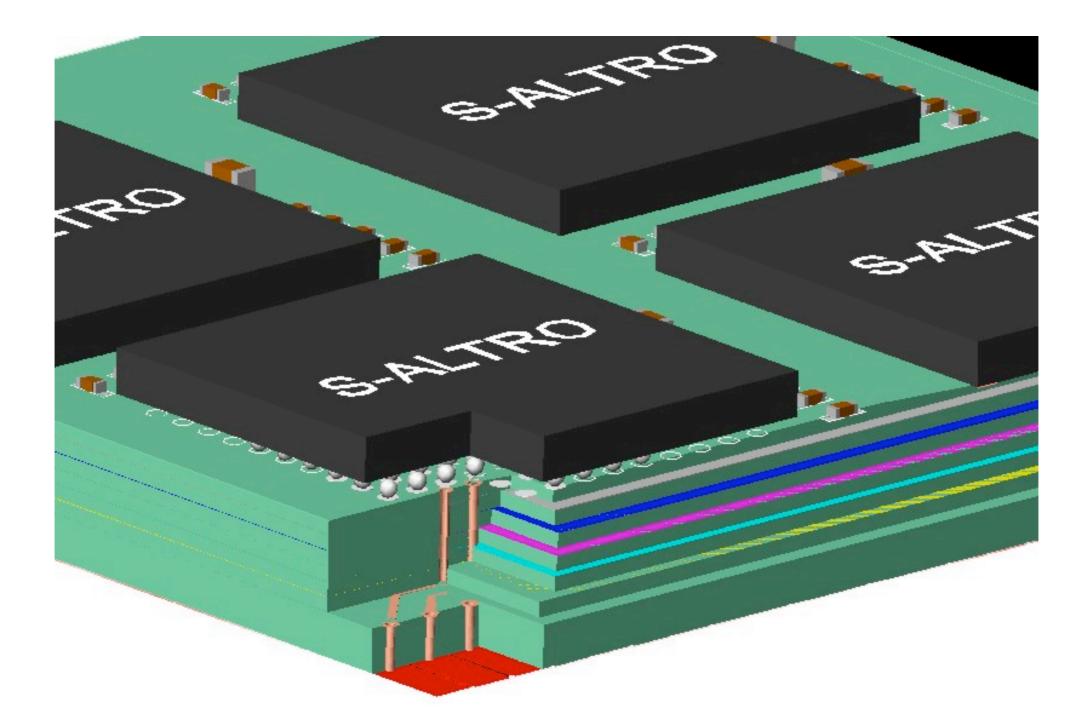

## Layer stack-up

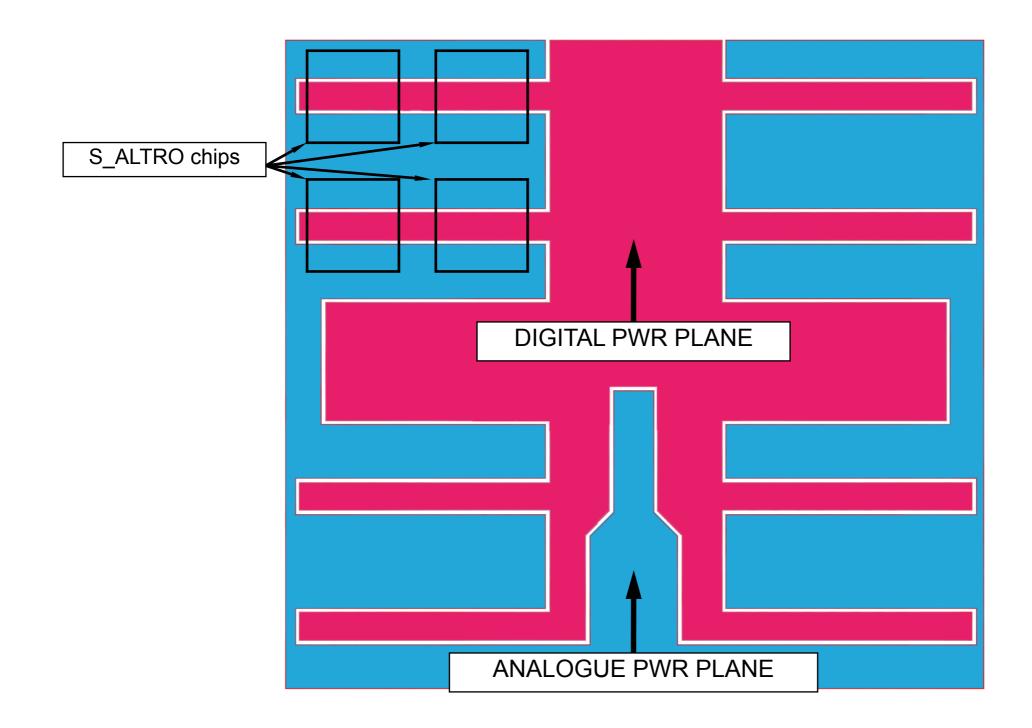

### Power distribution

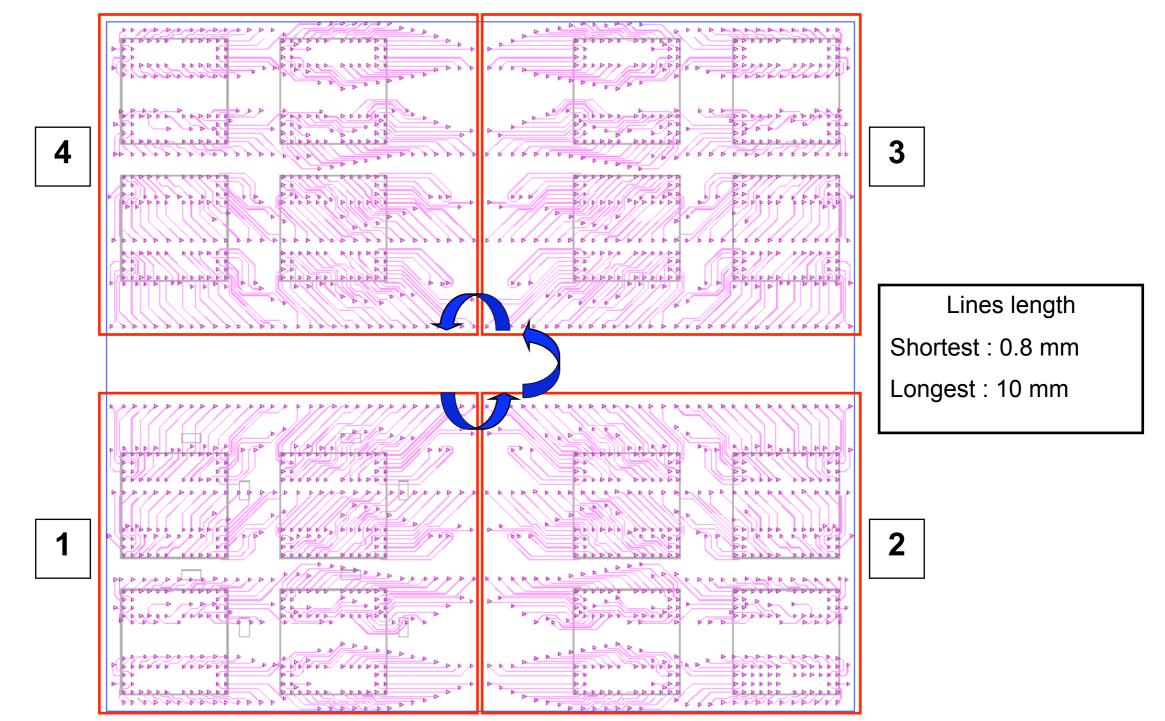

# Signal routing

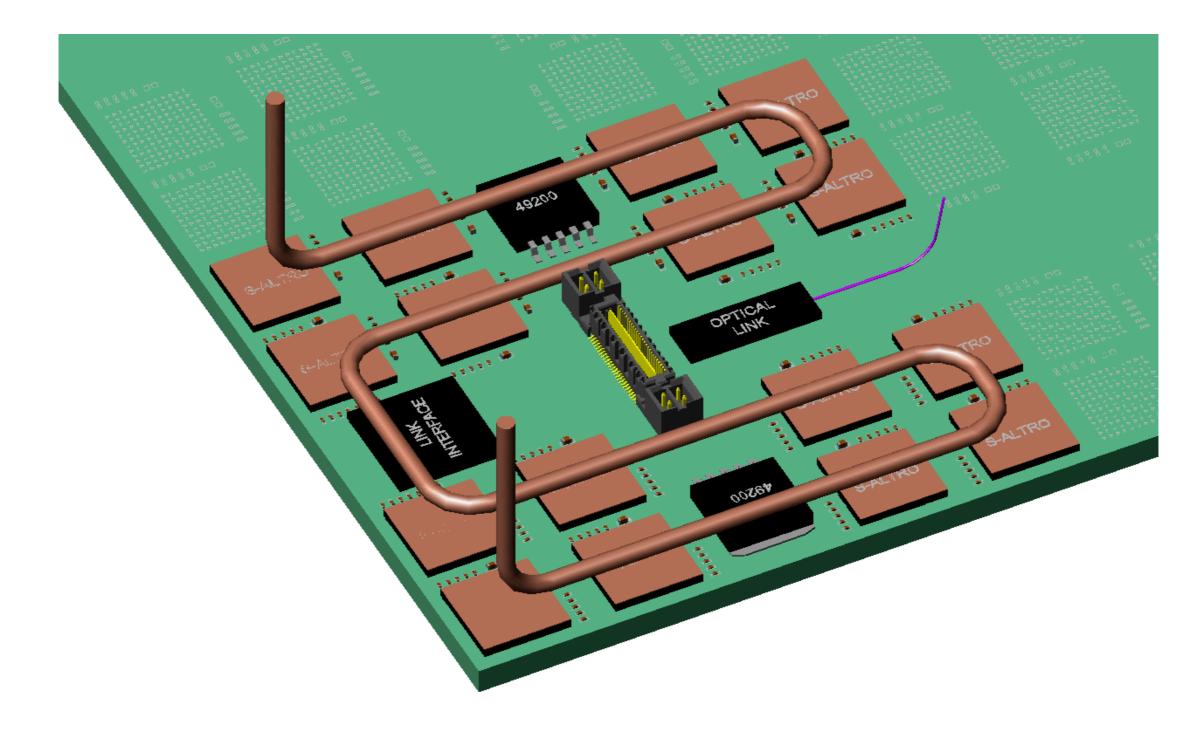

# Close-up view

## Close-up view II

## Plans

- Adopt design to real geometry, in particular:

- non-quadratic shape of chamber

- mounting margins

- Understand heat production and cooling

- 40mW/ch

- Power pulsing

- FPGA prototype by Japanese group