# FRONT-END READOUT & DAQ for SI TRACKERS at LINEAR COLLIDER

Aurore Savoy-Navarro, Université Pierre et Marie Curie/CNRS-IN2P3, France

A. Charpy <sup>1)</sup>

A. Commerma <sup>2)</sup>

J. David <sup>1)</sup>

A. Dieguez <sup>2)</sup>

D. Dzahini <sup>3)</sup>

A. Lhazar <sup>1)</sup>

T.H. Pham <sup>1,4)</sup>

A. Savoy-Navarro <sup>1)</sup>

R. Sefri <sup>1)</sup>

L. Vaubien <sup>1)</sup>

1) LPNHE-Paris

2) Barcelone U.

3) LPSC Grenoble

4) Now at IPHC

### International Linear Collider Workshop 2010

Friendship Hotel, Beijing, China, 26-30 March 2010

# **R&D on Front End Electronics**

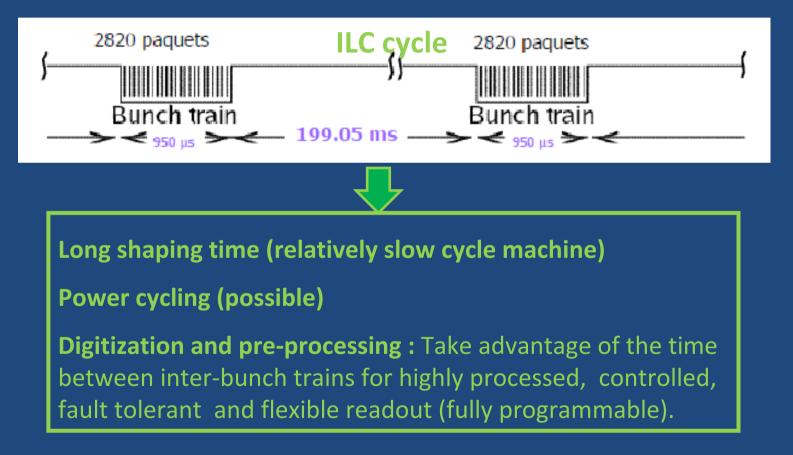

The FEE is closely related to the fact 1) that microstrips are currently the baseline for LC sensors and 2) to the cycle of the ILC machine.

# PURSUING OUR R&D LINE ON THE ELECTRONICS

# FEE basic piece:

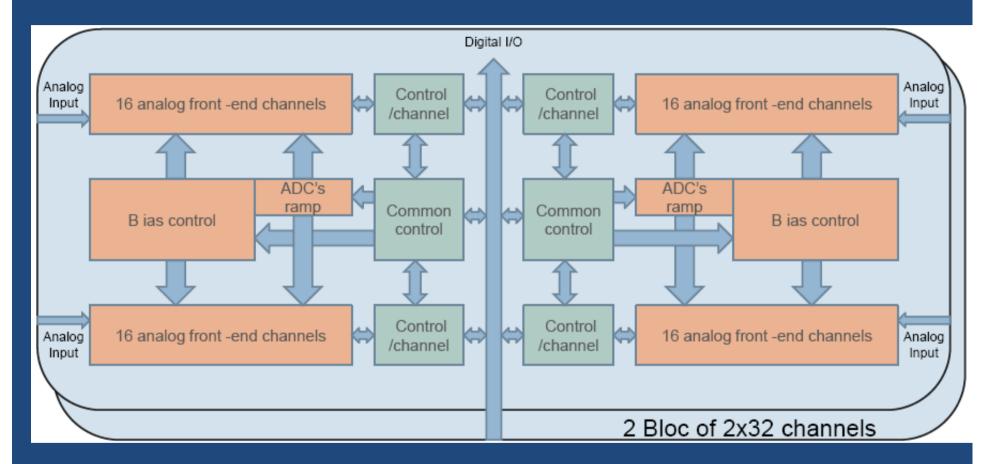

- Goal: Integrate 2048 channels in 90nm (65nm?) CMOS: but by elementary blocks of 256 channels: multiplexing factor 256:1)

- Amplifiers : 20 mV/MIP over 10 MIP range

- Shapers :  $500ns-2\mu s$  (now optimizing at 500 ns)

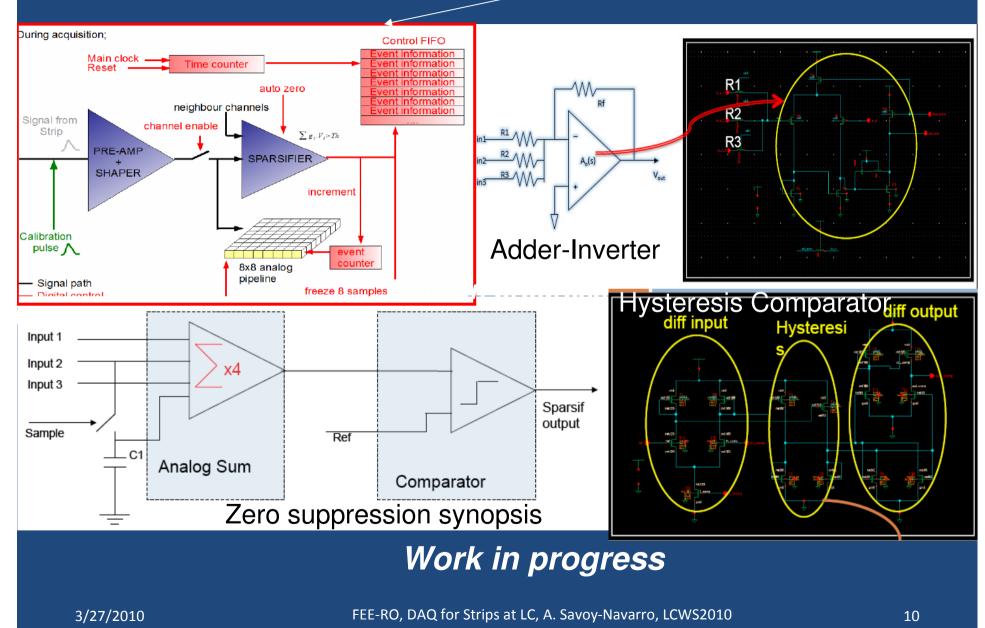

- Sparsifier : Threshold the sum of 3-5 adjacent channels

- Samplers : 8 samples at sampling clock period (80ns)

Event buffer 8 depth

- Noise baseline : O  $(375 + 10.5 \text{ e-/pF} @ 1 \ \mu \text{s} \text{ shaping}, 200 \ \mu \text{W} \text{ power})$

- ADC : 8 bit-ADC

- Power dissipation/channel for the overall FE chain: 1-1.5 mWatt

- Buffering, digital pre-processing

- Calibration

- Power switching (could save a factor of about 70)

- Total number of readout channels: 10<sup>7</sup> channels

### Main features of the new circuit (new= currently under design)

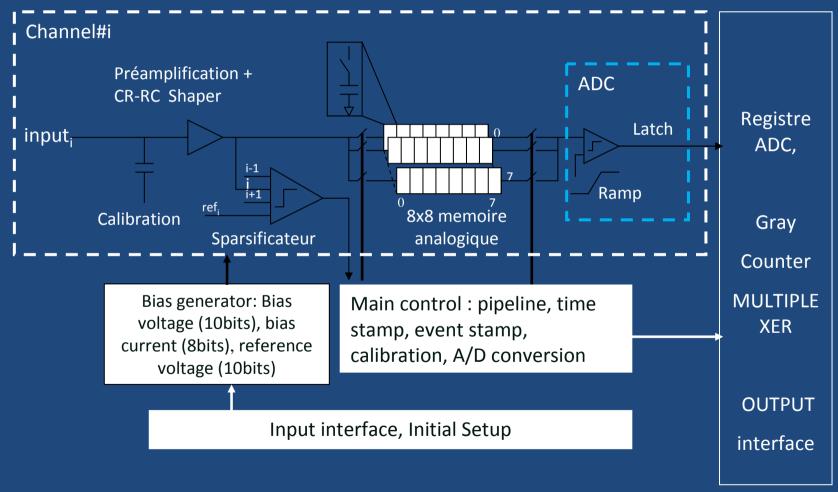

128 channels: Preamplifier, shaper, sparsifier, analogue pipeline (8x8 cells), 8-bit ADC, plus structure de tests/block

2D memory structure: 8x8/channels

Fully digital control:

- Bias voltage(10-bit) and current (8-bit)

- Power cycling (in optional)

- Shaping time programmable

- Sampling frequency programmable

- Internal calibration

- Sparsifier threshold programmable per channel

- Event tag and time tag generation

2 Trigger modes: Internal (integrated sparsification) External (LVTTL) for beam test

Developing a mix-mode FE readout with pulse-height reconstruction, zero suppression, full digital control (highly fault tolerant, flexible/robust) power cycling, in DSM CMOS technology

## **BUT: Major changes**

- Now 130nm IBM technology (previously UMC-130)

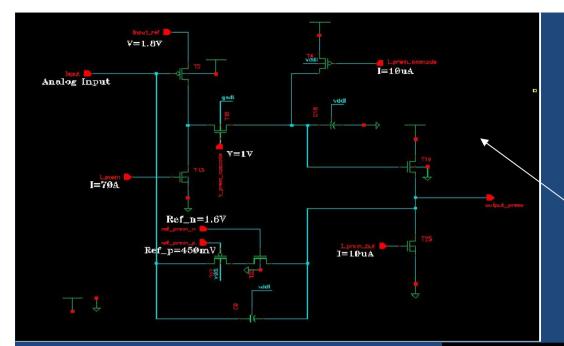

- Total revisit and optimization of the analogue main blocks (preampli+shaper; sparsifier+2D pipeline; ADC; DACs & controls)

- Revisit the targeted values of the main parameters to more modest values as the technology is much more sensitive.

- Modeling (VERILOGA) of the analogue part that follows the new design of each blocks in order to prepare the digital part while the analogue part is still in progress.

- Develop a mix mode simulation

- Define a modular architecture of the 128 channel chip by blocks of 32 (corresponding to the elementary multiplexing:1 ADC /32 channels)

Goals: Submit each of the major blocks by mid May 2010 and, while they are in foundry, proceed to the full 128 channel chip design.

### NEW SITR\_IBM130-128

### New modular architecture

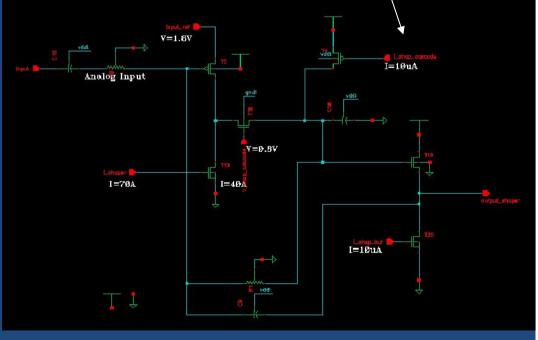

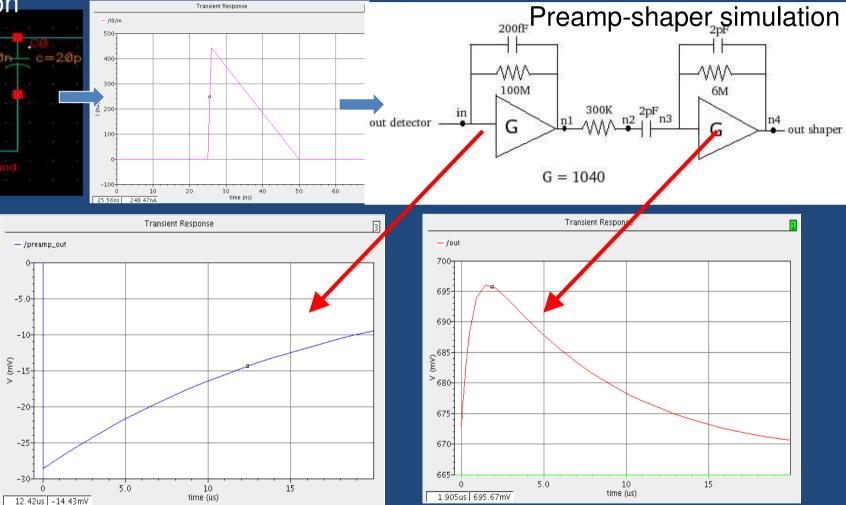

FEE-chip: the basic blocks preamplifier shaper block

Crucial piece!! Modified parameters: ✓Preamp: 20 mV/MIP over 10 MIP ✓Shaper: Peaking time at 0.5 μs *Work in progress*

# FEE-chip: sparsifier+pipeline block

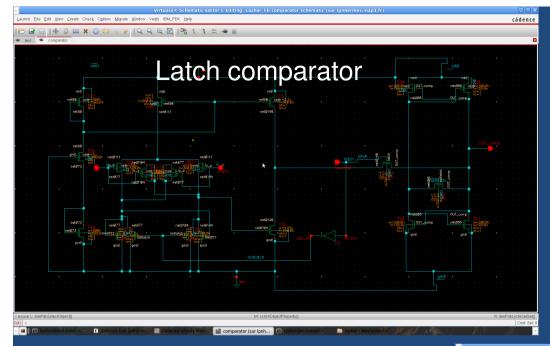

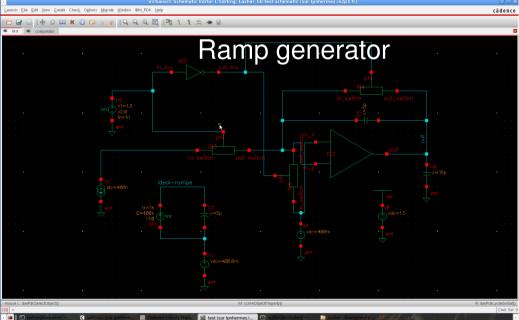

### FEE – ADC block

Two important elements of The Wilkinson ADC: The Comparator and Ramp Generator. Now: 8bit-ADC

### Work in progress: Block submitted to foundry May 2010

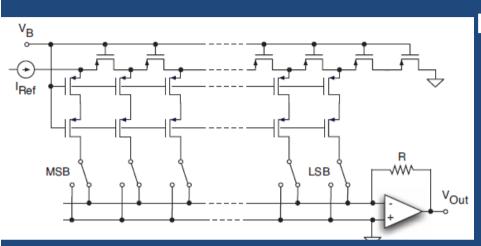

### **FEE-chip: DACs for voltage & current control** *Courtesy D. Dzahini et al. (LPSC)*

Low area implementation for R2RDAC

Based on the expertise of the LPSC Team we will explore several DAC Designs for the later version of the Chip (SiTR\_128)

C2C versus Segmented Mode DAC: speed; dynamic range; high value for Cu

Presently: block with the previous DAC version translated in IBM-130 for May

FEE-RO, DAQ for Strips at LC, A. Savoy-Navarro, LCWS2010

# MODELING the FEE-RO chip Verilog-A modeling:

- Model analog channel

- Develop in parallel analog and digital

- Test and validate digital code concepts

- Verify interactions between the two sides

- Setup mixed signal environment while analog is not

- available

- Faster simulations => faster debugging loops

MODELING the FEE-RO chip

Verilog-A modeling :

Work process

- Code all non-generic components

- Use Cadence Model Writer

- Compile source codes to Virtuoso

- Generate symbols

- Draw schematics with models instances

- Simulate to validate model

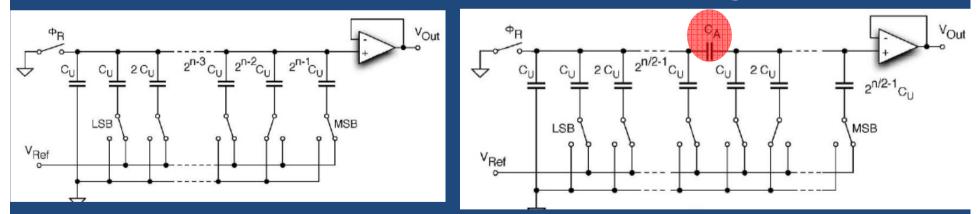

# Verilog-A modeling : Detector signal Example of Validation tests

Full chain simulated including multichannel simulation: now refining modeling

3/27/2010

FEE-RO, DAQ for Strips at LC, A. Savoy-Navarro, LCWS2010

### DAQ issues

- Processing of the data on detector at the various stages

- Synchronization

- Linking to the global DAQ

- Cabling

Work in progress, indeed mostly just starting...

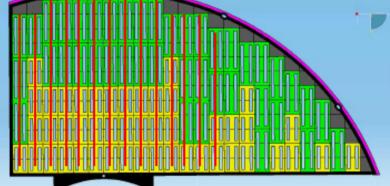

### DAQ step 1: data processing on the module

Some challenging aspects/consequences of the elementary module microcosm:

✓ High processing level on chip: taking advantage of the machine cycle & the potential DSM CMOS tech., the chip includes a fair amount of data processing.

✓ The readout pitch vs sensor size & channel number/module

An elementary module in the designed architecture of the detector, will include a relatively large number of channels (Order 2000) because of the small readout pitch (50 µm) and of the large size of the sensor (10x10cm<sup>2</sup>).

For a basic multiplexing 256/1 at the ADC level, this means 8 FEE chips.

✓ Connection of the chips onto the sensor:

How to output the data is strongly related to the way the chips are connected on the sensor. Also various ways to gather them are under study (superchip or?)

Choose to work as much as possible in parallel mode (vs daisy chaining)

Concentrate the data output at the module level => 1<sup>st</sup> concentration step: Buffering plus some data output processing plus data synchronization

3/27/2010

### DAQ step 1: very preliminary schematics

### Explored solutions at the module level

8 SiTR\_256 on kapton TAB linked to a buffer 1<sup>st</sup> concentrator level/unit

8 SiTR\_256 Gathered on a Superchip Including the 1<sup>st</sup> concentrator unit

- Data are sent from each chip to the concentrator unit on module

- Synchronization via the bunch trains:

- bunch adressing is performed at chip level by the internal chip clock

- module & train synchronization from global DAQ via the concentrator unit

FEE-RO, DAQ for Strips at LC, A. Savoy-Navarro, LCWS2010

3/27/2010

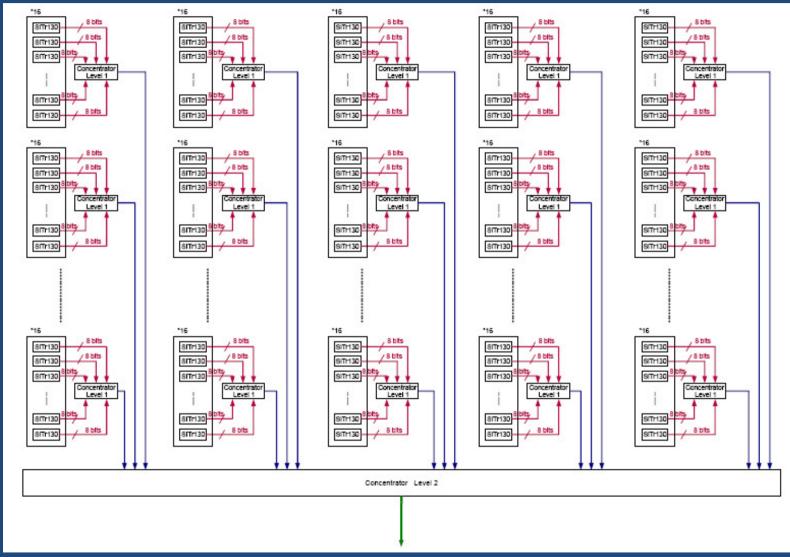

# DAQ step 2: gathering in parallel mode several modules into supermodules

### FEE-RO, DAQ for Strips at LC, A. Savoy-Navarro, LCWS2010

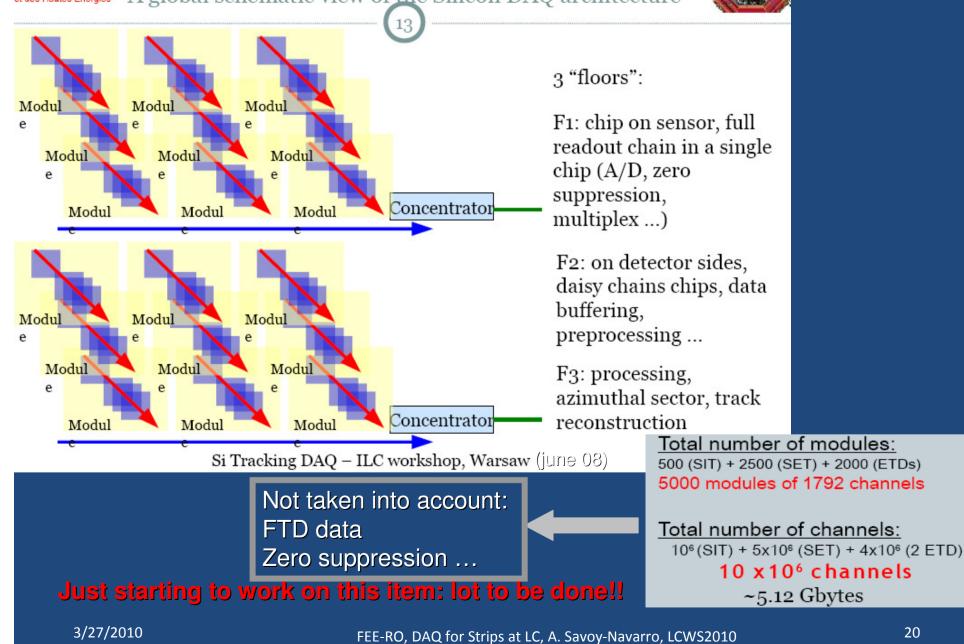

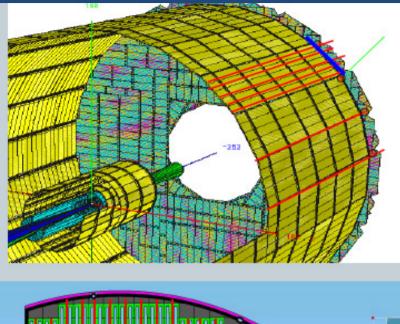

#### LPNHE Laboratoire de Physique Nucléaire et des Hautes Energies DAQ Silicon tracking architecture A global schematic view of the Silicon DAQ architecture

### **Reading out the DAQ sub-elements**

• On the "module": Chaining of <u>8 SiTR\_130-256</u>

• "Super Module": Chaining the adjacent ladders toward a level 1 concentrator

• Half cylinder ("Detector Element"): Level 1 concentrator (toward level 2 ?)

• Toward the global Silicon DAQ system by Optical fibers

• Send to Global DAQ system

Depending on the final requirements

Just starting to think about the topology design & how to build the DAQ chain: *Just getting our nose out of the FEE chip....*LOT to DO: setting of a task force

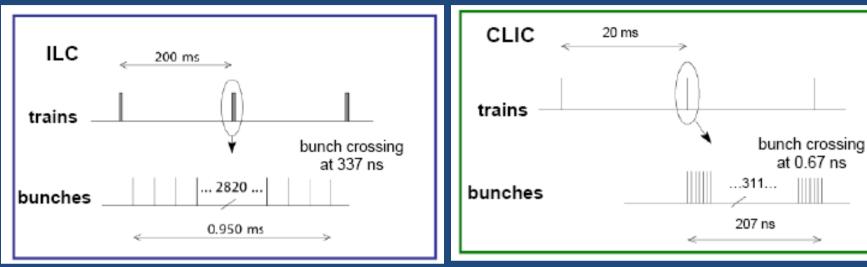

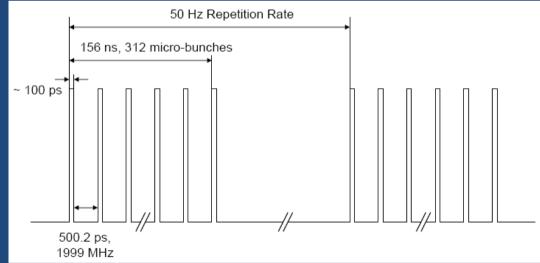

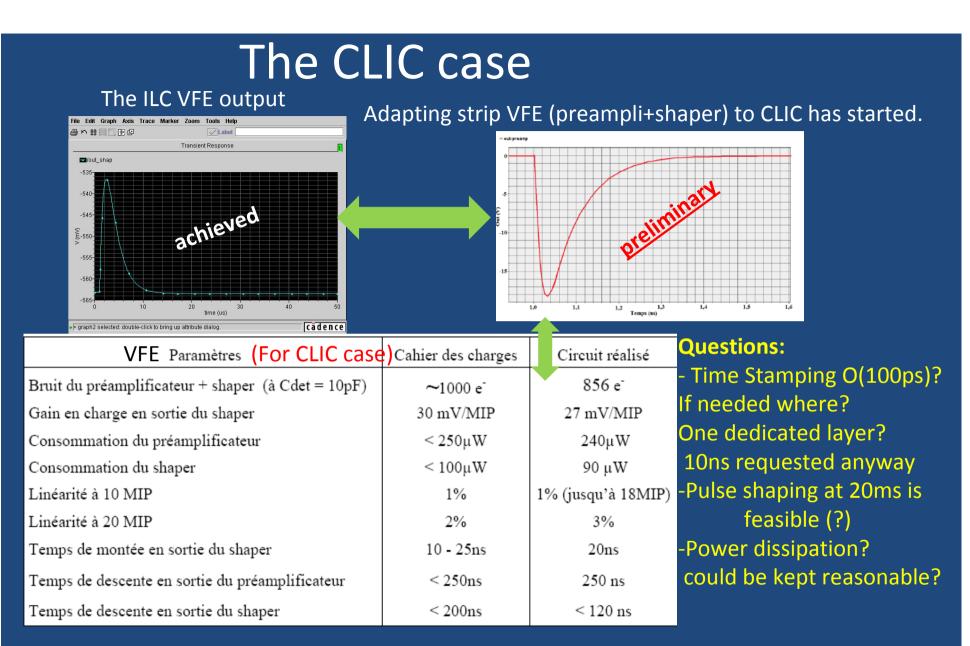

### Machine cycle: CLIC vs ILC

CLIC & ILC: different e+ e- machines (technology, Ecm range)

- $\Rightarrow$ Thus their cycles are different

- ⇒ so the environmental conditions imposed to the detectors & their associated electronics

- ⇒So also the Physics (going to higher Energy)

We also have some idea based on our LHC previous experience how to achieve a fast pulse reconstruction and get a time stamping with O(25ns) resolution.

3/27/2010

FEE-RO, DAQ for Strips at LC, A. Savoy-Navarro, LCWS2010

# **ELECTRONICS ROADMAP**

- ➢ Go to 256 channels

- ➢ Go to deeper DSM when mature (90 or 65 nm)

- > Thinning (50 μm)

- Direct connection chip onto sensor

- > Design/strategy of the DAQ architecture on detector:

- => synchronization

- => data processing, compacting & buffering

- => cabling

- Linking with general DAQ

- Adapting FE to CLIC cycle

- Bunch tagging at CLIC

- Pursue developing TOT alternative

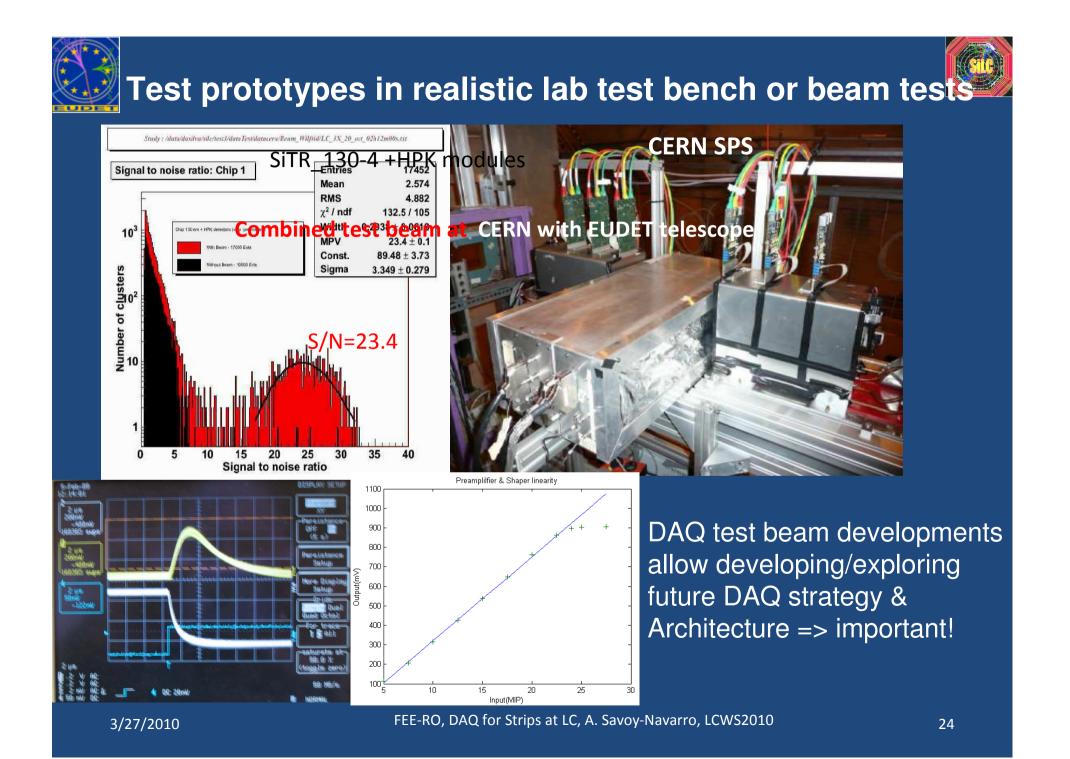

As for all the Silicon Tracking R&D topics: have a short term baseline and Keep on developing longer term, beyond the baseline solutions. Each step in the development is submitted to the evaluation in realistic test beam conditions: important!