## **AHCAL Electronics**

#### **Status Commissioning**

Mathias Reinecke for the AHCAL developers

HCAL main meeting Hamburg, Dec. 10th, 2009

#### **Outline**

- System Commissioning

- Labview DAQ operation

- First Results

- Testbeam Preparation

- The Next Generation

- Conclusions and Outlook

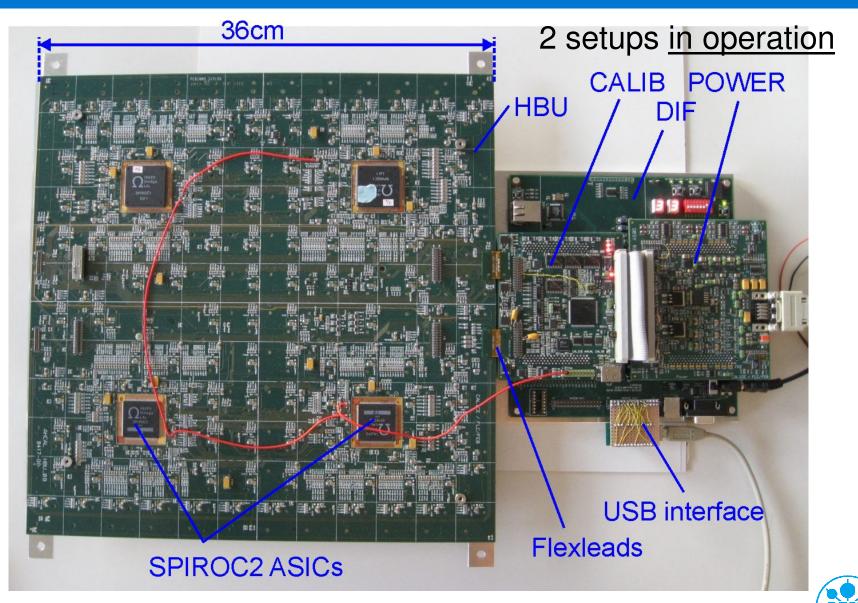

### HCAL Base Unit (HBU) and system setup

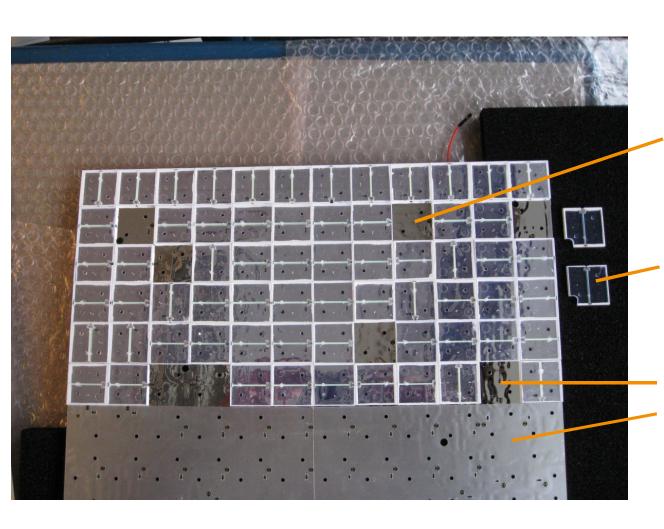

## Tile Assembly – HBUII SPIROC2 area

Some positions cannot be assembled (tiles do not fit in)

"mechanics tiles" (cassette construction)

Reflector foil: without cover (blank) still with cover

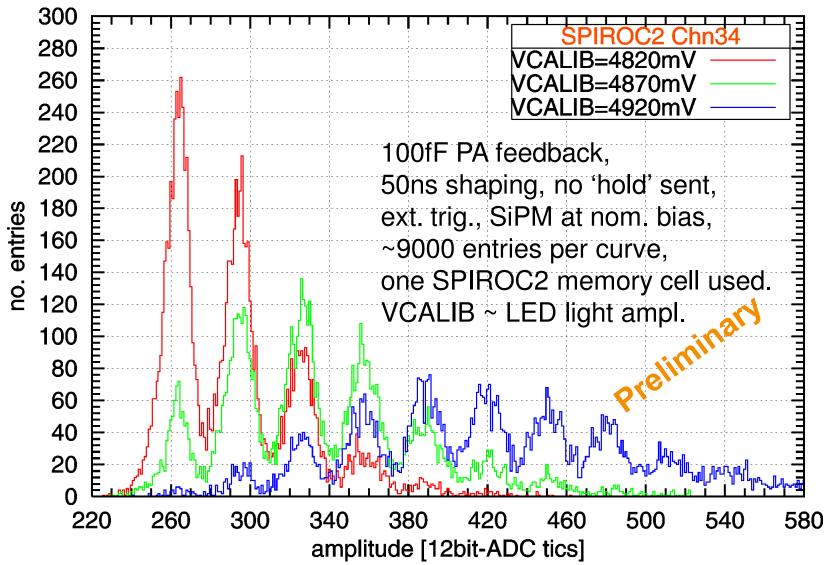

### Single-Photon Peaks I

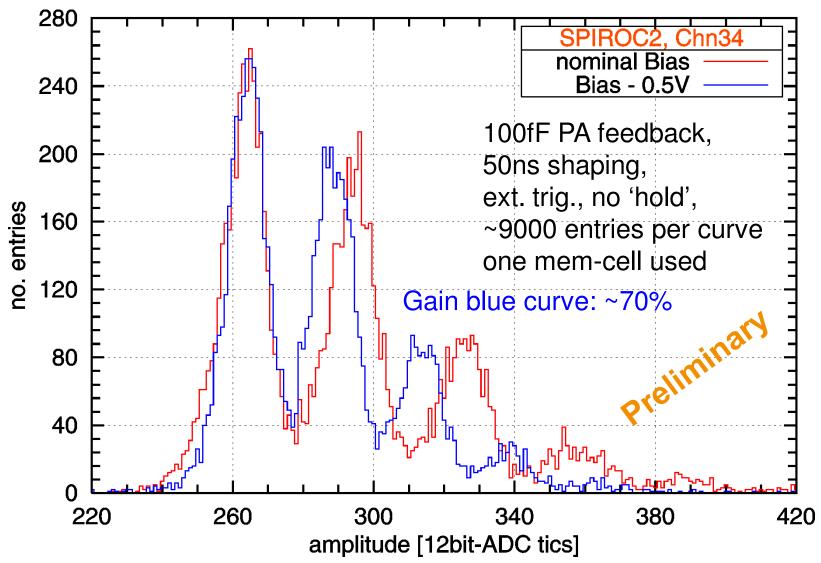

### Single-Photon Peaks II (reduced SiPM bias)

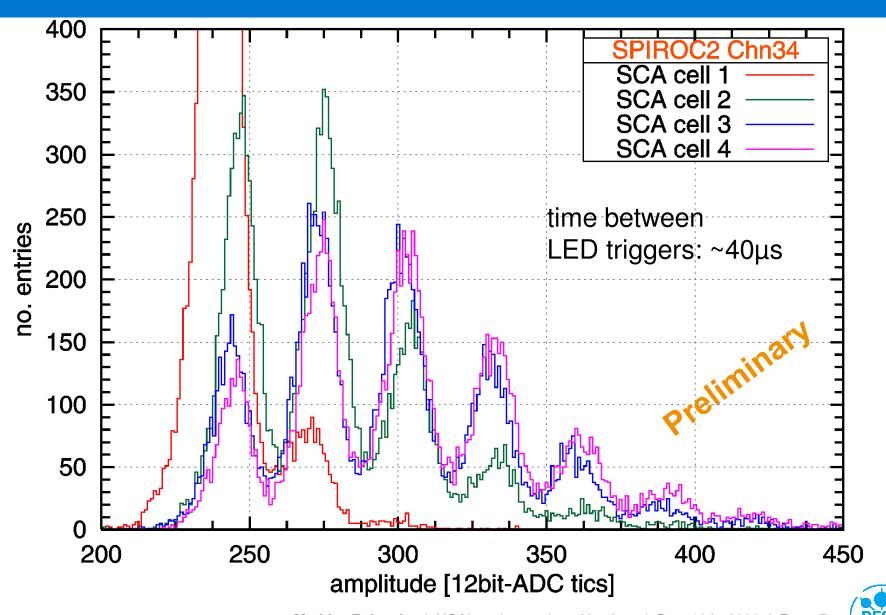

### Single-Photon Peaks III (SPIROC2 SCA test)

## Single-Photon Peaks III (SPIROC2 SCA test)

- Different light amplitudes due to integrated LED system, but reason unknown (no level shifts of GND or VCALIB observed).

- Offset may be due to SCA cells, or due to GND level shifts.

- Without correction, sum of SCA cell results (black curve) should not be used.

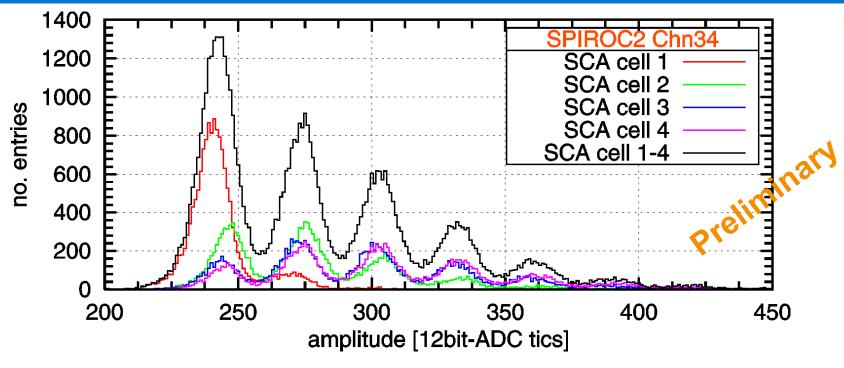

### integrated LED system – dynamic range

# SPIROC2: 400fF PA feedback, 50ns shaping, results for 18 assembled channels shown

- LED comp-to-comp spread is large => preselection necessary.

- Dynamic range: Change LED capacitor? VCALIB max = 10V.

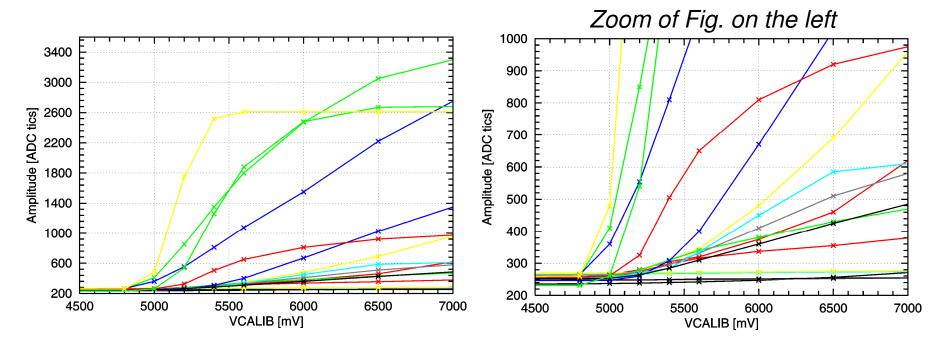

### Testbench Labviews - Histogram Building

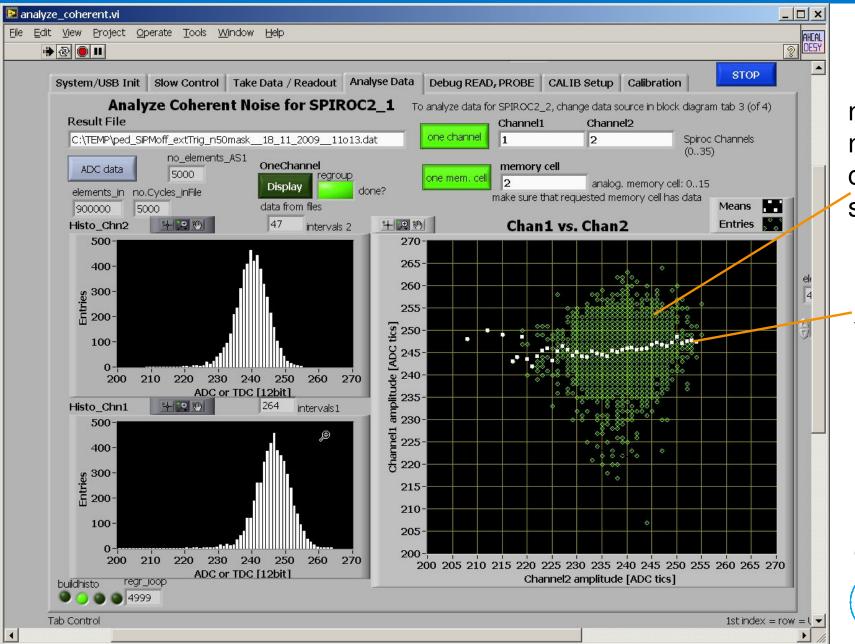

### **Testbench Labviews – Coherent Noise Analysis**

no coh. noise: circular shape

mean values (white points)

now: rip off block capacit.

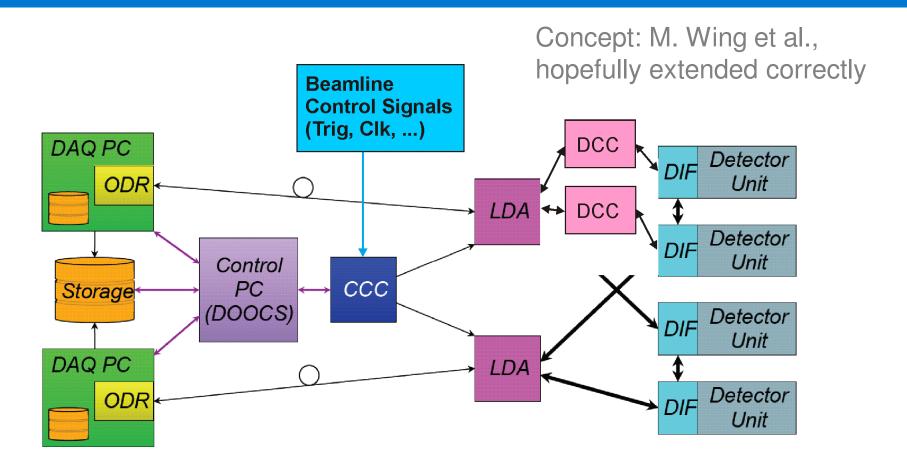

## **Testbeam Synchronization (CALICE DAQ setup)**

- All timing critical signals are distributed from central DAQ (via CCC).

- All detector units (+DIFs) run synchronously.

#### **Testbeam Data Taking: Internal Trigger**

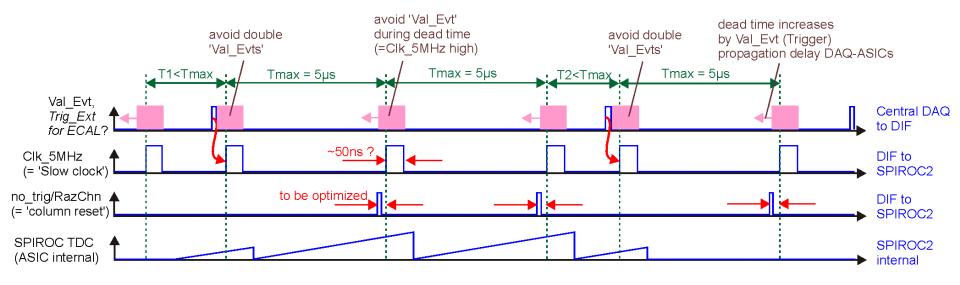

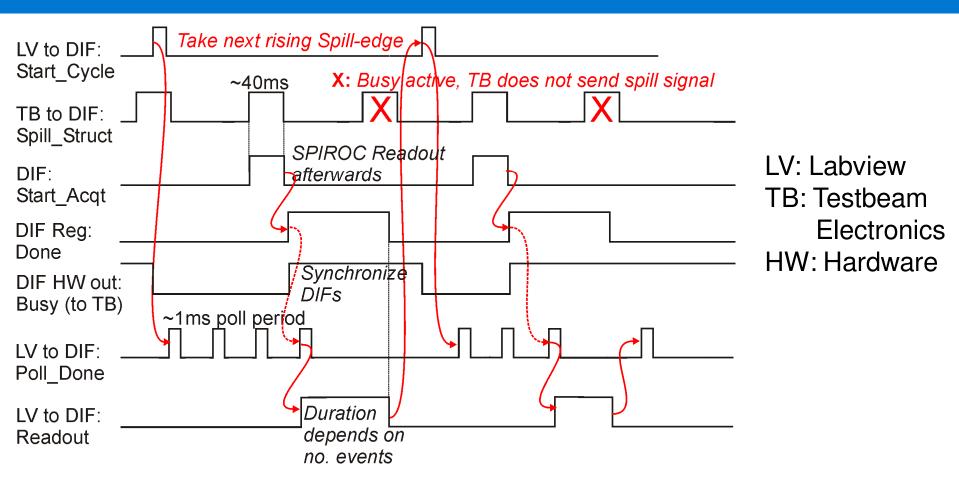

#### AHCAL timing scheme for common CALICE testbeam

- Internal Trigger with "Validate\_Event". Pink boxes: deadtime!

- Do we need "Internal trigger mode" without Val\_Evt in TB (full clock rate)?

- CALICE DAQ: Synchronize Val\_Evt on global clock (multi-DIF synchron.).

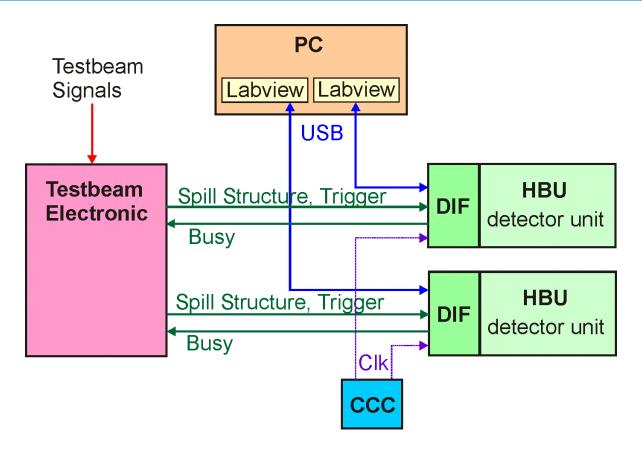

## **DESY Testbeam Synchronization (Labview setup)**

- Synchronization done by temporary hardware signals to/from DIF.

- > First: Only one DIF/HBU used. With two HBUs the CCC is needed.

- Readout Speed limited due to USB/Serial Interface.

### **DESY Testbeam Synchronization (Labview setup)**

- Due to shutdown of DESYII: HBU testbeam tests end of Feb 2010.

- External and Internal trigger will be tested.

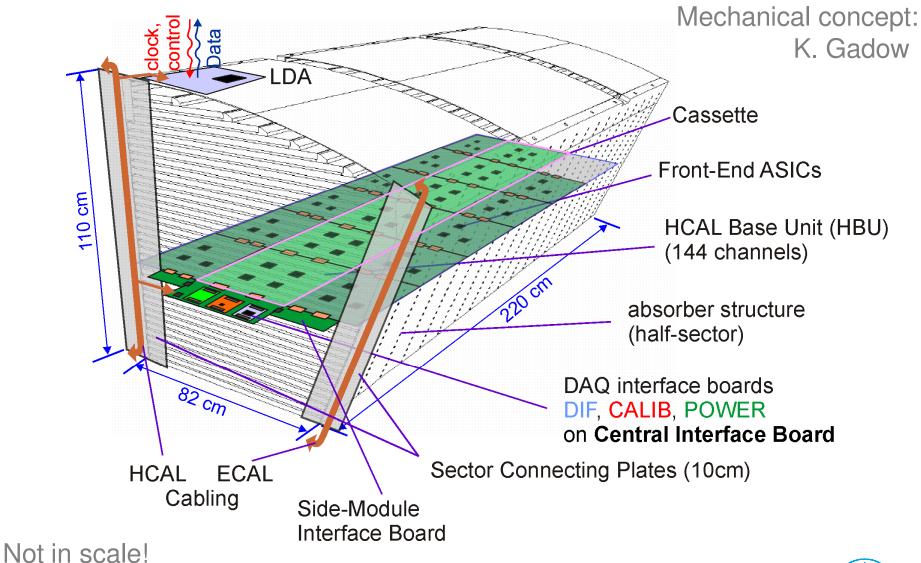

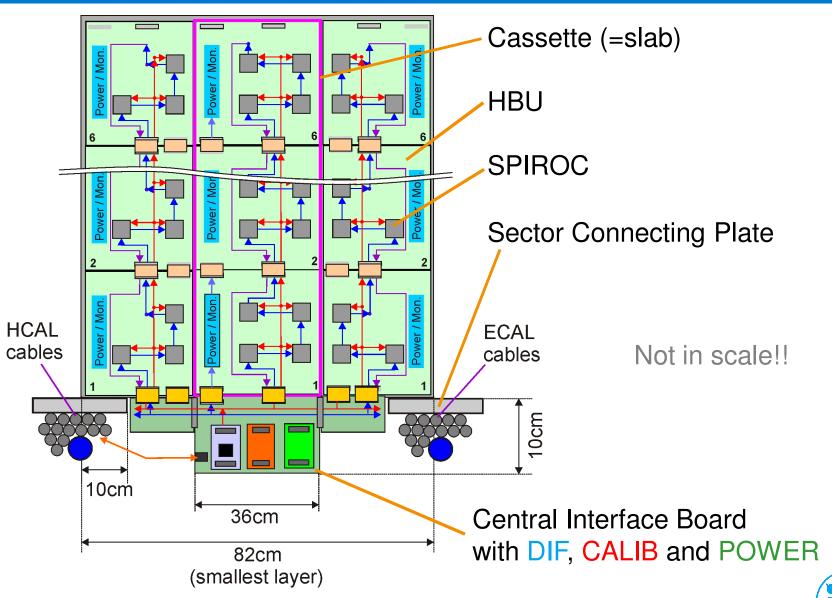

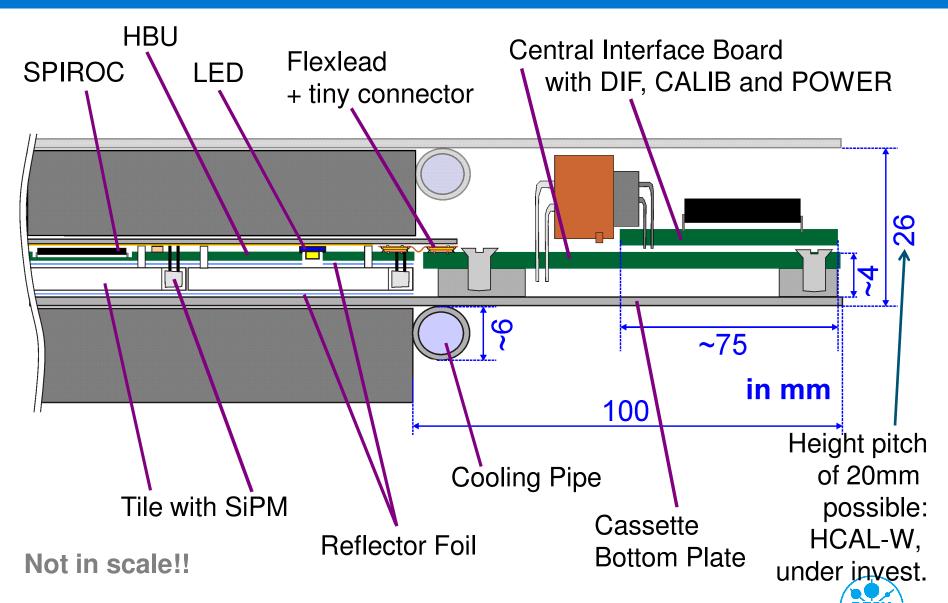

## The Next Generation ('final' ILC setup concept)

#### **The Next Generation**

#### **The Next Generation**

#### **Conclusions and Outlook**

- > AHCAL prototype in full operation! 2 setups realized!

- CALICE DAQ (hardware, DIF firmware) still has to be implemented.

- we expect a first system Feb/March 2010. Till then: Labview operation.

- SPIROC2a submission Jan2010. Changes under discussion.

- DESY electron-testbeam preparation ongoing.

- Redesigns of AHCAL modules are prepared now.

- Fibre based calibration system in operation as well! (see Ivo's talk)

- A lot of system's and SPIROC analogue and digital tests ahead.

- all shown analysis have not been completed.

- status only demonstrates readiness of the system and system's tools.