# **ILD Silicon Tracking system**

A. Savoy-Navarro, Université Pierre et Marie Curie/CNRS-IN2P3

#### Based on the ongoing R&D work by the SiLC Collaboration. Also to be included as contributions to this Workshop:

Contribution on behalf of SiLC to the Simu pre-Meeting (W.Mitaroff)

IV<sup>th</sup> ILD Worshop, January 29, 2010 Les Cordeliers, Université Pierre et Marie Ourie, Paris

## Main topics on the 2012 roadmap for the ILD Si tracking system

- Sensors

- FE Bectronics

→ new basic module

- FEE/ sensor direct connection

- Associated DAQ chain -> global DAQ system

- Mechanics & Detector Integration issues

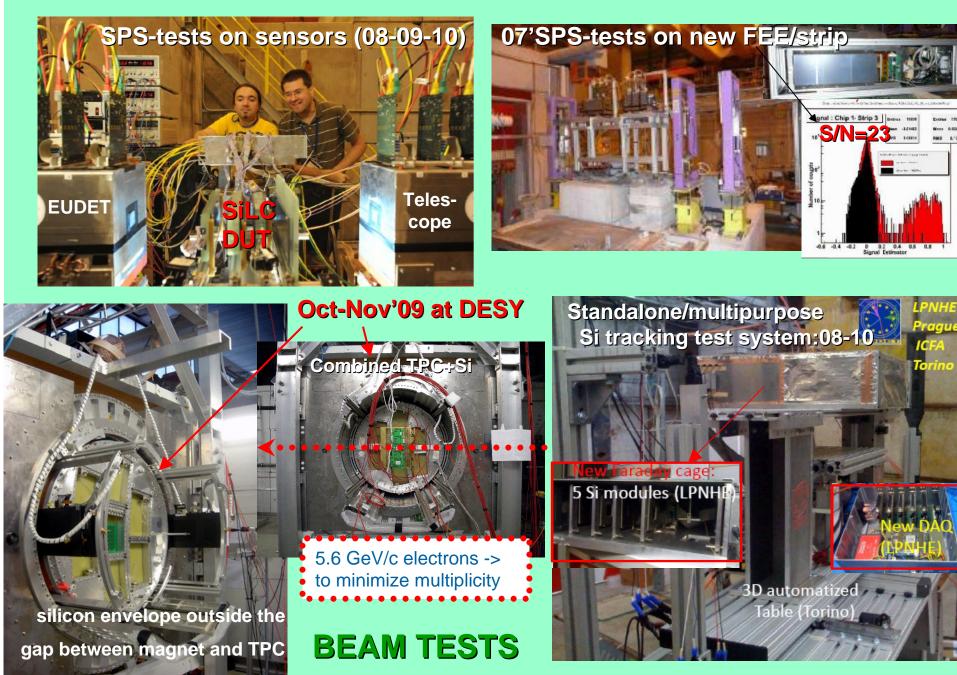

- Test bench and test beam inputs

- Detailed simulation developments

- Work plan for 2010-2012

also Keeping an eye on longer term future => Beyond Baseline

## **Silicon Sensors**

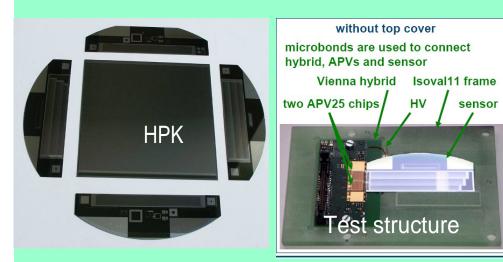

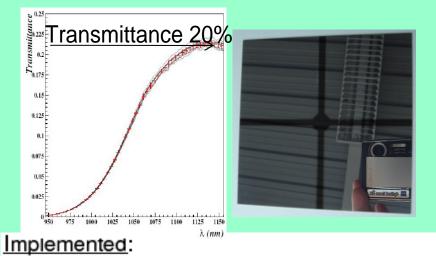

- **Baseline**: strip sensors, 8'', 200 μm thick, 50 μm pitch, alignment friendly (a.f.) with 70% transmittance & active edge options.

- **Present status:** 6", 320 m thick, 9.15x9.15 cm<sup>2</sup>, 50 pitch (HPK) and very preliminary A.F. option (20% measured transmittance)

Fully characterized at Lab and test beam with detailed Test Structure studies

Ø~10 mm window where AI back-metalization has been removed

Suggested (not cost effective for small batches):

- Strip width reduction (in alignment window)

- Alternate strip removal (in alignment window)

### Si sensors: how to reach 2012 baseline

R&D based on developed Lab test infrastructure, expert Labs, Industry, transfer to Industry

- 1) Next step on standard strips with HPK:  $200\mu$  m thick and 6''(8'') (feasible)

- 2) Developing more performing A.F. strips: R&D IMB-CNM and IFCA-CSIC

Very detailed simulation studies

Design and production of baby-sensor prototypes with optimised transmittance: 70%

First batch produced by CNM, under test by IFCA:

Promising first results. R&D pursued at least 2 more years.

Once technology is fully proven, transfer to Industry

Looks in good shape and feasible by 2012

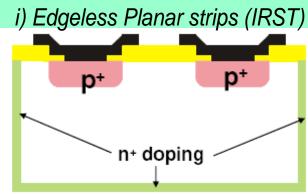

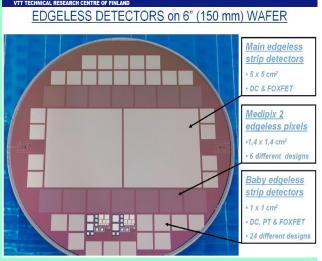

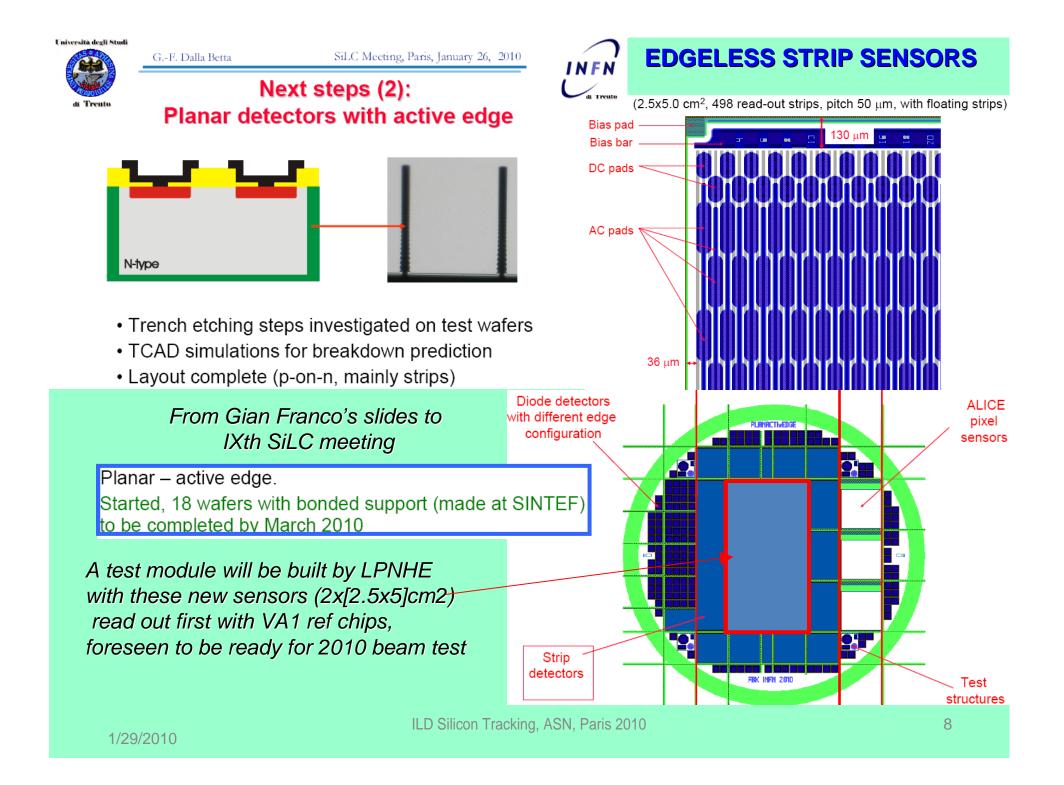

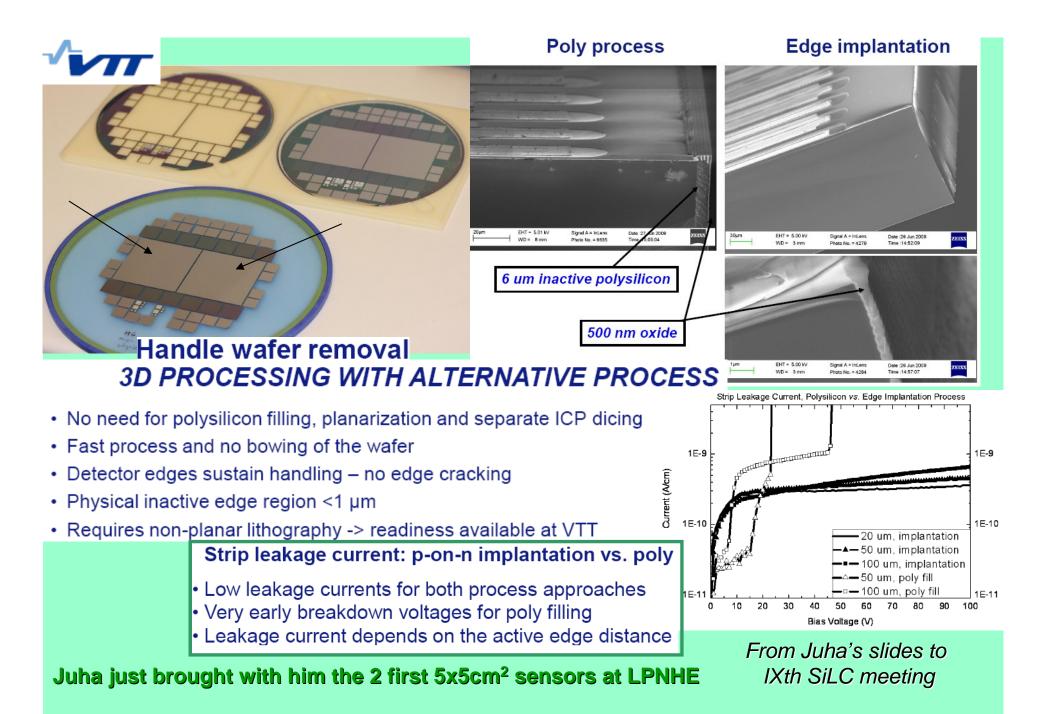

3) Active Edge strip sensors: two research lines under investigation

ii) Edgeless SOI strips (VTT) Full electrical tests

5x5cm<sup>2</sup> sensors Look very promising

2.5x5 cm2 proto sensors by Spring 2010 Once R&D is achieved and techno proven: transfer to Industry

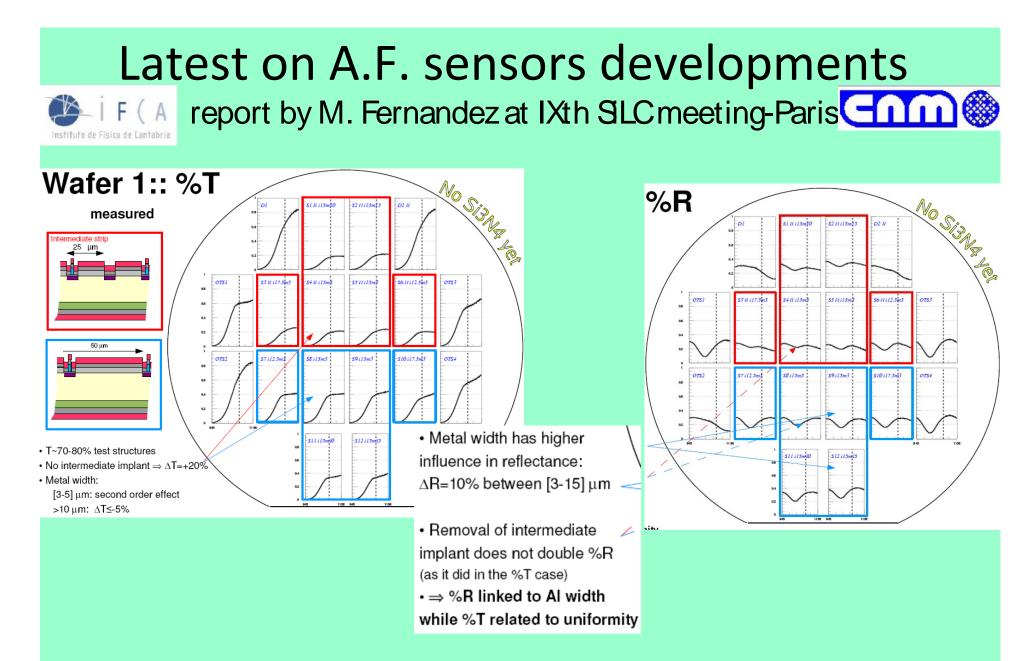

### Latest on A.F. sensors developments

**I F** ( A Instituto de Física de Cantabria

report by M. Fernandez at IXth SiLC meeting-Paris

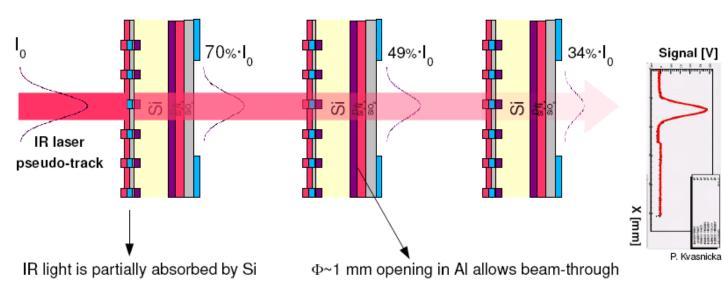

· Aim: align Si microstrip sensors using IR laser tracks

• Higher %T  $\Rightarrow$  simpler implementation of the system:

| Transmittance | 90% | 80% | 70% | 60% | 50% | 40% | 20% |  |

|---------------|-----|-----|-----|-----|-----|-----|-----|--|

| Traversed     | 30  | 15  | 10  | 7   | 5   | 4   | 2   |  |

|               |     | S   |     | HE  | ж   |     |     |  |

- System features:

- Laser intensity~200  $\text{MiPS} \Rightarrow \text{sharing same DAQ}$  as Si detector

- Silicon modules are directly monitored, no external fiducial marks

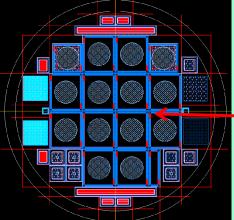

- 5+1 wafers

- 12 µstrip detectors per wafer (6 with intermediate strips, without metal contacts)

- 50 μm RO pitch

(25 μm interm. strip)

- 256 RO strips

- 1.5 cm length

varying strip width

(3,5,10,15 μm)

#### Promising results: R&D foreseen until end 2011, then transfer to Industry

1/29/2010

ILD Silicon Tracking, ASN, Paris 2010

## Edgeless strips sensors: Why?

Edgeless sensors decrease the non active edge regions of sensors (usually of a few hundreds of microns) down to about 10 to 20  $\mu m$ .

Our interest in edgeless or active edge sensors is motivated by:

- ✓ allow building large area Slicon trackers seamlessly tiled detector matrices,

- ✓ thus no need for sensor overlap.

- $\checkmark$  easier to build

- ✓ decrease of the material budget

- improvement of the tracking performances both in momentum and spatial resolution.

Two solutions based on the edgeless strip based on Edgeless planar and Edgeless SOI technologies are pursued.

1/29/2010

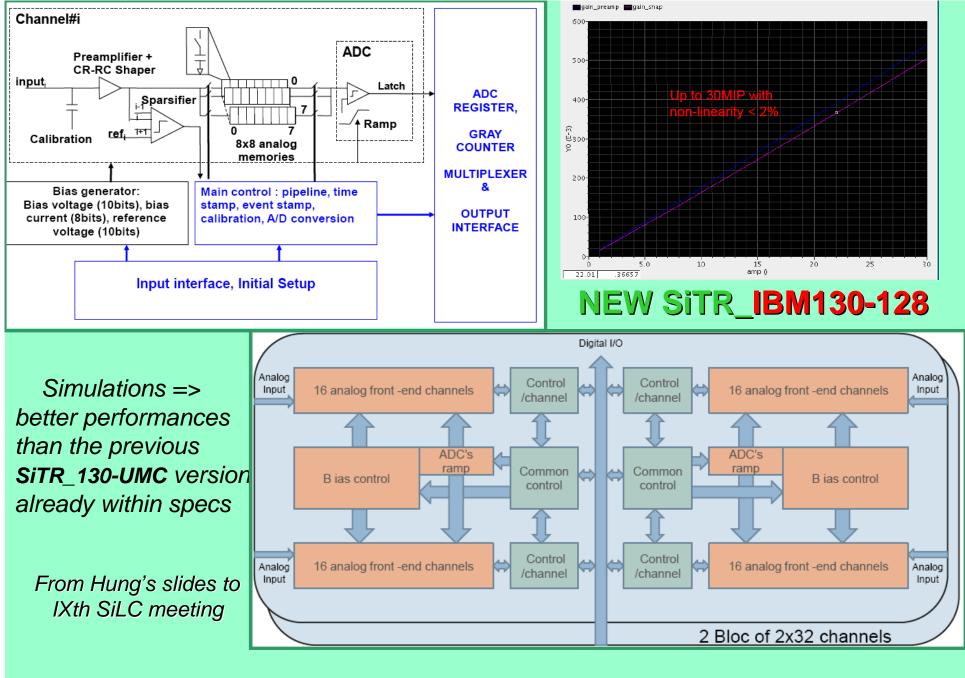

### **FE & R.O Electronics**

- **Baseline**: mix-mode analogue & digital STR design, in 90 nm DSM technology, blocks of 256 channels, direct connection with strip sensors, connection to DAQ (cabling, signal transmission), time stamping.

- **Current status:** in preparation, STR\_IBM-128, 130nm IBM, to equip a large number of test beam prototypes.

- Preliminary versions with various levels of design integration produced and tested:

- STR\_180 (VFE), STR\_130-4 (all analogue+A/D), STR\_130-88 (full mix-mode design)

- STR\_130-128: available end 2010 for equipping S tracker prototypes for test beams.

### FE/RO Electronics: how to reach 2012 baseline

### **ROADMAP ON ELECTRONICS**

- Go to 256 channels => block of 8x256 in one

- Go to 90nm CMOS techno

- Thinning 50  $\mu m$

- Direct connection FE-chip onto strip sensor

- Connection to the DAQ (serial/parallel)

- Connectics and cabling

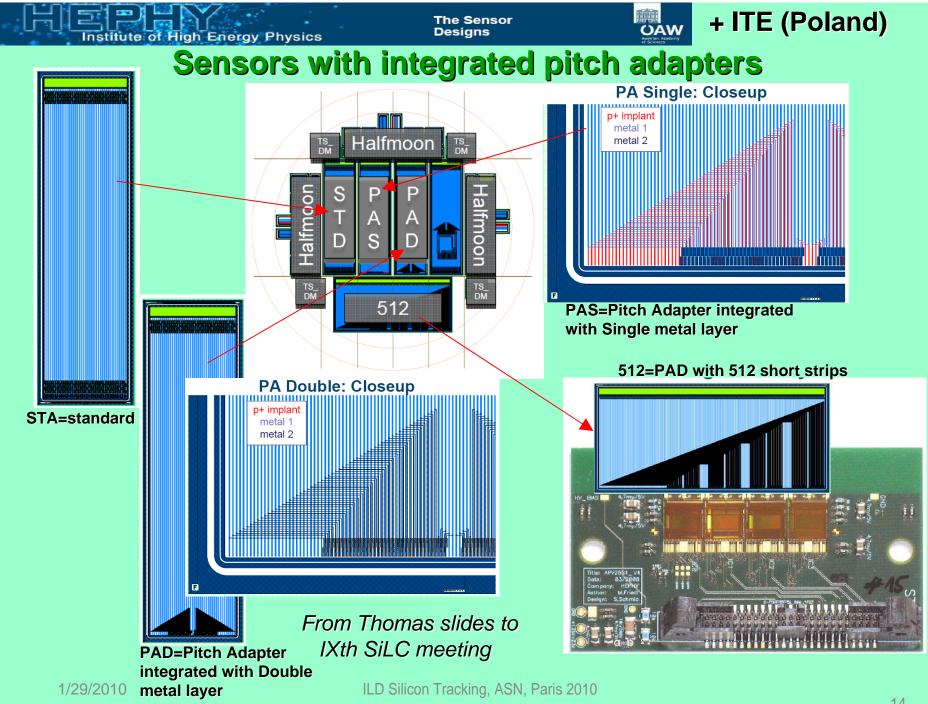

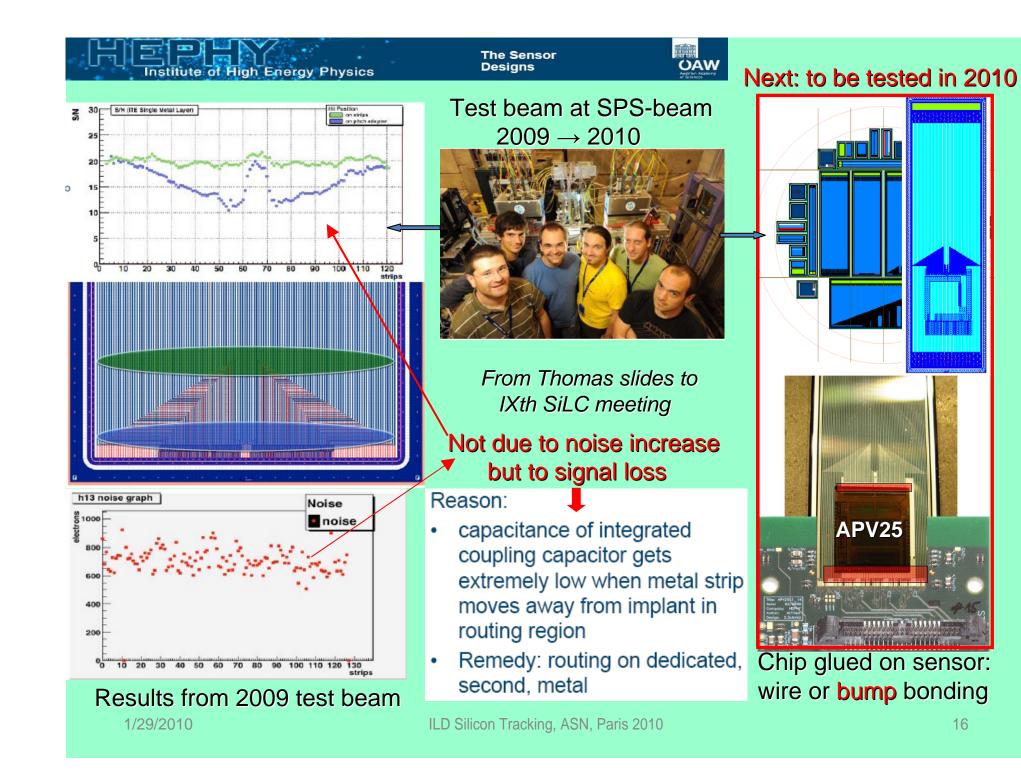

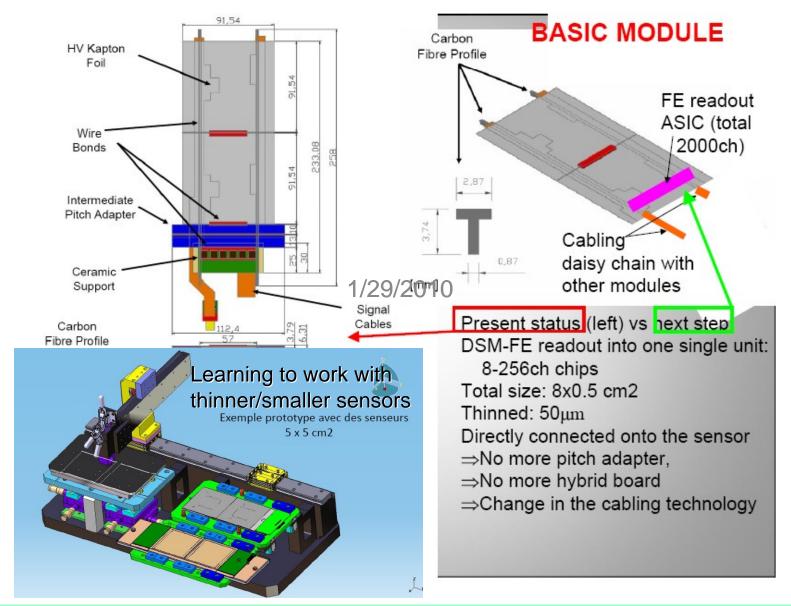

## **Direct connection sensors-FEE**

Major R&D objective: NO MORE Hybrid FEE board +pitch adapter

Presently: Module with 2 HPK built for EUDET at LPNHE

### ALL in ONE SOLUTION => direct connection of FE chip onto the sensor

- material budget,

- ✤ simplification of elementary module (tile) and

- ✤ of overall detector construction (burden put on sensor and FEE chip),

- improvement in performances

- Use high tech advances (cost?)

SiLC is pursuing in different steps: wiring onto the sensors: HEPHY + ITE-Warsaw (proto at CERN t.b'09-10); bump bonding in 10-11: HPK+LPNHE (with new FE chip), HEPHY+ITE (tests with APV25); investigating new ways in //: 3D vertical interconnect (part of the worldwide 3D interconnect effort) and **alternative solutions**.

#### LPNHE DAQ Silicon tracking architecture Physique Nucléaire A global schematic view of the Silicon DAQ architecture et des Hautes En ergies

Laboratoire de

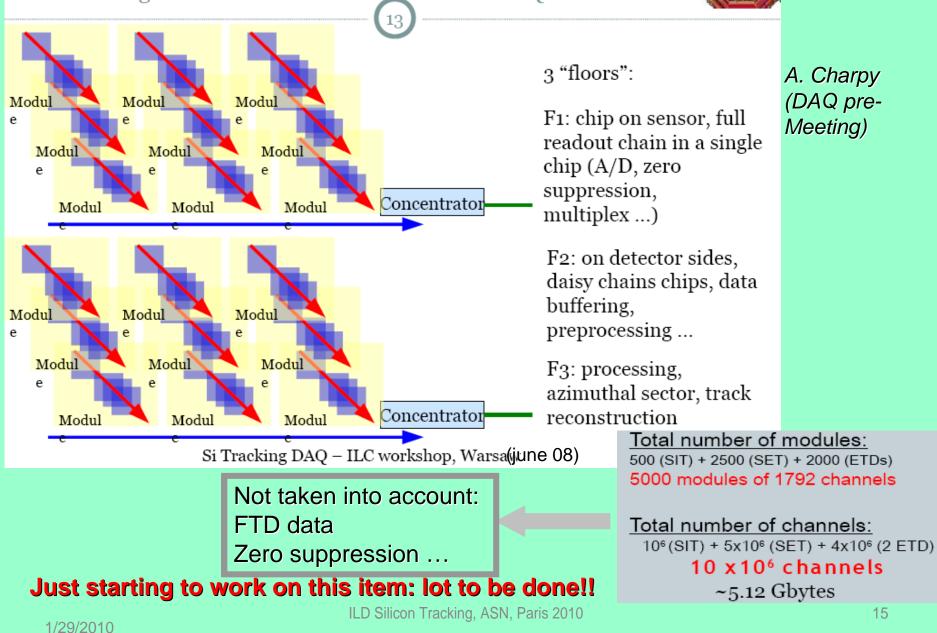

### **Chaining the DAQ sub-elements**

A. Charpy DAQ Pre-meeting • On the "module": Chaining of <mark>8 SiTR\_130-256</mark>

• "Super Module": Chaining the adjacent ladders toward a level 1 concentrator

• Half cylinder ("Detector Element"): Level 1 concentrator (toward level 2 ?)

• Toward the global Silicon DAQ system by Optical fibers

• Send to Global DAQ system

Depending on the final requirements

Just starting to think about the topology design & how to build the DAQ chain: Just getting our nose out of the FEE chip....LOT to DO: setting of a task force

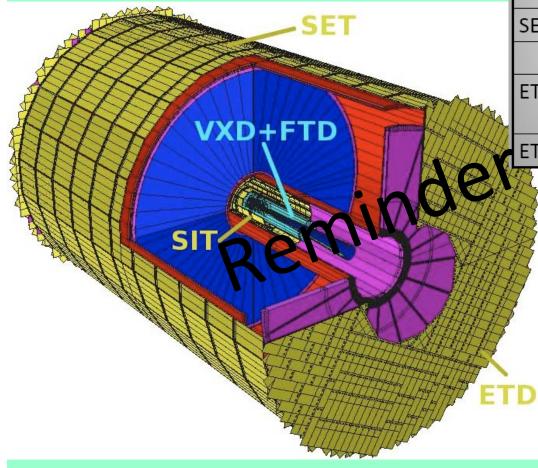

### Mechanics and Detector Integration

### **Baseline includes:**

- Modules made of planar strip sensors, FEE chip directly connected to strips, light structures and cabling/connectics, easy to build, based on a unique sensor size (but FTD).

- Light support structures

- Alignment systems & cooling included in the Si detector schema.

### **Optimization => simplified architecture, minimized %X0**

Present status: experience & advances gained from:

- expertise from LHC R&D and construction

- construction of prototypes for beam tests (SiLC)

- work on the ILD-LOI:

- => preliminary design of each component

- => their integration in the ILD detector design

- => the answers to alignment issues

- to push pull

- to time stamping

### But still lot of work to do for the 2012 baseline!

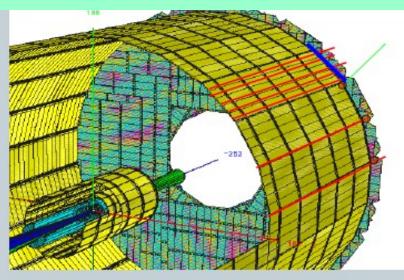

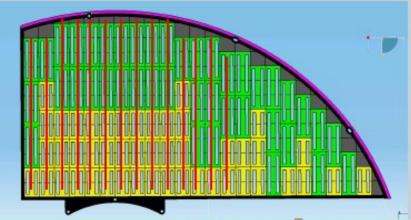

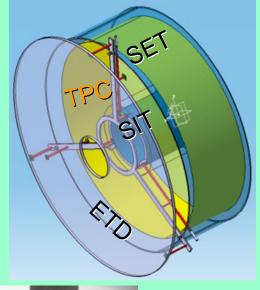

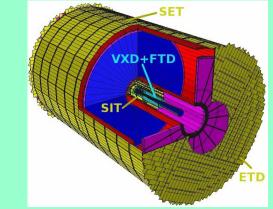

## ILD Hybrid tracking: The Slicon Envelope

(in numbers as currently in the ILD LOI)

|   | Component | Layer #               | # modules                         | # sensors/<br>module    | # channels | Total<br>surface m2 |  |

|---|-----------|-----------------------|-----------------------------------|-------------------------|------------|---------------------|--|

| ) | SIT1      | 1 <sup>st</sup> layer | 33 3                              |                         | 66.000     | 0.9                 |  |

|   |           | 2 <sup>nd</sup> layer | 99                                | 1                       | 198.000    | 0.9                 |  |

|   | SIT2      | 1 <sup>st</sup> layer | 90 3                              |                         | 180.000    | 2.7                 |  |

|   |           | 2 <sup>nd</sup> layer | 270                               | 1                       | 540.000    | 2.7                 |  |

|   | SET       | 1 <sup>st</sup> layer | 1260                              | 5                       | 2.520.000  | 55.2                |  |

|   |           | 2 <sup>nd</sup> layer | 1260                              | 5                       | 2.520.000  | 55.2                |  |

| ~ | ETD_F     | X or U or V           | 82/quad<br>=328/layer<br>=984/ETD | 2 or 3 or<br>possibly 4 | 2.000.000  | 30                  |  |

| 4 | ETD_B     | idem                  | idem                              | idem                    | idem       | 30                  |  |

#### Total number of channels: $10^{6}$ (SIT) + 5x10<sup>6</sup> (SET) + 4x10<sup>6</sup> (2 ETD) = 10 x10<sup>6</sup> channels Total area:

7 (SIT)+110 (SET) +2x30(ETDs) = **180 m<sup>2</sup>** Total number of modules:

500 (SIT) + 2500 (SET) + 2000 (ETDs)= 5000 modules with same sensor unit.

Unique sensor type (except FTD) but variable length strips wrt module location

GEANT4 simulation (here) & mechanical design (CATIA) in progress

1/29/2010

### Mechanics & Integration: how to reach the 2012 baseline The to-do-list:

- **Elementary module** sensor, FEE & connection/strip, cabling, support structure

- CAD design of each components, including more and more details.

- Support structure studies: constraint studies, tests with mechanical prototype

- Integration in the overall ILD detector

- **Alignment systems:** laser based (A.F.) with AF sensors for FTD, SIT (SET, ETD?) Alignment system for Si components between them and with the other components.

- **Cooling:** to be further evaluated (power cycling real impact and eventual drawback?)

- **Construction lines:** design and development of tools for construction lines appropriate to the detector to be built, even in Labs already equipped for LHC, construction set-up have to be adapted.

- Push pull issues to be studied and solved (tests?) but first better defined! (In red the most critical issues)

CAD studies, detector prototyping for test beams, mechanical prototypes for dedicated studies, definition of the tools and setting up of the construction lines. Completed in parallel with detailed simulation studies and test beams.

#### **THE ELEMENTARY "TILE":**

sensor x FEE chip x connect FE/strips x mechanics x cabling ≤ 0.8% total

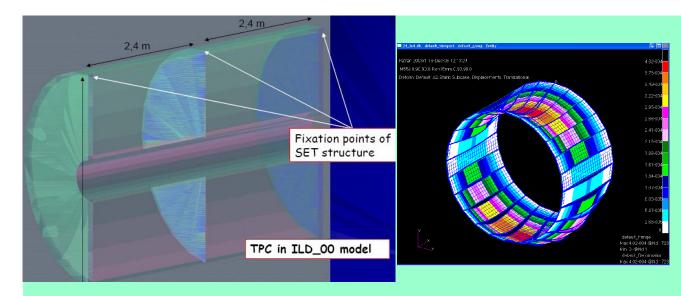

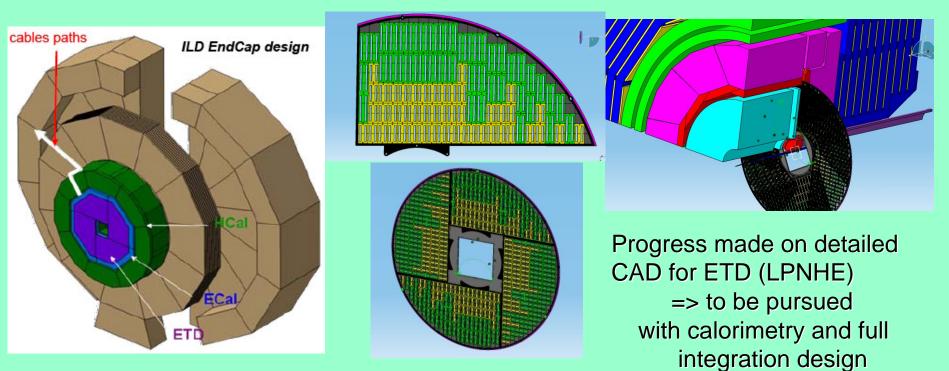

#### SET/ETD: CAD & INTEGRATION

Restarting work on CAD design of the SET and SIT/SET possible common support (Torino)

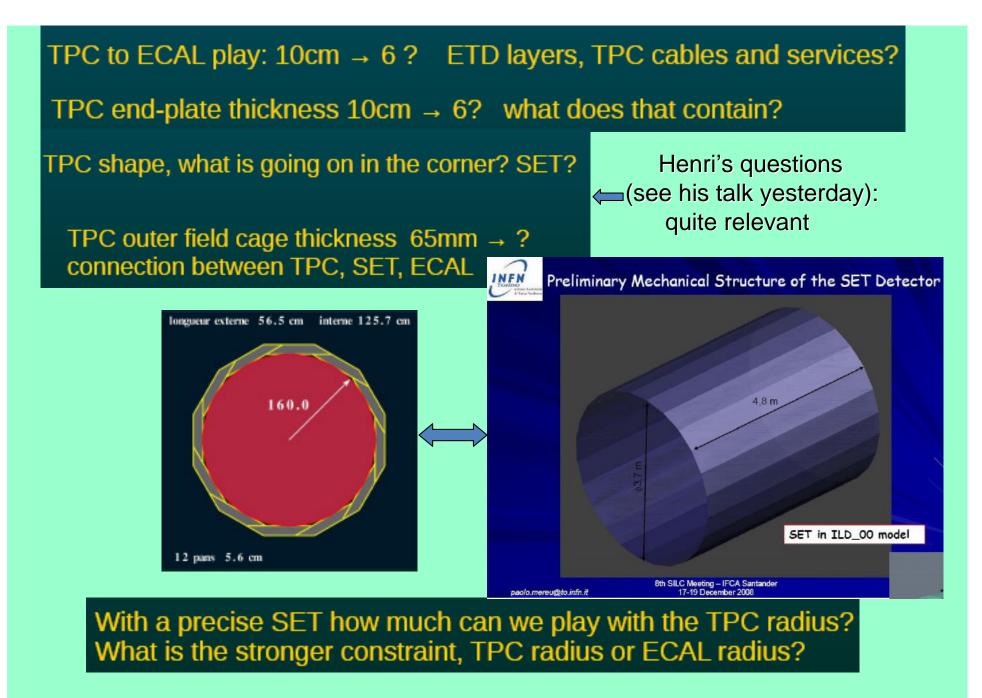

## SIT/SET/ETD:

- Detector design: good design => to be detailed

- Detailed CAD of support structures, ST/SET common structure (common support structure proposed by Torino)

- ETD: CAD design well advanced to be rediscussed with calo/Mathieu

- Detailed simulation studies to be performed in the barrel with realistic material budget

- Same and much more tricky in the EndCap: (TPC endcap?)

- Alignment: SIT can use the same system than FTD not the SET or the ETD (to be studied)

- Alignment between SET/SIT (strategy OK)

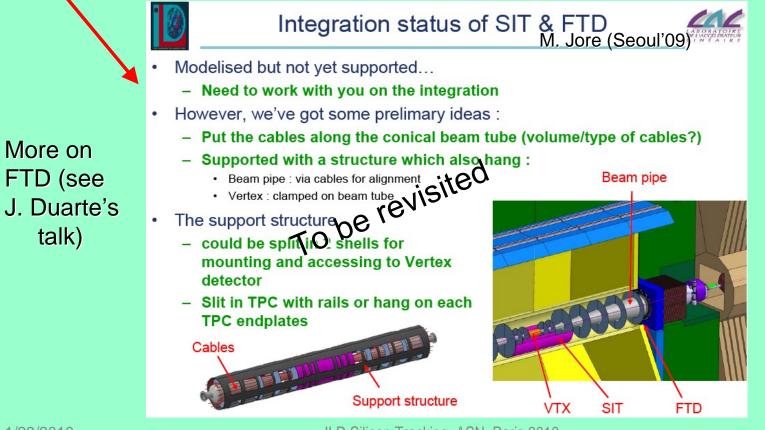

### Innermost Si tracking: SIT+FTD

- To be optimized: number and positioning of the disks

- To be decided: S technology & 3+4 present scheme

- Alignment: OK for ST and for FTD with A.F. sensors (include fibers)

- Estimate of material budget to be refined

- Support of ST & FTD disks on TPC to be revisited

The spanish teams especially IFCA & IFIC have taken care of FTD simulations, detector design and alignment. Needs to be pushed further on.

## **Alignment strategies:**

Between components: IR Laser+fibers + pixels + FEE off the shell system

How to align **SET & ETD?**

Multilayer Si tracking system: A.F. sensors + IR laser + fibers read out as usual strip sensor

Passing from test bench to the reality of a large detector

An Hybrid tracking system as ILD tracking system: TPC+Si  $\Rightarrow$ Not only one system to align the whole Si tracker as in the case of an All-Si-Tracker

Useful also when push pull: system run outside data taking. Independent DAQ.

1/29/2010

ILD Silicon Tracking, ASN, Paris 2010

System kit set-up to

Experience the system

in the Lab test bench.

ILD Silicon Tracking, ASN, Paris 2010

1/29/2010

### Simulations and performances studies

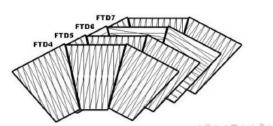

#### (*W. Mitaroff presentation at simu pre-meeting*) LOI => DBD: from SGV/ LDT fast simus to detailed simulation

### Si Tracker Detector Geometry

- Full Simulation Systems:

- Mokka (V. Saveliev): not fully implemented ILD\_00;

- ILCroot (A. Charpy): full & detailed description.

- New Geometry System:

- will replace present Mokka-GEAR database system;

- commitment to the "full description" as in ILCroot.

Strips

| Layer | R [ mm]   | z  [ mm] | RL [%] | σ[μm] | d <sub>strip</sub> [ µm] | α [°]           | Туре   |

|-------|-----------|----------|--------|-------|--------------------------|-----------------|--------|

| FTD1  | 24.5-160  | 220      | 0.25   | 7     | -                        | -               | Pixels |

| FTD2  | 39.9-160  | 380      | 0.25   | 7     | -                        | -               | Pixels |

| FTD3  | 52.0-304  | 660      | 0.25   | 7     | -                        | -               | Pixels |

| FTD4  | 84.4-309  | 1070.6   | 0.65   | -     | 25                       | 6               | Strips |

| FTD5  | 116.7-309 | 1481.2   | 0.65   | 3-3   | 25                       | 6               | Strips |

| FTD6  | 149-309   | 1891.8   | 0.65   | -     | 25                       | 6 (rot. by 90°) | Strips |

Proposal for an optimized forward tracker (with minimal diversity of sensors):

### Si Tracker Material Budget

- Work on including realistic figures for

- Front/end electronics;

- Cabling on detector;

- "Cooling" of detector.

- Already a good approximation provided by the R&D activities; will be updated.

- Open questions: how important are

- Longitudinal resolution (strip stereo angles how) ?

- Time tagging (relief bunch-train induced problems)?

- **ETD:** assess usefulness for forward calorimetry ?

- Goal: optimization studies to be revisited

- so far done mainly by LDT, to be redone by Full Sim.

181.4-309

2302.5

### Simulations and performances studies (cont'd)

(W. Mitaroff presentation at simu pre-meeting)

### Si Tracker Software Tools Track Reconstruction (1)

- Three main regions and three track reconstruction strategies (see Winfried's talk)

- => very forward (FTD only)

- => EndCap (VXD+FTD+piece of TPC+ETD)

=> Central Barrel (TPC + ST/SET)

- -> In parallel pursue the development of the track reconstruction ambitious plan as proposed by Winfried (provided we have the manpower...)

- As first step: work with the hits on <u>all</u> S tracking components as done so far with ST and FTD

#### Let's Keep an eye on longer term future

#### => Beyond BaseLine: A Silicon Pixel Tracker Ch. Damerell (RAL)

- The idea (first presented at Sendai LCWS 2008) is to develop a silicon pixel tracking system as a possible upgrade for ILD

- Main advantage would be reduced material budget (<10% X<sub>0</sub> over all polar angles for vertex detector plus tracking system)

- Guiding principle is a 'separated function' approach:

- ~5 tracking layers (barrel plus disks) with 50  $\mu$ m pixels, integrating signals throughout the bunch train (~0.6% X<sub>0</sub> per layer)

- A few timing layers (two as an envelope close to the ECAL, one as a barrel between vertex detector and first tracking layer) with 150 μm pixels (~2% X<sub>0</sub> per layer)

- So we provide precise timing for each track, but not for each point on the track

- This approach relies on the well-established robustness of pixel tracking systems wrt background – what is lost in timing can be compensated by fine granularity. *Timing consumes power (hence increases material budget) while granularity need not*

- One promising technology is charge-coupled CMOS pixels, already under development for ILD vertexing (the ISIS option)

The SiLC collaboration is including this research line with 3 key points: detailed simulation studies, possible staging (?), pixel technology

1/29/2010

## Plan & timeline (still tentative)

Legend: 90nm\* = change in technology; New version\* \* = 90nm+8x256 block+thinning

| Workpackage | item              | 2010                         | 2011           | 2012                   |

|-------------|-------------------|------------------------------|----------------|------------------------|

| 1) sensors  | Strips 200µm/8"   | Collab with                  | Industry Test  | 1 <sup>st</sup> series |

|             | A.F. strips       | R&D →                        | Full proof Ind | ustry transfer         |

|             | Active edge strip | R&D                          | R&D            | Industry transfer      |

| 2) Direct   | Wire bonding      | Prototyping &                | R&D with firm  | industrialisation      |

| connection  | Bump bonding      | Prototyping                  | & R&D with     | Industry (HPK)         |

| Chip-strips | 3DVert connect    | R&D                          | R&D            | R&D >                  |

|             | alternative       | R&D                          | R&D            | prototyping            |

| 3) FEE chip | 130nm-128ch       | Foundry/test/                | New prod for   | Test beam protos       |

| R.O>DAQ     | 90nm*, 256ch      | design                       | Layout test    | Equip protos F.P.      |

|             | New version**     |                              |                | New version            |

|             | Connect/Cabling   | R&D                          | R&D & tests    | R&D & tests            |

|             | Path to DAQ       | R&D                          | R&D & tests    | <b></b>                |

| 1/29/2010   | ILD \$            | Silicon Tracking, ASN, Paris | 2010           | 31                     |

## Si tracking-ILD: Plan & timeline (cont'd)

| Workpackage   | item                 | 2010                         | 2011          | 2012         |

|---------------|----------------------|------------------------------|---------------|--------------|

| 4)Detector    | Elem. Module         |                              |               | >            |

| Construction  | cooling              |                              |               | >            |

| &integration  | Alignment syst.      |                              |               | >            |

|               | Support struct.      |                              |               | >            |

|               | CAD detector studies |                              |               | >            |

|               | Integration study    |                              |               | >            |

| 5) Test beams | Will accompany       | & complete the               | R&D studies & | developments |

| & simulation  | Will accompany       | & complete the               | R&D studies & | developments |

| studies       |                      |                              |               |              |

|               |                      |                              |               |              |

|               |                      |                              |               |              |

|               |                      |                              |               |              |

| 1/29/2010     | ILD S                | Silicon Tracking, ASN, Paris | 2010          | 32           |

| 1  |          | les estates                                   | T           |          |               |           |                 |                     |             |                       |               | Long and      |

|----|----------|-----------------------------------------------|-------------|----------|---------------|-----------|-----------------|---------------------|-------------|-----------------------|---------------|---------------|

| N° | 0        | Nom de la tâche                               | Tri 2 Tri 3 | Tri 4    | 2010          | Tri 2 Tri | 2 Tri 4         | 2011<br>Tri 1 Tri 2 |             | 2012<br>Tri 1 Tri 2   | Tri 2 Tri 4   | 2013<br>Tri 1 |

| 1  |          |                                               | 1112 1 1113 | 1014     |               | 1012 1 10 | 3 1 1114        |                     |             |                       | 1 11 9 1 11 4 | +             |

| 2  | i –      | Sensors                                       |             |          |               |           |                 |                     |             |                       |               | d I           |

| 3  | 1        | Strips 200µm/8"                               | -           |          |               |           |                 |                     |             |                       |               | j l           |

| 4  | 111      | Collab with industry                          |             |          |               |           |                 | I                   | <b>_</b>    |                       |               | ·             |

| 5  | 1        | Test 1st series                               |             |          |               |           |                 |                     | -           |                       |               | 1             |

| 6  | <b>F</b> | A.F. strips                                   |             |          | <u></u>       |           |                 |                     |             |                       |               |               |

| 7  | 11       | R&D Full Proof                                | -           |          |               |           |                 | I                   | -           |                       |               |               |

| 8  | 111      | Industry transfer                             |             |          |               |           |                 | 1                   |             |                       |               | 1             |

| 9  | 1        | Active edge strip                             |             |          | ₩ <b></b>     |           |                 |                     |             |                       |               |               |

| 10 | 11       | R&D Industry transfer                         |             |          |               |           |                 | 1                   |             |                       |               |               |

| 11 | í –      |                                               |             |          |               |           |                 | 1                   |             |                       |               |               |

| 12 | i        | Direct connection Chip-strips                 |             |          | ₩ <b>~~~</b>  |           |                 |                     |             |                       |               | d i           |

| 13 | i —      | Wire bonding                                  |             |          | ∳: <b>─</b> ─ |           |                 |                     |             |                       |               | a I           |

| 14 |          | prototyping & R&D with firm industrialisation | 1           |          |               |           |                 |                     |             |                       |               |               |

| 15 | 1        | Bump bonding                                  | 1           |          | ÷             |           |                 |                     |             |                       |               | i i           |

| 16 |          | prototyping & R&D with industry (HPK)         | 1           |          | c             |           |                 |                     |             |                       |               |               |

| 17 | 1        | 3DVert connect                                |             |          |               |           |                 |                     |             |                       |               | ž 🛛           |

| 18 | 11       | R&D                                           | 1           |          |               |           |                 | 1                   |             |                       |               | il l          |

| 19 | 1        | alternative                                   |             |          | ý —           |           |                 |                     |             |                       |               | a 🛛           |

| 20 | 11       | R&D                                           |             |          |               |           |                 |                     |             |                       |               |               |

| 21 |          | Prototyping                                   |             |          |               |           |                 |                     |             |                       |               | li I          |

| 22 | 1        |                                               | 1           |          |               |           |                 |                     |             |                       |               |               |

| 23 | 1        | FEE chip R.O> DAQ                             |             |          |               |           |                 |                     |             |                       |               | a 🕴           |

| 24 | 1        | 130nm-128ch                                   |             | <u> </u> | =             |           |                 |                     |             |                       |               | ø 🛛           |

| 25 | 11       | Foundry / test                                |             |          |               |           | $ \rightarrow $ |                     |             |                       |               |               |

| 26 | 111      | New prod for test beam protos                 |             |          |               |           |                 |                     |             |                       |               | 1             |

| 27 |          | 90nm*, 256ch                                  |             |          |               |           | <b>_</b>        | !                   |             | 1                     |               | a             |

| 28 | 31.0     | Design Layout test equip protos F.P.          |             |          |               |           |                 |                     |             |                       |               | <i>k</i> –    |

| 29 |          | New version**                                 |             |          |               |           |                 |                     |             | ÷                     |               | Pi I          |

| 30 | 31.1     | New version                                   |             |          |               |           |                 |                     |             |                       |               | 4             |

| 31 |          | Connect/Cabling                               |             |          | ₩ <b>~~~</b>  |           |                 |                     |             |                       |               | 퀴 🛛           |

| 32 | 31.2     | R&D tests                                     |             |          | c             |           |                 |                     |             |                       |               | <u>k</u>      |

| 33 |          | Path to DAQ                                   |             |          | ₩ <b></b>     |           |                 | !                   |             |                       |               | <b>4</b>      |

| 34 | 11       | R&D tests                                     |             |          |               |           |                 |                     |             |                       |               | ¥             |

| 35 |          |                                               |             |          |               |           |                 |                     |             |                       |               |               |

| 36 |          | Detector Construction & Integration           |             |          | <u>۳</u>      |           |                 |                     |             |                       |               | 4             |

| 37 | 11       | Elem. Module                                  | l           |          | 2010          |           |                 | 0014                |             | 0040                  |               |               |

| N° | 0        | Nom de la tâche                               | Tri 2 Tri 3 | Tri 4    | Tri 1         | Tri 2 Tri | 3 Tri 4         | 2011<br>Tri 1 Tri 1 | 2 Tri 3 Tri | 2012<br>4 Tri 1 Tri 2 | Tri 3 Tri 4   | 2013<br>Tri 1 |

| 38 |          | cooling                                       |             |          |               | 114 1 11  | 0 1 104         |                     |             |                       | 1 119 1 114   |               |

| 39 | 11       | Alignment syst.                               | 1           |          | <u> </u>      |           |                 | :                   |             | 1                     |               | ái l          |

| 40 | 11       | Support struct.                               | 1           |          |               |           |                 | -                   |             |                       |               |               |

| 41 |          | CAD detector studies                          | 1           |          |               |           |                 |                     |             | 1                     |               | al I          |

| 42 | 11       | Integration study                             | 1           |          | <u> </u>      |           |                 | :                   |             | 1                     |               |               |

| 43 | Ē        |                                               | 1           |          |               |           |                 | i                   |             |                       |               |               |

| 44 | 11       | Test beams & simulation studies               | 1           |          |               |           |                 | i                   |             | ĺ                     |               |               |

| 44 | 1-4-4    | l est beams & simulation studies              |             |          |               |           |                 |                     |             |                       |               | 41            |

## **Concluding remarks**

- Reasonably good chances to reach the 2012 defined baseline on each of the crucial items,

- Provided (at least keeping) the FTE (avoid dispersion in too mmany other projects)

- And getting the needed funding

- ASSET: synergy with LHC upgrades

Ce document à été crée avec Win2pdf disponible à http://www.win2pdf.com/fr La version non enregistrée de Win2pdf est uniquement pour évaluation ou à usage non commercial.