# TPC DAQ: status and plans

### G. De Lentdecker

(Université Libre de Bruxelles, Brussels, Belgium)

and Ulf Mjornmark

(University of Lund, Sweden)

On behalf of the LCTPC Collaboration

# Overview

- Current status

- AFTER DAQ

- ALTRO DAQ

- Future developments

### **Current status**

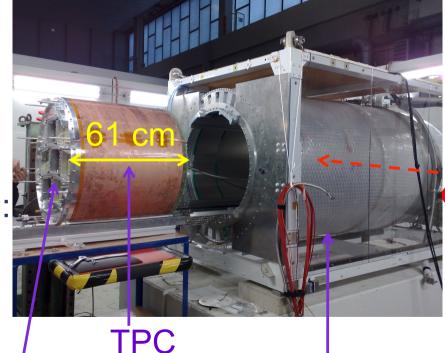

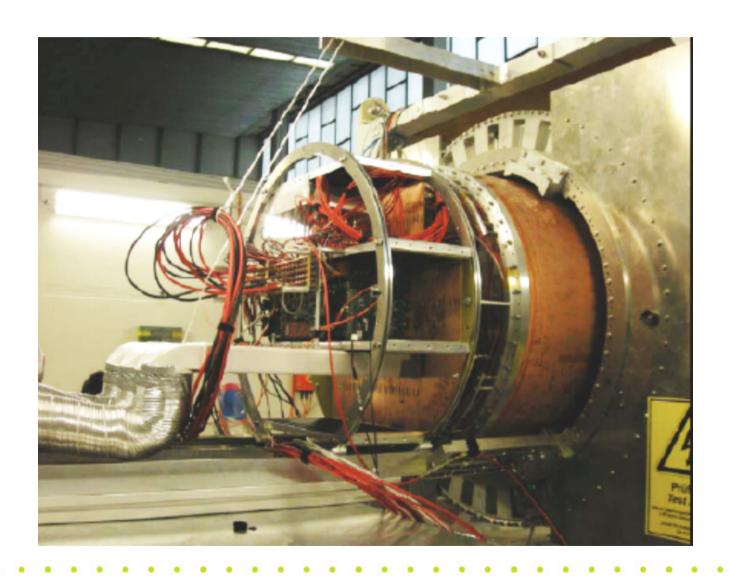

- Since end of 2008, LCTPC collaboration is testing a large TPC prototype (LPTPC) with 6 GeV e<sup>-</sup> beam in DESY

- TPC endplate allows to easily accommodate different Micro

Pattern Gas Detector (MPGD)

- 3 MPGD technologies are tested:

- MICROMEGAS + PADs

- Double GEM + PADs

- Triple GEM + CMOS Timepix chip

- 3 ReadOut Electronics are tested:

- MICROMEGAS + T2K AFTER

- Double GEM + ALTRO (ALICE)

- Triple GEM + CMOS Timepix chip

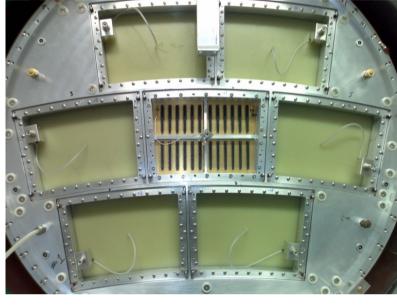

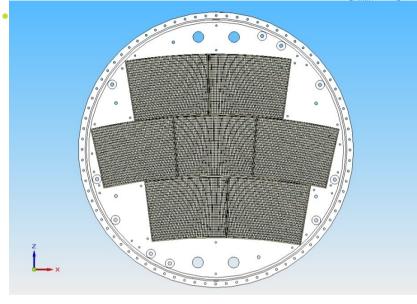

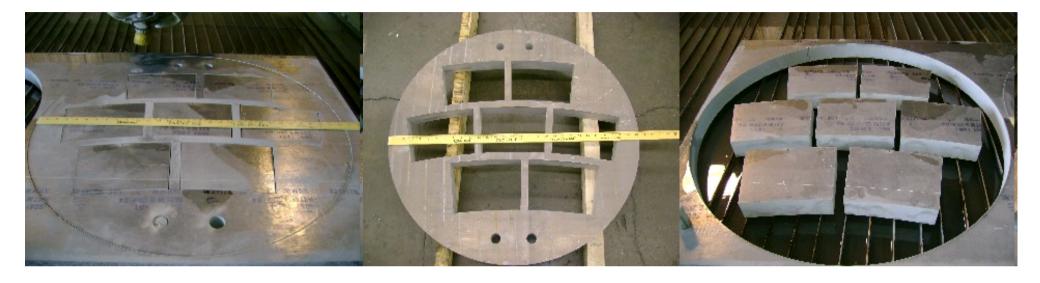

TPC endplate

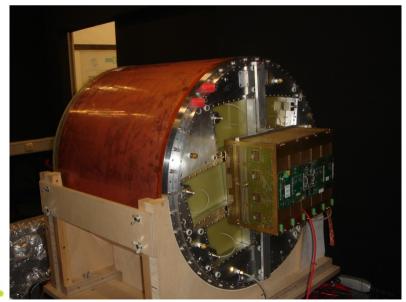

Solenoid (1T)

### Current status II

- Since end of 2008, 12 weeks of test beam in DESY with LPTPC

- Both GEMs and MICROMEGAS are running nicely

- As well as their DAQ

- However

- Different DAQ systems for the different detectors

- In ILD, space will be limited for TPC electronics (10 cm)

- => need redesign of FE readout and DAQ interface

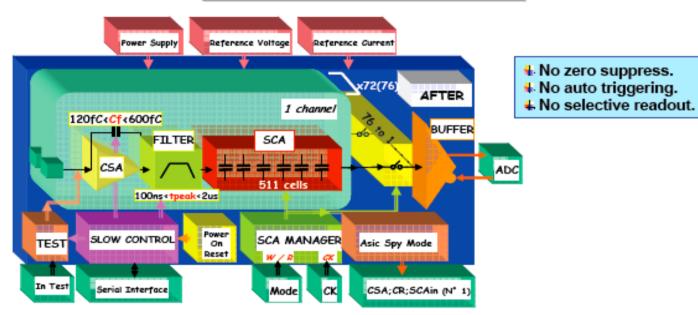

# IC DAQ for MICROMEGAS+AFTER

POWER Supply

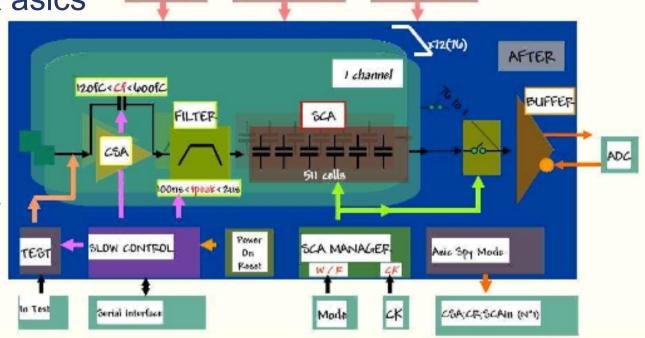

- AFTER electronics was developed for the T2K TPC

- 1 FEC has 4 AFTER asics

- 1 AFTER has 72 ch:

- 4 gains

- 16 peaking times

from 100 ns to 2 μs

- 511 analog memory cells/channel

Reference Current

Peterence Voltage

- 6 FECs are driven by a Front-End Mezzanine (FEM) card

- FEM is linked to Data Concentrator Card (DCC) via a duplex optical fiber

- DCC sends data to DAQ PC through Ethernet channel

#### **DATA FLOW** DAQ: • Maximum rate: 14 Hz (Zero Suppression mode) • Triggered by beam (no TLU) • Easy to use (GUI) Back-end T2K electronics Optical electronic 1-hour automatic 1728 channels fibre (ML405) rsync backup TCP/IP via ethenet PC T2K DAQ 0000 0000 on Linux ILC\_DATA\_01 ILC\_BCKP\_01 Grid 0000 ILC\_DATA\_02 ILC\_BCKP\_02

0000

Saclay

27/01/2010

NativeToLCIO (Yun-Ha Shin)

Transfert done by K. Dehmelt

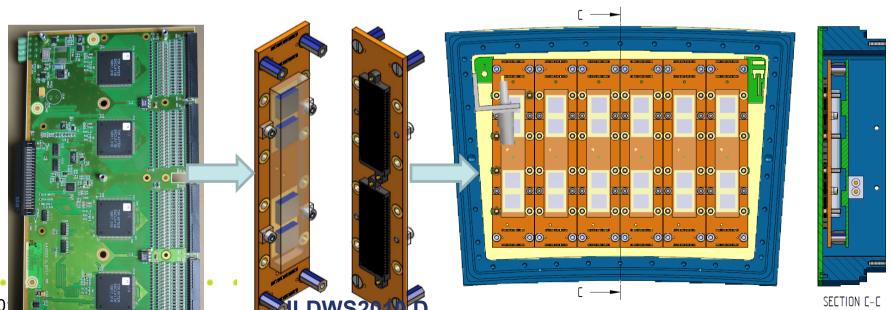

# Future Plan

Resistive technology choice

In 2008/2009 with one detector module (1728ch)

In 2010 with 7 detector modules.

Reduce the electronics

27/01/2010

# Future plans

- This requires:

- New PCB routing

- keep pad layout

- Use flat 300 point connectors

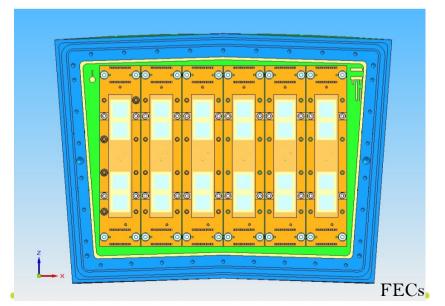

#### New FEC

- Remove part of the protection (Resistive foil protects)

- Remove packaging (silicon is 7x7mm instead of 20x20 for the packaging)

- transfer power regulation and ADC to the mezzanine module card.

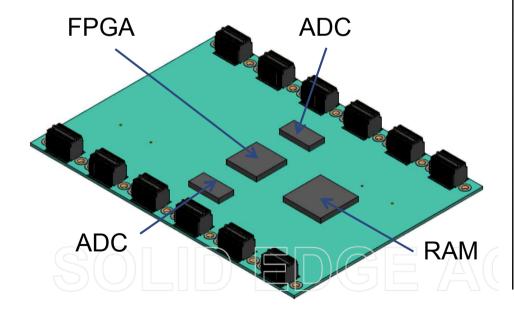

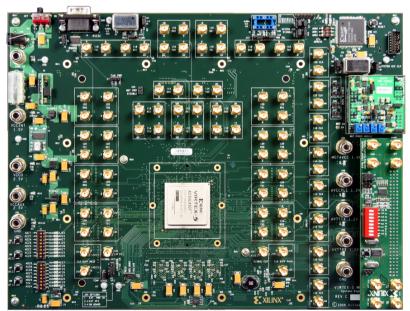

# Future plans

=> requires new FEM and Back-end Module:

• **FEM**:

- Back-end:

- ML523 development kit from Xilinx

- → vc5vfx100t FPGA from Virtex-5 device family

- Embedded PowerPC

- 16 Multi Gigabit Transceivers

- Embedded Ethernet MAC

- → 128 Mbyte DDR2 memory

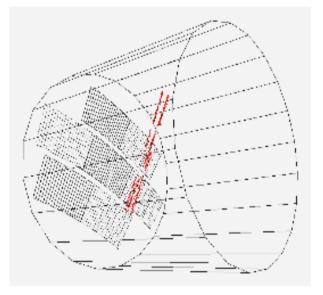

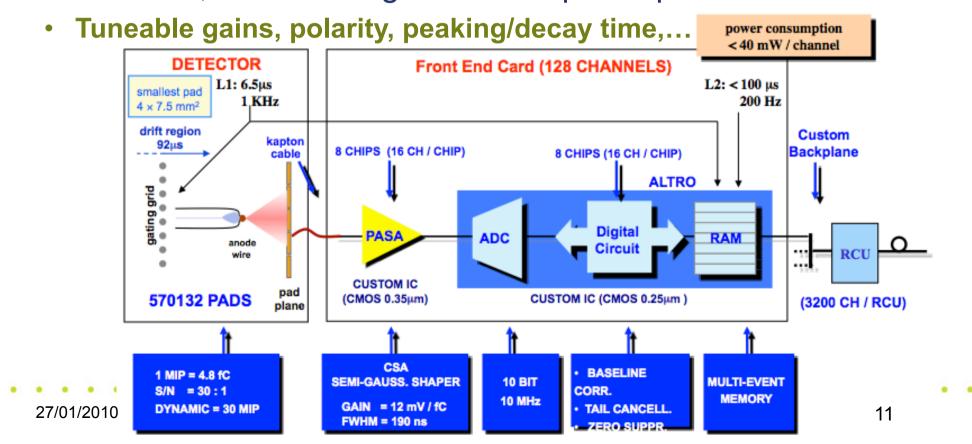

# LPTPC equipped with Double GEM + ALTRO

### **ALTRO RO**

- ALTRO chip (ALICE TPC Read Out) has 16 channels

- Digitize and buffer the signal

- Perform zero-suppression

- 1 FEC has 8 ALTRO chips

- For LCTPC, CERN designed a new preamp: PCA16

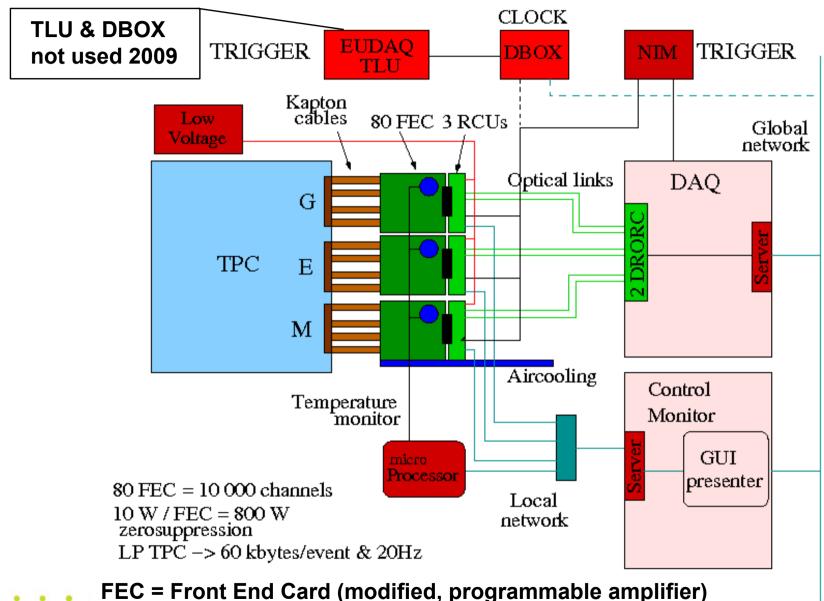

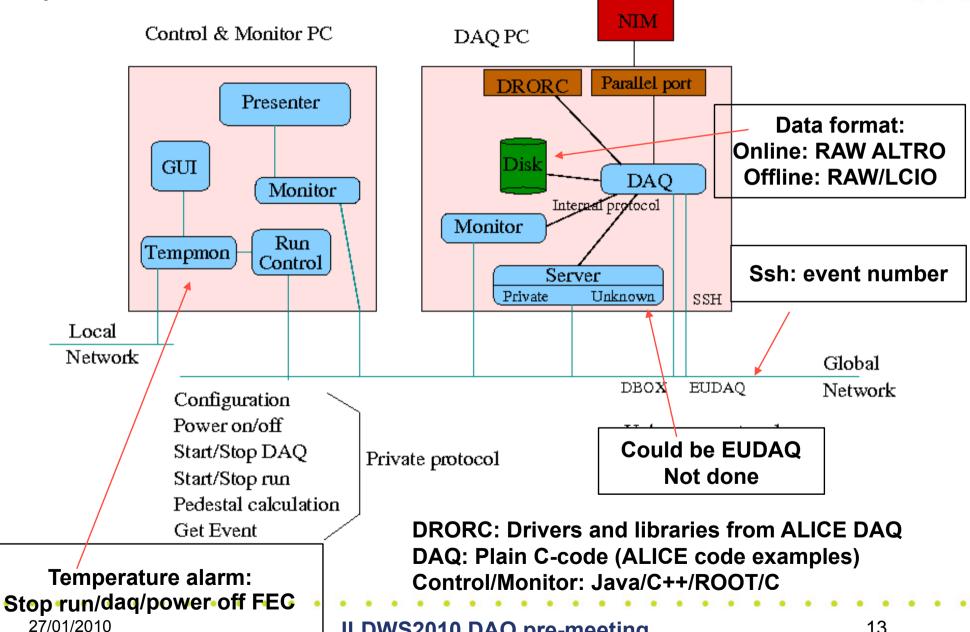

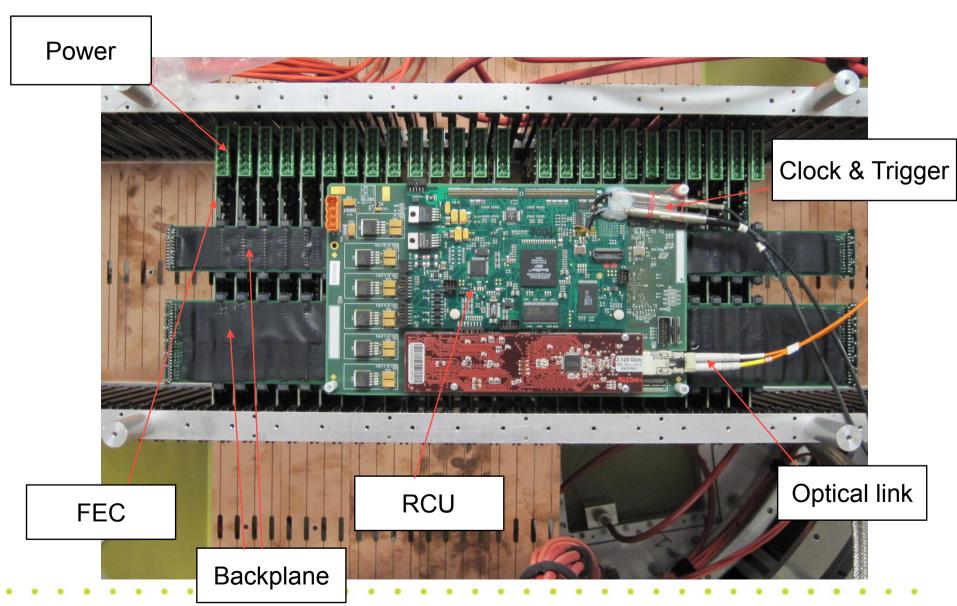

# DAQ for GEM + ALTRO

FEC = Front End Card (modified, programmable amplifier)

RCU= Readout Control Unit (modified trigger/clock inputs

DRORC = Data ReadOut Receiver Card

## ALTRO standalone software

**ILDWS2010 DAQ pre-meeting**

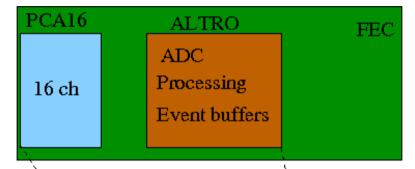

# CURRENT ALTRO READOUT

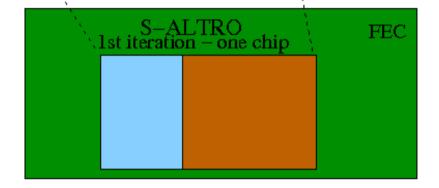

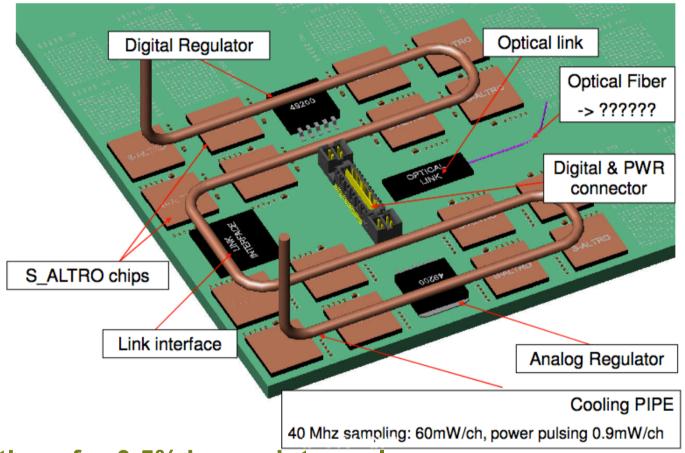

# FEC Developments: S-ALTRO

#### Present:

(programmable)

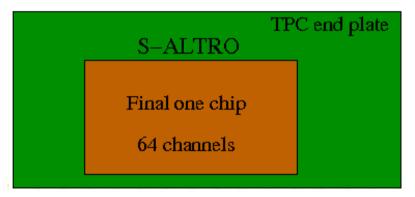

### Future:

**ALTRO**

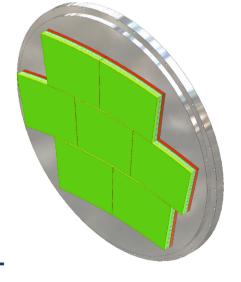

### S-ALTRO mounted on TPC endplate

S-ALTRO will be flip-chip mounted on PCB (! Cooling!)

### **Expectations for 0.5% beam duty cycle:**

- average power / channel 0.5 mW / channel (at 10 MSPS)

- average power / m<sup>2</sup> 100 W (at 10MSPS)

- For the short term:

- Try to use EUDAQ and TLU for the different readout electronics

- This should help for future combined test beams

- At much longer term:

- Investigate the possibility to use micro-TCA standard

# Conclusions and plans

- The Large TPC Prototype is working well, with GEMs and MICROMEGAS

- AFTER and ALTRO DAQ working fine as well

- For both, a lot of developments ongoing to reduce the size of the FE readout

- + Need to use EUDAQ and TLU for future combined test beams

- + Interests to try microTCA standard

# Back-up slides

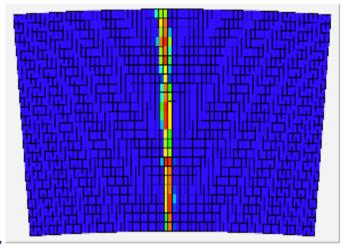

### **TPC Performance**

Size  $\phi = 3.6 \text{m}, L = 4.3 \text{m}$  outside dimensions

Momentum resolution (3.5T)  $\delta(1/p_t) \sim 9 \times 10^{-5}/\text{GeV/c}$  TPC only (× 0.4 if IP incl.)

Momentum resolution (3.5T)  $\delta(1/p_t) \sim 2 \times 10^{-5}/\text{GeV/c}$  (SET+TPC+SIT+VTX)

Solid angle coverage Up to  $\cos\theta \simeq 0.98$  (10 pad rows)

TPC material budget  $\sim 0.04 X_0$  to outer fieldcage in r

$\sim 0.15 {\rm X}_0$  for readout endcaps in z

Number of pads/timebuckets  $\sim 1 \times 10^6/1000$  per endcap

Pad size/no.padrows  $\sim 1 \text{mm} \times 4-6 \text{mm}/\sim 200 \text{ (standard readout)}$

$\sigma_{\text{point}}$  in  $r\phi$  < 100 $\mu$ m (average over L<sub>sensitive</sub>, modulo track  $\phi$  angle)

$\sigma_{\mathrm{point}}$  in rz  $\sim 0.5$  mm (modulo track  $\theta$  angle)

2-hit resolution in  $r\phi$  ~ 2 mm (modulo track angles) 2-hit resolution in rz ~ 6 mm (modulo track angles)

dE/dx resolution  $\sim 5 \%$

Performance > 97% efficiency for TPC only (p<sub>t</sub> > 1GeV/c), and

> 99% all tracking (p<sub>t</sub> > 1 GeV/c) [82]

Background robustness Full efficiency with 1% occupancy,

simulated for example in Fig. 4.3-4(right)

Background safety factor Chamber will be prepared for  $10 \times$  worse backgrounds

at the linear collider start-up

# LP-TPC Endplate

21

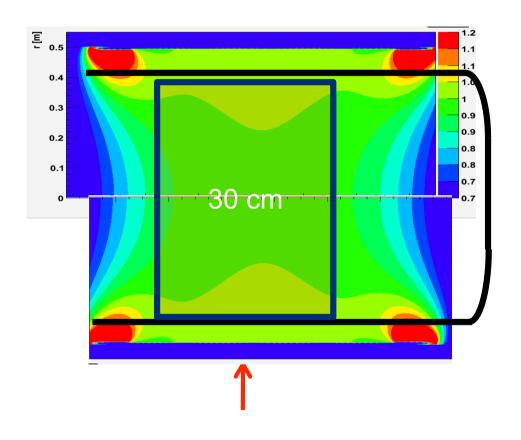

# B field

# Readout Electronics: AFTER

### **AFTER Main Features**

#### Main features:

- Input Current Polarity: positive or negative

- 72 Analog Channels

- 4 Gains: 120fC, 240fC, 360fC & 600fC

- 16 Peaking Time values: (100ns to 2µs)

- 511 analog memory cells / Channel:

Fwrite: 1MHz-50MHz; Fread: 20MHz

- Slow Control

- Power on reset

- Test mode:

calibration or test [channel/channel] functional [72 channels in one step]

Spy mode on channel 1:

CSA, CR or filter out

LCTPC meeting Oct. 10, 2007

E. DELAGNES