# Beam Tests in 2010-2011

A realistic approach?

LC TPC WP meeting mostly dedicated to WP5 discussions

4 March, 2010

Takeshi MATSUDA DESY/FLC

1

# **R&D Phases**

## 1. <u>Demonstration Phase</u>: Small prototype tests still going!

Provide a basic evaluation of the properties of an MPGD TPC and demonstrate that the requirement (1-b,c) can be met using small prototypes.

## 1. Consolidation Phase: LP1: 2007-2010 & LP2 2010 -

Design, build and operate a "Large Prototype" (of large number of measured points) at the EUDET facility in DESY comparing tecnologies and demonstrating (1-a) in a way.

## 1. Design Phase:

Start working on an engineering design for aspects of the TPC at ILC.

(LC TPC collaboration: MOU)

At each phase, we perform beam tests probably with different purposes.

## **Options of MPGD for ILC TPC**

**Based on the studies with small MPGD TPC Prototypes**

<u>Analog TPC</u>: Immediate options for the current ILC schedule (1) Multi layer GEM + Narrow (1mm wide) pad readout: Defocusing by multilayer GEM

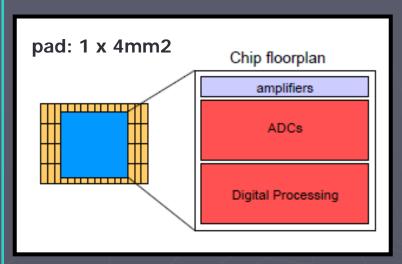

Narrow (1mm) pads  $\rightarrow$  S-ALTRO meets with 4mm\*\*2 pads.

(2) MicroMEGAS + Resistive anode pad

Widening signal by resistive anode

Size of pads (wider → minimum?)

Adopting S-ALTRO

(3) Multilayer GEM + Timepix:

small pixel  $\rightarrow$  need to improve the efficiency for primary electrons larger pixel  $\rightarrow$  more like an analog TPC with much smaller pads

Digital TPC: Still many hardware issues: (4) Ingrid-MicroMEGAS + Timepix: Digital → Free from the gas gain fluctuation More information from primary electrons 30% improvement in position resolution (?) (to be demonstrated)

# **TPC Large Prototype Beam Test (LP1)**

LP1 at DESY T24-1 beam area

# **TPC Large Prototype Tests: LP1**

| 2008:    |                                                                      |

|----------|----------------------------------------------------------------------|

| Nov-Dec  | MicroMEGAS modles w/ resistive anode (T2K electronics)               |

|          |                                                                      |

| 2009:    |                                                                      |

| Feb-Apr  | 3 Asian GEM Modules w/o Gating GEM (3,000ch ALTRO electronics)       |

| Apr      | TDC electronics with an Asian GEM Module                             |

| Apr-May  | Maintenance of PCMAG                                                 |

| May-Jun  | Micromegas w/ two different resistive anodes (New T2K electronics)   |

|          | Setup and test of laser-cathode calibration                          |

| Jun      | GEM+Timepix (Bonn)                                                   |

| Jun      | Installation of PCMAG lifting stage and Si support structure         |

| July     | TDC electronics with an Asian GEM module                             |

|          | ALTRO electronics study w/ an Asian GEM module                       |

| July-Aug | Installation of PCMAG lifting stage                                  |

| Aug      | MicroMegas w/o resistive anode with laser-cathode calibration        |

| Sept     | A Bonn GEM module ( A small aria GEM with ALTRO electronics)         |

| Nov.     | A preliminary test of the silicon emvelope with a MicroMegas module. |

| Dec.     | Test of new MicroMEGAS modules with new reistive anode.              |

# 2010: (see next page)

# TPC Large Prototype Beam Test: LP1 in 2010

"Demonstrate full-volume trucking in non-uniform magnetic field, trying to provide a proof for the momentum resolution at LC TPC"

2010: spring/summer 4 Asian GEM Modules w/ gating GEM (10,000ch ALTRO electronics) DESY GEM modules (w/ gating devices?) (ALTRO electronics) fall /winter 7 MicroMEGAS modules w/ resistive anode (12,000ch T2K electronics)

#### New MicroMEGAS modules in 2010

## Two Other Important R&D Issues in 2010-2012

Advanced endplate:

Requirement: thickness 15% Xo

Thin endplate High density, low power electronics S-ALTRO to match with the small pad size (4mm\*\*2) surfacemounted directly on the back of pad plane of MPGD detector module Power delivery, power pulsing and cooling

Ion Feed back and Ion disks: Gating Device

Ion feed back ration and beam backgrounds

Estimate distortion due to the ion disks (simulation) Options of gating device: Wire gating, GEM gating Methods of calibration

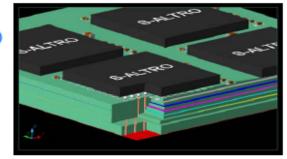

# Advanced Endplate: S-ALTRO LC TPC collbaoration High density, low power , low material electronics for TPC

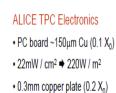

ALICE TPC

Musa / CERN

**S-ALTRO Team**

# The S-ALTRO team at CERN

P. Aspell, H. Franca Santos, E. Garcia, A. Junique, M. Mager, C. Patauner, A. Ur Rehman, L. Musa

ILC (ILD) TPC

## **Advanced Endplate: S-ALTRO**

High density, low power electronics for TPC

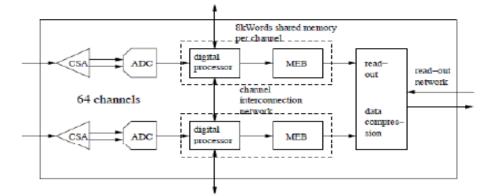

### A multi purpose readout chip for TPC detectors

#### A multi-purpose readout chip for TPC detectors

- 64 complete readout channels (from detector pad to data link)

- programmable charge sensitive amplifier

- sensitivity to a charge in the range ~10<sup>2</sup> ~10<sup>6</sup>

- programmable shaping time in the range 30 to 300ns

#### 10-bit 40 MSPS ADCs

- 8k multi acquisition memory per channel (dynamically allocated)

- digital signal conditioning (4th order IIR filter and FIR filter) for baseline correction

- 3-D zero suppression

- lossless data compression

- readout net work controller

- output bandwidth 160 Mbyte/sec

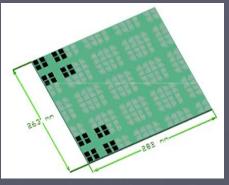

Advanced Endplate: S-ALTRO

Chip size and Power consumption

### Chip size:

(\*estimate) 0.2 mm<sup>2</sup> Shaping amplifier ADC  $0.7 \text{ mm}^2$  (\*) Digital processor 0.6 mm<sup>2</sup> (\*) When 1.5mm<sup>2</sup>/channel 64 ch/chip 🌩 ~ 100 mm<sup>2</sup>

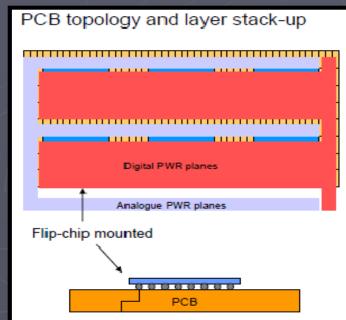

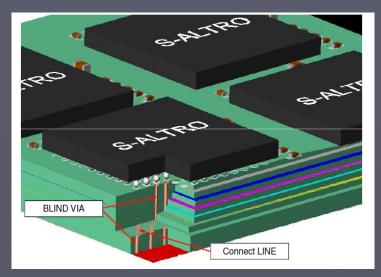

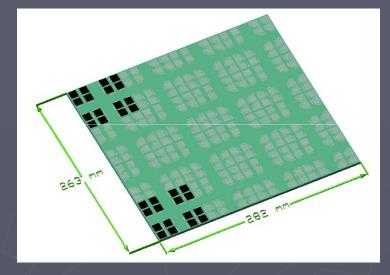

<u>~ 27 x 27 cm<sup>2</sup></u> PCB board ⇒ ~16400 pads or 256 chips/board Bare die flip-chip mounted or chip scale package Minimum-size capacitors (0.6x0.3x0.3mm3) Standard linear voltage regulators Data link based on ALICE SPD GOL MCM

### Power consumption: (\*) 10 -40MHz

Amplifier ADC Digital Proc Power reg. Data links Power reg. eff. Total Duty cycle: Average power

8 mW/channel 12-34 mW/channel (\*) 4 mW/channel 2 mW/channel 2 mW/channel 75% 32-60mW/channel (\*) 1.5% (Electrical duty) 0.5 mW / channel 100 -200W/m2 (\*)

L. Musa

## Advanced Endplate: S-ALTRO Status and Schedule

### Status & Plans

#### Status

- 2006 12-channel prototype of CSA (no programmability)

- 2007 16-channel prototype programmable (1000 chips for LPTPC @ Desy)

- 2009 2-channel ADC prototype (samples expected in June)

- 08/09 specifications digital blocks and design entry (Verilog) of data processor

#### Plans

#### 2009

- characterization of ADC samples (Jul Aug)

- optimization of ADC design or ADC IP (S3) and migration to IBM 130nm

- design of 16-channel of complete readout chain (with simplified digital processor)

#### 2010

- characterization of 16-channel prototype

- decide how to continue the project according to the results achieved

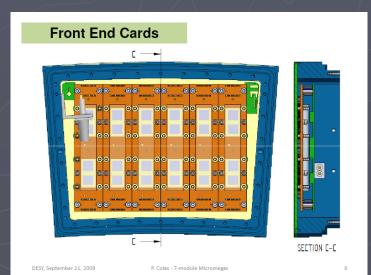

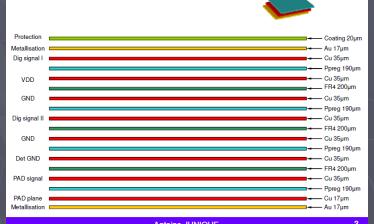

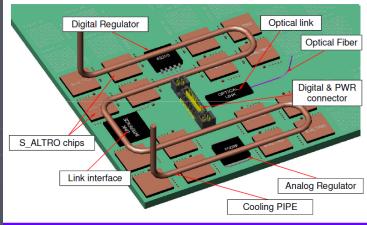

# Advanced Endplate: S-ALTRO Design of Pad Board

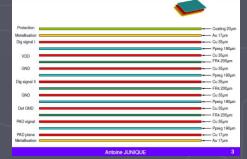

## LAYER STACKUP

18 layer PAD PCB

## **MODULE DETAILS**

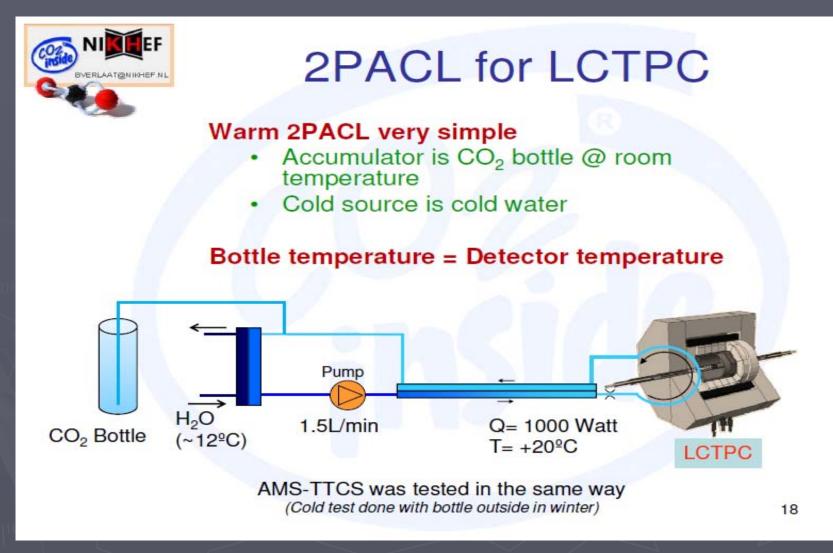

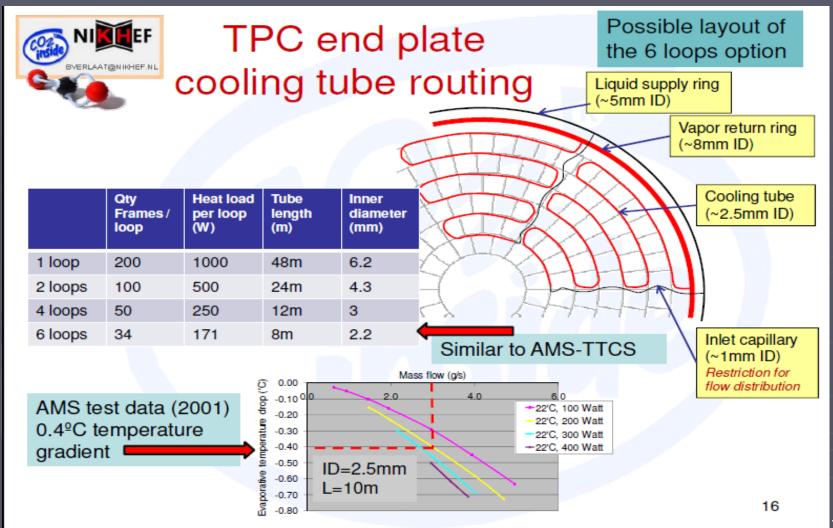

Option of Cooling: <u>2-phase CO2</u> <u>cooling</u>/traditional H2O cooling Advanced Endplate: PCB Test Test with a Pad PCB model

### S-ALTRO Team LC TPC groups

## Test:

Power switching Power delivery Cooling: Thermo-mechanical feature In a high field (DESY 5T magnet, PCMAG, etc.)

## Pad PCB model:

Realistic design of pad PCB with all components 64ch S-ALTROs replaced by proper FPGAs and OP amp/ADC as current load and heat source. Connect pads to the FPGA analog outputs Try cooling by the 2-phase CO2 cooling (AMS and LHCB: Bart Verlaat/Nikhef) Test also digital software model/communication in FPGA Test in high magnetic field

## Schedule: 2010

#### **MODULE DETAILS**

#### LAYER STACKUP

Bart Verlaat/Nikhef

# Advanced Endplate: Cooling Option of the 2-phase CO2 cooling

Applied to AMS and LHCb

#### Bart Verlaat/Nikhef

# Advanced Endplate: Cooling Preliminary Design Consideration for ILC TPC Advantage of thin piping (high pressure)

15

<u>TPC Large Prototype Beam Test (LP2) in 2011-2012</u> Most\_realistic to stay at DESY

2011 Some remaining tests from 2010? Modification of PCMAG (6months) for "Liq. He less" operation (funded by AIDA and else)

2012- Tests of "Advanced Endplate (at least modules)"

Continue testing modules with Time pix with the current LP TPC with PCMAG at DESY

With options of:

Some dedicated tests in a higher magnetic field

Some dedicated tests with a hadron beam

### Because of:

Time/limited Availability of hadron test beam/unclear (in 2011) Funding for moving LP TPC/not foreseen Still possible to measure momentum precisely We do not need the (I)LC time structure of beam for test(?)