# Development of Readout ASIC for FPCCD Vertex Detector

Tomoyuki Saito (Tohoku University)

Y. Sugimoto, A. Miyamoto, Y. Takubo (KEK)H. Ikeda (JAXA), H. Sato (Shinsyu)K. Itagaki, H. Yamamoto (Tohoku)

ALCPG – Linear Collider Workshop of the America 21 March, 2011. Eugene, USA

## Outline

- FPCCD Vertex detector

- Readout ASIC for FPCCD

- Performance of ASIC

- FPCCD readout test

- Second prototype

- Summary

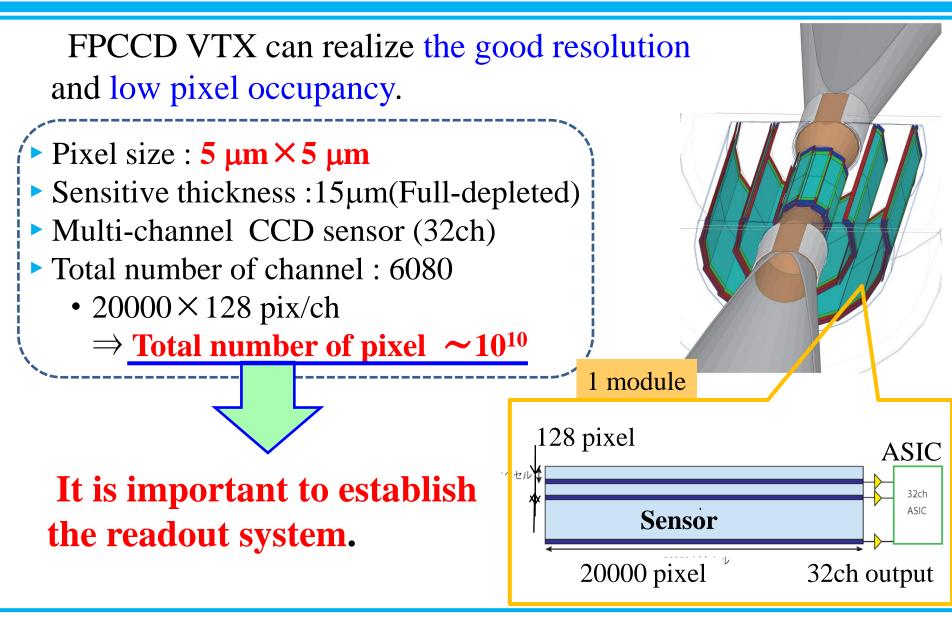

## FPCCD Vertex detector

## Development of Readout ASIC

We have to develop **the multi-channel middle-speed readout** ASIC with **low power consumption**.

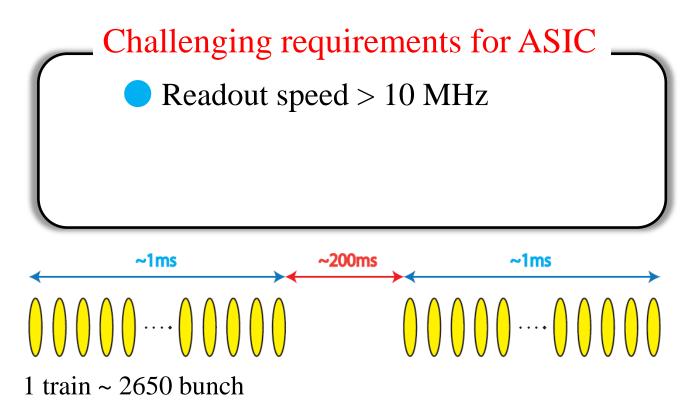

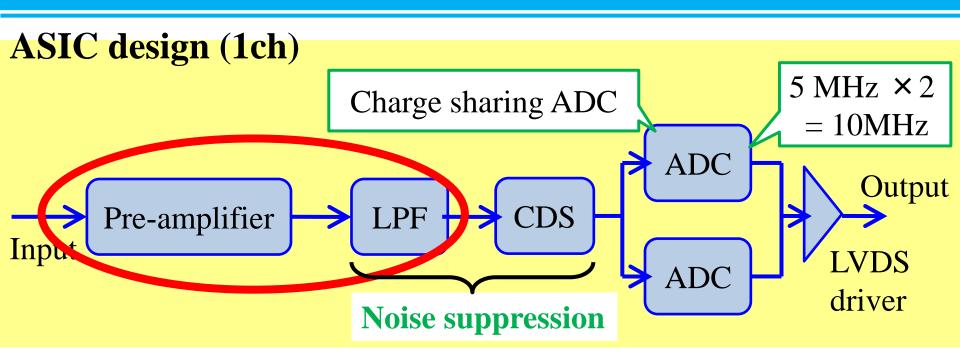

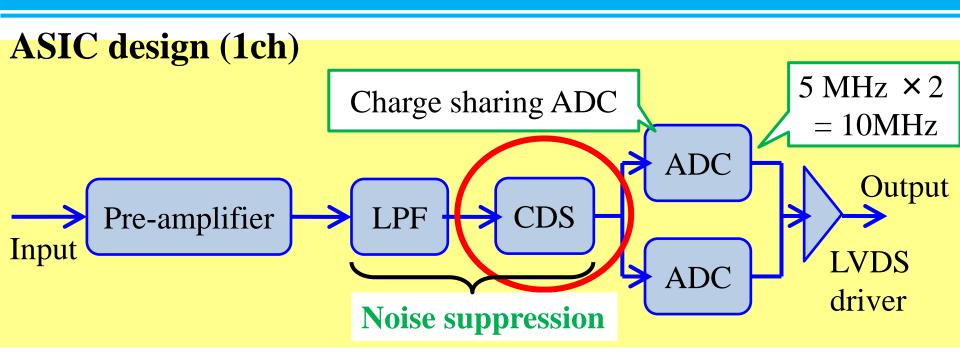

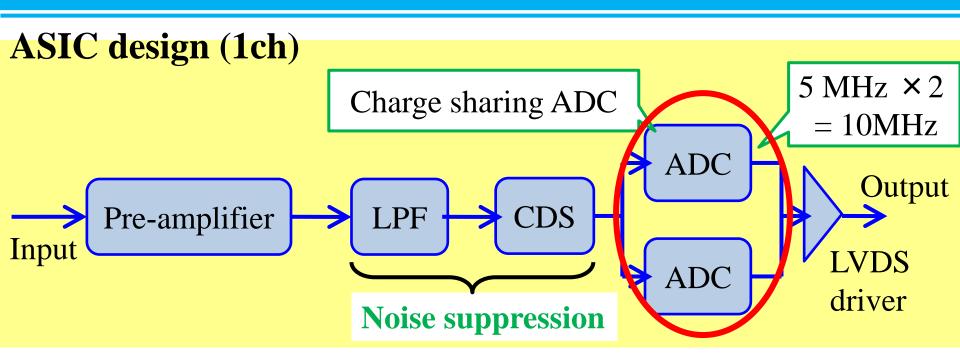

## Development of Readout ASIC

We have to develop **the multi-channel middle-speed readout** ASIC with **low power consumption**.

## Development of Readout ASIC

We have to develop **the multi-channel middle-speed readout** ASIC with **low power consumption**.

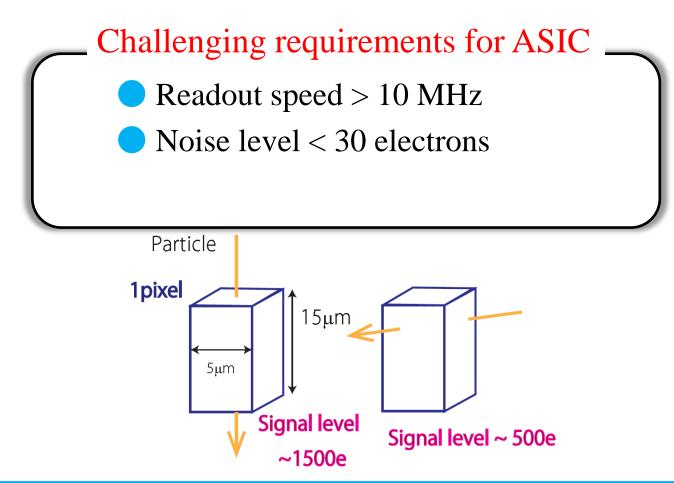

Challenging requirements for ASIC

Readout speed > 10 MHz

Noise level < 30 electron</li>

Power Consumption < 6 mW/ch</li>

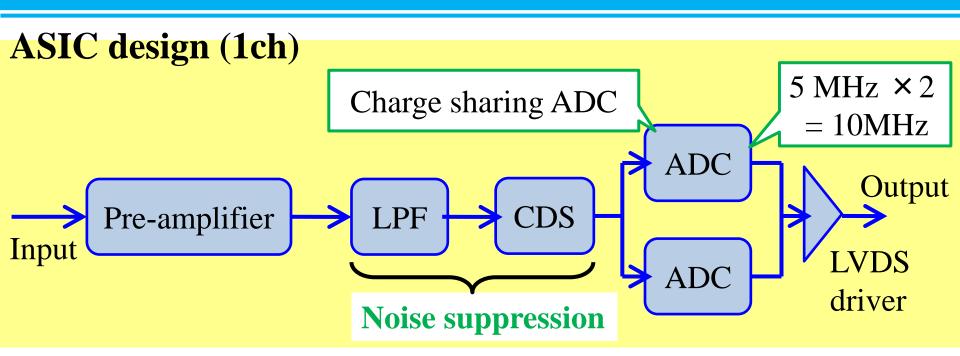

We designed the ASIC satisfied about these requirements.

The parameters of Pre-amplifier and Low-pass filter (LPF) can be set along the command by PC.

- The parameters of Pre-amplifier and Low-pass filter (LPF) can be set along the command by PC.

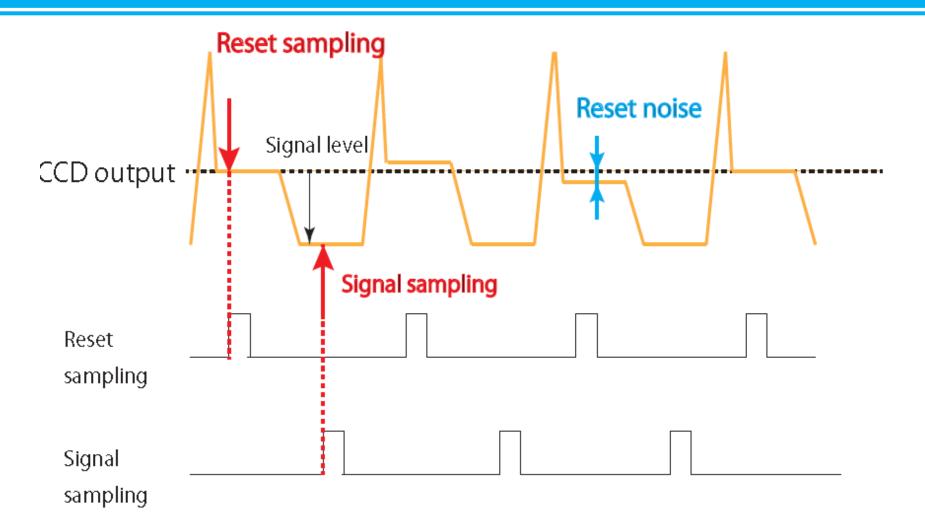

- Correlated Double Sampling (CDS) works effectively to suppress the noise on CCD.

- The parameters of Pre-amplifier and Low-pass filter (LPF) can be set along the command by PC.

- Correlated Double Sampling (CDS) works effectively to suppress the noise on CCD.

- Charge sharing ADC has low power consumption.

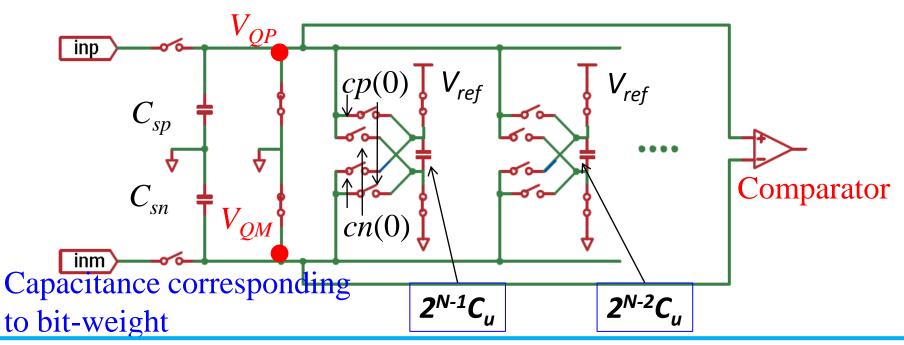

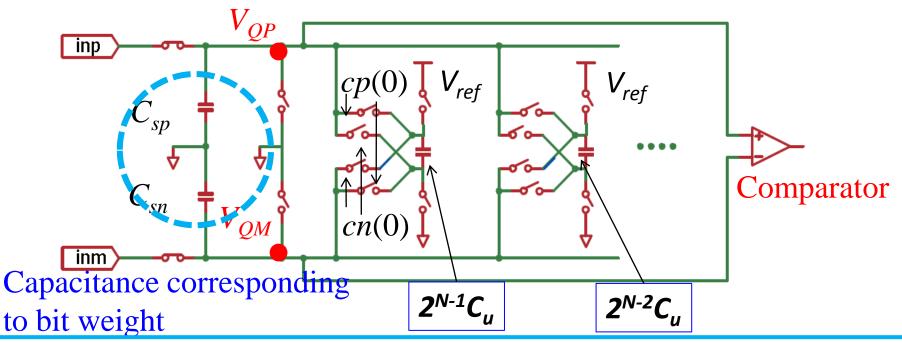

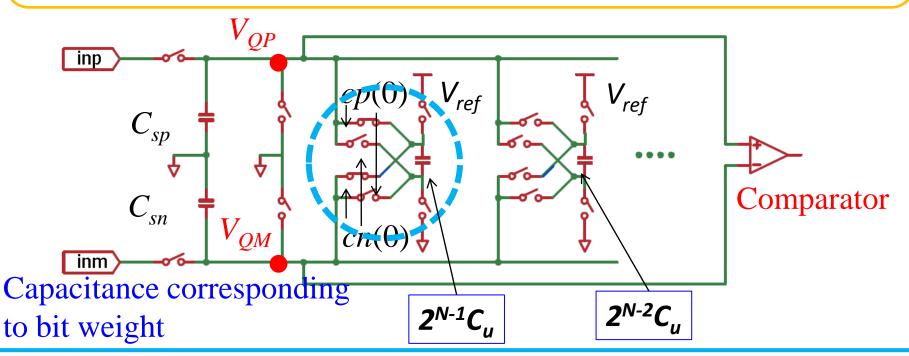

## Charge sharing ADC

Charge sharing ADC: Low power consumption

A/D conversion by the charge operation between capacitance array

Tomoyuki Saito (Tohoku), ALCPG11 @ Oregon Univ.

## Charge sharing ADC

Charge sharing ADC: Low power consumption A/D conversion by the charge operation between capacitance array (1) Input signal is accumulated at  $C_{sp}$  and  $C_{sn}$ , and the comparator compares  $V_{QP}$  and  $V_{QM}$ .  $\rightarrow$  decision on the highest-bit

Tomoyuki Saito (Tohoku), ALCPG11 @ Oregon Univ.

## Charge sharing ADC

Charge sharing ADC: Low power consumption A/D conversion by the charge operation between capacitance array ① Input signal is accumulated at  $C_{sp}$  and  $C_{sn}$ , and the comparator compares  $V_{QP}$  and  $V_{QM}$ .  $\rightarrow$  decision on the highest-bit ② Switch *cp* or *cn* (depend on the result of ①) is connected.  $\rightarrow$  compare  $V_{OP}$  and  $V_{OM} \rightarrow$  decision on second-bit

Tomoyuki Saito (Tohoku), ALCPG11 @ Oregon Univ.

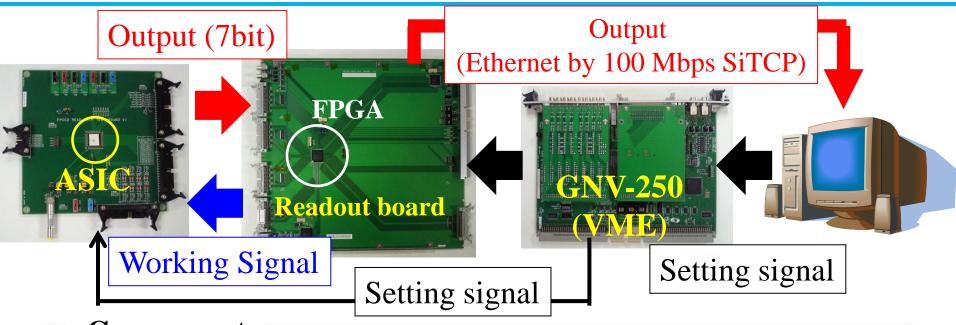

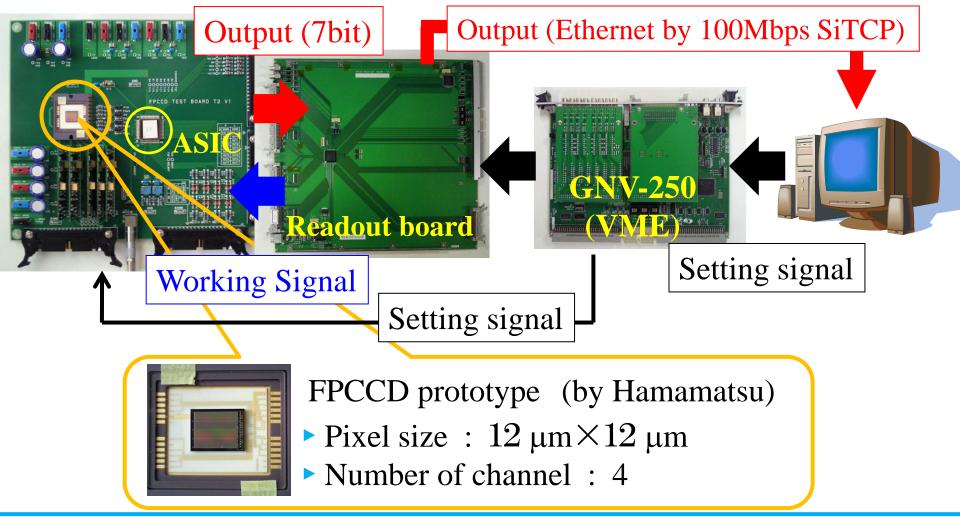

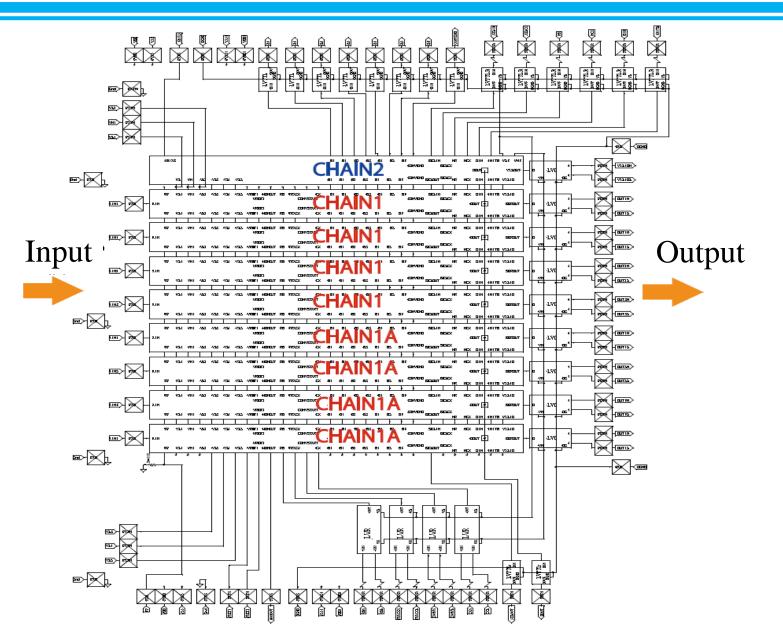

## ASIC readout system

- Component

- **Board for ASIC**

- **Readout board** (equipped for the main FPGA)

- $\rightarrow$  Clock production, Sending the working signal

- **GNV-250 (VME)**  $\rightarrow$  Setting of the parameter (Gain, LPF) ► **PC**

- $\rightarrow$  Software process (DAQ-Middleware)

The performance of ASIC was tested by the developed system.

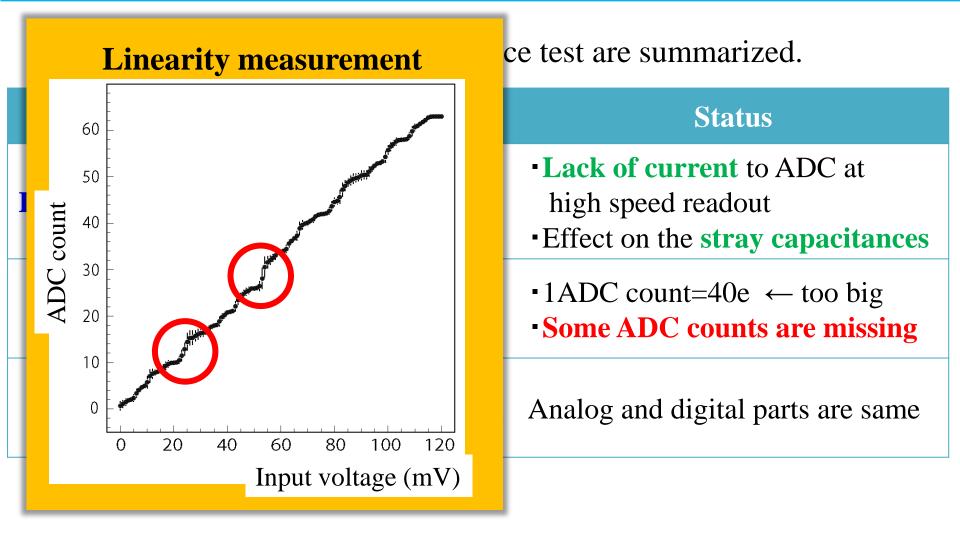

### Performance test of 1st prototype ASIC

#### The results on the performance test are summarized.

|                      | Result                   | Goal    | Status                                                                                                         |

|----------------------|--------------------------|---------|----------------------------------------------------------------------------------------------------------------|

| Readout speed        | 1.5 MHz                  | 10 MHz  | <ul> <li>Lack of current to ADC at<br/>high speed readout</li> <li>Effect on the stray capacitances</li> </ul> |

| Noise level          | 40 e                     | 30 e    | <ul> <li>•1ADC count=40e ← too big</li> <li>• Some ADC counts are missing</li> </ul>                           |

| Power<br>consumption | 13 mW/ch<br>(Simulation) | 6 mW/ch | Analog and digital parts are same                                                                              |

### Performance test of 1st prototype ASIC

## Performance test of 1st prototype ASIC

#### The results on the performance test are summarized.

|                      | Result                   | Goal    | Status                                                                                                         |

|----------------------|--------------------------|---------|----------------------------------------------------------------------------------------------------------------|

| Readout speed        | 1.5 MHz                  | 10 MHz  | <ul> <li>Lack of current to ADC at<br/>high speed readout</li> <li>Effect on the stray capacitances</li> </ul> |

| Noise level          | 40 e                     | 30 e    | <ul> <li>•1ADC count=40e ← too big</li> <li>• Some ADC counts are missing</li> </ul>                           |

| Power<br>consumption | 13 mW/ch<br>(Simulation) | 6 mW/ch | Analog and digital parts are same                                                                              |

#### We have to address these issues in next prototype of ASIC.

### FPCCD readout

## FPCCD readout system

The readout test of FPCCD was performed by the developed system.

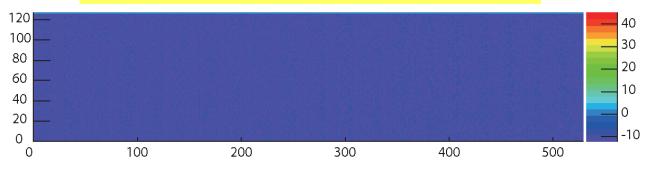

## FPCCD readout test

The signal which was sent from FPCCD to the PC is investigates.

Pedestal distribution (ADC count)

#### ⇒ Uniform distribution

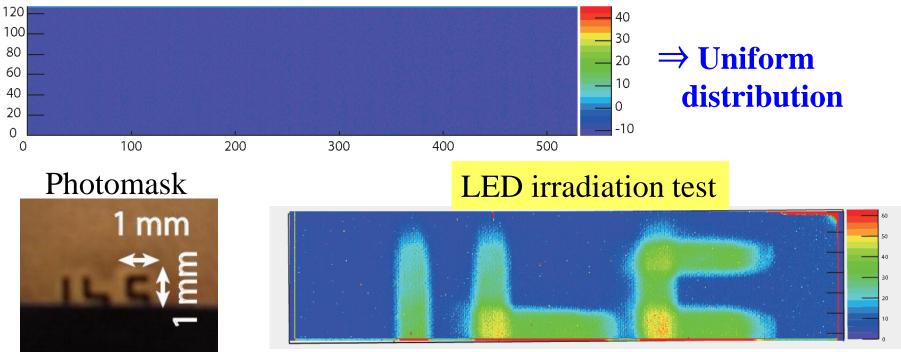

## FPCCD readout test

The signal which was sent from FPCCD to the PC is investigates.

#### Pedestal distribution (ADC count)

#### **Success in reading "ILC"**

The developed readout system works normally.

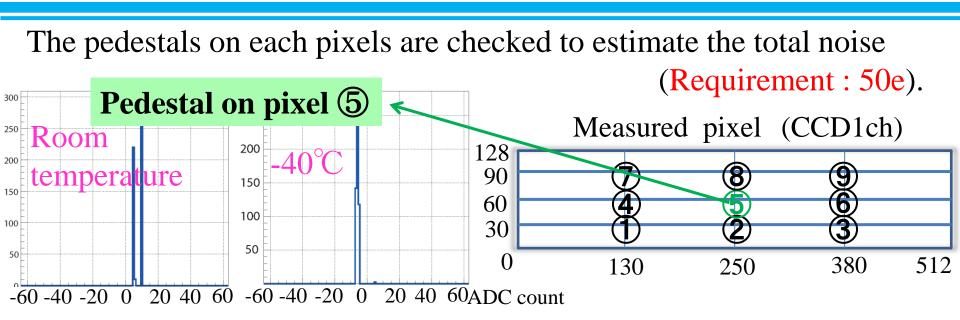

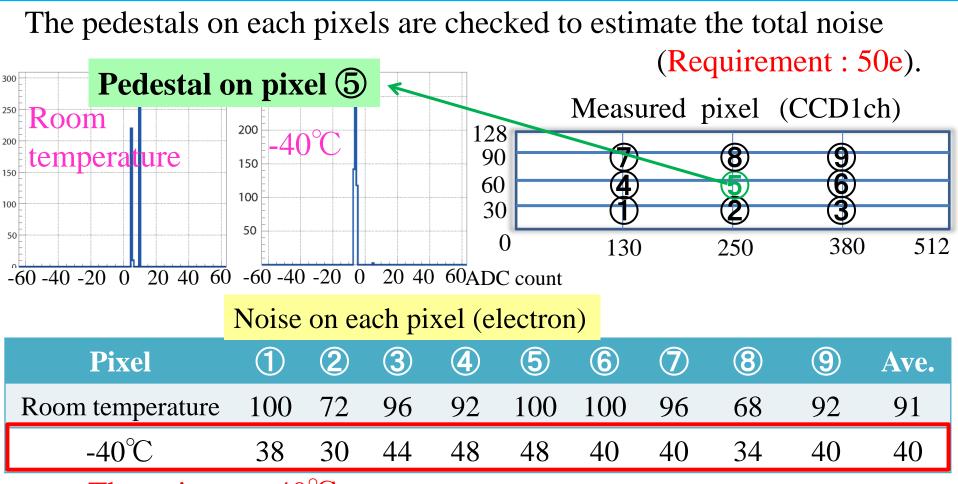

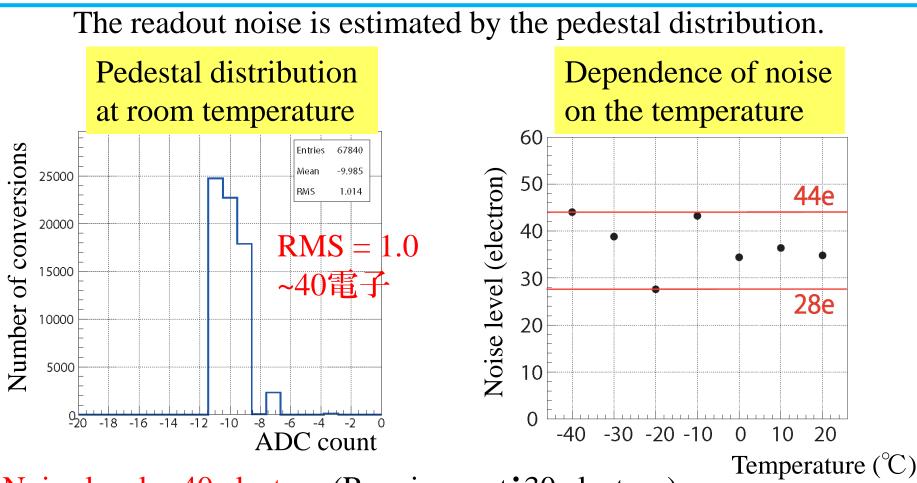

### Readout noise on total system

### Readout noise on total system

- The noises at  $-40^{\circ}$ C

- equal to that of only ASIC.

- are satisfied with the requirement (50 electrons).

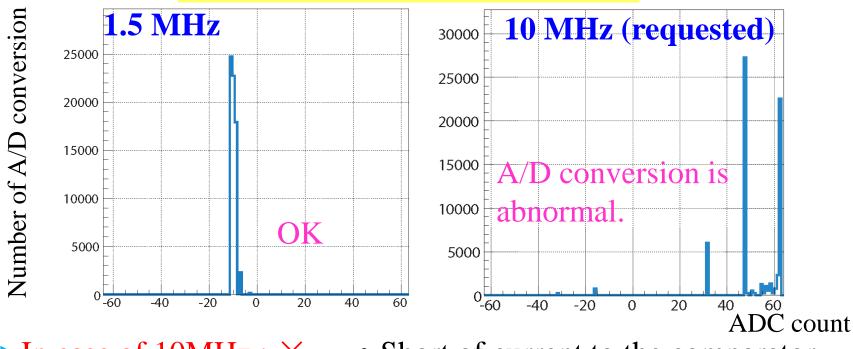

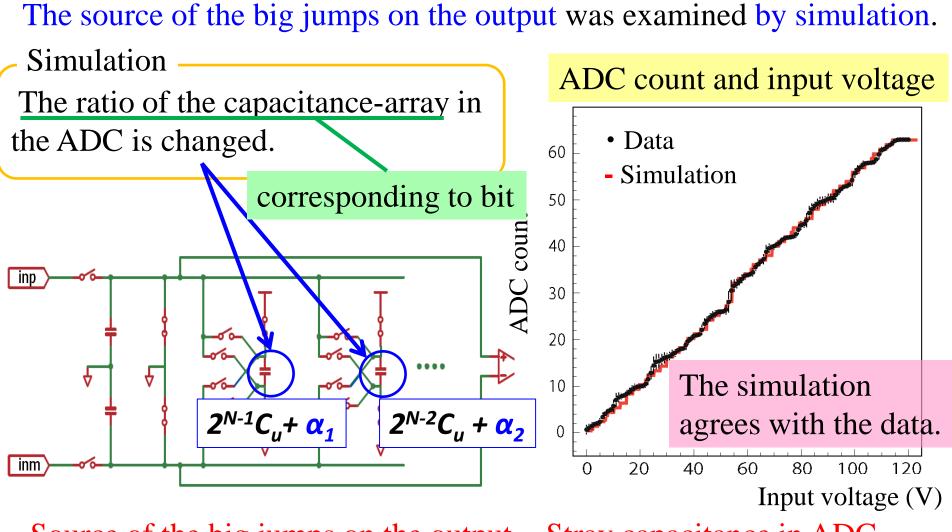

#### **Problems on the 1st prototype ASIC**

- ① Slow readout speed

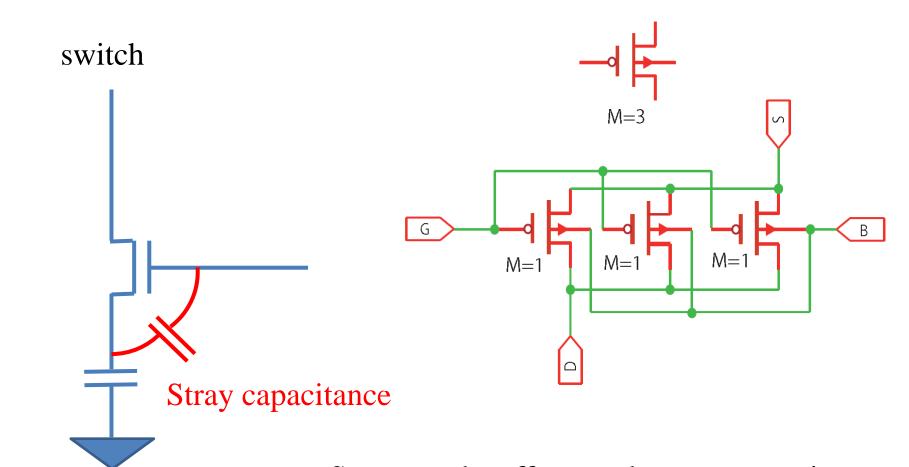

- 2 Big jumps on ADC count output by the stray capacitances

- 3 Large power consumption

Goal: 10 MHz readout speed and solution to ADC count jumps

Goal: 10 MHz readout speed and solution to ADC count jumps

**Main modification**

Readout speed : The number of pins is increased,  $80 \rightarrow 100$ .

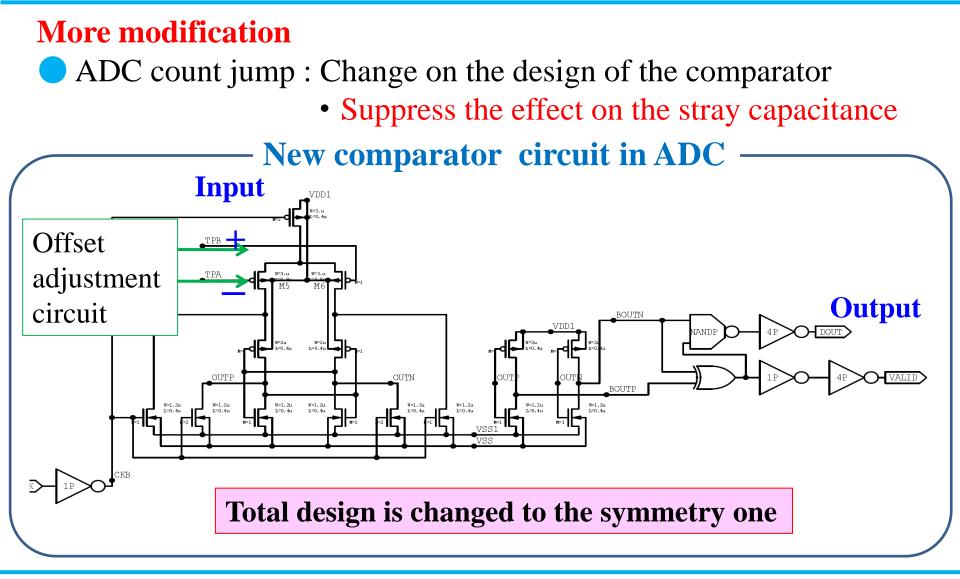

Goal: 10 MHz readout speed and solution to ADC count jumps

- **Main modification**

- Readout speed : The number of pins is increased,  $80 \rightarrow 100$ .

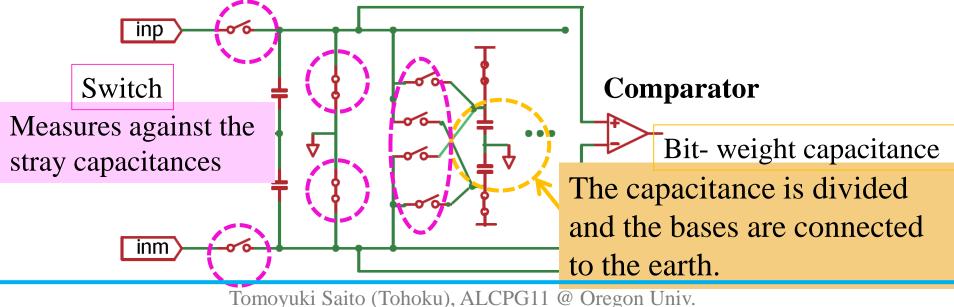

- Some jumps of ADC counts

- Addition the offset adjustment circuit to the comparator.

#### Goal: 10 MHz readout speed and solution to ADC count jumps

#### **Main modification**

- Readout speed : The number of pins is increased,  $80 \rightarrow 100$ .

- Some jumps of ADC counts

- Addition the offset adjustment circuit to the comparator.

- Change of the ADC design for the suppression of the effect on the stray capacitance

Tomoyuki Saito (Tohoku), ALCPG11 @ Oregon Univ.

4300

4300

and the spectrum and the second second second

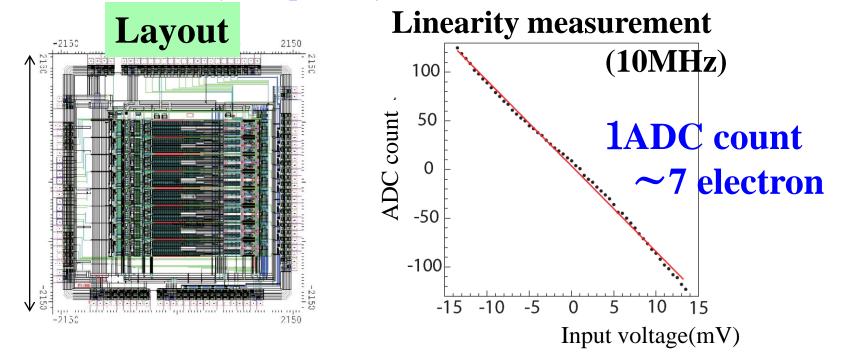

## Development of 2nd ASIC (2)

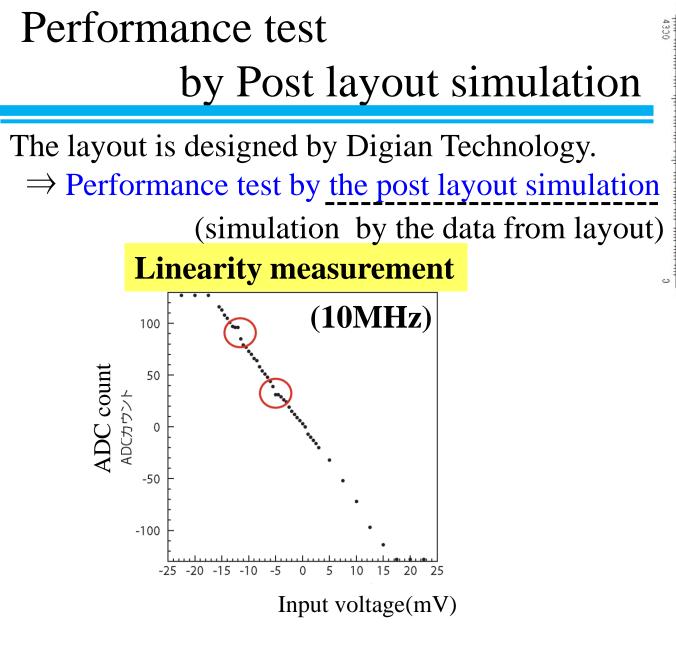

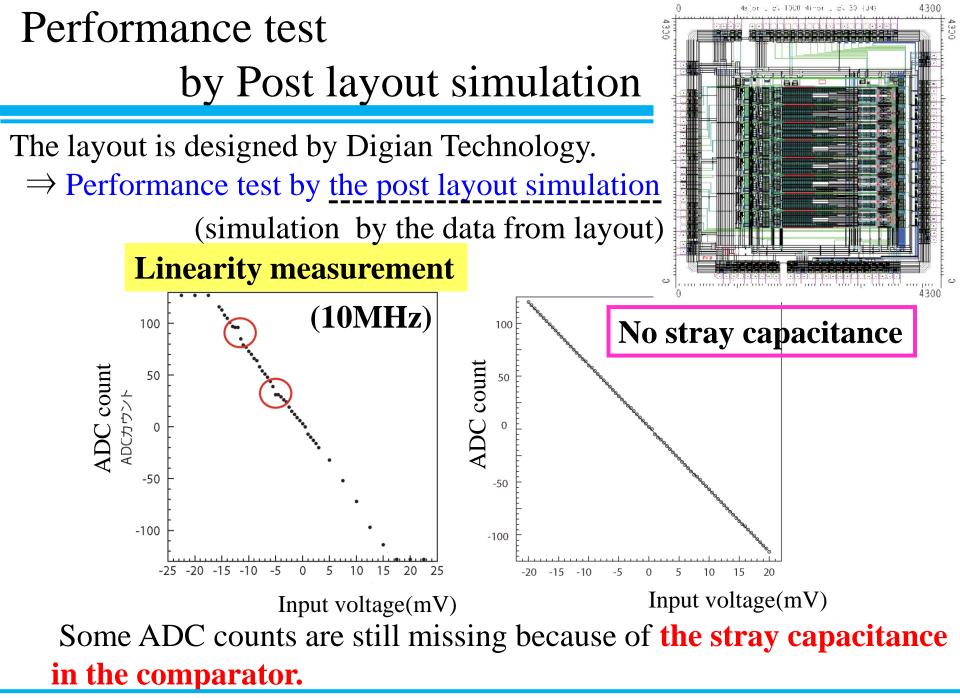

### Performance test 2 by Post layout simulation

The layout added more changes was also designed by Digian Technology.  $\Rightarrow$  Performance test by the post layout simulation

The design of the second ASIC works normally at 10 MHz

The 2nd prototype ASIC arrived at the end of Feb.

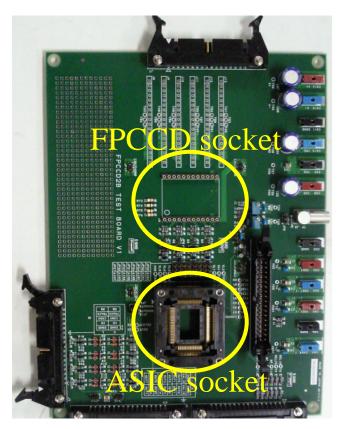

# 2nd prototype of ASIC

#### • 2nd prototype ASIC

- Produced by TSMC

- Process : 0.35µm CMOS

- Number of channel : 8

Chip area size : 4.3 mm × 4.3 mm

#### 2nd prototype ASIC packaged

#### Test board for 2nd prototype

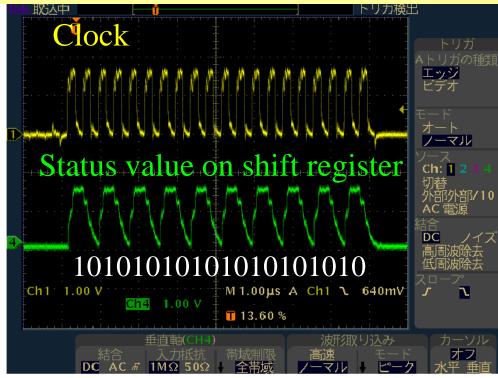

## Parameter setting

The behaviors of the shift registers for setting the parameter (gain, filter, offset) are investigated.

Behavior of the shift register in the case that "101010..." is written

The output corresponds with the command.

#### The parameter is set correctly by order of the PC.

## Summary and Plan

The 2nd prototype was developed to solve the problems on 1st ASIC. **Second prototype of ASIC**

- can be satisfied with the requirements on the readout speed and noise level in the post layout simulation.

- Power consumption [Simulation] : 27 mW/ch

(requirement: 6 mW/ch)

- We received at the end of Feb. and has been tested the performance.

- Parameter set  $\rightarrow$  OK

- ADC check.

- Readout test with  $6 \mu m \times 6 \mu m FPCCD$

Thickness

## Back up

### ASIC

# Correlated Double Sampling (CDS)

The noise can be suppressed by sampling the difference between the reset and signal level

### Measures against stray capacitance in switch

Suppress the effect on the stray capacitance By tuning the M value which is corresponded to bit-weighted

# 1st prototype of ASIC

#### - 1st prototype ASIC

- Layout by Digian technology

- Produced by TSMC

- Process : 0.35µm CMOS

- Number of channel : 8

- ▶ Size : 2.85 mm × 2.85 mm

#### Packaged ASIC

#### **ASIC Layout** -15001500 Major tick=1000 Minor tick=50 .500 .500 -1500-1500 -15001500

## Performance check ~Readout speed~

The readout speed was checked by the pedestal distributions

Pedestal distribution (ADC count)

▶ In case of  $10MHz : \times \rightarrow \bullet$  Short of current to the comparator

• Stray capacitance

► Upper limit on readout speed ~ 1.5 MHz From now on, readout speed = 1.5 MHz

## Performance check ~Readout noise~

- Noise level = 40 electron (Requirement: 30 electron)

- 1ADC count = 40 electron  $\rightarrow$  Bad resolution to estimate the noise

- ► Small dependence on temperature (Cryostat : -50°C)

# Performance check ~Linearity~

Source of the big jumps on the output = Stray capacitance in ADC