# JRA3 DAQ Task Status report

**Vincent Boudry** Matthew Wing

EUDET Final Annual meeting DESY, 30/09/2010

# DAQ Task goal

- "Generic" DAQ based AMAP on commercial boards

- Extensible for Large Detectors

- Provide the **digital** readout of CALICE embedded front end (ROC\* chips)

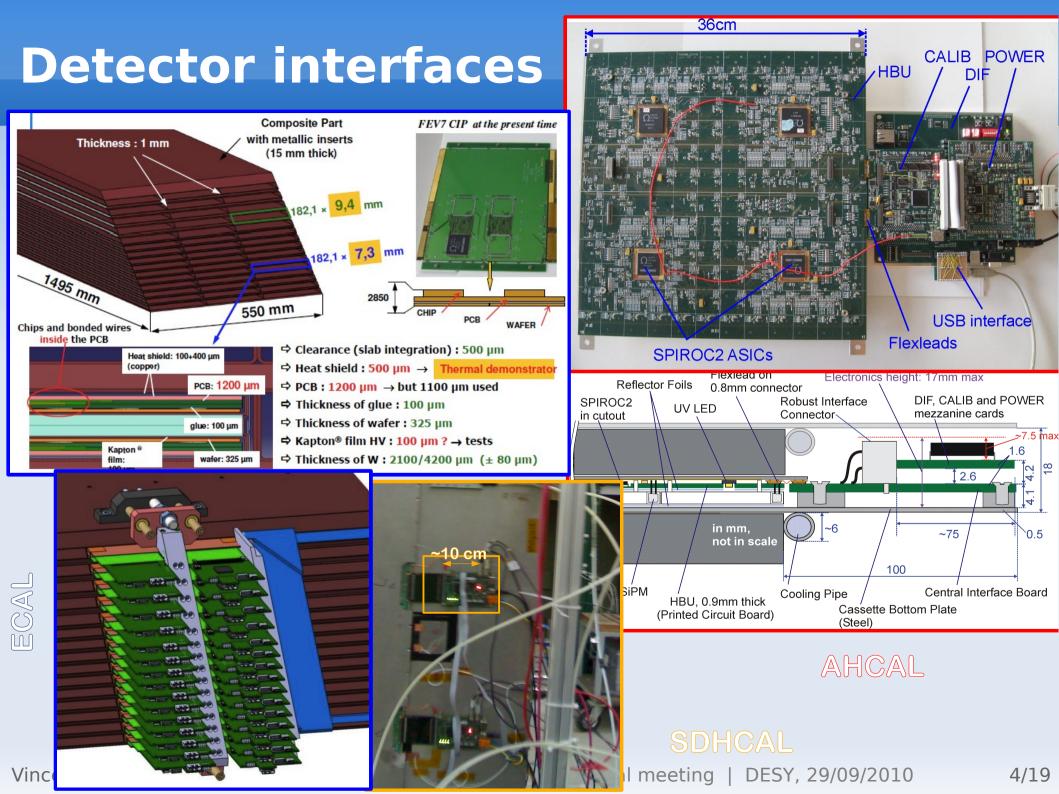

- All calorimeters seen through standard Detector InterFace board (DIF)

- Pass configuration; fast commands; clocks;

- Receives Data; Busy

- 1 (opt. 2) Concentrator cards level

- ▶ 1 Clock and Control Card (CCC) for the fast signal distribution and collection

- Advanced Off-detector receiver (FPGA based event builder)

- All signals on 1 cables; add-hoc communication protocol

- 8b/10b coding

- 3 CALICE prototypes en route:

- ► SDHCAL : ~400.000 ch; digital  $\rightarrow$  2b/ch,

- ▶ ECAL : ~22.000 ch; Energy,

- ► AHCAL : ~52.000 ch: Energy & time

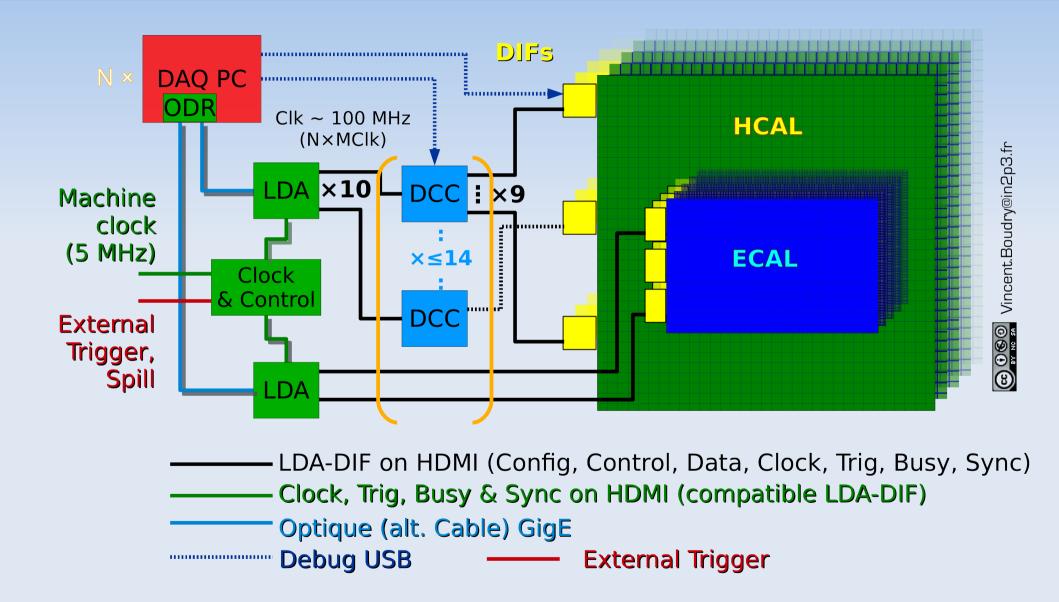

# **CALICE DAQ2 scheme**

#### CCC

- Overall status unchanged for a while

- Full complement of 10 boards with power supplies

- One in LLR and two in LAPP

Recent work :

- CCC link to LDA has been done

- Board designed at UCL and built at Cambridge

- Produced 25 boards (one for each LDA), tested and ready for use (summer students)

- Capacitor changed on CCC; supplied with wrong value (summer students)

- CCC + add-on in use (supplying a clock) in system tests

- Was used as DIF-Master (dev<sup>t</sup> of LAPP) in beam test:

- Sending hard-coded Fast Commands & signals to DIF directly

- DIF readout done by USB

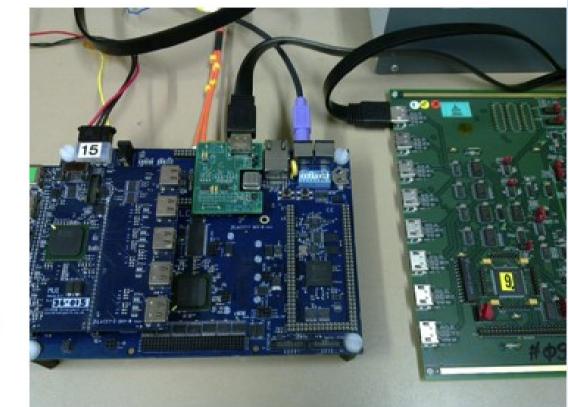

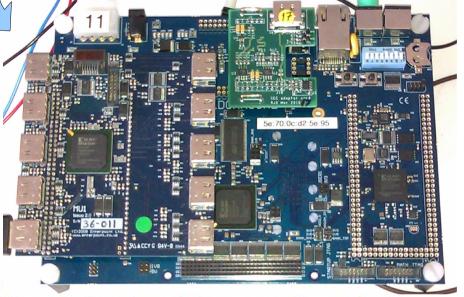

#### LDA

- The LDA (from Enterpoint) consists of :

- Mulldonoch2 baseboard;

- add-on HDMI board to connect to 10 DIFs;

- an add-on ethernet board to connect to an ODR;

- a CCC add-on board.

# Requires add-hoc protection (contrains, chocs, physicists)

Hardware status—recall all three (Enterpoint) boards had problems and needed redesign :

another came along with the production run; some HDMI connectors broke or broke the cable. Care needed on (un-)plugging; ease is cable dependent;

- SAMTEC admitted fault in their connectors; 8 boards with manufacturer for repair;

- decided to get a few more spares ...

- added termination resistors on all HDMI boards at UCL (improves signalling and reduces FPGA power)

- all boards apart from those in repair at UCL

#### **REM: "Happy end" of a long saga**

#### **Beam InterFace card**

#### **Basis**:

- CALICE chips use auto-trigger

- Readout can be triggered by single event using external trigger (e.g. beam hodoscope)

- $\rightarrow$  "Single event" mode

- History of Chip is usable (e.g. in case of selective ext. trigger)

- Readout triggered by environmental internal or extern trigger

- Chip full

- ILC-like mode (end-of-spill)

- Require some device to radout the beam line parameters

- Scintillators; Cherenkov PM (coding of CEDAR bits)

- ► Time of event (⊃ rec for wire chambers) within a 5 MHZ clock period

#### Implementation

- 2 solutions

- Add-hoc card for interfaces with a CALICE ROC (SPIROC ?) + 1 DIF

- Small adaption (buffers) card on a DIF + "simulation" of a digital ROC in the FPGA

- Part of the coding can be "tricky"

- Both offer full compatibility with CALICE DIF for the DAQv2.

- To be implemented for 2<sup>nd</sup> version of CALICE beam test

- One of the task of AIDA (WP8.6.2)

- ► For "standalone" CALICE tests

- ▶ Functionnalities  $\supset$  in JRA1 TLU

#### **HW status**

- DIFs

- ECAL DIF ready and working; 22 ready; mat for 40 in total (CAM)

- ► **DHCAL** DIF: **165**/170 cards tested & **ready** (LAPP)

- ▶ **AHCAL** DIF: proto exist, **in design**, prod in NIU  $\rightarrow$  4 unit

- CCC: 10 cards ready; 4 in use in 4 labs; 3 more shipped → LLR

- DCC: 3 prototypes ready; 2 prod cards being tested (✓) → 20 end of october

- LDA: 25 main board scheduled (½ done; ½ to be done)

- ► 5 v1 + 15 v2 Ethernet mezzanine : ✓

- ▶ 6 CCC mezzanine ✓

- ▶ 20 HDMI Mezzanine: faulty connectors on 8  $\rightarrow$  in repair

- ODR + PC

- ▶ 8 ODR ready ; network card being used instead (debugging, ease of use)

- ▶ 6 PC available: 1 in LLR ; 3 other ready; OS needs to be upgraded

- BIF: none (to be developped in AIDA)

#### ~ No more basic problem with HW Reliability of HDMI connectors mechanics ?

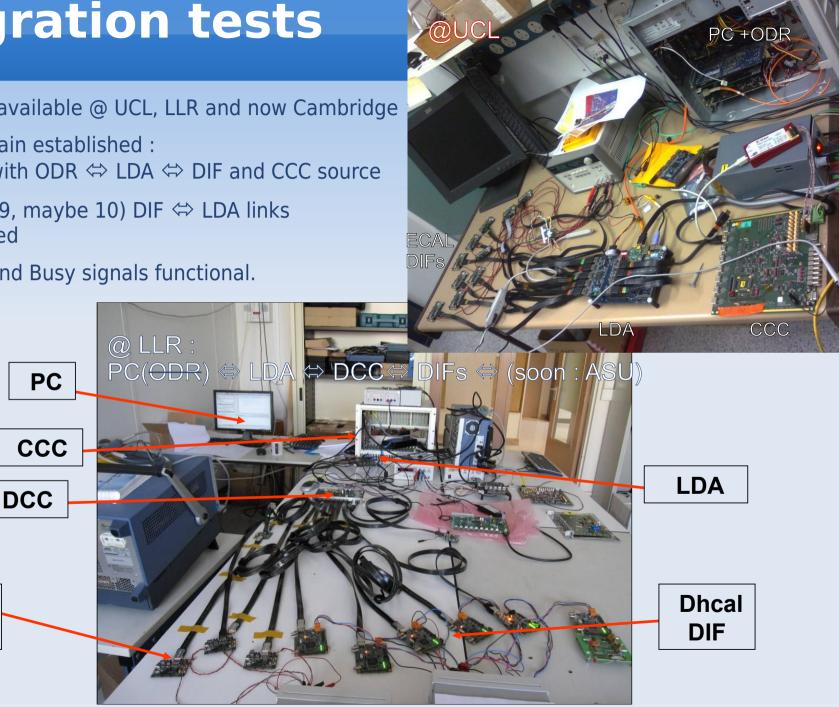

# Integration tests

- Systems available @ UCL, LLR and now Cambridge

- Whole chain established : DAO PC with ODR  $\Leftrightarrow$  LDA  $\Leftrightarrow$  DIF and CCC source

- Multiple (9, maybe 10) DIF  $\Leftrightarrow$  LDA links established

- FastTrig and Busy signals functional.

**Ecal**

DIF

9/19

# **Python Test toolkit**

- Interactive hardware test software (GUI)

- ► Each HW test easily scriptable: simple user-friendly python API: each function defined ↔ 1 graphical pane with "Run" button

- Intensively used by Franck/Remi

- Available to anyone working with USB/RS/Ethernet devices

- C libraries implementing the complete DIF Task force protocole

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | File Edit Options Buffers Tools Python Help                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Messages DA_version GULDS<br>Send FCD CC reset send FC DCC get status<br>Send FCD CC 7(20)<br>Wessages Send FCD CC 7(20)<br>Send FCD CC 7(20)<br>Wessages Send FCD CC 7(20)<br>Send FCD CC 7(20)<br>Wessages Send FCD CC 7(20)<br>Send FCD CC 7(20 | Initial       Send a biock transfer command       Diff Unit with whole DC register page 14a out link [0x3]         GULD IF & DIF _ Command       Data       < | <pre>def send FC_DCC get status(INT0x lda out mask = 0x8):     """Send FCMD K28.3/D15.0 (aka. 7C/D15.0, DCC get status) and     print out the whole DCC register page"""     comma = commons.encode_8b10b_kd(28, 3)     data = commons.encode_8b10b_kd(15, 0)     ans = LDA.do lda_send_fastcmd(INT0x lda out_mask, comma, data)     calicediag.GUI.set_statusbar_message("Get_Status FCMD sent")     return _unpack_DCC_get_status_page(ans[16:]) is not False     '-: DCC.py</pre> |

https://svn.in2p3.fr/calice/online-sw/trunk/pyserdiag/

### **Reliability tests**

#### Stress tests using pseudo-random generator

- $9 \times \text{DIF} \rightarrow 1 \times \text{DCC} \rightarrow 1 \times \text{LDA} \rightarrow \text{PC}$

- 4 DIFs generate pseudo random data

- Results

- ▶ Direction DIF → LDA  $\checkmark$

- ► Maximum DCC  $\rightarrow$  LDA link occupancy (40Mbps)  $\checkmark$

- Up to 5.6 TB transferred (2 weeks), no error

#### End-to-end test: FIFO write/read

- PC  $\leftrightarrow$  1×LDA  $\leftrightarrow$  1×DCC  $\leftrightarrow$  1×DIF

- Tests both fast-commands and block transfer "read" requests

- Results:

- ► PC ↔ LDA Ethernet OK with built-in delais (1 ms)

- fixed 2 wks ago for Block transfer (Config), still issues when interleaving Fast Commands

- Still to be fixed Buffer overflow on non-connected links

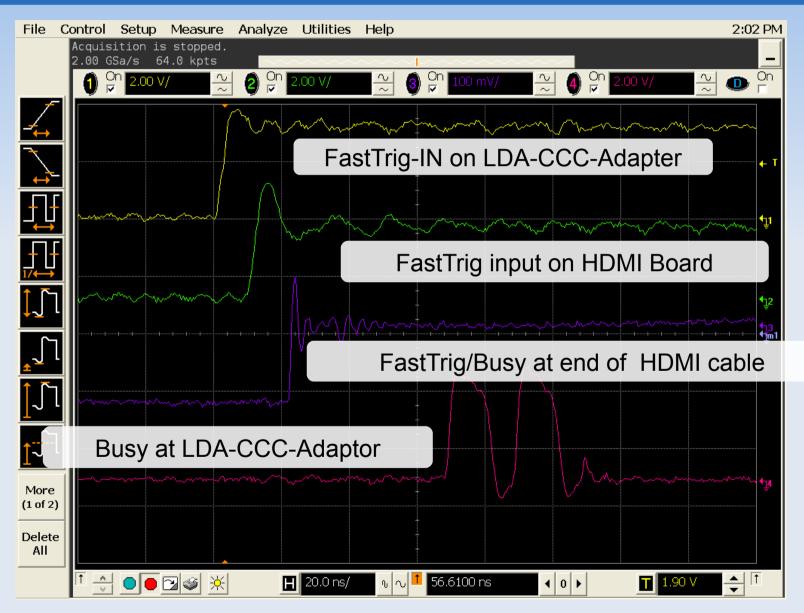

# CCC←→LDA Fast signals tests (from 29/09/2010 15:45!)

### FW status

LDA+CCC comm

| uch delay due to cut<br>nginneer in 2009 | ay due to cut and leave from key<br>er in 2009 Reuse MUX from DCC [?] |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|------------------------------------------|-----------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                          | LDA                                                                   | DCC /           | DIF's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Ethernet                                 | ✓ at full speed                                                       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| CCC                                      | Clk; Trig; Busy                                                       | Clk; Trig; Busy | Clk; Trig; Busy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Nlinks up<br>(                           | 9/10 conn.<br>no MUX                                                  | 9               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Fast Commands                            | <u>ا</u>                                                              | <b>v</b>        | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Block transfert                          | 1                                                                     | 1               | <ul> <li>Image: A set of the set of the</li></ul> |  |  |

| Data <sup>1)</sup>                       | ✔ (< 50 MHz)                                                          | ✔ (< 50 MHz)    | ✓ (<50 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| ROC                                      |                                                                       |                 | Structure ✓<br>Adapt SDHCAL USB<br>Code on going                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

FW have been advancing rather fast during the last 3 months

Generic code for all DIFs

Many progresses recently End of October for first full minimal usable chain?

### Performances

- Rather low demanding in term of bandwidth

- ▶ SDHCAL : ~ 20MB/s in Spill

- ► ECAL: ~100MB/s

- ► AHCAL: ~ 300 MB/s

- Data limited by ASICs readout

- Some code (System C, by D. Decotigny) exists for simulation of full chain

- Many other studies...

|                |                       |                      | DAQ                    | /2 data flux        |                     |                          |                      |

|----------------|-----------------------|----------------------|------------------------|---------------------|---------------------|--------------------------|----------------------|

| N DIF/LDA      | N DIF/DCC             | [MHz]                | LDA-DIF FLUX<br>[MB/s] | [MHz]               | LDA FLUX<br>[MB/s]  |                          | [MB/s]               |

| 1(             | )                     | <mark>9</mark> 50    | 6.25                   | 5 <mark>1000</mark> | 125                 | 1000                     | 170                  |

|                |                       | 7                    |                        | ASIC Dclk           |                     | 1                        |                      |

| Detector       | DHCAL                 | Evt Size             | Mem Size               | ASIC DCIK<br>[MHz]  | ASIC FLUX<br>[MB/s] |                          | from LC-DET-2004-02  |

|                |                       | 20 B                 | 128                    | 2.5                 | 0.31                |                          |                      |

| Mode           | Calib/Noise<br>Single | Calib/noise<br>Burst | TB<br>Single           | TB<br>Burst         | Demo                | Occupancy<br>100 GeV π i |                      |

| N ASIC/DIF     |                       | 8 48                 |                        |                     | 4.8                 | Mean                     |                      |

| σ (NASIC)      |                       | <b>0</b> C           | 2.6                    | 3 2.6               | 2.6                 | sigma                    |                      |

| Touched DIF/pl | e                     | 3 3                  | 1                      | I 1                 | 1                   | +3⊄ /√Mem                | Size                 |

| ASIC           | 20                    | B 2 560 B            | 20 E                   | 2 560 B             | 2 560 B             |                          |                      |

| R/O time 1     |                       |                      |                        |                     |                     |                          |                      |

| R/O time ALL   | <b>3 072</b> μ        | s 393 216 µ s        | s 307µs                | s 39 322 µ s        | ; 39 322 µ́s        |                          | Parameters codes     |

| DIF            | 960                   | B 122 880 B          | 96 E                   | 3 12 288 B          | 12 288 B            |                          | Hardware (~fixed)    |

| R/O time       | e 154 µ               | s 19661µs            | s 15µs                 | s 1966µs            | s 1966µs            | 1                        | DAQ (achievable)     |

|                | 0.000                 | D 4000 000 D         |                        | 10.000 5            | 10.000 5            |                          | Physics (occupancies |

| LDA w/o DCC    | 9 600                 |                      |                        |                     |                     |                          |                      |

| R/O time       | e 77 µ                | s 9,830 µ s          | s 3µs                  | s 328µs             | s 328µs             |                          |                      |

| DCC            | 8,640                 | B 1,105,920 B        | 288 E                  | 36,864 B            | 36,864 B            |                          |                      |

| R/O time       | e 1382 µ              | s 176947µs           | s 46µs                 | s 5898µs            | s 5898µs            |                          |                      |

| LDA w/ DCC     | 86,400                | , ,                  | ,                      | ,                   |                     |                          |                      |

| R/O time       | e 691 µ               | s 88 474 µ s         | s 23 µ s               | s 2949µs            | s 2949µs            |                          |                      |

| ODR            | 172.800               | B 22,118,400 B       | 5,760 E                | 3 737.280 B         | 737.280 B           | I                        |                      |

| 1000MB/s       |                       | , .,                 |                        |                     |                     |                          |                      |

| Disk           | 172,800               | B 22,118,400 B       | 5,760 E                | 3 737,280 B         | 737,280 B           | 1                        |                      |

| 170MB/s        | s 1016µ               | s 130108µs           | s 34 µ s               | s 4337µs            | s 4337µs            |                          |                      |

| Max R/O time   | <b>3 072</b> μ        | s 393 216 µ s        | а <b>307</b> µs        | s 39 322 µ s        | ; 39 322 µ s        |                          |                      |

| Min Freq       | 0.33 kH               | z 0.00 kHz           | 3.26 kHz               | 2 0.03 kHz          | -                   |                          |                      |

| Min. evts Freq |                       | 0.33 kHz             | ,                      | 3.26 kHz            | : 3.26 kHz          |                          |                      |

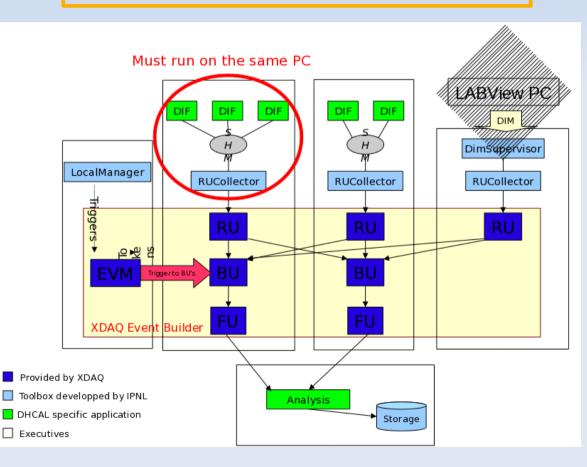

# Software: XDAQ framework

- dev<sup>ts</sup> started @IPNL for electronics test using XDAQ in 2008

- Ch. Combaret

- Gained (a lot of) impulsion with involvment of L. Mirabito (resp. of DAQ SW for CMS tracker)

- Ran for ≥ 1 year in TB, Cosmics & Electronics test

- USB readout

- Interface to old LabView program

- Recent development

- Writing of LCIO data in RAW format

- versatile online analysis framework (root histos)

- → Marlin Based

- XDAQ vs DOOCS vs TANGO vs …

- Some developpements done in DOOCS

- lacks of manpower & expertise

- "killed" in the transition region

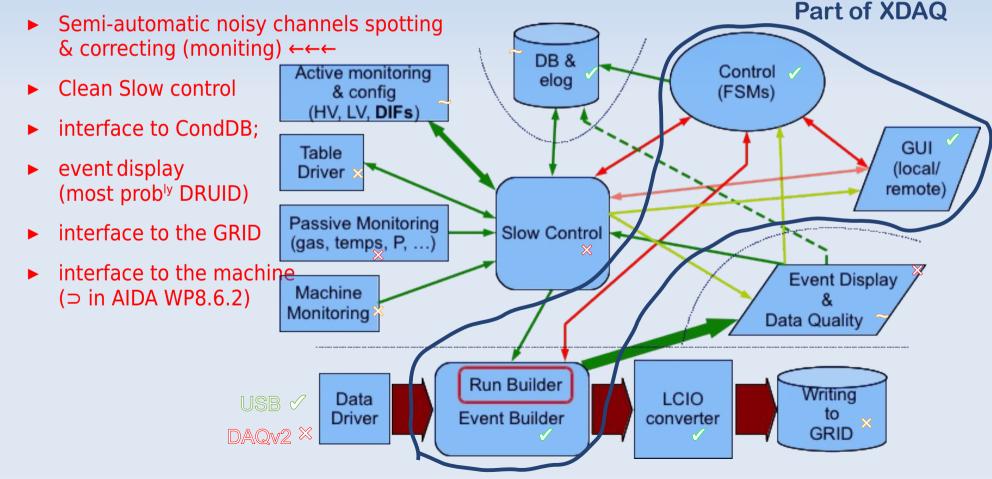

#### **SW** status

- Missing critical elements

- Configuration DB (being worked on)

- ► DAQ2 interface  $\leftarrow \rightarrow$  XDAQ being worked on

- Missing utilities

#### Documentation

- EUDET Memos's

- Most of Code, Manual and HW description is available on CALICE twiki: https://twiki.cern.ch/twiki/bin/view/CALICE/CALICEDAQ

- Some part's of FW is still scattered on various SVN servers

### Delivery

- HW ready to be delivered to labs

- CCC already in use in 4 labs

- Wait another 1.5–2 months for v0 of complete FW and SW integration

- ▶ Preparatory work on specific FW and SW can already start (≤1 month)

### Installation

- mechanics

- mod. VME crate for

- DCC

- CCC

- Special box for LDA

- Support for cables

- Final set-up not yet known:

- stand alone SDHCAL

- stand alone ECAL

- Stand alone AHCAL

- Combined test

- $\rightarrow$  5 m long HDMI cables

- halogen free;

# Conclusions

- Technological prototypes of CALICE are getting close

- ► All use 2<sup>nd</sup> version of ROC chips

- Being integrated in large prototypes  $\rightarrow$  extensive TB in 2011

- 1 m<sup>3</sup> SDHCAL in Spring; some ECAL slabs in cosmics & beam; some AHCAL slab in beam.

Big effort for CALICE!!

- The DAQ will be ready for TB

- All HW elements available

- ► FW & SW almost ready

- ► SW: XDAQ survived natural selection ( $\leftarrow \rightarrow$  DOOCS)

- Combined (with other system)  $\geq$  2012

- Prepare HW and SW beforehand

- ◆ SW & HW ←→ TLU & EUDAQ first

Big effort for CALICE!! ~15++ individuals from: • UK: CAM, MAN, UCL,

- RHUL, Imperial

- FR: LLR, LAPP, IPNL

- DE: DESY