# DCDC converters for the upgrade of the LHC experiments

F.Faccio, S.Michelis, G.Blanchot, C.Fuentes, B.Allongue - CERN/PH dept.

http://cern.ch/project-dcdc

# Motivation for the development of radiation and magnetic field tolerant DCDC converters

What are the components of a full DCDC converter? Do we have them all by now?

In summary, what can a DCDC converter bring to a detector system

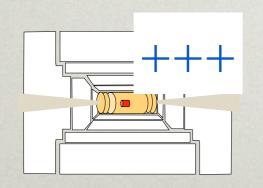

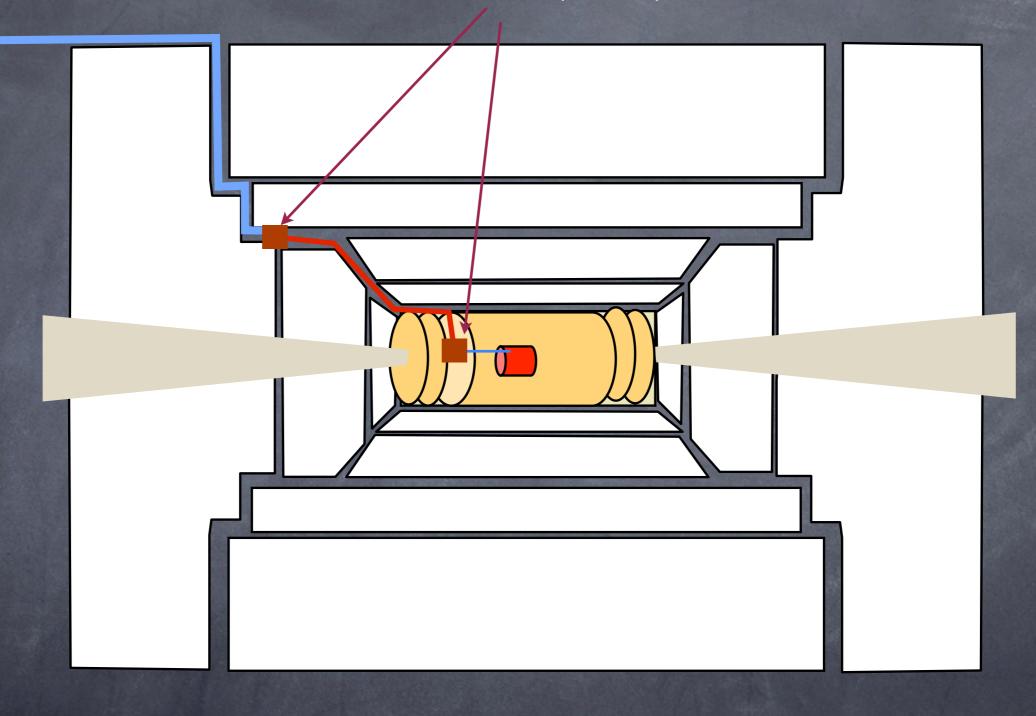

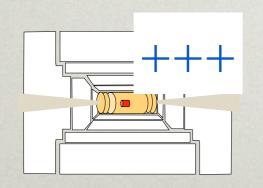

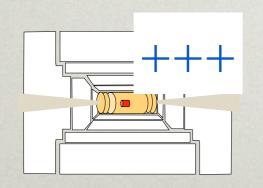

Conceptual representation of the power distribution system typically used in the LHC experiments

Power loss in cables: PLoss=Rcable I<sup>2</sup>

Power loss in cables: PLoss=Rcable I<sup>2</sup>

The electronics load (the FE boards) needs power at a precise voltage  $P_{Load}=V_{Load}I_{Load}$

Power loss in cables: PLoss=Rcable I2

The electronics load (the FE boards) needs power at a precise voltage  $P_{Load}=V_{Load}I_{Load}$

$$P_{in}=V_{in}I_{cable} \longrightarrow iConv \longrightarrow P_{out}=V_{Load}I_{Load}$$

iConv is magic because Pin=Pout Therefore if Vin>VLoad, Icable>ILoad

Waiting for the iConv, a DCDC converter can do the job with the drawback of some power loss

Waiting for the iConv, a DCDC converter can do the job with the drawback of some power loss

... but some 'magic' is still required: the DCDC needs to function in the radiation and magnetic field of the experiments

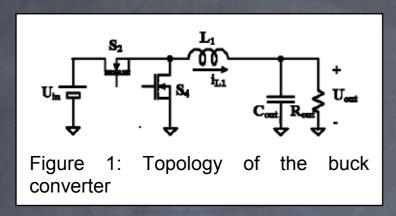

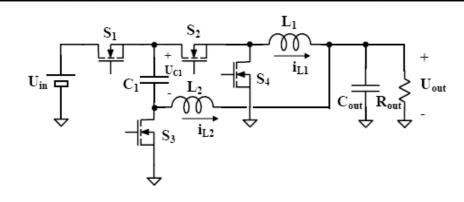

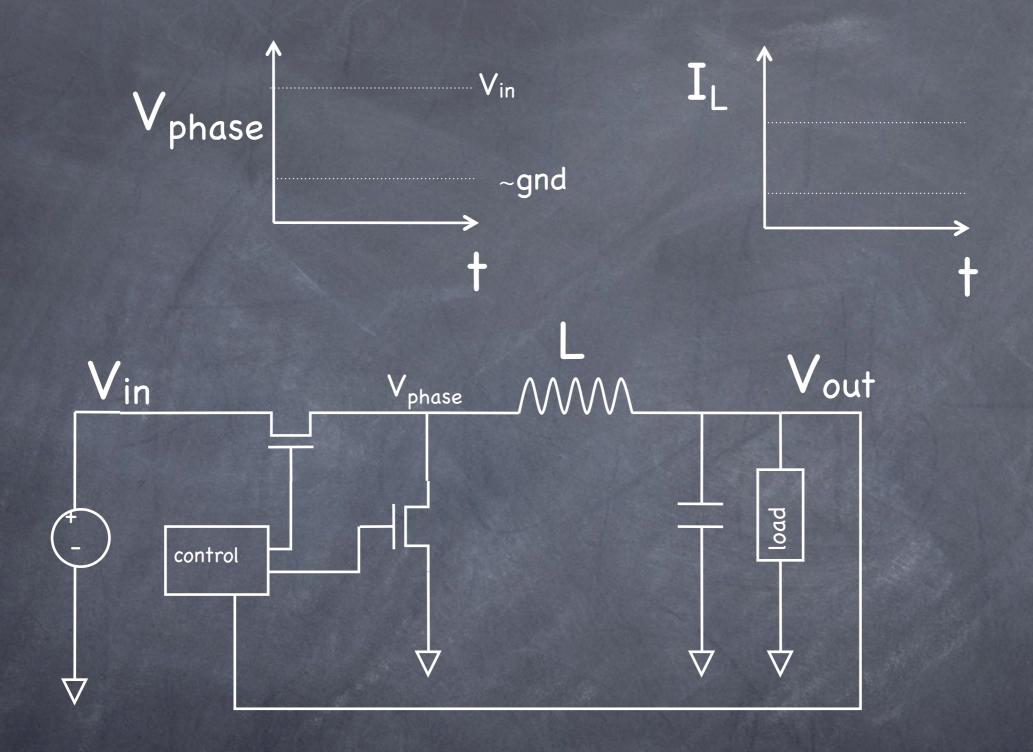

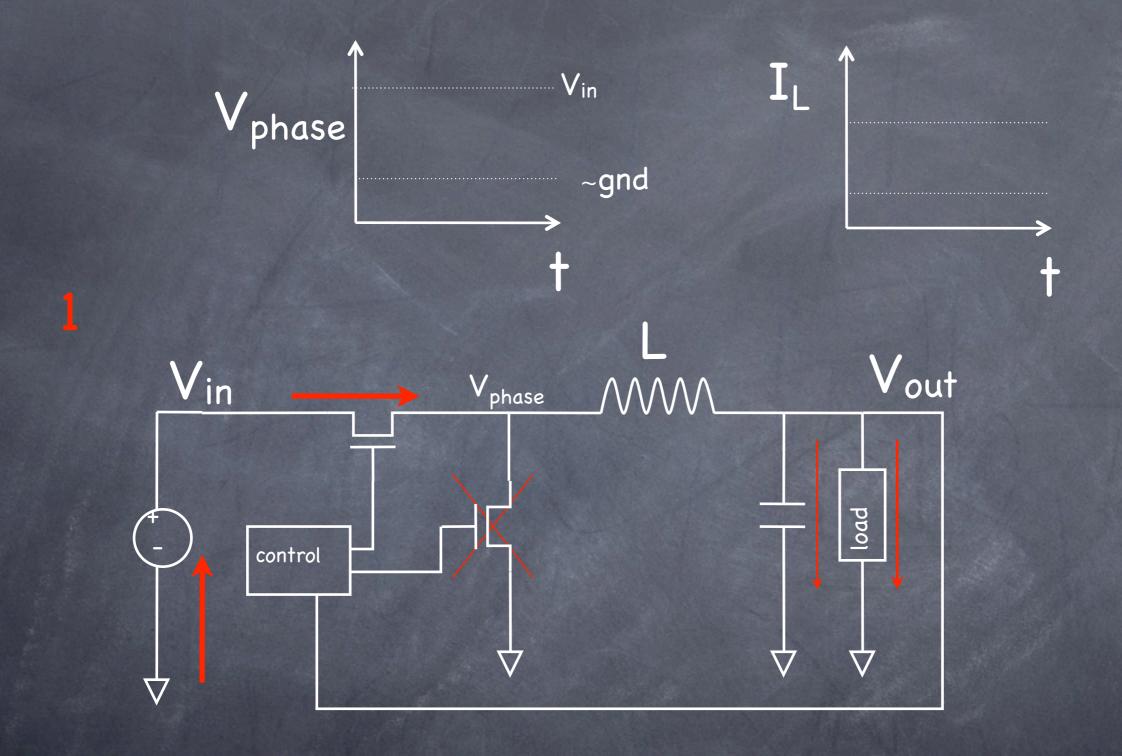

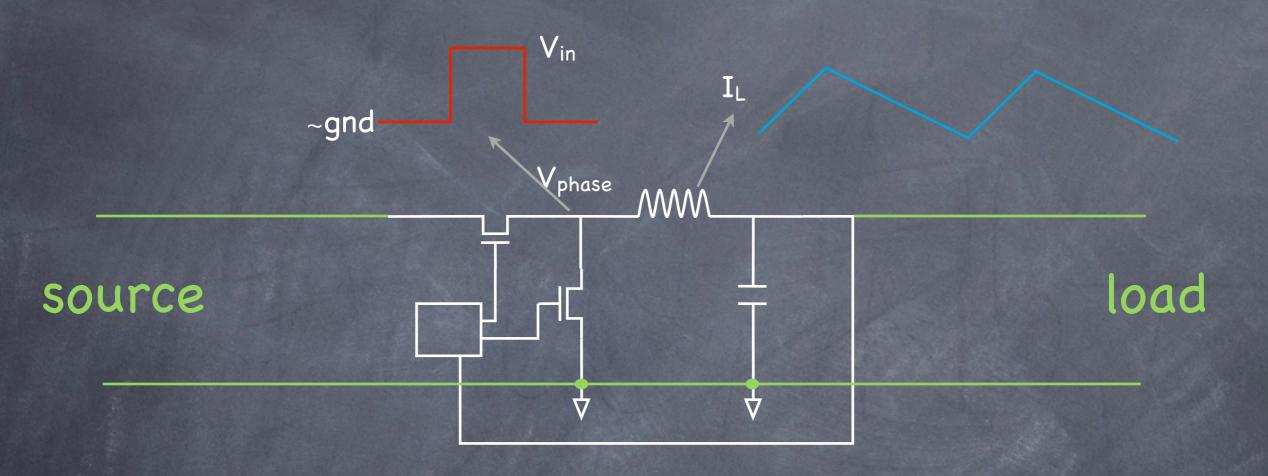

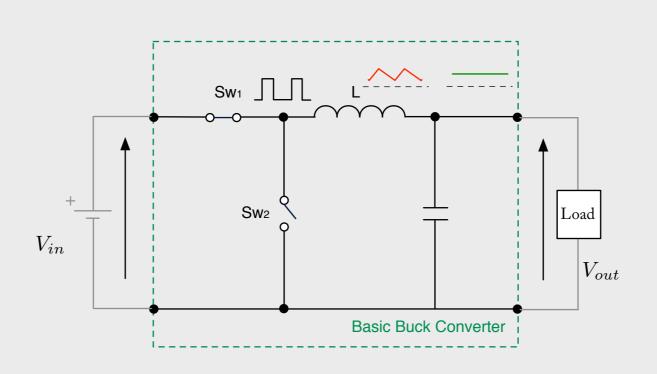

Figure 3: Topology of the two phase interleaved buck with integral voltage divider

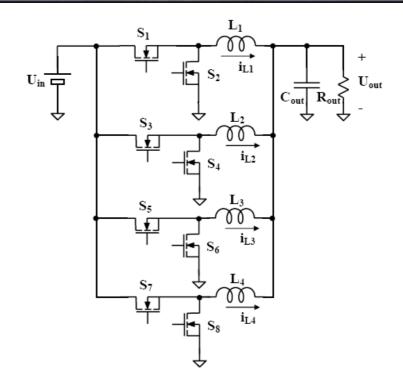

Figure 2: Topology of the 4-phase interleaved buck converter

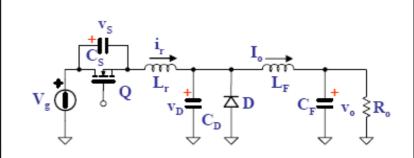

Figure 4: Topology of a multi-resonant buck converter

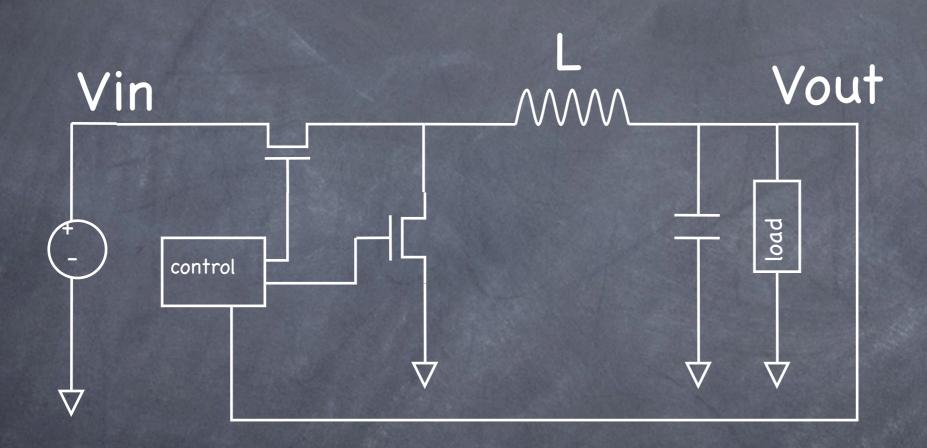

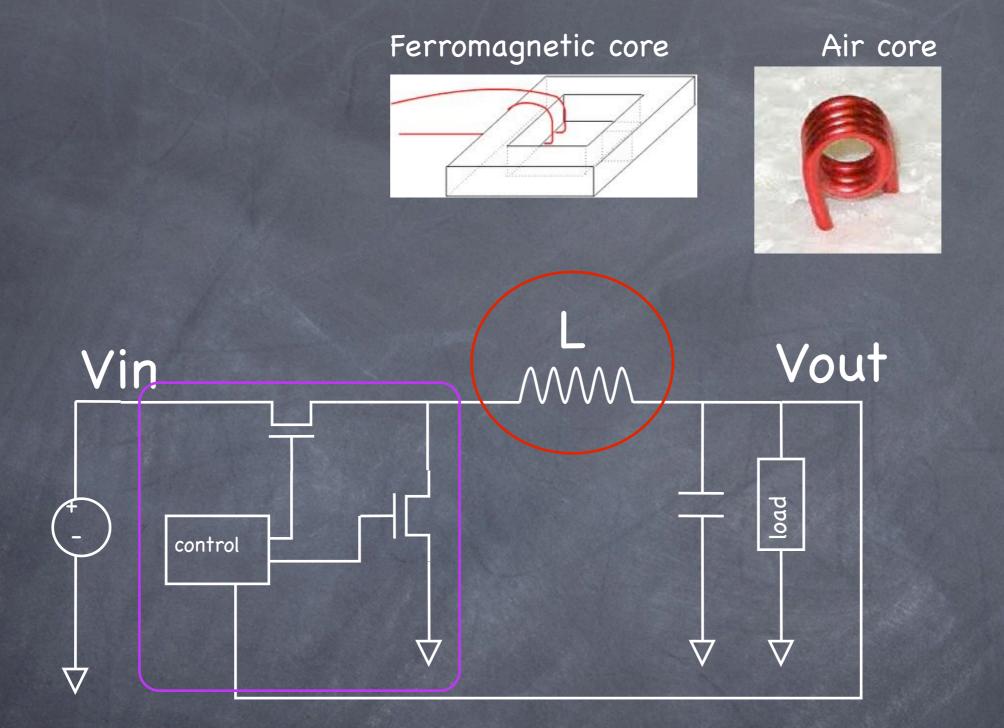

Ferromagnetic core Air core Vout Vin Mload control  $\Diamond$

Qualification required for radiation effects: TID, displacement damage, SEEs

#### Electrical specs

| Input voltage  | 10-12V                            |

|----------------|-----------------------------------|

| Output voltage | 1.2-3.3V                          |

| Output current | up to 3A*                         |

| Efficiency     | >80% (for V <sub>out</sub> =2.5V) |

Conducted and radiated noise compatible with installation in close proximity to FE electronics and detectors

#### Mechanical specs

Small size (footprint, height)

Small contribution to material budget

Connectable to cooling system

#### Environmental specs

| TID tolerance              | 250 Mrad                                                                                                  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Displacement damage        | 2.5·10¹⁵ n/cm² (1MeV equivalent)                                                                          |  |  |

| SEE                        | Absence of destructive SEEs and Vout transients when tested with heavy ions up to an LET of 30 MeVcm²mg-1 |  |  |

| Magnetic field             | 4 T                                                                                                       |  |  |

| Temperature of cooling pad | -30 to +10 °C                                                                                             |  |  |

<sup>\*</sup> We will know the real output current limit soon, with measurements of a mature ASIC in a realistic configuration (cooling)

# Motivation for the development of radiation and magnetic field tolerant DCDC converters

What are the components of a full DCDC converter? Do we have them all by now?

In summary, what can a DCDC converter bring to a detector system

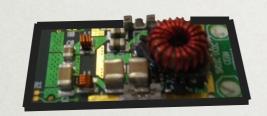

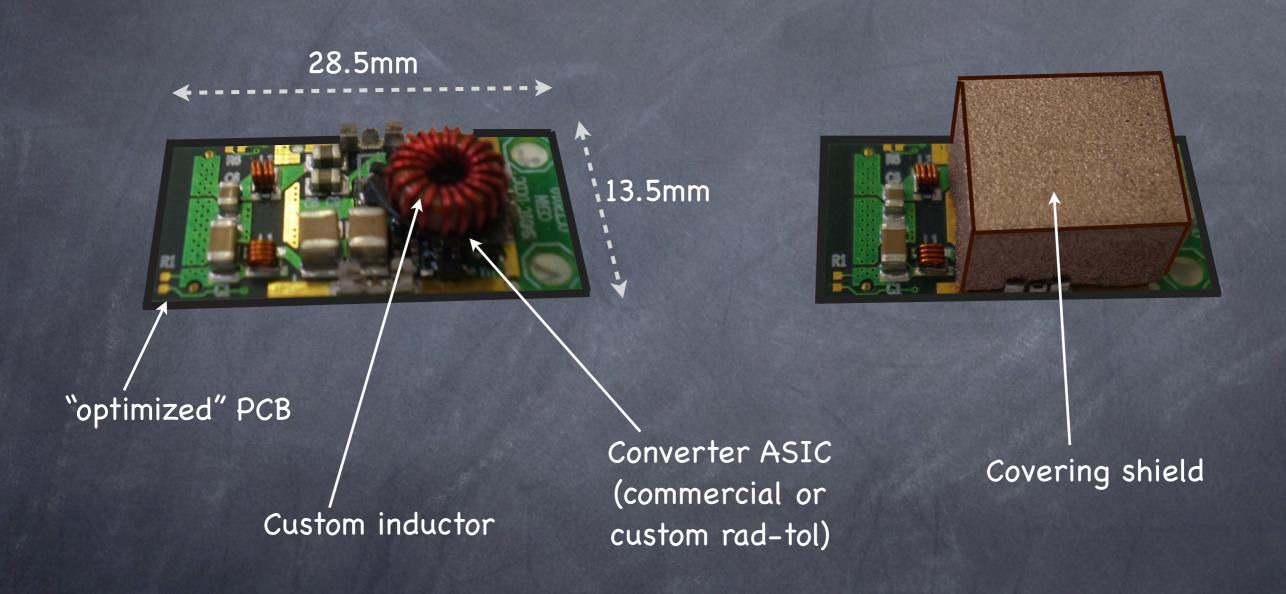

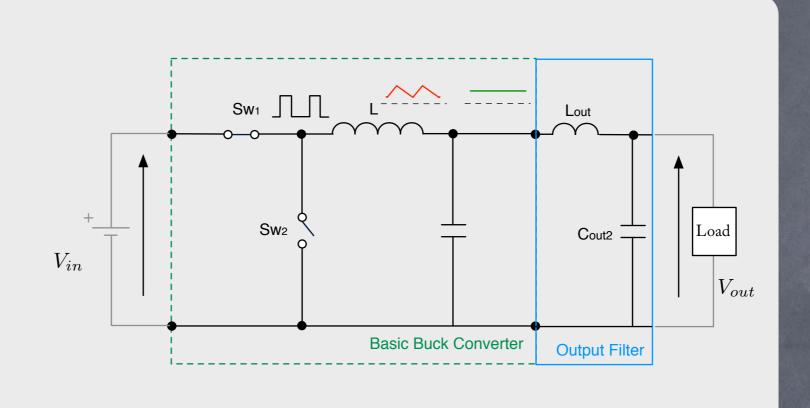

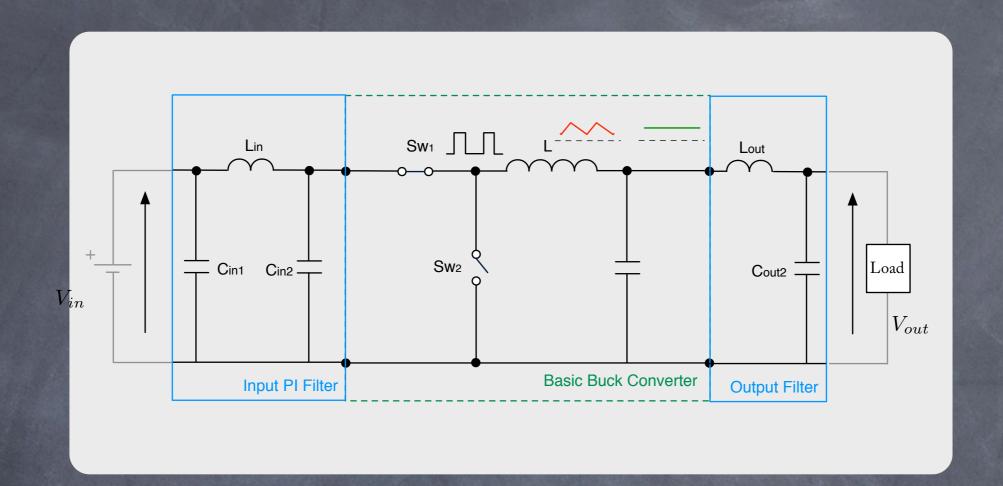

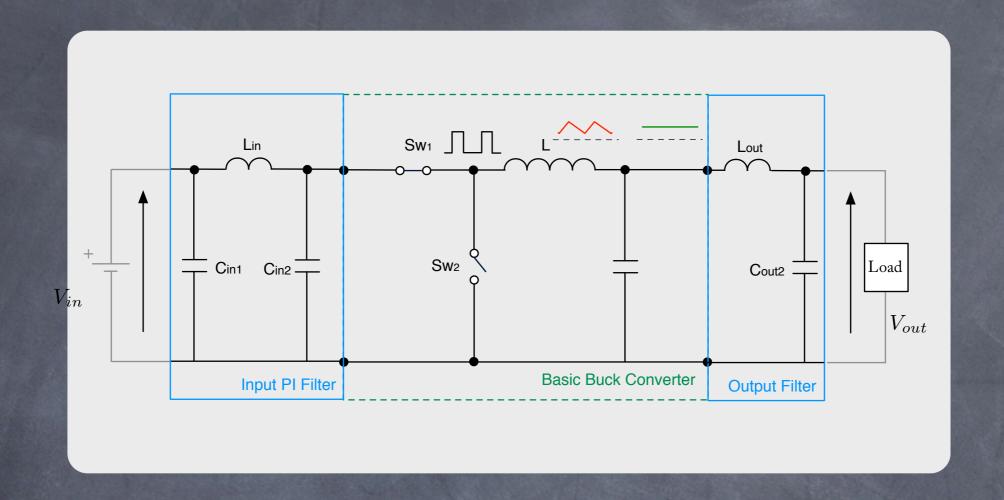

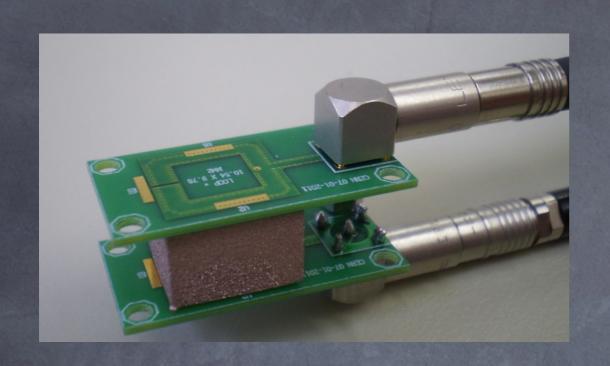

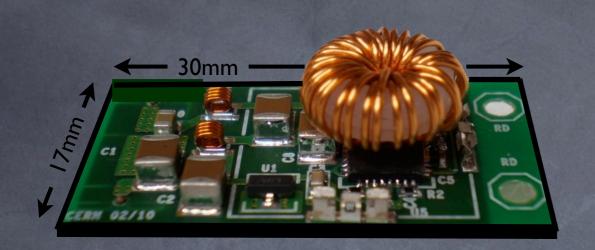

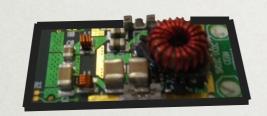

#### Example prototype of a full DCDC

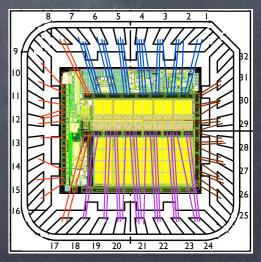

#### Steps for ASIC design:

- 1. pre-selection of CMOS technology

- 2. design of ASIC prototypes

- 3. verify electrical and radiation performance on ASIC prototypes

|                      | AMIS2     | IHP1                       | IHP2                                           | AMIS4                                           |

|----------------------|-----------|----------------------------|------------------------------------------------|-------------------------------------------------|

| Full control loop    | ✓         | ✓                          | ✓                                              | 1                                               |

| Dead times' handling | Fixed     | Adaptive<br>(QSW)          | Adaptive<br>(QSW and CCM,<br>sharp transition) | Adaptive<br>(QSW and CCM,<br>smooth transition) |

| On-chip regulator(s) | No        | No                         | <b>√</b>                                       | 1                                               |

| Soft Start           | Simple RC | Simple RC with comparators | Full sequence with comparators                 | State machine                                   |

| Over-I protection    | No        | No                         | ✓                                              | ✓                                               |

| Over-T protection    | No        | No                         | No                                             | 1                                               |

| Under-V disable      | No        | No                         | No                                             | 1                                               |

Used in system tests

#### Steps for ASIC design:

- 1. pre-selection of CMOS technology

- 2. design of ASIC prototypes

- 3. verify electrical and radiation performance on ASIC prototypes

|                      | AMIS2     | IHP1                       | IHP2                                           | AMIS4                                           |

|----------------------|-----------|----------------------------|------------------------------------------------|-------------------------------------------------|

| Full control loop    | ✓         | ✓                          | ✓                                              | <b>✓</b>                                        |

| Dead times' handling | Fixed     | Adaptive<br>(QSW)          | Adaptive<br>(QSW and CCM,<br>sharp transition) | Adaptive<br>(QSW and CCM,<br>smooth transition) |

| On-chip regulator(s) | No        | No                         | <b>√</b>                                       | ✓                                               |

| Soft Start           | Simple RC | Simple RC with comparators | Full sequence with comparators                 | State machine                                   |

| Over-I protection    | No        | No                         | <b>√</b>                                       | <b>√</b>                                        |

| Over-T protection    | No        | No                         | No                                             | <b>√</b>                                        |

| Under-V disable      | No        | No                         | No                                             | <b>√</b>                                        |

Packaged in QFN32

Used in system tests

Tape-out Jan2011 Expected early summer

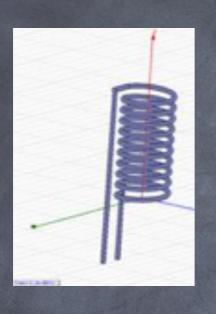

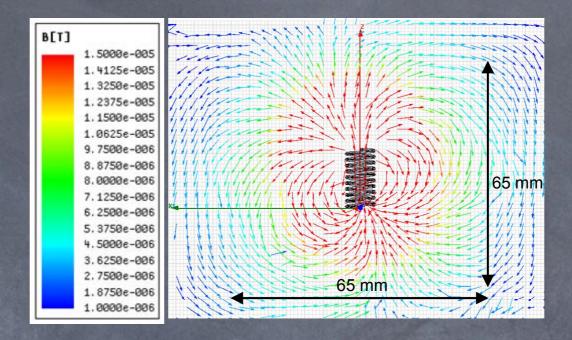

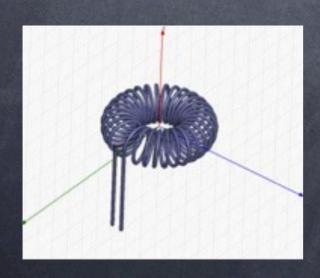

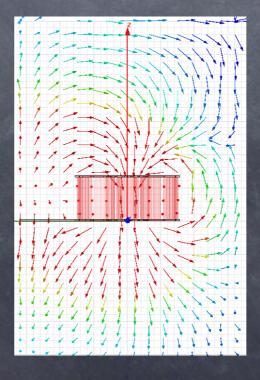

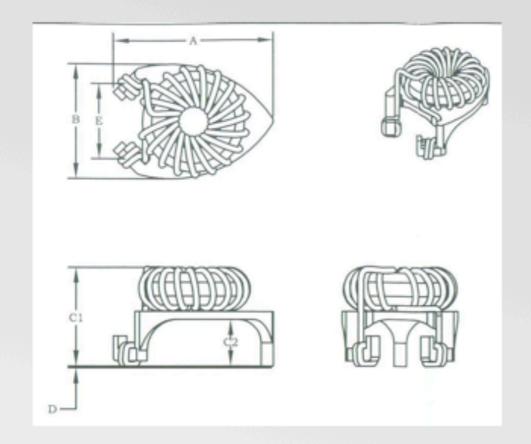

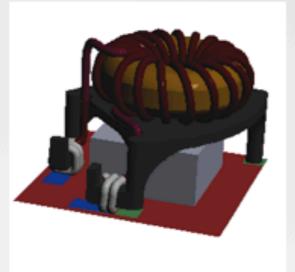

#### Solenoid

#### Toroid

#### Coilcraft design

L=220 nH ESR=30m $\Omega$

Component selection and placement

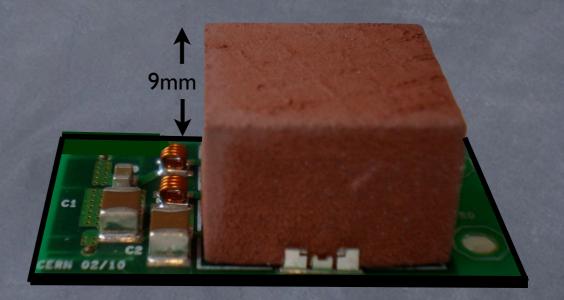

### Different constructions and thickness (t)

Painted Shield t = ?

Tape Shield t = 35 µm

Coated Shield 10 < t < 100 µm

#### This prototype uses the AMIS2 ASIC (rad tolerant)

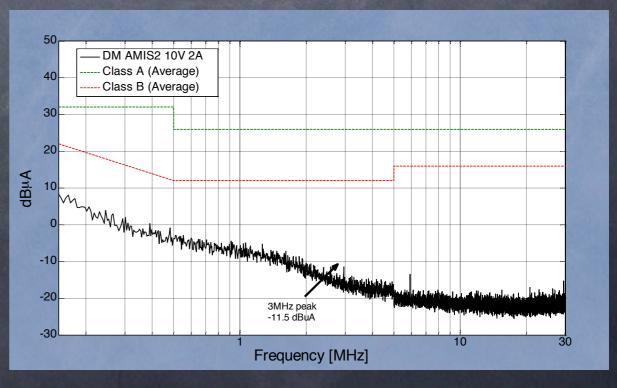

Measured output noise (current) for Vin=10V, Vout=2.5V, Iout=2A. Note that 0 dB $\mu$ A = 1 $\mu$ A

# Test with FEE Hcal CMS

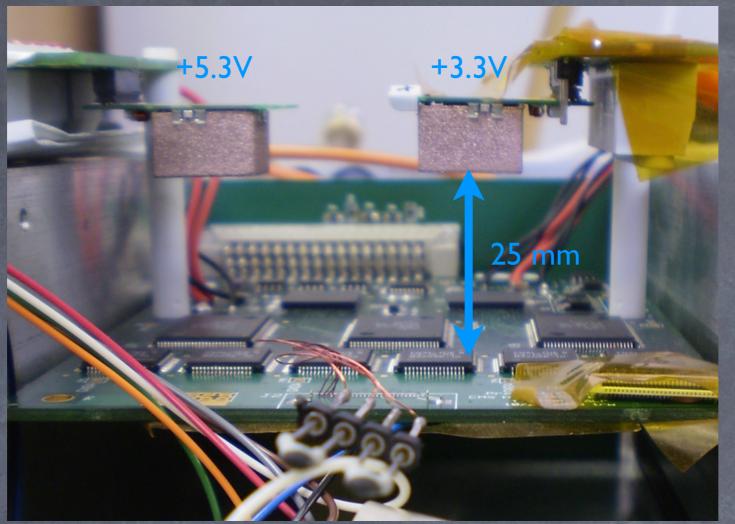

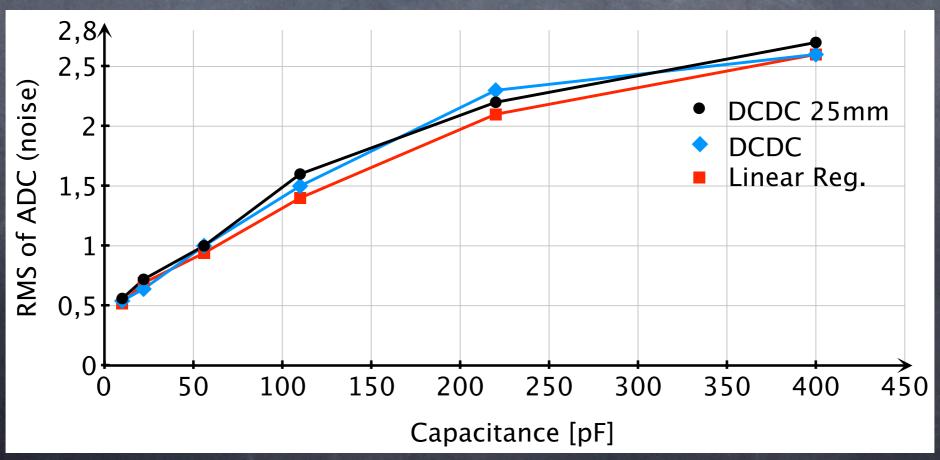

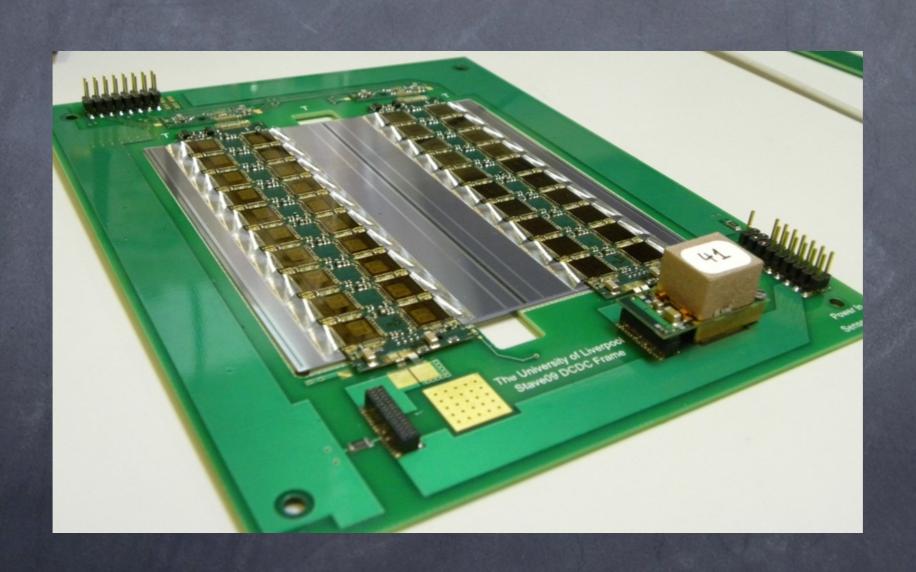

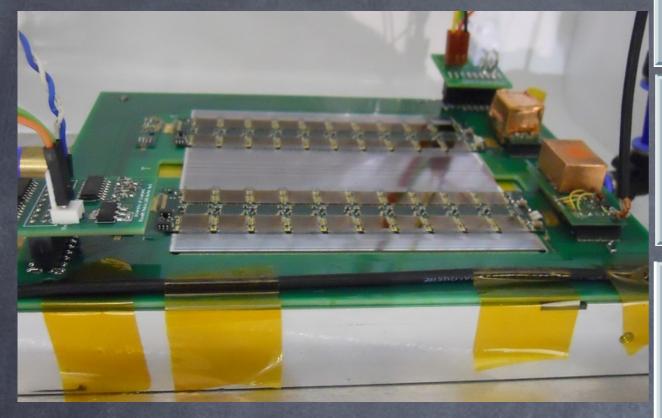

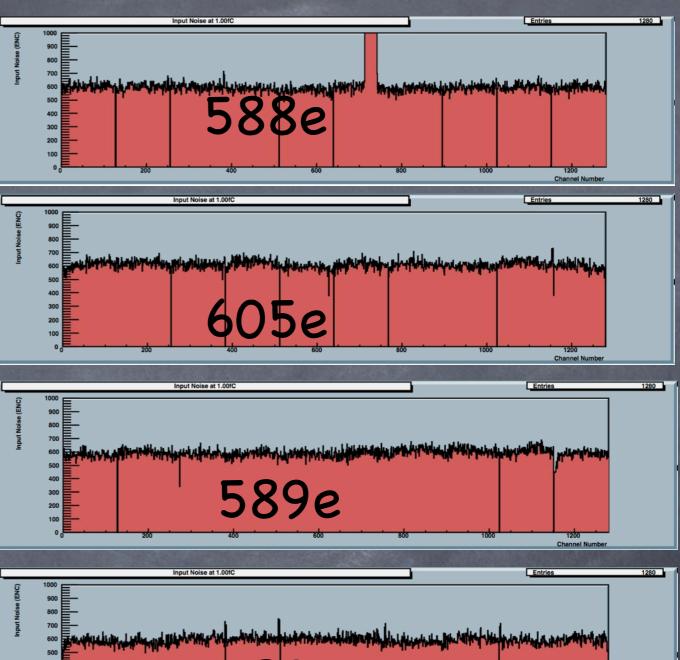

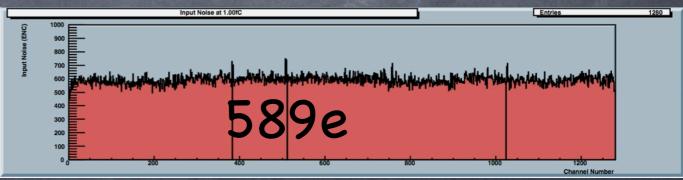

# Test with Frame Module ATLAS SCT prototype (Liverpool)

| Hybrid | Linear regulator [ENC] | DCDC STV10<br>[ENC] |

|--------|------------------------|---------------------|

| 62     | 570                    | 588                 |

|        | 596                    | 605                 |

| 61     | 585                    | 589                 |

|        | 591                    | 599                 |

# Motivation for the development of radiation and magnetic field tolerant DCDC converters

What are the components of a full DCDC converter? Do we have them all by now?

In summary, what can a DCDC converter bring to a detector system

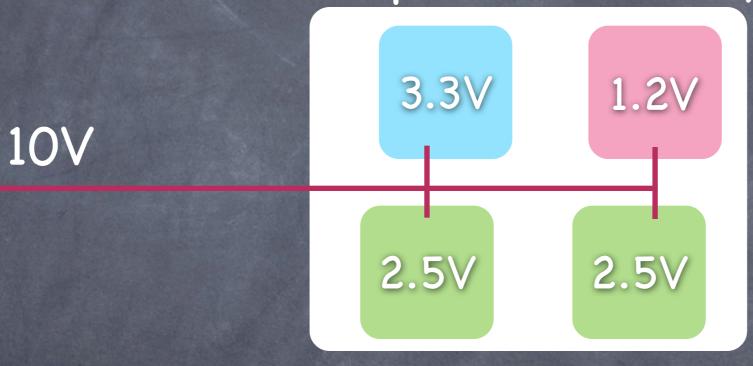

The use of DCDC converters on-detector enables power distribution at higher voltage, hence lower current in the cables

It also adds local voltage regulation

With its high efficiency, it is far superior to a linear regulator for the above purpose (large conversion ratio)

A power distribution system with DCDC converters can be build modular, which allows for progressive and selective turn-on and -off of portions. It can also be built using cascaded conversion stages for higher efficiency.

Additionally, different load voltages can be locally generated from a unique power bus

#### FE board or portion of a system

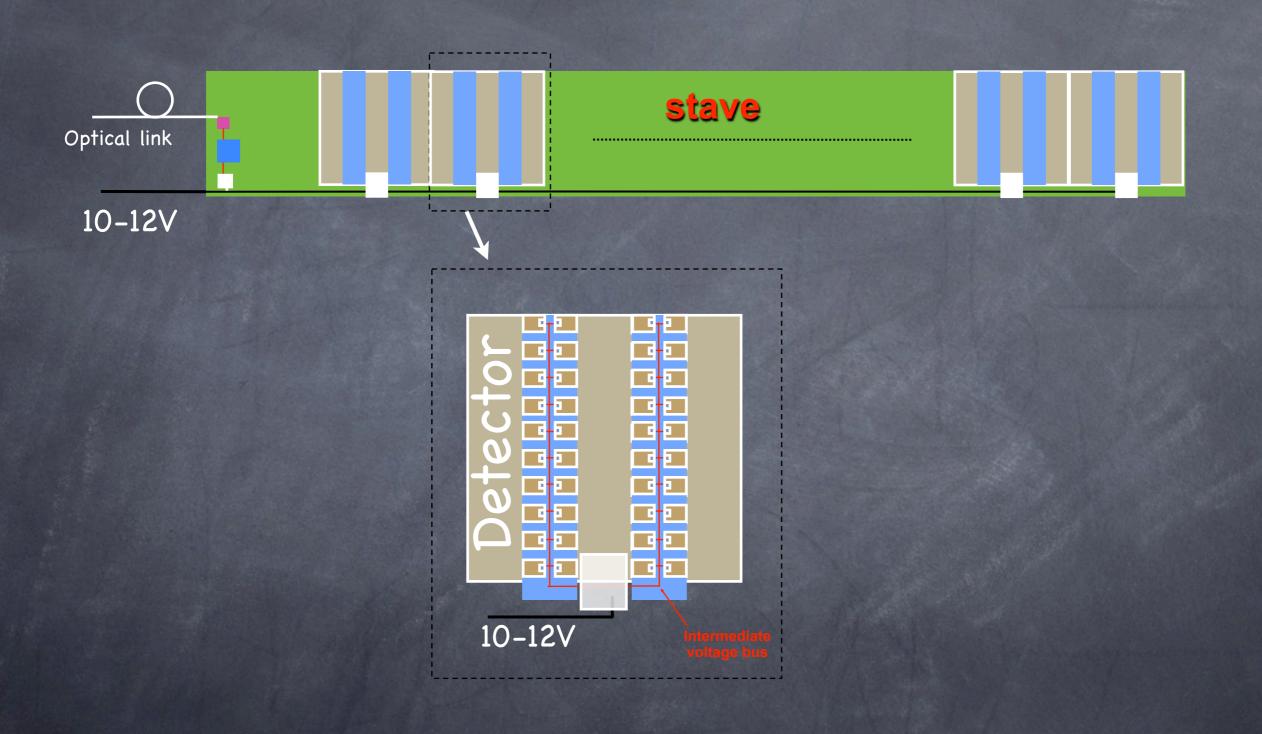

### CMS pixels upgrade phase 1

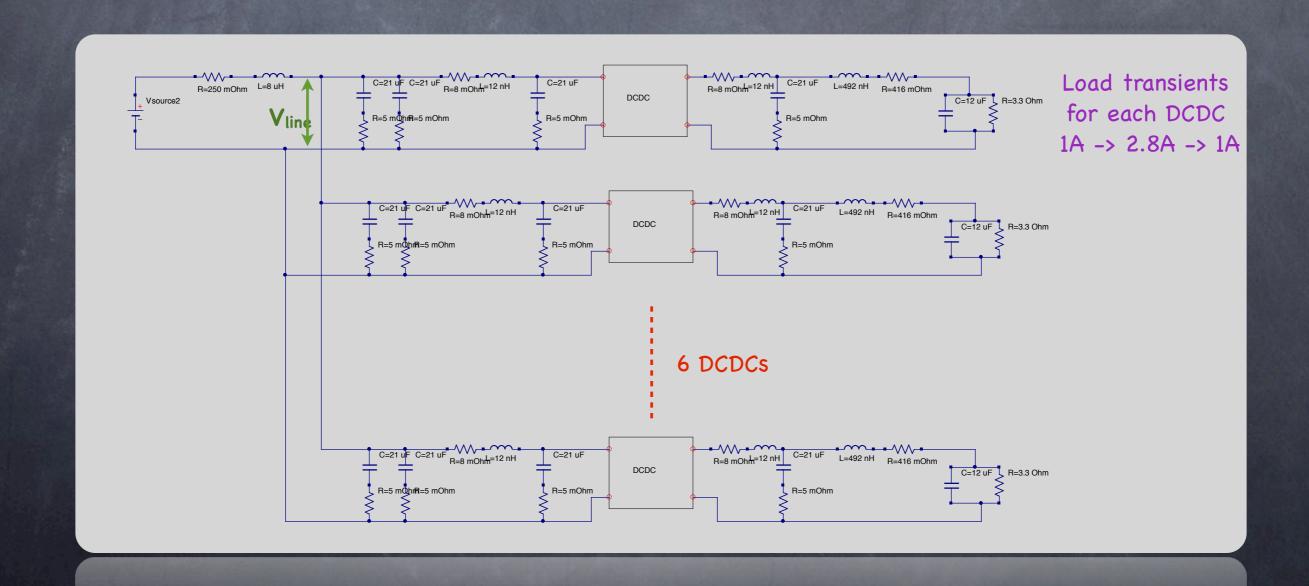

- The full distribution scheme (with ideal PS) is studied, using the best available estimates

- The case studied below is an unreal worst-case configuration

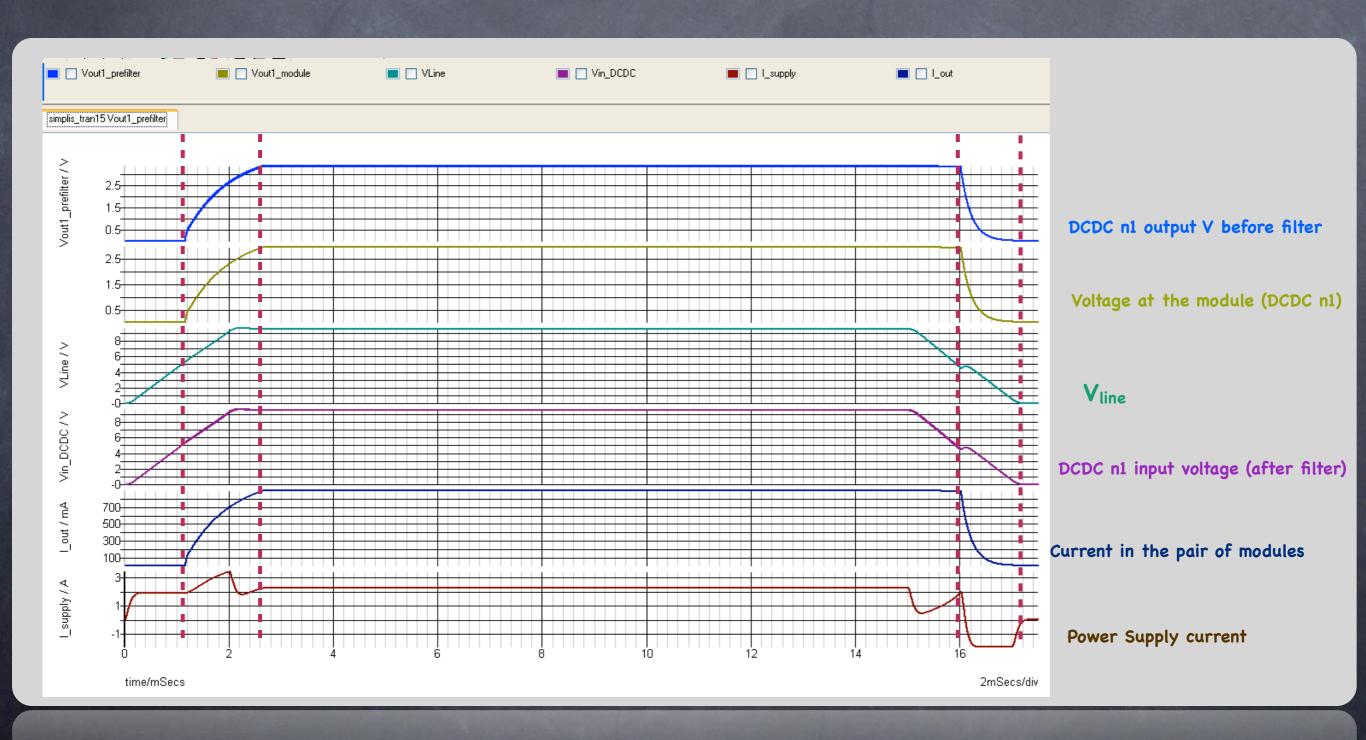

#### Power-on & power-off of full PS channel

Voltage ramp from the PS (rise & fall time 2ms) to turn-on and -off all 6 converters loaded with an equivalent 1A current

### Conclusion

- DCDC converters are required for the upgrade of the LHC experiments, already at phase1

- They enable power distribution at higher voltage, decreasing the current on the cables. A modular distribution system can be designed, facilitating partitioning of domains from an individual supply bus

- The development of full DCDC converters satisfying the requirements of the LHC experiments is well advanced. With the availability of more mature ASICs, in a few months, all the basic elements and required skills will be available (as far as we can judge now)