# EMI aspects for systems with train cycled operation: CALICE-AHCAL

EMI: electro magnetic interference

Cycle : power gets ON and OFF ?

Systems: signal chain from sensor to power supply

CALICE-AHCAL: as example the analogue hadron calorimeter

Peter Göttlicher For CALICE collaboration DESY Orsay, May, 9<sup>th</sup>/10<sup>th</sup>, 2011

## Outline

- CALICE-AHCAL: View of power/EMI/grounding

- General issues for EMI in a system

- The design chain of a system from frontend to power supply

- The layer with the sensors

- The end of layer region

- The cable to power supply

- Power supply

- Summary

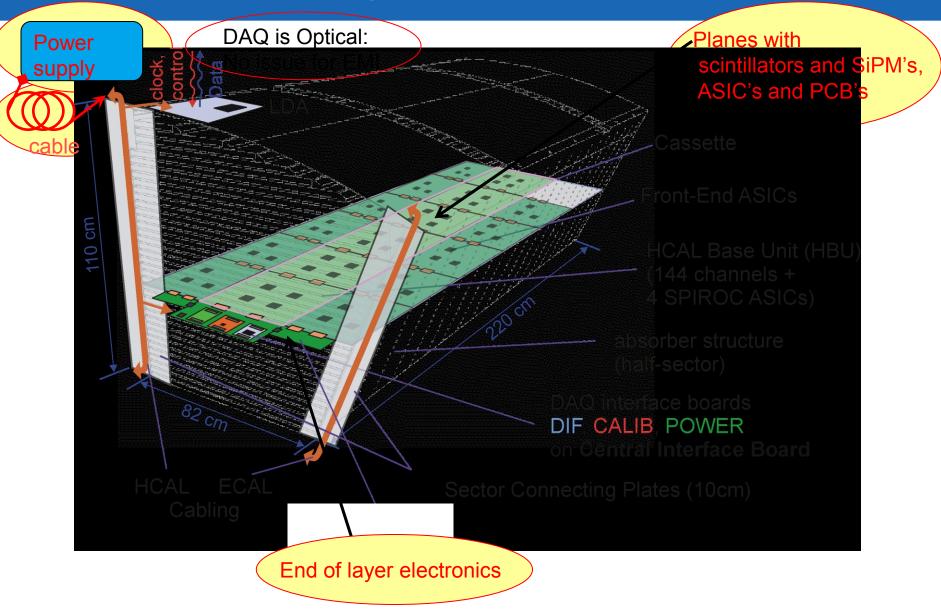

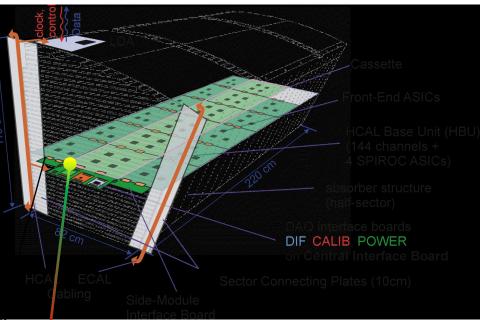

## **CALICE-AHCAL:** Design in a few words

DE)

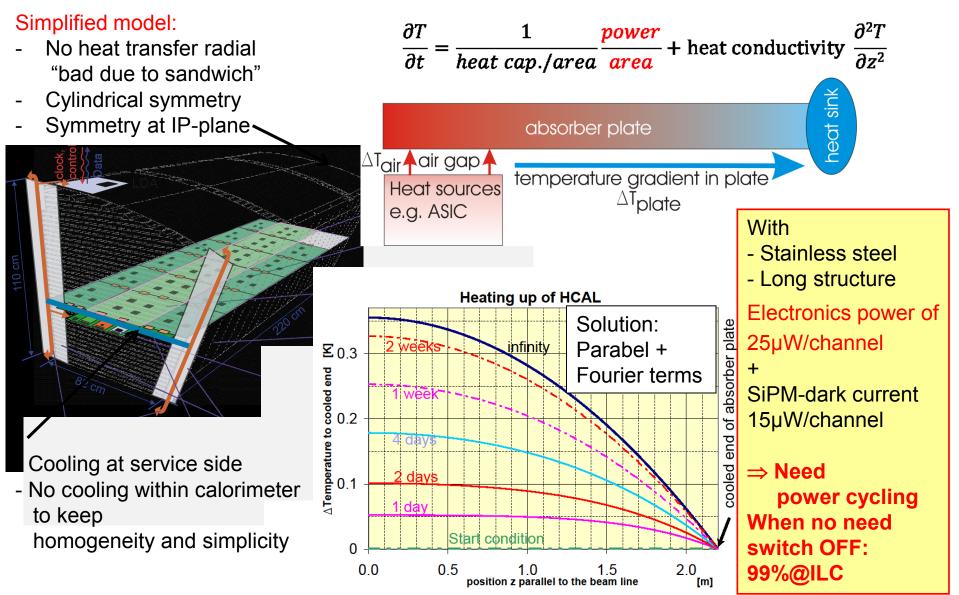

## **CALICE-AHCAL:** Why power cycling?

See : P.Göttlicher, TWEPP07, Prague, proceedings

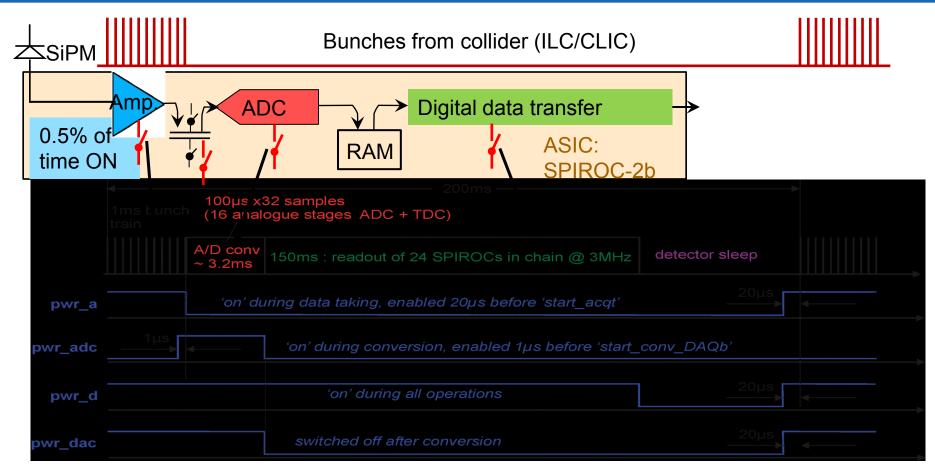

## **CALICE-AHCAL: ASIC for power cycling**

L. Raux et al., SPIROC Measurement: Silicon Photomultiplier Integrated Readout Chips for ILC, Proc. 2008 IEEE Nuclear Science Symposium (NSS08)

#### **Algorithm for CALICE-AHCAL:**

The ASIC **switches the current** of the functional blocks OFF. ASIC gets supplied **all the time with voltage**.

PCB electronics and instruments stabilize the voltage

## General issues for EMI in a system

#### **Reference ground**

- Need good definition

- Any induced/applied current produces voltage drops

- Separation between reference / power return / safety or controlling currents

and keeping currents within "own" volume and instrumentation

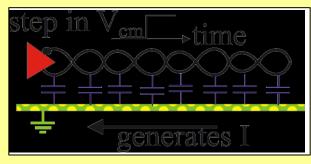

### **Capacitive coupling**

To do:

- Keep common mode voltage stable

- Keep voltages on plates stable, facing to other plates

- Keep reference closer than foreign

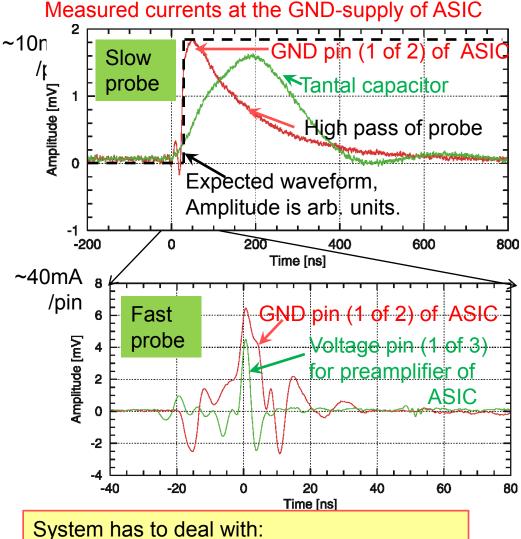

### Current loops

#### To do:

- Controlling return currents

- Keeping loops small

- Avoid overlapping with foreign components.

Guideline: Avoiding emission avoids in most cases picking up of noise

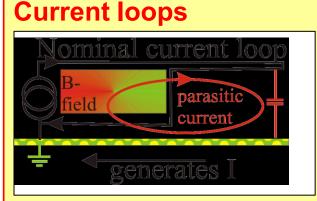

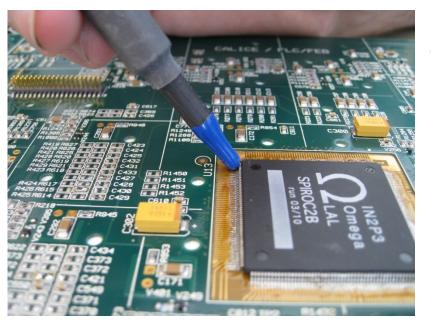

## The design chain of a system: ASIC, the current switch

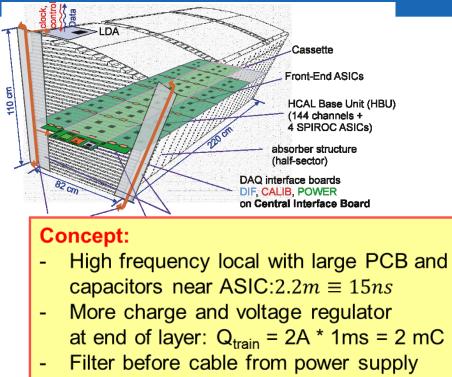

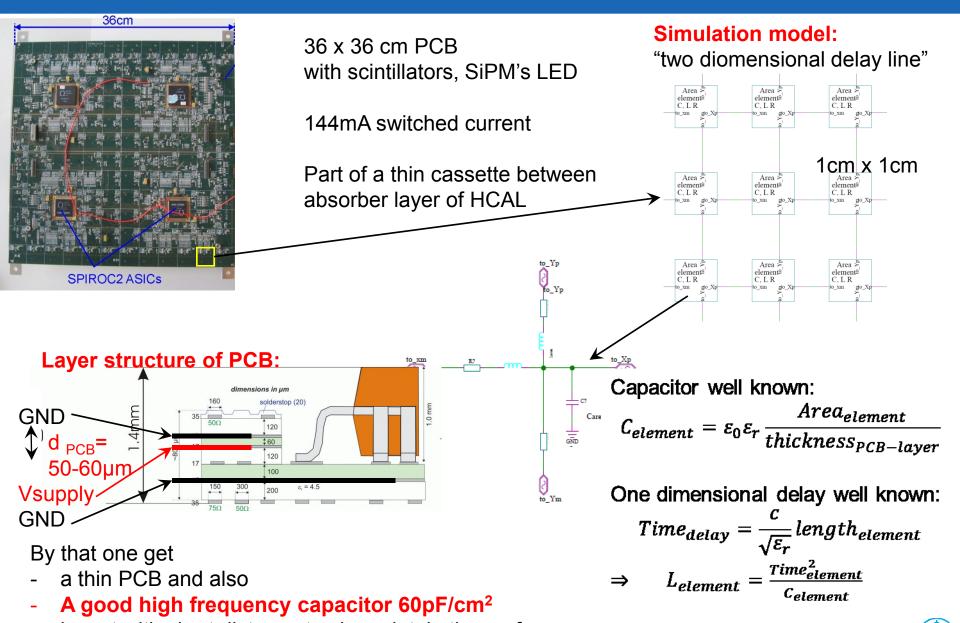

Board available with 12 x 12 channels, each 3 x 3cm<sup>2</sup> A layer will be around 2m<sup>2</sup>: 2200 channels

Each ASIC 36 channels: Currents switched: ~36mA/ASIC

~ 144mA/board ~2.2A/layer

Measurement: Slow: 0.25 – 50MHz Fast: 30MHz-3GHz

System has to deal with: 5Hz from train repetition to few 100 MHz 2.2A for a layer

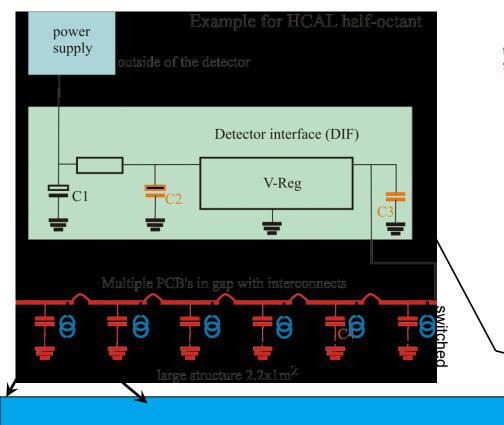

## The design chain of a system: Chain for voltage stabilization

- Galvanic isolated power supply

Reality on lab-desk: One HBU:HcalBaseUnit

SPIROC2 ASICs

**USB** interface

Flexleads

#### Future

## The layer with the sensors: HcalBaseUnit

- layout with short distance to via maintain the performance. | LC power workshop | Orsay, May 9th 2011 | Page 9

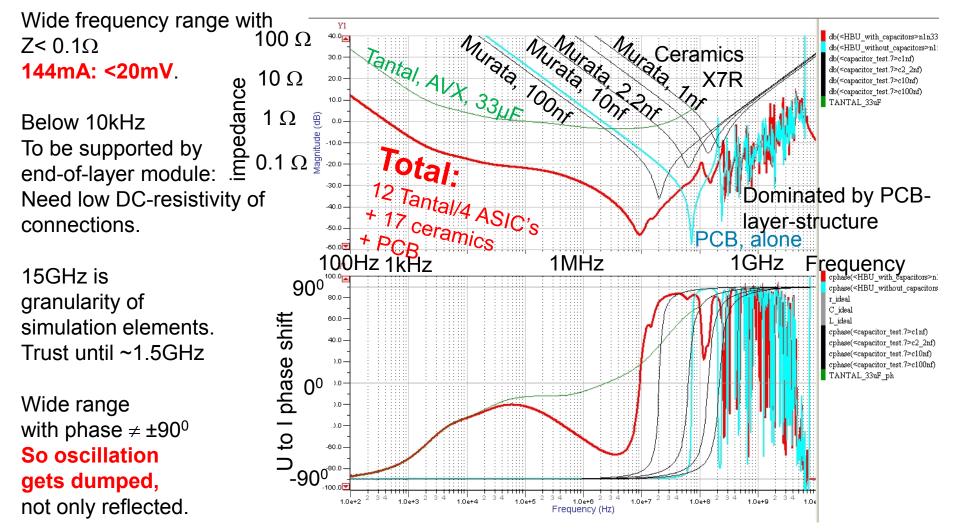

## The layer with the sensors: HcalBaseUnit The impedance, simulation

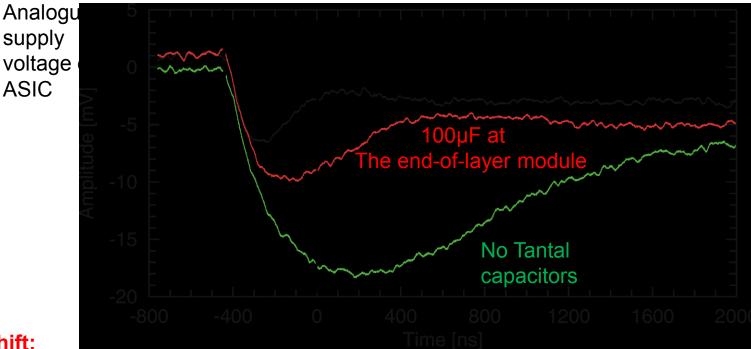

## The layer with the sensors: HcalBaseUnit, Voltage stability, measurement

#### DC-voltage shift:

For the test OK,

To be looked at for extension from one to six HBU's in a chain Resistivity of voltage source, interconnect,

With 6 boards total current and resistance grow: Voltage drop 60mV,  $\,$  is still OK.  $\checkmark$

#### Higher AC-shift, if Tantal is further away

CALICE AHCAL: thin 33µF-Tantal available to mount near ASIC's on HBU Nice to understand, whether DC-resistance or distance is the source, or?

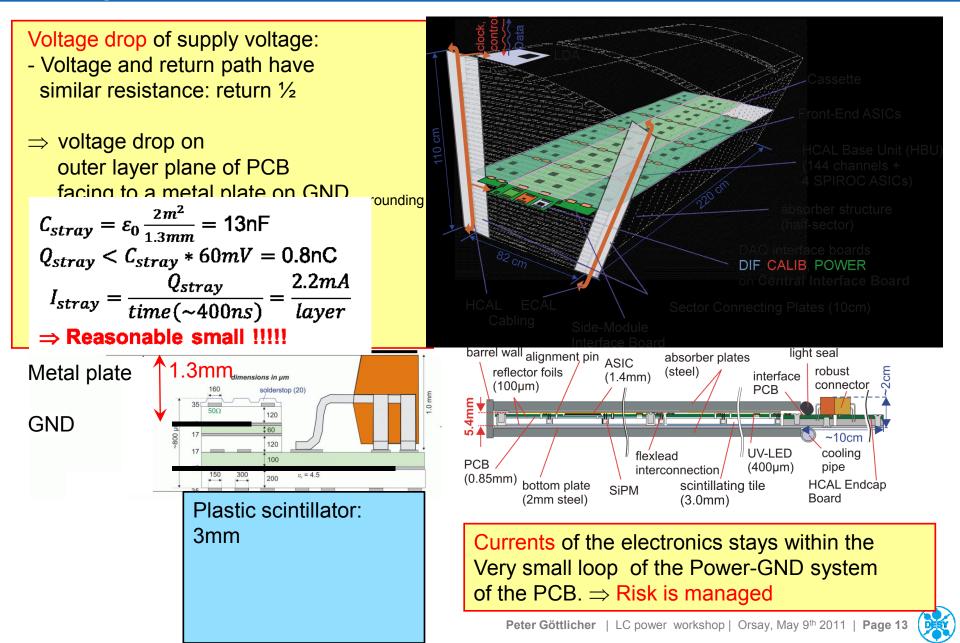

## The layer with the sensors Definition of the GND to surrounding

Within the detection layer the GND is return path ( $\Delta V \sim 60 \text{mV}$ ) and reference

Steel of structure is part of general GND<sub>safety</sub>

so it is not good to use, because currents might not stay there and move into whole ILD.

Slow control and bias voltage regulatio is at end-of-layer electronics. Bias is the most critical in the system.

There it is easy to get a connection fro GND<sub>surrounding</sub> to GND<sub>electronics</sub> and *v* very good to keep the SiPM bias defined.

#### <u>Proposal:</u>

Connect it at end-of-layer and per layer

Doing so and per layer means:

No other connection is allowed and all other should be kept galvanic isolated or the risk to introduce currents into the PE-system has to be managed. Within the layer: up to 60mV between

GND-PE and local GND-electronics.

#### Disadvantage:

- A supply and return line per layer

- Space constrains:

Pair in a multi pair cable?

#### Compromise:

Grouping neighboring layers (keep current limit of connectors within the range of fused supply)

## The layer with the sensors, Stray capacitance to steel structure

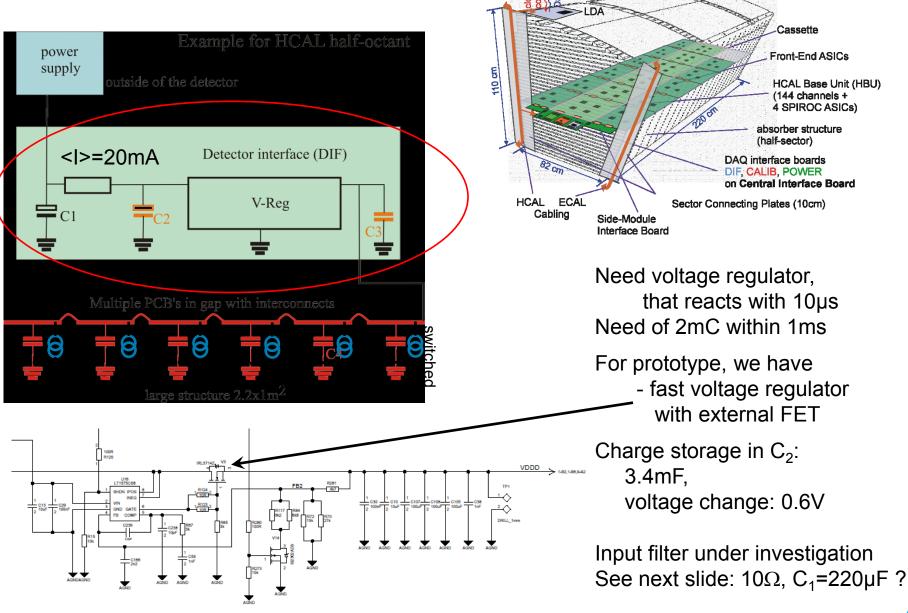

## The design chain of a system: Chain for voltage stabilization

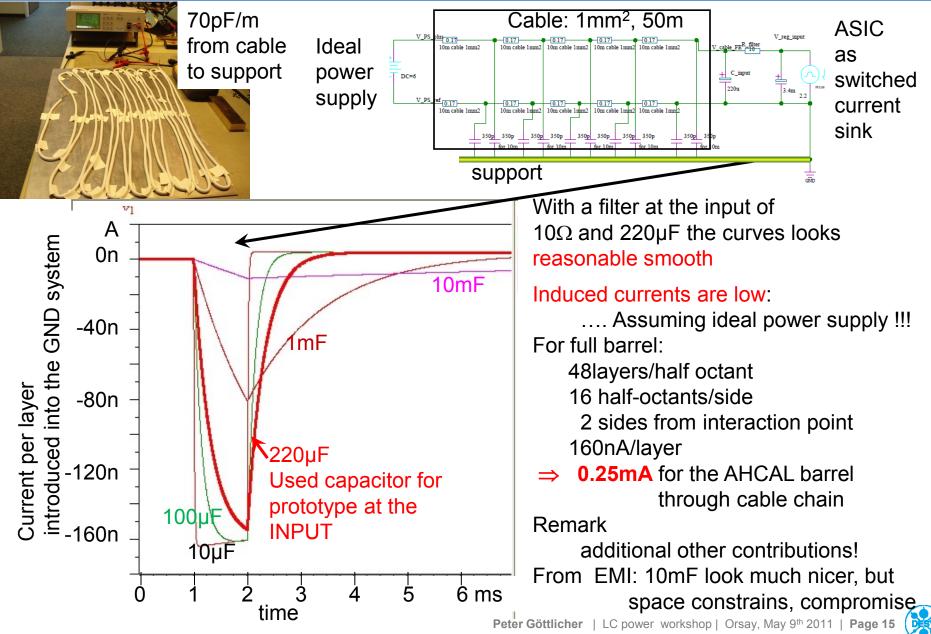

## The design chain of a system: Feed back into the supply cable and its support

## The design chain of a system: Other cable issues

#### DC-current in cable:

- Additional constant load at the end of the layer: ~0.7A : 6kW for AHCAL-CALICE,

FPGA-based, charge storage w/o DC/DC-converter Voltage drop for 1mm<sup>2</sup>, 50m : 1.2V, reasonable efficiency.

**Careful:**

or well understood overlay regions with GND/foreign.

.... That good performance, because of closing higher current loops locally and local charge storage.

her

Simulation underestimates

parasitic effects

parasitic effects

Peter Göttlicher

| LC power workshop | Orsay, May 9th 2011 | Page 16

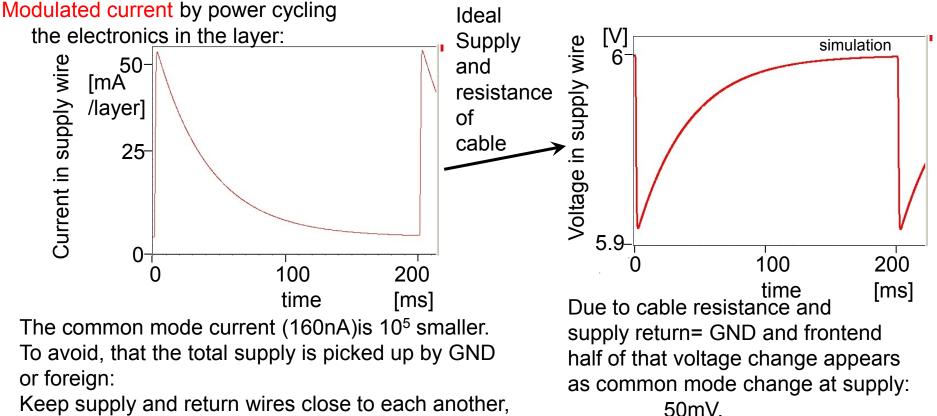

## The design chain of a system: Power supply

## Tasks, requested for functionality?

Galvanic isolation needed for: Definition of GND-point at sensitive frontend Compensation of voltage drop on cable Avoiding currents in the safety GND system Need exactly ONE cable per channel to detector

Low capacitive coupling from electronic-system to GND<sub>safety</sub> typical supplies have few 100nF, small laboratory 1-10nF factor 1000 more than the cable..... 0.25mA for AHCAL-barrel induced current transform immediately into 250mA.

From Frontend requested reaction times of power supply: < 1ms That is fast for standard power supplies ! Slower reaction times causes higher voltage changes and larger induced currents.....

## Options: It is outside experiment:

Most of that is not investigated so far in the context of CALICE-AHCAL - more mechanical space opens options

- charge storage to slow down before power supply start to regulate

- filter for common mode currents

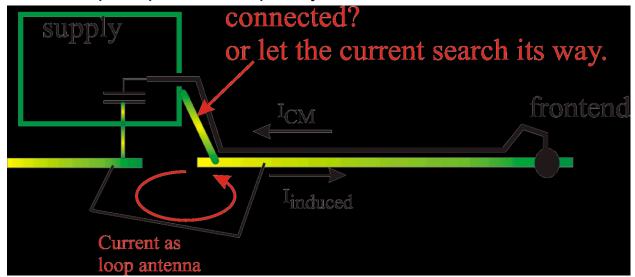

## The design chain of a system: Power supply

## Integration issues:

Connection of cable support to the housing?

- + good to dump the currents induced to the cable support without loop antenna

- -- No galvanic isolation between service-room and experiment, most modern systems don't allow that at all, too many connections anyway,

but if fully realized: No pickup of low frequency noise-currents

Fusing, current limits to weakest point of chain until next fuse/limit front end likes small connectors, but also grouping layers to reduce cables Compromises including the frontend

## Summary

- Detectors for Linear Colliders requires many channels with low power

- Train structure allows 99% time to be OFF: Factor 100 in critical regions

- Coherent fast switching ON/OFF of high current:

CALICE-AHCAL: 2.2A\*layers : 3.4kA for the second secon

3.4kA for the barrel 5Hz to few 100MHz

- System aspects at local design

- Keeping currents local with well defined return-path

- Local charge storage for wide frequency range with

- Good circuit and PCB design: ceramics, tantals

keeps

- the impedance small

- the currents leaving a defined volume small with slow rise times

- System aspects within whole experiment

Lower frequency part has to be handled by cables and power supply Need well control of cable routing and good integration of power supply.

Simulation leaves many parasitic effects out Underestimates the high frequency EMI-disturbance .... Experiments, concepts to be better than simulation promises Peter Göttlicher | LC power workshop | Orsay, May 9th 2011 | Page 19