# **DEPFET APS for future collider applications**

### Status and prospects of the DEPFET project –

Laci Andricek for the DEPFET Collaboration www.depfet.org

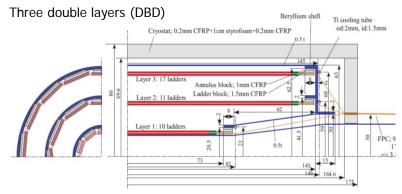

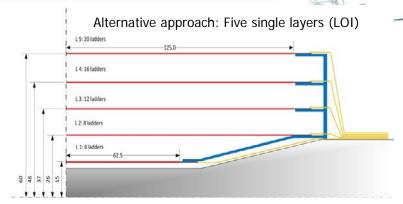

## Introduction – The ILD VXD

|                   | ILD LOI 5-layer layout | Belle II                               |      |

|-------------------|------------------------|----------------------------------------|------|

| Radii             | 15, 26, 38, 49, 60     | 14, 22                                 | mm   |

| Sensitive length  | 123 (L1), 250 (L2-L5)  | 90 (L1), 122 (L2)                      | mm   |

| Sensitive width   | 13 (L1), 22 (L2-L5)    | 12.5 (L1-L2)                           | mm   |

| Number of ladders | 8, 8, 12, 16, 20       | 8, 12                                  |      |

| Pixel size        | 25x25 (L1-L5)          | 55x50 & 60X50 (L1), 70x50 & 85x50 (L2) | μm²  |

| frame rate        | 20 (L1), 4 (L2-L5)     | 50                                     | kHz  |

| Number of pixels  | 800                    | 8                                      | Mpix |

Belle II PXD ladder: (almost) prototypes for L1 and L2 of ILD LOI layout!!

#### DEPFET Meeting, Seeon, June 2012

mpi /halbleiterlabor

### The most challenging requirements

- :- small pixels (~20 $\mu m$ ) for excellent single point resolution (~3 $\mu m$ )

- :- minimal material

$\rightarrow$  thin sensors with large S/N; minimize support, services, and cooling material

- :- like the CPS option, the DEPFET runs in a rolling shutter mode (read-out during the bunch train)

- $\rightarrow$  due to background, take as many frames as possible to minimize occupancy!

- $\rightarrow$  our goal is (as written in the LOI) ~1/50µs frame rate (innermost layer)

- :- radiation tolerant up to ~1Mrad and ~10<sup>12</sup>  $n_{eq}$ /cm<sup>2</sup> for 10 years operation (e<sup>-</sup> in the MeV range)

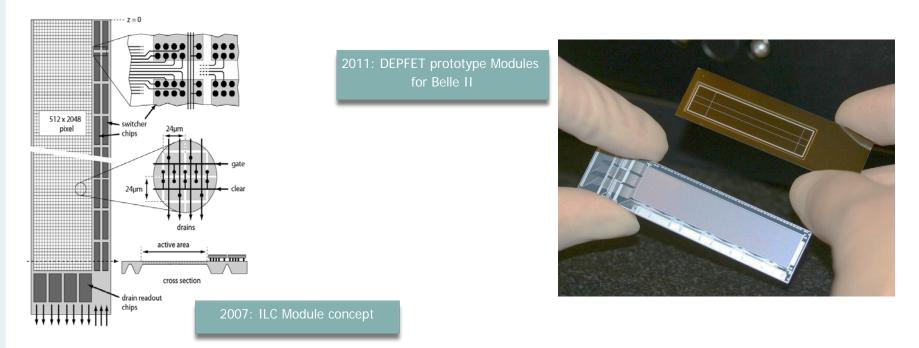

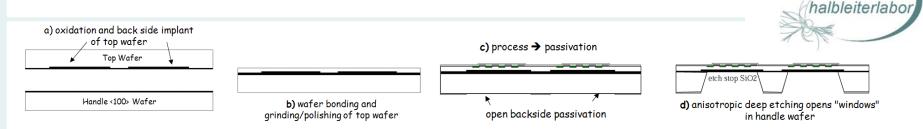

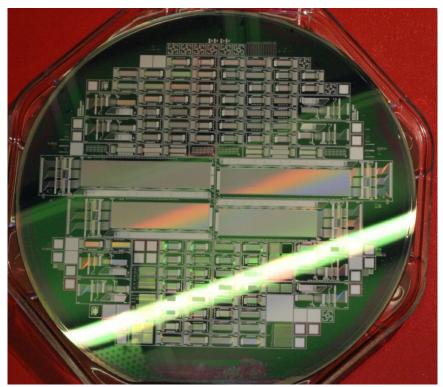

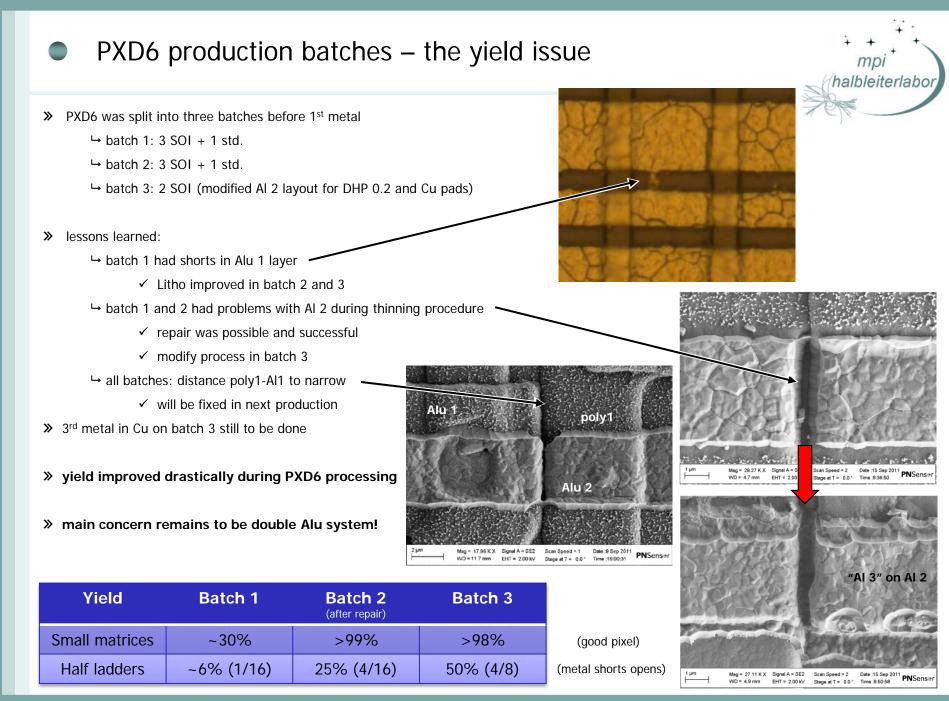

# PXD6: first thin DEPFETs on SOI

- SOI wafers (50 μm top layer, 400 μm handle)

+ 2 reference wafers on std.

- Technology variations on the wafer and wafer-to-wafer (new dry etch techniques, oxide thickness..)

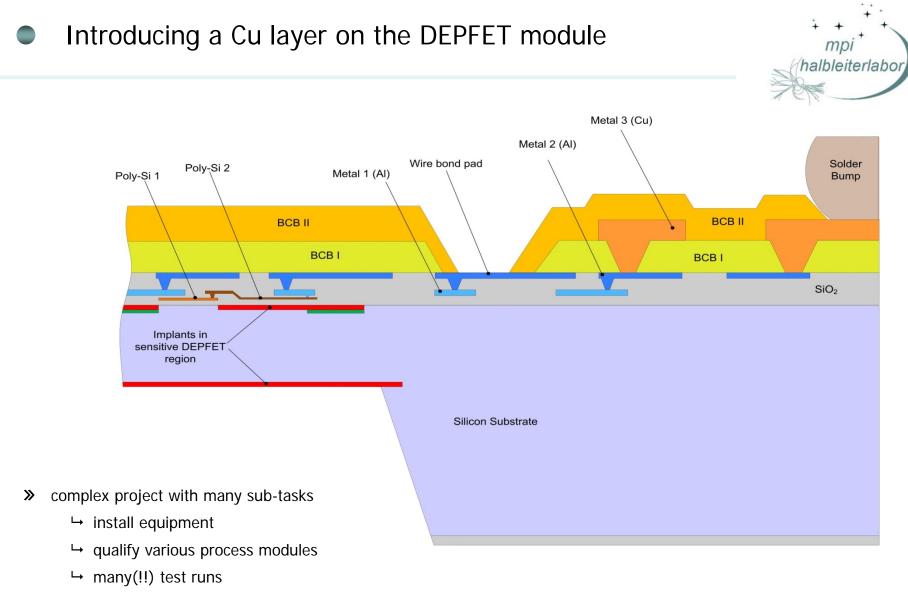

- >> 9 impl., 19 litho., 2 poly Si, 2 Al (.... & 3<sup>rd</sup> metal Cu later)

- → 3m (SOI) + 16m (main process incl. thinning)

- » About 100 test matrices in different variations

- $\rightarrowtail$  pixel sizes from 20  $\mu m$  to 200  $\mu m$

- $\hookrightarrow$  shorter gate length, improved clear structures ...

- $\mapsto$  various drift region and pixel designs ...

- >> 4 large half-ladders with the most promising options

- > purpose of this production run:

- $\mapsto$  practice full process sequence (incl. thinning)

- $\mapsto$  build sensors for system tests

- $\mapsto$  test design variations and verify simulations

- → gain yield experience

# PXD6 testing in the lab

- > bench tests in the lab

- → determine best operating point (Clear, ClearGate, Drift..)

- └→ in-pixel studies with laser

- └→ radioactive source tests

- └→ read-out speed...

- >> goal @Belle II

- ≫ 320 MHz system clock

- > 50 kHz frame rate (20µs r/o time per frame)

- ≫ 768 rows, 4-fold r/o  $\rightarrow$  ~100 ns per row

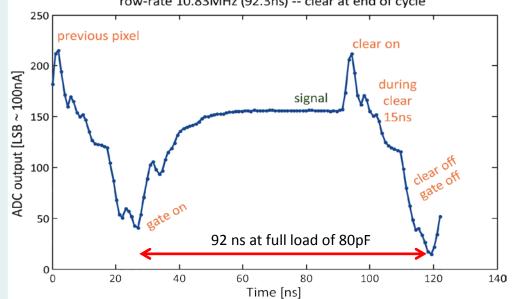

single pixel DEPFET (COCG LE) current output as seen by DCD row-rate 10.83MHz (92.3ns) -- clear at end of cycle

### LCWS 2012, Arlington, October 2012

# r/o speed with ILC-type sensor: status and prospects

- ≫ 100ns per r/o → 2048 rows per half-ladder, 2-fold r/o →  $\sim$  1/100µs frame rate state of the art

- >> possible improvements (with current f/e electronics and ADC)

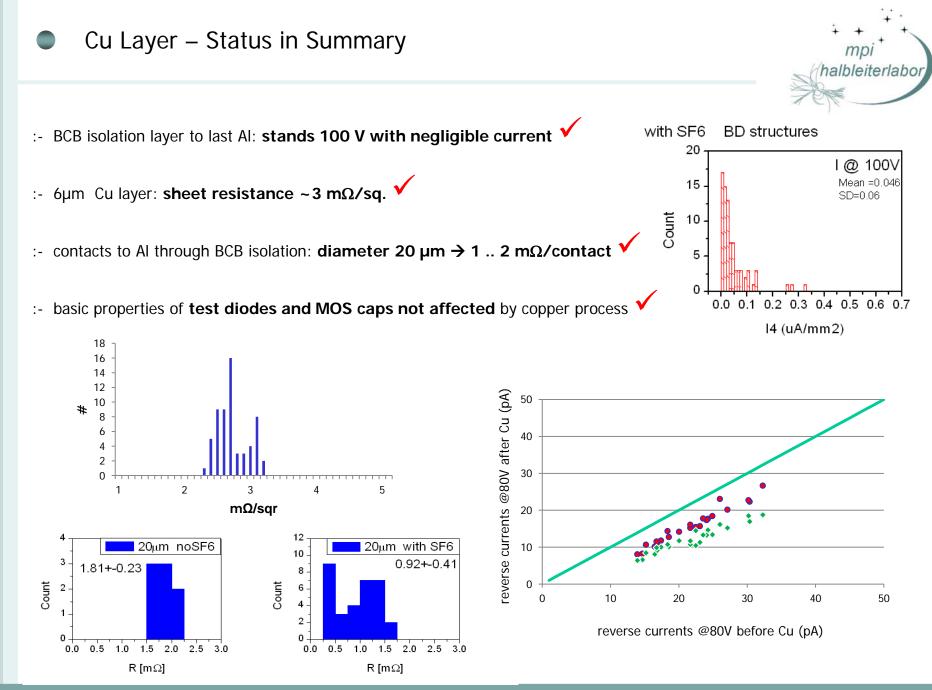

- → Sensor technology: a third metal layer in the sensitive area is within reach (Cu, see later)

- $\rightarrow$  4-fold read-out with small pixels  $\rightarrow$  1/50µs frame rate

- → optimization of cluster size for shallow(er) tracks

- $\rightarrow$  Introduce three regions in z with ~25µm/50µm/100µm pixel pitch in z (similar to Belle II)

- $\rightarrow$  #rows reduced by factor ~2  $\rightarrow$  1/25 µs frame rate possible

### » R&D status and plans:

- → 3<sup>rd</sup> metal layer well advanced, used already at ladder periphery for Belle II PXD

- → simulation work planned: variable pixel sizes in z and impact on physics

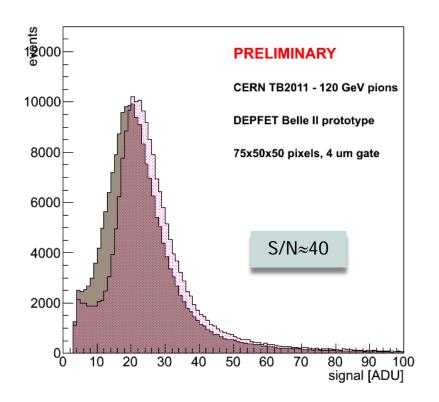

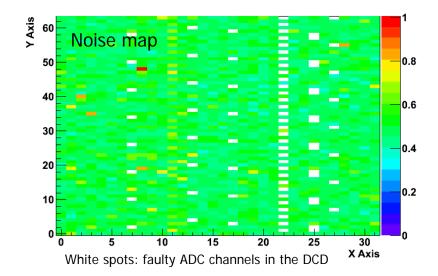

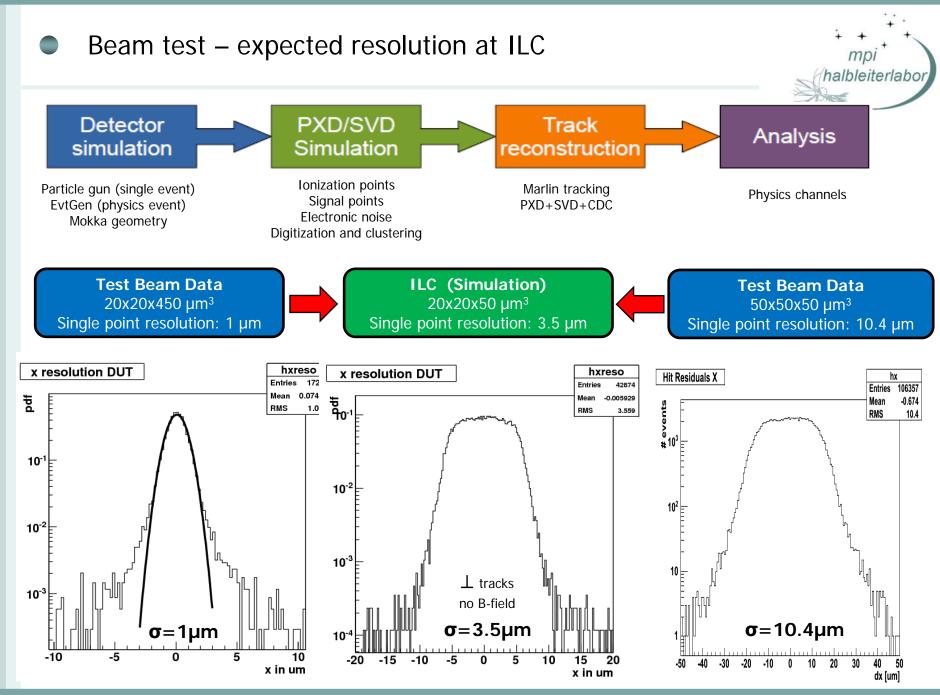

# 120 GeV pions beam test results

- » latest beam test Oct. 2011, CERN SPS, 120GeV pions

- → PXD6 matrices, thickness 50µm

- $\mapsto$  L=4µm, 75x50µm<sup>2</sup> pixel

- » very homogeneous noise and hit maps, few ADC channels bad

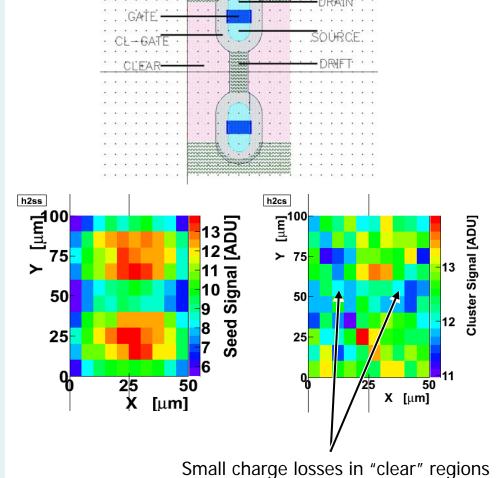

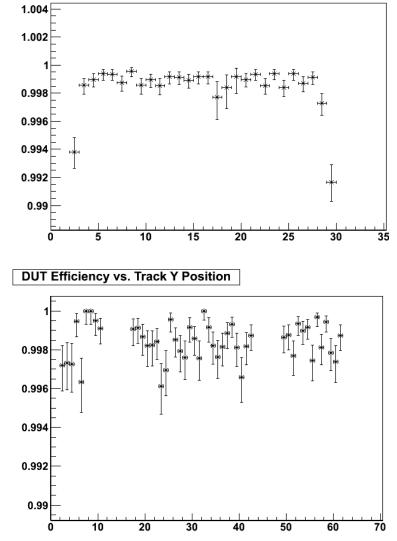

### Beam test – efficiency, charge collection

- > small charger losses <10% in clear region

- » efficiency >99.5%, both in X and y

**DUT Efficiency vs. Track X Position**

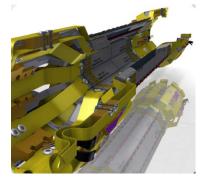

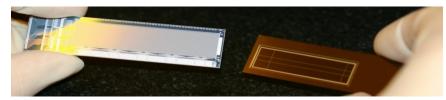

### Transition from test systems to integrated modules

- » PCB for the various matrices ..... "hybrids"

- » first bump bonded chip on PXD6 matrices

- $\rightarrow$  2 metal layers, not the final geometry, simple 3<sup>rd</sup> metal later

- → need still support PCB for I/O

- → not perforated balcony, Au studs as UBM

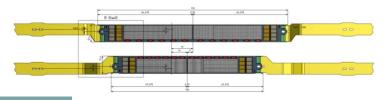

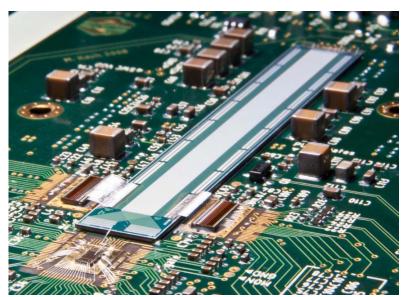

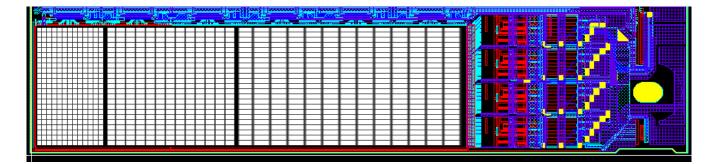

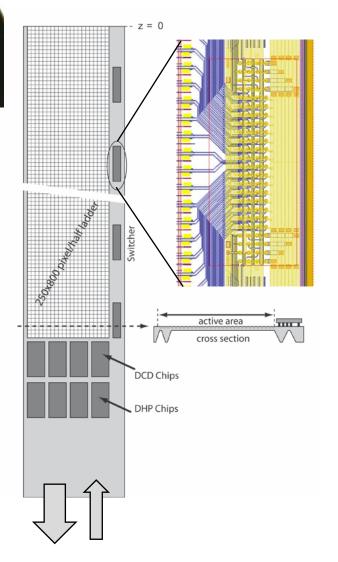

- » Belle-II PXD Module (two modules form a ladder)

- → three metal layers, Cu as LM only on periphery

- $\mapsto$  4 DCD, 4 DHP, 6 Switchers  $\rightarrow$  ~3000 bonds/module

- $\hookrightarrow$  Cu as UBM, bumps partly on thinned perforated frame

- $\rightarrow$  passive components soldered to substrate

- $\mapsto$  I/O and power over Kapton cable

$\hookrightarrow$  dummies and test diodes

LCWS 2012, Arlington, October 2012

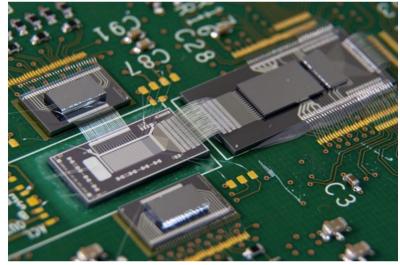

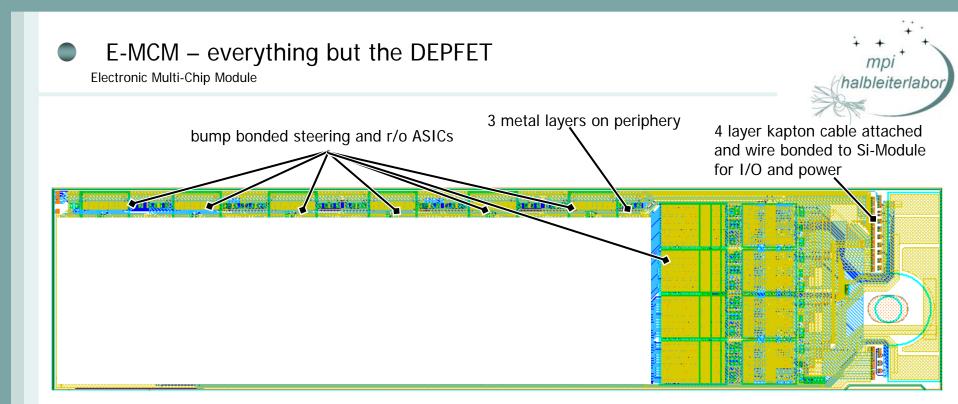

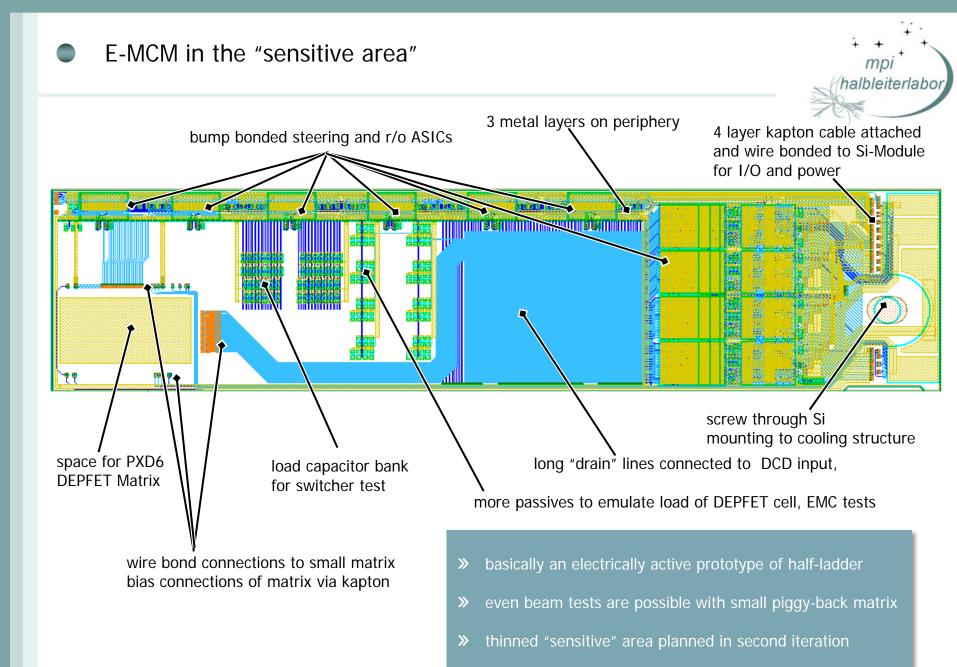

- > metal system as close as possible to final, best guess for the layout  $\rightarrow$  same as for final production

- → full schematic at the periphery for 6 Switcher, 4 DCD, 4 DHP

- → landing pads for solder bumps on ASICs

- → space for passives (caps and termination resistors)

- → I/O and power over 4-layer kapton cable at EOS

- → mechanically attached to cooling end-flange

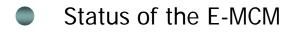

- E-MCMs ready for FC and test

- $\mapsto$  realistic system test

- $\mapsto$  result  $\rightarrow$  Belle II production

DEPFET technology with 3<sup>rd</sup> low impedance metal layer!!

Also for ~20 $\mu$ m pixels: 2-fold read-out  $\rightarrow$  4-fold  $\rightarrow$  2x higher frame rate at same row rate

### Thinning step $\rightarrow \mu$ -joint between half-ladders

- » v-grooves in support silicon

- » butt-joint between two half-ladders

- » reinforced with 3 ceramic inserts

- » 2x300µm dead area per ladder

- » mechanical tests  $\rightarrow$  remarkably robust!!

- » bowing: up to 1 mm sag (over 10 cm)

- » tension: 40 to 60 N, then the Si broke

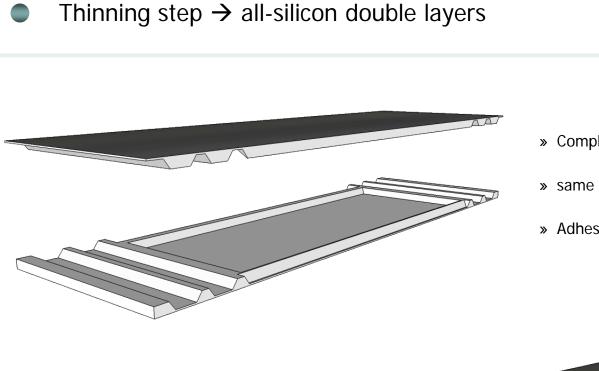

- » Complementary etch grooves in support frames

- » same process step as thinning and  $\mu\text{-joint}$

- » Adhesive joint between layers

- » DEPFET option **not** linked to 5-layer VXD!

- » R&D needed for this

- » single layer ladder engineered to a large extent

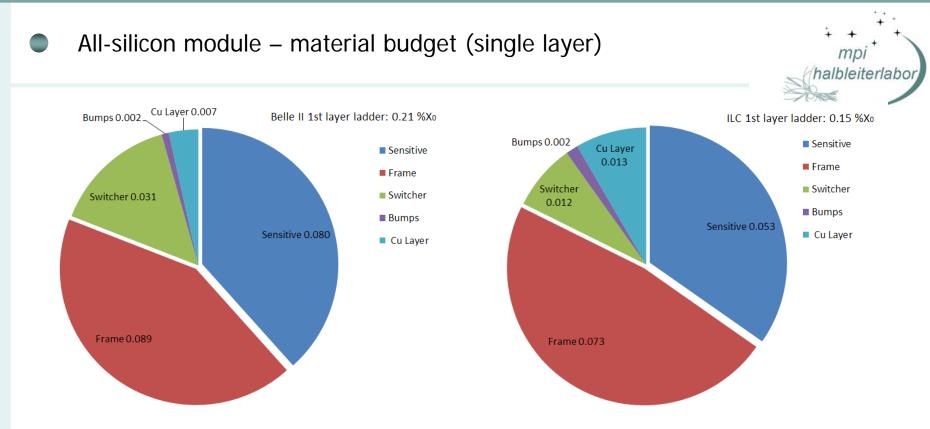

|                    | Belle II          | ILC                |

|--------------------|-------------------|--------------------|

| Frame thickness    | 525 μm            | 450µm              |

| Sensitive layer    | 75 µm             | 50µm               |

| Switcher thickness | 500µm             | 100µm              |

| Cu layer           | only on periphery | 50% cover over all |

| Total              | 0.21 %X0          | 0.15 %X0           |

- Test of first thin DEPFETs (PXD6) well advanced

- beam tests show the expected resolution and S/N at full-speed readout

- First batch of Belle II production of 75µm thin DEPFETs launched

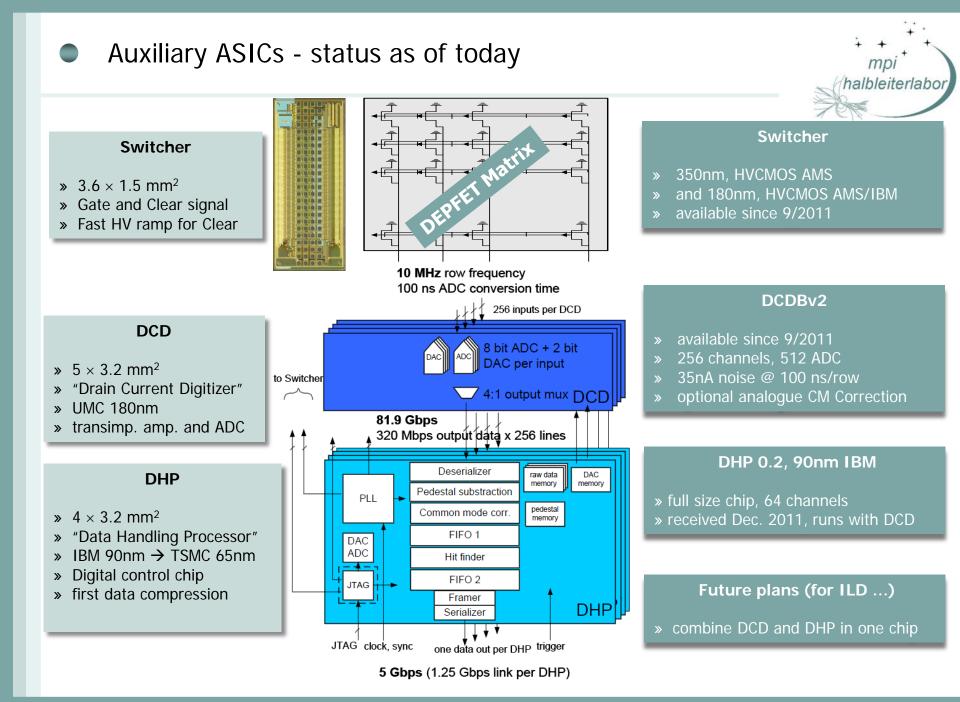

- Full set of auxiliary ASCIs available and tested at full speed (320 MHz, 10MHz row rate)

- test of on- and off-ladder interconnect with dedicated test devices

"E-MCM": Third metal layer, flip-chip, kapton attachment... → full system test!

- prospects for the DEPFET at ILC:

- solution gain of 2x-4x in speed with optimized pixel layout and 3rd metal layer ( $\rightarrow$  1/25µs frame rate)

- Iadder concept for the ILD 5-layer layout can be used as engineered

- with little R&D material budget down to 0.15 %X0 possible

- concept for all-silicon double layers shown, DEPFET is not linked with the 5-layer ILD layout!!

- I had to skip:

- mechanical/thermal measurements on thin ladders ... (gas cooling, vibrations of thin sensors..)

- radiation tolerance of DEPFETs: irradiation results with 10 MeV electrons (→ backup slides)

- and many other (important technical!!!) details  $\rightarrow$  ~300 pages Belle II PXD "White Book"

- Paper to be published in IEEE TNS: "DEPFET active pixel detectors for a future linear e+e- collider"

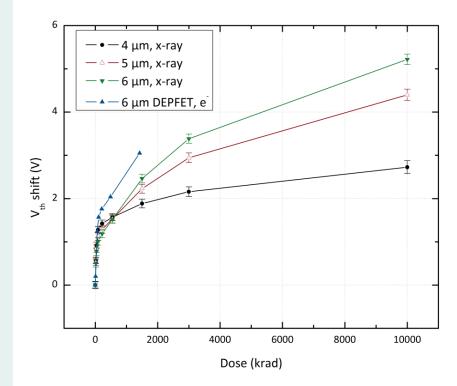

### Electron irradiations

- » Compare 10 MeV electrons and x-ray irradiation

- » e- irradiation in commercial irradiation facility in Dresden

DEPFET V<sub>th</sub> shift after e- and x-ray irradiation

1.5x10<sup>-4</sup>  $\alpha = 4.08 * 10^{-19} \text{ A/cm}$ 1.3x10<sup>-4</sup> 1.0x10<sup>-4</sup> AI / V (A/cm<sup>3</sup>) 7.5x10<sup>-5</sup> 5.0x10<sup>-5</sup> Equation v = a + b\*x No Weighting Weight 2.18605E-10 Residual Sum of Squares 2.5x10<sup>-5</sup> Adj. R-Square 0.98955 Standard Error Value Intercer Deltal/V Slope 4.08259E-19 2.09495E-20 0.0 2.00E+014 0.00E+000 1.00E+014 3.00E+014 4.00E+014 Electron fluence (cm<sup>-2</sup>)

NIEL damage measured on pin-diodes a(10 MeV n)=4e-17 (A/cm) (RD50) a(10 MeV e-)=4e-19 (A/cm) (this work)

", hardeness factor" e-: 0.01 (0.04 expected)

Hardness Factor of 10 MeV electrons

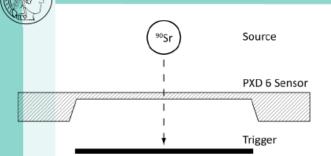

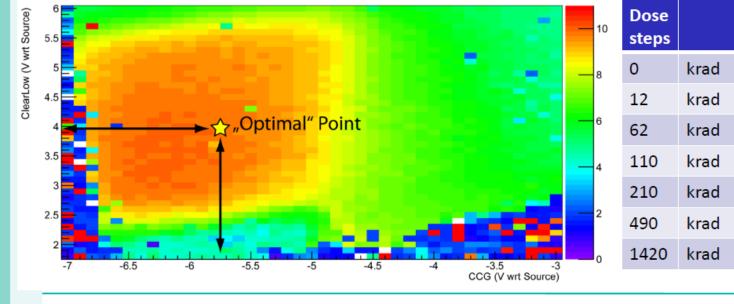

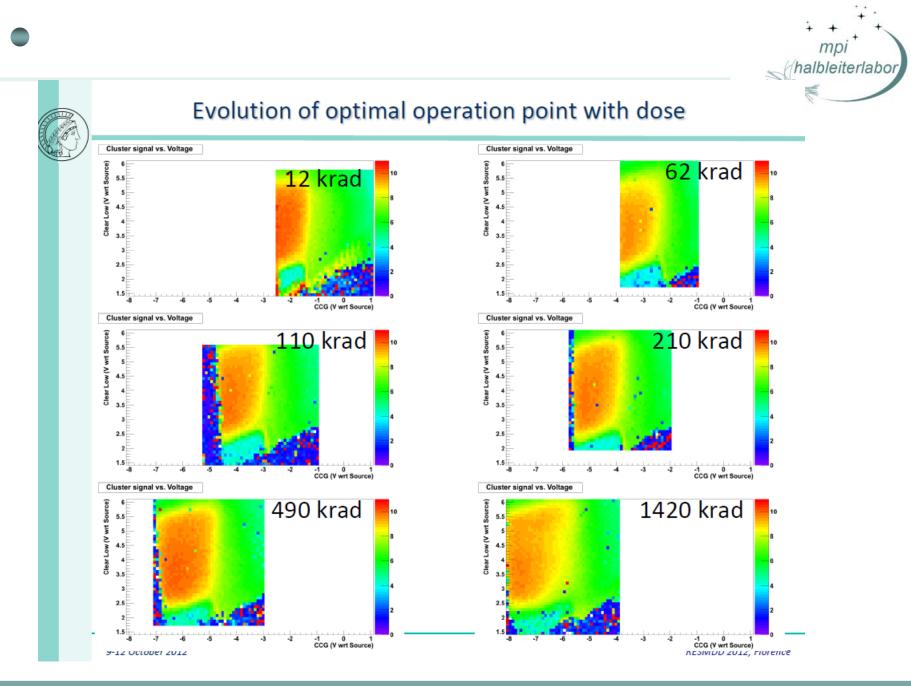

### Electron irradiation of DEPFET matrix

Matrix irradiated with 10 MeV electrons in increasing dose steps.

Shift in V<sub>th</sub> of Clear Gate via a  $^{90}\rm{Sr}$  and fitting a Landau to the MPV. Then choose optimal operation point.

### Cluster charge collection in the ClearLow-ClearGate parameter space

9-12 October 2012

RESMDD 2012, Florence

### LCWS 2012, Arlington, October 2012

#### Ladislav Andricek, MPI für Physik, HLL